Sample &

Buy

### TUSB3210

SLLS466G - FEBRUARY 2001 - REVISED DECEMBER 2015

Support &

Community

....

# **TUSB3210 Universal Serial Bus General-Purpose Device Controller**

Technical

Documents

## 1 Features

- Multiproduct Support With One Code and One Chip (up to 16 Products With One Chip)

- Fully Compliant With USB 2.0 Full-Speed Specifications: TID #40270269

- Supports 12-Mbits/s USB Data Rate (Full Speed)

- Supports USB Suspend, Resume, and Remote Wake-Up Operation

- Integrated 8052 Microcontroller With:

- 256 × 8 RAM for Internal Data

- 8K × 8 RAM Code Space Available for Downloadable Firmware From Host or I<sup>2</sup>C Port

- 8K × 8 RAM for Development

- 512 × 8 Shared RAM Used for Data Buffers and Endpoint Descriptor Blocks (EDB)

- Buffer Space for USB Packet Transactions

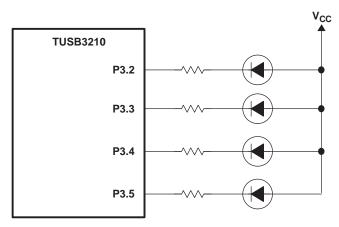

- Four 8052 GPIO Ports: Port 0, 1, 2, and 3

- Master I<sup>2</sup>C Controller for External Slave Device Access

- Watchdog Timer

- Operates From a 12-MHz Crystal

- On-Chip PLL Generates 48 MHz

- Supports a Total of Three Input and Three Output (Interrupt, Bulk) Endpoints

- Power-Down Mode

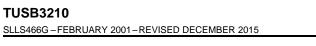

- 64-Pin LQFP Package

## 2 Applications

Tools &

Software

- Keyboards

- Barcode Readers

- Flash Memory Readers

- General-Purpose Controllers

## **3** Description

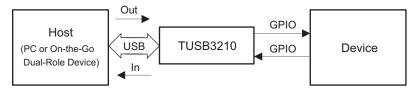

The TUSB3210 device is a USB-based controller targeted as a general-purpose MCU with GPIO. The TUSB3210 device has  $8K \times 8$  RAM space for application development. In addition, the programmability of the TUSB3210 device makes it flexible enough to use for various other general USB I/O applications.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |  |  |

|-------------|-----------|---------------------|--|--|

| TUSB3210    | LQFP (64) | 10.00 mm × 10.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

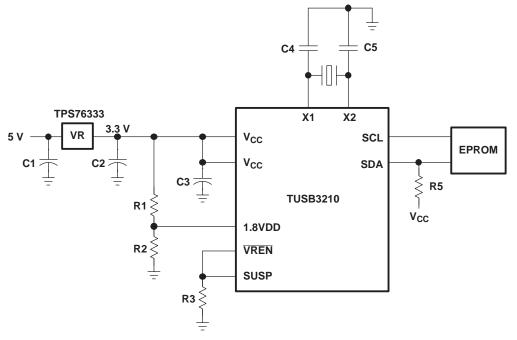

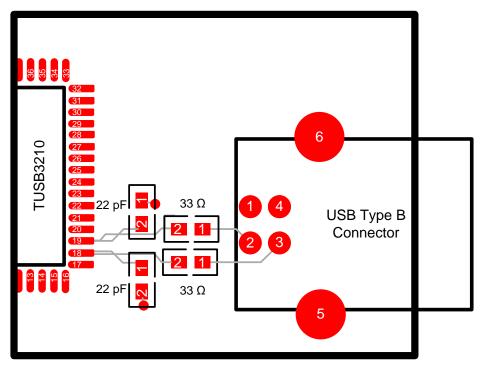

#### **Application Example**

Texas Instruments

www.ti.com

# **Table of Contents**

| 1 | Feat | tures                            | 1 |

|---|------|----------------------------------|---|

| 2 | Арр  | lications                        | 1 |

| 3 | Des  | cription                         | 1 |

| 4 | Rev  | ision History                    | 2 |

| 5 | Pin  | Configuration and Functions      | 4 |

| 6 | Spe  | cifications                      | 6 |

|   | 6.1  | Absolute Maximum Ratings         | 6 |

|   | 6.2  | ESD Ratings                      | 6 |

|   | 6.3  | Recommended Operating Conditions |   |

|   | 6.4  | Thermal Information              | 6 |

|   | 6.5  | Electrical Characteristics       | 7 |

| 7 | Deta | ailed Description                |   |

|   | 7.1  | Overview                         | 8 |

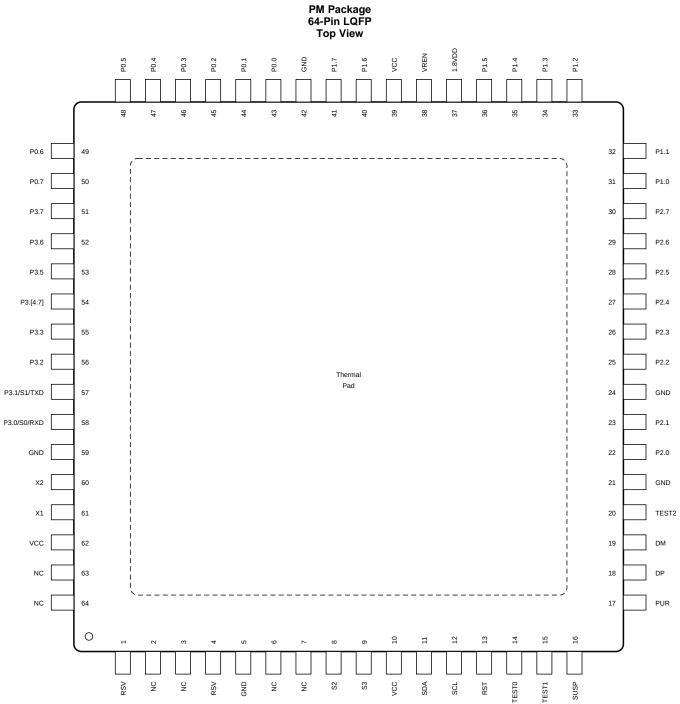

|   | 7.2  | Functional Block Diagram         | 8 |

|   | 7.3  | Feature Description              |   |

|   | 7.4  | Device Functional Modes          | 9 |

|   |      |                                  |   |

|    | 7.5  | Register Maps                     | 10 |

|----|------|-----------------------------------|----|

| 8  | Арр  | lication and Implementation       | 39 |

|    | 8.1  | Application Information           | 39 |

|    | 8.2  | Typical Applications              | 40 |

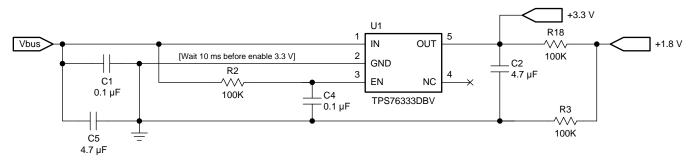

| 9  | Pow  | er Supply Recommendations         | 43 |

| 10 | Lay  | out                               | 43 |

|    | 10.1 | Layout Guidelines                 | 43 |

|    | 10.2 | Layout Example                    | 44 |

| 11 | Dev  | ice and Documentation Support     | 45 |

|    | 11.1 | Documentation Support             | 45 |

|    | 11.2 | Community Resources               | 45 |

|    | 11.3 | Trademarks                        | 45 |

|    | 11.4 | Electrostatic Discharge Caution   | 45 |

|    | 11.5 | Glossary                          | 45 |

| 12 |      | hanical, Packaging, and Orderable |    |

|    | Info | rmation                           | 45 |

|    |      |                                   |    |

# 4 Revision History

| REVISION | DATE          | CHANGES                                                                                                                                                                                                                                                                                                                                                             |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F        | December 2015 | 1. Pin Configuration and Functions section, ESD Ratings table,<br>Thermal Information table, Feature Description section, Device<br>Functional Modes, Application and Implementation section, Power<br>Supply Recommendations section, Layout section, Device and<br>Documentation Support section, and Mechanical, Packaging, and<br>Orderable Information section |

| E        | August 2007   | <ol> <li>Deleted reference to 8K × 8 ROM</li> <li>Clarified Section 2.2.2, bit 0.</li> <li>Clarified Section 2.6.5 (VID/PID support)</li> </ol>                                                                                                                                                                                                                     |

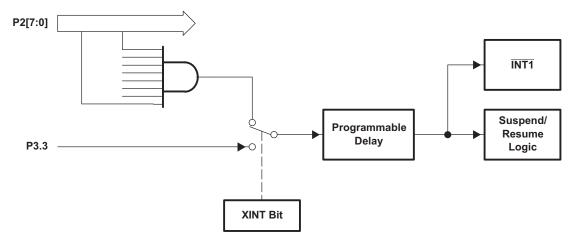

| D        | June 2004     | <ol> <li>Corrected description for pin 20 (TEST2).</li> <li>Added description of programmable delay to the <i>P2[7:0]</i>, <i>P3.3 Interrupt (INT1)</i> section.</li> <li>Added delay values for I[3:0] to the INTCFG register description.</li> </ol>                                                                                                              |

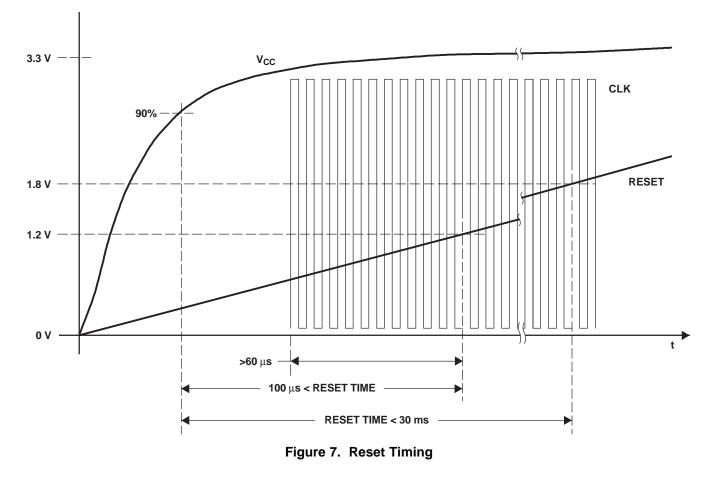

| с        | Nov-2003      | <ol> <li>Added USB logo to cover page.</li> <li>Corrected pin 37 (1.8VDD) polarity in <i>Terminal Functions</i> table.</li> <li>Removed note for pin 20 (TEST2) from <i>Terminal Functions</i> table.</li> <li>Removed application diagram Figure 7.</li> <li>Clarified Section 4-2, Reset Timing</li> </ol>                                                        |

| В        | April 2003    | <ol> <li>Grammatical clean-up</li> <li>Clarification on pin 55 (P3.3) and its functionality as INT1.</li> <li>Additional corrections in the <i>8052 Interrupt and Status Registers</i> section.</li> </ol>                                                                                                                                                          |

## **Revision History (continued)**

| REVISION | DATE CHANGES  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A        | February 2003 | <ol> <li>Removed most references to ROM version, including the <i>MCU</i><br/><i>Memory Map (ROM Version)</i> figure.</li> <li>Clarified pin names and descriptions for pins 8 (S2), 9 (S3), 21<br/>(GND), 37 (VDD18), 57 (P3.1/S1/TXD), and 58 (P3.0/S0/RXD).</li> <li>Removed NOTE from cover page.</li> <li>Expanded Ordering Information table.</li> <li>Clarified pin functions for pins 14 (TEST0) and 15 (TEST1) (14<br/>&amp; 15) in Terminal Functions table. Simplified Terminal Function<br/>table for GPIO ports.</li> <li>Added note on open-drain output pins for Terminal Functions<br/>table.</li> <li>Added ET2 information to the 8052 Interrupt Location Map<br/>table and further clarified the entire 8052 Interrupt and Status<br/>Registers section.</li> <li>Corrected quiescent and suspend current values in Electrical<br/>Characteristics table.</li> </ol> |  |

| *        | February 2001 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

Texas Instruments

www.ti.com

TUSB3210 SLLS466G – FEBRUARY 2001–REVISED DECEMBER 2015

#### www.ti.com

### **Pin Functions**

| PIN         |                                      |                                                                                                        | <b>DECODIPTION</b>                                                                                                                                                                                            |  |

|-------------|--------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME        | NO.                                  | I/O                                                                                                    | DESCRIPTION                                                                                                                                                                                                   |  |

| 1.8VDD      | 37                                   | I/O                                                                                                    | 1.8 V. When VREN is high, 1.8 V must be applied externally to provide current for the core during suspend.                                                                                                    |  |

| DM          | 19                                   | I/O                                                                                                    | Differential data-minus USB                                                                                                                                                                                   |  |

| DP          | 18                                   | I/O                                                                                                    | Differential data-plus USB                                                                                                                                                                                    |  |

| GND         | 5, 21, 24, 42,<br>59                 | _                                                                                                      | Power supply ground                                                                                                                                                                                           |  |

| NC          | 2, 3, 6, 7, 63,<br>64                |                                                                                                        | No connection                                                                                                                                                                                                 |  |

| P0.[0:7]    | 43, 44, 45,<br>46, 47, 48,<br>49, 50 | I/O                                                                                                    | General-purpose I/O port 0 bits 0–7, Schmitt-trigger input, 100-µA active pullup, open-drain output                                                                                                           |  |

| P1.[0:7]    | 31, 32, 33,<br>34, 35, 36,<br>40, 41 | I/O                                                                                                    | General-purpose I/O port 1 bits 0–7, Schmitt-trigger input, 100-µA active pullup, open-drain output                                                                                                           |  |

| P2.[0:7]    | 22, 23, 25,<br>26, 27, 28,<br>29, 30 | I/O                                                                                                    | General-purpose I/O port 2 bits 0–7, Schmitt-trigger input, 100-µA active pullup, open-drain output                                                                                                           |  |

|             |                                      |                                                                                                        | P3.0: General-purpose I/O port 3 bit 0, Schmitt-trigger input, 100-µA active pullup, open-drain output                                                                                                        |  |

| P3.0/S0/RXD | 58                                   | I/O                                                                                                    | S0: See VIDSTA: VID/PID Status Register                                                                                                                                                                       |  |

|             |                                      |                                                                                                        | RXD: Can be used as a UART interface                                                                                                                                                                          |  |

|             |                                      | P3.1: General-purpose I/O port 3 bit 1, Schmitt-trigger input, 100-µA active pullup, open-drain output |                                                                                                                                                                                                               |  |

| P3.1/S1/TXD | 3.1/S1/TXD 57 I                      |                                                                                                        | S1: See VIDSTA: VID/PID Status Register                                                                                                                                                                       |  |

|             |                                      |                                                                                                        | TXD: Can be used as a UART interface                                                                                                                                                                          |  |

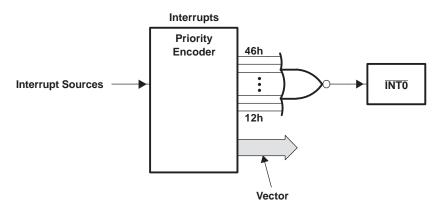

| P3.2        | 56                                   | I/O                                                                                                    | General-purpose I/O port 3 bit 2, Schmitt-trigger input, 100-μA active pullup, open-drain output; IN only used internally (see <i>Logical Interrupt Connection Diagram (INTO)</i> )                           |  |

| P3.3        | 55                                   | I/O                                                                                                    | General- <u>purp</u> ose I/O port 3 bit 3, Schmitt-trigger input, 100-µA active pullup, open-drain output; may support INT1 input, depending on configuration (see Figure 6)                                  |  |

| P3.[4:7]    | 54, 53, 52, 51                       | I/O                                                                                                    | General-purpose I/O port 3 bits 4-7, Schmitt-trigger input, 100-µA active pullup, open-drain output                                                                                                           |  |

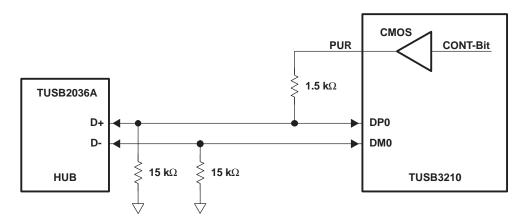

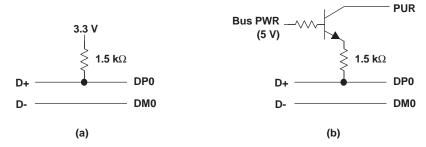

| PUR         | 17                                   | 0                                                                                                      | Pullup resistor connection pin (3-state) push-pull CMOS output (±4 mA)                                                                                                                                        |  |

| RST         | 13                                   | I                                                                                                      | Controller master reset signal, Schmitt-trigger input, 100-µA active pullup                                                                                                                                   |  |

| RSV         | 1, 4                                 | —                                                                                                      | Reserved (Do not connect these pins.)                                                                                                                                                                         |  |

| S2          | 8                                    | I                                                                                                      | General-purpose input, can be used for VID/PID selection under firmware control. This input has no internal pullup; therefore, it must be driven or pulled either low or high and cannot be left unconnected. |  |

| S3          | 9                                    | I                                                                                                      | General-purpose input. This input has no internal pullup; therefore, it must be driven or pulled either low or high and cannot be left unconnected.                                                           |  |

| SCL         | 12                                   | 0                                                                                                      | Serial clock I <sup>2</sup> C; push-pull output                                                                                                                                                               |  |

| SDA         | 11                                   | I/O                                                                                                    | Serial data I <sup>2</sup> C; open-drain output                                                                                                                                                               |  |

| SUSP        | 16                                   | 0                                                                                                      | Suspend status signal: suspended (HIGH); unsuspended (LOW)                                                                                                                                                    |  |

| TEST0       | 14                                   | I                                                                                                      | est input0, Schmitt-trigger input, 100-µA active pullup                                                                                                                                                       |  |

| TEST1       | 15                                   | I                                                                                                      | Test input1, Schmitt-trigger input, 100-µA active pullup                                                                                                                                                      |  |

| TEST2       | 20                                   | I                                                                                                      | Test input2, Schmitt-trigger input, 100-µA active pullup. This pin is reserved for testing purposes and must be left unconnected.                                                                             |  |

| VCC         | 10, 39, 62                           | —                                                                                                      | Power supply input, 3.3-V typical                                                                                                                                                                             |  |

| VREN        | 38                                   | Ι                                                                                                      | Voltage regulator enable: enable active-LOW; disable active-HIGH                                                                                                                                              |  |

| X1          | 61                                   | I                                                                                                      | 12-MHz crystal input                                                                                                                                                                                          |  |

| X2          | 60                                   | 0                                                                                                      | 12-MHz crystal output                                                                                                                                                                                         |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                      | MIN  | MAX                   | UNIT |

|------------------|----------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage       | -0.5 | 4                     | V    |

| VI               | Input voltage        | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Vo               | Output voltage       | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| I <sub>IK</sub>  | Input clamp current  |      | ±20                   | mA   |

| I <sub>OK</sub>  | Output clamp current |      | ±20                   | mA   |

| T <sub>stg</sub> | Storage temperature  | -65  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 $^{\left( 2\right) }$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

|                 |                          | MIN | NOM | MAX      | UNIT |

|-----------------|--------------------------|-----|-----|----------|------|

| V <sub>CC</sub> | Supply voltage           | 3   | 3.3 | 3.6      | V    |

| VI              | Input voltage            | 0   |     | $V_{CC}$ | V    |

| $V_{\text{IH}}$ | High-level input voltage | 2   |     | $V_{CC}$ | V    |

| VIL             | Low-level input voltage  | 0   |     | 0.8      | V    |

| T <sub>A</sub>  | Operating temperature    | 0   |     | 70       | °C   |

### 6.4 Thermal Information

|                       |                                              | TUSB3210  |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PM (LQFP) | UNIT |

|                       |                                              | 64 PINS   |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 61.3      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 25.1      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 32.4      | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 2.4       | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 32.1      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$T_A = 25^{\circ}C, V_{CC} = 3.3 V \pm 0.3 V, GND = 0 V$

|                     | PARAMETER                                         | TEST CONDITIONS                     | MIN                   | TYP | MAX | UNIT |

|---------------------|---------------------------------------------------|-------------------------------------|-----------------------|-----|-----|------|

| V <sub>OH</sub>     | High-level output voltage                         | $I_{OH} = -4 \text{ mA}$            | V <sub>CC</sub> – 0.5 |     |     | V    |

| V <sub>OL</sub>     | Low-level output voltage                          | I <sub>OL</sub> = 4 mA              |                       |     | 0.5 | V    |

| V <sub>IT+</sub>    | Positive input threshold voltage                  | $V_I = V_{IH}$                      |                       |     | 2   | V    |

| V <sub>IT-</sub>    | Negative input threshold voltage                  | $V_{I} = V_{IL}$                    | 0.8                   |     |     | V    |

| V <sub>hys</sub>    | Hysteresis (V <sub>IT+</sub> – V <sub>IT–</sub> ) | V <sub>I</sub> = V <sub>IH</sub>    |                       | 1   |     | V    |

| IIH                 | High-level input current                          | $V_{I} = V_{IH}$                    |                       |     | ±1  | μA   |

| IIL                 | Low-level input current                           | $V_{I} = V_{IL}$                    |                       |     | ±1  | μA   |

| I <sub>OZ</sub>     | Output leakage current (Hi-Z)                     | $V_{I} = V_{CC} \text{ or } V_{SS}$ |                       |     | 10  | μA   |

| CI                  | Input capacitance                                 |                                     |                       | 5   |     | pF   |

| Co                  | Output capacitance                                |                                     |                       | 7   |     | pF   |

| I <sub>CC</sub>     | Quiescent                                         |                                     |                       | 25  | 45  | mA   |

| I <sub>CCx</sub>    | Suspend                                           |                                     |                       |     | 45  | μA   |

| I <sub>CCx1.8</sub> | Suspend 1.8 VDD                                   |                                     |                       |     | 1   | μA   |

## 7 Detailed Description

### 7.1 Overview

The TUSB3210 device is a USB-based controller targeted as a general-purpose MCU with GPIO. The TUSB3210 device has 8K × 8 RAM space for application development. In addition, the programmability of the TUSB3210 device makes it flexible enough to use for various general USB I/O applications. Unique vendor identification and product identification (VID/PID) can be selected without the use of an external EEPROM. The onboard oscillator generates the internal system clocks using a 12-MHz crystal. The TUSB3210 device can be programmed through an inter-IC (I<sup>2</sup>C) serial interface at power on from an EEPROM, or the application firmware can be downloaded from a host PC through USB. The popular 8052-based microprocessor allows several third-party standard tools to be used for application development. In addition, the vast amounts of application code available in the general market can also be used (this may or may not require some code modification due to hardware variations).

## 7.2 Functional Block Diagram

NOTE: 8K × 8 ROM version is available. Contact TI Marketing.

#### 7.3 Feature Description

### 7.3.1 USB 2.0 Full-Speed Compliant

The TUSB3210 device s fully compliant with USB 2.0 full-speed; it supports 12 Mbits/s of USB data rate (full speed) as well as supporting USB suspend, resume, and remote wake-up operation.

### 7.3.2 Code Space Available

The TUSB3210 device has 8K × 8 RAM for firmware development. This firmware can be loaded though USB or using  $I^2C$  serial interface from an EEPROM. The MCU executes a read from an external EEPROM and tests to determine if it contains the code (test for boot signature). If it contains the code, the MCU reads from EEPROM and writes to the 8K RAM in XDATA space. If not, the MCU proceeds to boot from the USB.

#### 7.3.3 Clock Generation

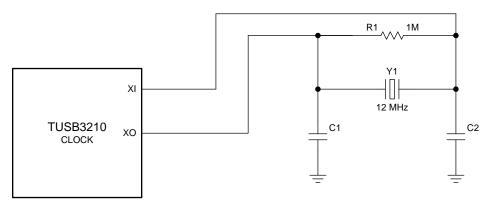

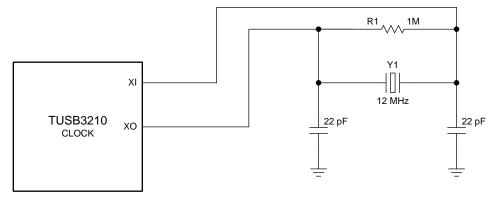

The TUSB3210 device accepts a 12-MHz crystal input to drive an internal oscillator of 48 MHz. If a clock is provided to X1 instead of a crystal, X2 is left open. Otherwise, if a crystal is used, the connection must follow the guidelines shown in Figure 1. Because X1 and X2 are coupled to other leads and supplies on the PCB, it is important to keep the leads as short as possible and away from any switching leads. TI also recommends minimizing the capacitance between X1 and X2, which can be accomplished by shielding C1 and C2 with the clean ground lines.

Figure 1. Clock Generation Diagram

### 7.3.4 UART Interface

The TUSB3210 device can use P3.0 and P3.1 as UART port; this UART is normally used for debug purposes.

### 7.4 Device Functional Modes

#### 7.4.1 Interface Configuration

The TUSB3210 device contains onboard ROM microcode, which enables the MCU to enumerate the device as a USB peripheral. The ROM microcode can also load application code into internal RAM from either external memory through the I<sup>2</sup>C bus or from the host through the USB.

#### 7.4.2 GPIO Controller

The TUSB3210 device is a USB-based controller targeted as a general-purpose MCU with GPIO. The TUSB3210 device has 8K × 8 RAM space for application development to control these GPIOs.

TEXAS INSTRUMENTS

www.ti.com

### 7.5 Register Maps

| TEST0 | TEST1 | FUNCTION                                                                      |  |  |

|-------|-------|-------------------------------------------------------------------------------|--|--|

| 0     | 0     | Selects 48-MHz clock input (from an oscillator or other onboard clock source) |  |  |

| 0     | 1     | Reserved for testing purposes                                                 |  |  |

| 1     | 0     | Reserved for testing purposes                                                 |  |  |

| 1     | 1     | Selects 12-MHz crystal as clock source (default)                              |  |  |

#### Table 1. Test0 and Test1 Functions

#### 7.5.1 MCU Memory Map

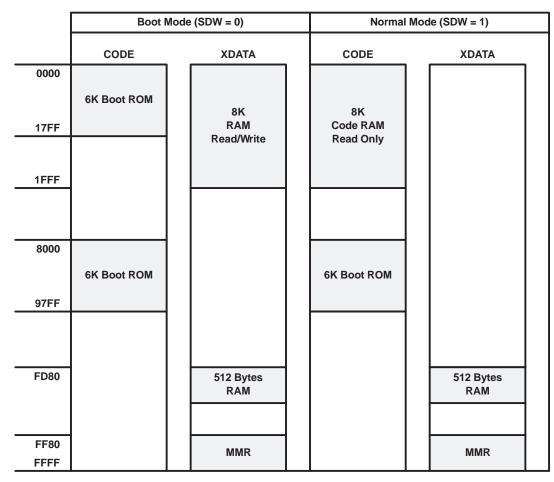

Figure 2 illustrates the MCU memory map under boot and normal operation. It must be noted that the internal 256 bytes of IDATA are not shown because it is assumed to be in the standard 8052 location (0000 to 00FF). The shaded areas represent the internal ROM/RAM.

When the SDW bit = 0 (boot mode): The 6K ROM is mapped to address 0000–17FF and is duplicated in location 8000–97FF in code space. The internal 8K RAM is mapped to address range 0000–1FFF in data space. Buffers, MMR and I/O are mapped to address range (FD80–FFFF) in data space.

When the SDW bit = 1 (normal mode): The 6K ROM is mapped to 8000–97FF in code space. The internal 8K RAM is mapped to address range 0000–1FFF in code space. Buffers, MMR, and I/O are mapped to address range FD80–FFFF in data space.

| Figure 2. | MCU | Memory I | Map | (TUSB3210) |

|-----------|-----|----------|-----|------------|

|-----------|-----|----------|-----|------------|

#### TUSB3210 SLLS466G – FEBRUARY 2001 – REVISED DECEMBER 2015

#### www.ti.com

#### 7.5.2 Miscellaneous Registers

#### 7.5.2.1 TUSB3210 Boot Operation

Because the code space is in RAM (with the exception of the boot ROM), the TUSB3210 firmware must be loaded from an external source. Two options for booting are available: an external serial EEPROM source can be connected to the I<sup>2</sup>C bus, or the host can be used through the USB. On device reset, the SDW bit (in the ROM register) and the CONT bit in the USB control register (USBCTL) are cleared. This configures the memory space to boot mode (see Table 3) and keeps the device *disconnected* from the host.

The first instruction is fetched from location 0000 (which is in the 6K ROM). The 8K RAM is mapped to XDATA space (location 0000h). The MCU executes a read from an external EEPROM and tests to determine if it contains the code (test for boot signature). If it contains the code, the MCU reads from EEPROM and writes to the 8K RAM in XDATA space. If not, the MCU proceeds to boot from the USB.

Once the code is loaded, the MCU sets SDW to 1. This switches the memory map to normal mode; that is, the 8K RAM is mapped to code space, and the MCU starts executing from location 0000h. When the switch is done, the MCU sets CONT to 1 (in USBCTL register) This *connects* the device to the USB bus, resulting in the normal USB device enumeration.

### 7.5.2.2 MCNFG: MCU Configuration Register

This register is used to control the MCU clock rate (R/O notation indicates read only by the MCU).

| 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|------|-----|-----|-----|-----|-----|-----|

| RSV | XINT | RSV | R3  | R2  | R1  | R0  | SDW |

| R/W | R/W  | R/O | R/O | R/O | R/O | R/O | R/W |

| BIT | NAME   | RESET     |                                                                                                                                                                                                                                                            | FUNCTION                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |           | This bit ena                                                                                                                                                                                                                                               | bles/disables boot ROM.                                                                                                                                                                                                                                                                                                                         |

| 0   | SDW    | 0         | SDW = 0                                                                                                                                                                                                                                                    | When clear, the MCU executes from the 6K boot ROM space. The boot ROM appears in two locations: 0000 and 8000h. The 8K RAM is mapped to XDATA space; therefore, read/write operation is possible. This bit is set by the MCU after the RAM load is completed. The MCU cannot clear this bit. It is cleared on power-up reset or function reset. |

|     |        | SDW = 1   | When set by the MCU, the 6K boot ROM maps to location 8000h, and the 8K RAM is mapped to code space, starting at location 0000h. At this point, the MCU executes from RAM, and write operation is disabled (no write operation is possible in code space). |                                                                                                                                                                                                                                                                                                                                                 |

| 4–1 | R[3:0] | No effect | These bits r                                                                                                                                                                                                                                               | reflect the device revision number.                                                                                                                                                                                                                                                                                                             |

| 5   | RSV    | 0         | Reserved                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                 |

|     |        |           | INT1 source                                                                                                                                                                                                                                                | e control bit                                                                                                                                                                                                                                                                                                                                   |

| 6   | XINT   | 0         | XINT = 0                                                                                                                                                                                                                                                   | INT1 is connected to the P3.3 pin and operates as a standard INT1 interrupt.                                                                                                                                                                                                                                                                    |

|     |        |           | XINT = 1                                                                                                                                                                                                                                                   | INT1 is connected to the OR of the port-2 inputs.                                                                                                                                                                                                                                                                                               |

| 7   | RSV    | 0         | Reserved                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                 |

## 7.5.2.3 PUR\_n: GPIO Pullup Register for Port n (n = 0 to 3)

PUR\_0: GPIO pullup register for port 0

PUR\_1: GPIO pullup register for port 1

PUR\_2: GPIO pullup register for port 2

PUR\_3: GPIO pullup register for port 3

| 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PORT_n.7 | PORT_n.6 | PORT_n.5 | PORT_n.4 | PORT_n.3 | PORT_n.2 | PORT_n.1 | PORT_n.0 |

| R/W      |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| BIT | NAME                     | RESET | FUNCTION                                                                                                                                                                                                                                                                   |

|-----|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–7 | PORT_n.N<br>(N = 0 to 7) | 0     | The MCU can write to this register. If the MCU sets this bit to 1, the internal pullup resistor is disconnected from the pin. If the MCU clears this bit to 0, the pullup resistor is connected to the pin. The pullup resistor is connected to the $V_{CC}$ power supply. |

### 7.5.2.4 INTCFG: Interrupt Configuration

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| RSV | RSV | RSV | RSV | 13  | 12  | l1  | 10  |

| R/O | R/O | R/O | R/O | R/W | R/W | R/W | R/W |

| BIT | NAME   | RESET |                                   | FUNCTION                                                                                                                                           |

|-----|--------|-------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|     |        |       | The MCU can w<br>the lower nibble | rite to this register to set the interrupt delay time for port 2 on the MCU. The value of represents the delay in ms. Default after reset is 2 ms. |

|     |        |       | I[3:0]                            | Delay                                                                                                                                              |

|     |        |       | 0000                              | 5 ms                                                                                                                                               |

|     |        |       | 0001                              | 5 ms                                                                                                                                               |

|     |        |       | 0010                              | 2 ms (default)                                                                                                                                     |

|     |        |       | 0011                              | 3 ms                                                                                                                                               |

|     |        |       | 0100                              | 4 ms                                                                                                                                               |

|     |        |       | 0101                              | 5 ms                                                                                                                                               |

| 0–3 | I[3:0] | 0010  | 0110                              | 6 ms                                                                                                                                               |

|     |        |       | 0111                              | 7 ms                                                                                                                                               |

|     |        |       | 1000                              | 8 ms                                                                                                                                               |

|     |        |       | 1001                              | 9 ms                                                                                                                                               |

|     |        |       | 1010                              | 10 ms                                                                                                                                              |

|     |        |       | 1011                              | 5 ms                                                                                                                                               |

|     |        |       | 1100                              | 5 ms                                                                                                                                               |

|     |        |       | 1101                              | 5 ms                                                                                                                                               |

|     |        |       | 1110                              | 5 ms                                                                                                                                               |

|     |        |       | 1111                              | 5 ms                                                                                                                                               |

| 4–7 | RSV    | 0     | Reserved                          |                                                                                                                                                    |

#### 7.5.2.5 WDCSR: Watchdog Timer, Control, and Status Register

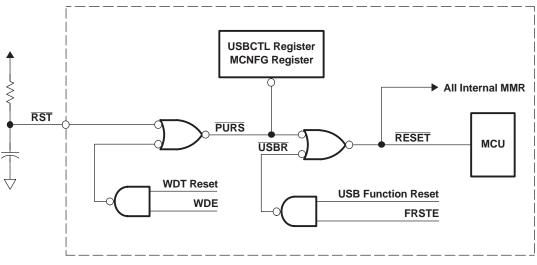

A watchdog timer (WDT) with 1-ms clock is provided. The watchdog timer works only when a USB start-of-frame has been detected by the TUSB3210. If this register is not accessed for a period of 32 ms, the WDT counter resets the MCU (see Figure 3, *Reset Diagram*). When the IDL bit in PCON is set, the WDT is suspended until an interrupt is detected. At this point, the IDL bit is cleared and the WDT resumes operation. The WDE bit of this register is cleared only on power up or USB reset (if enabled). When the MCU writes a 1 to the WDE bit of this register, the WDT starts running (W/O notation indicates write only by the MCU).

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| WDE | WDR | RSV | RSV | RSV | RSV | RSV | WDT |

| R/W | R/W | R/O | R/O | R/O | R/O | R/O | W/O |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| BIT | NAME | RESET |             | FUNCTION                                                                                                                                                                                                                                                        |  |  |  |

|-----|------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0   | WDT  | 0     | in a period | he MCU must write a 1 to this bit to prevent the WDT from resetting the MCU. If the MCU does not write a 1 a period of 31 ms, the WDT resets the device. Writing a 0 has no effect on the WDT. (WDT is a 5-bit punter using a 1-ms CLK.) This bit is read as 0. |  |  |  |

| 5–1 | RSV  | 0     | Reserved    | Reserved = 0                                                                                                                                                                                                                                                    |  |  |  |

|     |      |       |             | reset indication bit. This bit indicates if the reset occurred due to power-on reset or watchdog timer                                                                                                                                                          |  |  |  |

| 6   | WDR  | 0     | WDR = 0     | A power-up or USB reset occurred.                                                                                                                                                                                                                               |  |  |  |

|     |      |       | WDR = 1     | A watchdog time-out reset occurred. To clear this bit, the MCU must write a 1. Writing a 0 has no effect.                                                                                                                                                       |  |  |  |

|     |      |       | Watchdog    | timer enable.                                                                                                                                                                                                                                                   |  |  |  |

| 7   | WDE  | 0     | WDE = 0     | Disabled                                                                                                                                                                                                                                                        |  |  |  |

|     |      |       | WDE = 1     | Enabled                                                                                                                                                                                                                                                         |  |  |  |

#### 7.5.2.6 PCON: Power Control Register (at SFR 87h)

| 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|------|-----|-----|-----|-----|-----|-----|-----|

| SMOD | RSV | RSV | RSV | GF1 | GF0 | RSV | IDL |

| R/W  | R/O | R/O | R/O | R/W | R/W | R/O | R/W |

| BIT | NAME    | RESET                   |                            | FUNCTION                                                                                                                                                                                                                                                                                |  |  |

|-----|---------|-------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     |         |                         | MCU idle mo                | de bit. This bit can be set by the MCU and is cleared only by the $\overline{INT1}$ interrupt.                                                                                                                                                                                          |  |  |

|     |         | 0<br>IDL = 0<br>IDL = 1 | IDL = 0                    | The MCU is not in idle mode. This bit is cleared by the $\overline{INT1}$ interrupt logic when $\overline{INT1}$ is asserted for at least 400 $\mu s.$                                                                                                                                  |  |  |

| 0   | IDL     |                         | IDL = 1                    | The MCU is in idle mode and RAM is in low-power mode. The oscillator/APLL is off and the WDT is suspended. When in suspend mode, only INT1 can be used to exit from idle state and generate an interrupt. INT1 must be asserted for at least 400 µs for the interrupt to be recognized. |  |  |

| 1   | RSV     | 0                       | Reserved                   |                                                                                                                                                                                                                                                                                         |  |  |

| 3–2 | GF[1:0] | 00                      | General-purp               | ose bits. The MCU can write and read them.                                                                                                                                                                                                                                              |  |  |

| 6–4 | RSV     | 0                       | Reserved                   | Reserved                                                                                                                                                                                                                                                                                |  |  |

| 7   | SMOD    | 0                       | Double baud specification. | Double baud-rate control bit. For more information, see the UART serial interface in the M8052 core specification.                                                                                                                                                                      |  |  |

SLLS466G-FEBRUARY 2001-REVISED DECEMBER 2015

www.ti.com

### 7.5.3 Buffers + I/O RAM Map

The address range from FD80 to FFFF is reserved for data buffers, set-up packet, endpoint descriptor blocks (EDB), and all I/O. RAM space of 512 bytes [FD80–FF7F] is used for EDB and buffers. The FF80–FFFF range is used for memory-mapped registers (MMR). represents the internal XDATA space allocation.

The address range from FD80 to FFFF is reserved for data buffers, set-up packet, endpoint descriptor blocks(EDB), and all I/O. RAM space of 512 bytes [FD80–FF7F] is used for EDB and buffers. The FF80–FFFF range is used for memory-mapped registers (MMR). Table 2 represents the internal XDATA space allocation and Table 3 describes the registers function.

| DESCRIPTION                         | ADDRESS RANGE |                 |

|-------------------------------------|---------------|-----------------|

| Internal                            | FFFF          |                 |

| memory-mapped registers             | ↑             |                 |

| (MMR)                               | FF80          |                 |

| E e de statute servicite e blander  | FF7F          |                 |

| Endpoint descriptor blocks<br>(EDB) | ↑             |                 |

| (200)                               | FF08          |                 |

|                                     | FF07          |                 |

| Set-up packet buffer                | ↑             |                 |

|                                     | FF00          |                 |

|                                     | FEFF          |                 |

| Input endpoint-0 buffer             | ↑             | 512-Byte<br>RAM |

|                                     | FEF8          |                 |

|                                     | FEF7          |                 |

| Output endpoint-0 buffer            | ↑             |                 |

|                                     | FEF0          |                 |

| 5.1."                               | FEEF          |                 |

| Data buffers<br>(368 bytes)         | ↑ (           |                 |

|                                     | FD80          |                 |

| Tahlo | 2  | XDATA        | Snace |

|-------|----|--------------|-------|

| Iable | ∠. | <b>ADATA</b> | Space |

| Table 5. Memory-Mappeu Register Summary ( $\lambda DATA Range = Frou \rightarrow FFFF$ ) |           |                                                      |  |  |  |  |  |

|------------------------------------------------------------------------------------------|-----------|------------------------------------------------------|--|--|--|--|--|

| ADDRESS                                                                                  | REGISTER  | DESCRIPTION                                          |  |  |  |  |  |

| FFFF                                                                                     | FUNADR    | FUNADR: Function address register                    |  |  |  |  |  |

| FFFE                                                                                     | USBSTA    | SBSTA: USB status register                           |  |  |  |  |  |

| FFFD                                                                                     | USBMSK    | USBMSK: USB interrupt mask register                  |  |  |  |  |  |

| FFFC                                                                                     | USBCTL    | USBCTL: USB control register                         |  |  |  |  |  |

| 1                                                                                        | RESERVED  |                                                      |  |  |  |  |  |

| FFF6                                                                                     | VIDSTA    | VIDSTA: VID/PID status register                      |  |  |  |  |  |

| ↑                                                                                        | RESERVED  |                                                      |  |  |  |  |  |

| FFF3                                                                                     | I2CADR    | I2CADR: I <sup>2</sup> C address register            |  |  |  |  |  |

| FFF2                                                                                     | I2CDAI    | I2CDAI: I <sup>2</sup> C data-input register         |  |  |  |  |  |

| FFF1                                                                                     | I2CDAO    | I2CDAO: I <sup>2</sup> C data-output register        |  |  |  |  |  |

| FFF0                                                                                     | I2CSTA    | I2CSTA: I <sup>2</sup> C status and control register |  |  |  |  |  |

| <b>↑</b>                                                                                 | RESERVED  |                                                      |  |  |  |  |  |

| FF97                                                                                     | PUR3      | Port 3 pullup resistor register                      |  |  |  |  |  |

| FF96                                                                                     | PUR2      | Port 2 pullup resistor register                      |  |  |  |  |  |

| FF95                                                                                     | PUR1      | Port 1 pullup resistor register                      |  |  |  |  |  |

| FF94                                                                                     | PUR0      | Port 0 pullup resistor register                      |  |  |  |  |  |

| FF93                                                                                     | WDCSR     | VDCSR: Watchdog timer, control and status register   |  |  |  |  |  |

| FF92                                                                                     | VECINT    | VECINT: Vector interrupt register                    |  |  |  |  |  |

| FF91                                                                                     | RESERVED  |                                                      |  |  |  |  |  |

| FF90                                                                                     | MCNFG     | MCNFG: MCU configuration register                    |  |  |  |  |  |

| ↑                                                                                        | RESERVED  |                                                      |  |  |  |  |  |

| FF84                                                                                     | INTCFG    | INTCFG: Interrupt delay configuration register       |  |  |  |  |  |

| FF83                                                                                     | OEPBCNT_0 | OEPBCNT_0: Output endpoint-0 byte count register     |  |  |  |  |  |

| FF82                                                                                     | OEPCNFG_0 | OEPCNFG_0: Output endpoint-0 configuration register  |  |  |  |  |  |

| FF81                                                                                     | IEPBCNT_0 | IEPBCNT_0: Input endpoint-0 byte count register      |  |  |  |  |  |

| FF80                                                                                     | IEPCNFG_0 | IEPCNFG_0: Input endpoint-0 configuration register   |  |  |  |  |  |

## Table 3. Memory-Mapped Register Summary (XDATA Range = FF80 $\rightarrow$ FFFF)

SLLS466G - FEBRUARY 2001 - REVISED DECEMBER 2015

### 7.5.4 Endpoint Descriptor Block (EDB-1 to EDB-3)

Data transfers between USB, MCU and external devices are defined by an endpoint descriptor block (EDB). Four input and four output EDBs are provided. With the exception of EDB-0 (I/O endpoint 0), all EDBs are located in SRAM as shown in Table 4. Each EDB contains information describing the X and Y buffers. In addition, it provides general status information.

| ADDRESS  | SIZE      | DESCRIPTION                      |

|----------|-----------|----------------------------------|

| FF7F     |           |                                  |

| ↑        | 32 bytes  | RESERVED                         |

| FF60     |           |                                  |

| FF5F     |           |                                  |

| <b>↑</b> | 8 bytes   | Input endpoint 3: configuration  |

| FF58     |           |                                  |

| FF57     |           |                                  |

| ↑        | 8 bytes   | Input endpoint 2: configuration  |

| FF50     |           |                                  |

| FF4F     |           |                                  |

| ↑        | 8 bytes   | Input endpoint 1: configuration  |

| FF48     |           |                                  |

| FF47     |           |                                  |

| ↑        | 40 bytes  | RESERVED                         |

| FF20     |           |                                  |

| FF1F     |           |                                  |

| ↑        | 8 bytes   | Output endpoint 3: configuration |

| FF18     |           |                                  |

| FF17     |           |                                  |

| ↑        | 8 bytes   | Output endpoint 2: configuration |

| FF10     |           |                                  |

| FF0F     |           |                                  |

| ↑        | 8 bytes   | Output endpoint 1: configuration |

| FF08     |           |                                  |

| FF07     |           |                                  |

| ↑ (      | 8 bytes   | Setup packet block               |

| FF00     |           |                                  |

| FEFF     |           |                                  |

| ↑        | 8 bytes   | Input endpoint 0: buffer         |

| FEF8     |           |                                  |

| FEF7     |           |                                  |

| ↑        | 8 bytes   | Output endpoint 0: buffer        |

| FEF0     |           |                                  |

| FEEF     |           | Top of buffer space              |

| ↑        | 368 bytes | Buffer space                     |

| FD80     |           | Start of buffer space            |

Table 4. EDB and Buffer Allocations in XDATA

Table 5 lists the EDB entries for EDB-1 to EDB-3. EDB-0 registers are described separately.

| OFFSET | ENTRY NAME                               | DESCRIPTION                           |  |  |  |  |

|--------|------------------------------------------|---------------------------------------|--|--|--|--|

| 07     | EPSIZXY_n                                | I/O endpoint_n: X/Y buffer size       |  |  |  |  |

| 06     | 06 EPBCTY_n I/O endpoint_n: Y byte count |                                       |  |  |  |  |

| 05     | EPBBAY_n                                 | I/O endpoint_n: Y buffer base address |  |  |  |  |

| 04     | SPARE                                    | Not used                              |  |  |  |  |

| 03     | SPARE                                    | Not used                              |  |  |  |  |

| 02     | EPBCTX_n                                 | I/O endpoint_n: X byte count          |  |  |  |  |

| 01     | EPBBAX_n                                 | I/O endpoint_n: X buffer base address |  |  |  |  |

| 00     | EPCNF_n                                  | I/O endpoint_n: configuration         |  |  |  |  |

### Table 5. EDB Entries in RAM (n = 1 to 3)

### 7.5.4.1 OEPCNF\_n: Output Endpoint Configuration (n = 1 to 3)

| 7    | 6   | 5     | 4    | 3     | 2     | 1   | 0   |

|------|-----|-------|------|-------|-------|-----|-----|

| UBME | ISO | TOGLE | DBUF | STALL | USBIE | RSV | RSV |

| R/W  | R/W | R/W   | R/W  | R/W   | R/W   | R/O | R/O |

| BIT | NAME  | RESET  |               | FUNCTION                                                                                                              |          |

|-----|-------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------|----------|

| 1–0 | RSV   | 0      | Reserved      |                                                                                                                       |          |

|     |       |        | USB interrupt | enable on transaction completion. Set/cleared by MCU.                                                                 |          |

| 2   | USBIE | х      | USBIE = 0     | No interrupt                                                                                                          |          |

|     |       |        | USBIE = 1     | Interrupt on transaction completion                                                                                   |          |

|     |       |        | USB stall con | dition indication. Set/cleared by MCU.                                                                                |          |

| 3   | STALL | TALL 0 | 0             | STALL = 0                                                                                                             | No stall |

|     | OTALL |        | STALL = 1     | USB stall condition. If set by MCU, a STALL handshake is initiated and the bit is cleared by the MCU.                 |          |

|     |       |        | Double buffer | enable. Set/cleared by MCU.                                                                                           |          |

| 4   | DBUF  | х      | DBUF = 0      | Primary buffer only (X-buffer only)                                                                                   |          |

|     |       |        | DBUF = 1      | Toggle bit selects buffer                                                                                             |          |

| 5   | TOGLE | х      | USB toggle bi | t. This bit reflects the toggle sequence bit of DATA0, DATA1.                                                         |          |

| 6   | ISO   | х      | ISO = 0       | Non-isochronous transfer. This bit must be cleared by the MCU because only non-<br>isochronous transfer is supported. |          |

|     |       |        | UBM enable/c  | lisable bit. Set/cleared by the MCU.                                                                                  |          |

| 7   | UBME  | х      | UBME = 0      | UBM cannot use this endpoint.                                                                                         |          |

|     |       |        | UBME = 1      | UBM can use this endpoint.                                                                                            |          |

STRUMENTS

XAS

### 7.5.4.2 OEPBBAX\_n: Output Endpoint X-Buffer Base Address (n = 1 to 3)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| A10 | A9  | A8  | A7  | A6  | A5  | A4  | A3  |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

**TUSB3210**

| BIT | NAME    | RESET | FUNCTION                                                                                                                                                                                                                                                                    |

|-----|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 | A[10:3] | x     | A[10:3] of X-buffer base address (padded with 3 LSB of zeros for a total of 11 bits). This value is set by the MCU. UBM or DMA uses this value as the start address of a given transaction. Furthermore, UBM or DMA does not change this value at the end of a transaction. |

### 7.5.4.3 OEPBCTX\_n: Output Endpoint X-Byte Count (n = 1 to 3)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| NAK | C6  | C5  | C4  | C3  | C2  | C1  | C0  |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| BIT | NAME   | RESET |                            | FUNCTION                                                            |

|-----|--------|-------|----------------------------|---------------------------------------------------------------------|

| 6–0 | C[6:0] | x     | 011 1111b –<br>100 0000b – |                                                                     |

| 7   | NAK    | v     | NAK = 0                    | No valid data in buffer. Ready for host-out.                        |

|     | NAK    | х     | NAK = 1                    | Buffer contains a valid packet from host (host-out request is NAK). |

### 7.5.4.4 OEPBBAY\_n: Output Endpoint Y-Buffer Base Address (n = 1 to 3)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| A10 | A9  | A8  | A7  | A6  | A5  | A4  | A3  |

| R/W |

| BIT | NAME    | RESET | FUNCTION                                                                                                                                                                                                                                                                    |

|-----|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–0 | A[10:3] |       | A[10:3] of Y-buffer base address (padded with 3 LSB of zeros for a total of 11 bits). This value is set by the MCU. UBM or DMA uses this value as the start address of a given transaction. Furthermore, UBM or DMA does not change this value at the end of a transaction. |

### 7.5.4.5 OEPBCTY\_n: Output Endpoint Y-Byte Count (n = 1 to 3)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| NAK | C6  | C5  | C4  | C3  | C2  | C1  | C0  |

| R/W |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

| BIT | NAME   | RESET |                                                                                                                                                                                                                                | FUNCTION                                                 |

|-----|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 6–0 | C[6:0] | x     | Y-Buffer Byte count:<br>$000\ 0000b \rightarrow Count = 000\ 0001b \rightarrow Count = 000\ 0001b \rightarrow Count = 000\ 0000b \rightarrow Count = 000\ 0000b \rightarrow Count = 000\ 0000b \rightarrow Count = 000\ 0000b$ | byte<br>33 bytes                                         |

| 7   | NAK    |       | NAK = 0 No valid d                                                                                                                                                                                                             | ata in buffer. Ready for host-out                        |

| /   | NAK    | х     | NAK = 1 Buffer con                                                                                                                                                                                                             | ains a valid packet from host (host-out request is NAK). |

## 7.5.4.6 OEPSIZXY\_n: Output Endpoint X-/Y-Buffer Size (n = 1 to 3)

| 7   | 6   | 5          | 4   | 3   | 2   | 1   | 0   |

|-----|-----|------------|-----|-----|-----|-----|-----|

| RSV | S6  | <b>S</b> 5 | S4  | S3  | S2  | S1  | S0  |

| R/O | R/W | R/W        | R/W | R/W | R/W | R/W | R/W |

| BIT | NAME   | RESET | FUNCTION                                                                                                |

|-----|--------|-------|---------------------------------------------------------------------------------------------------------|

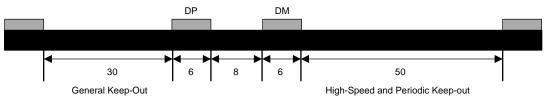

| 6–0 | S[6:0] | x     | X- and Y-Buffer size:<br>$000\ 0000b \rightarrow Count = 0$<br>$000\ 0001b \rightarrow Count = 1\ byte$ |