### **FEATURES**

- D4 SF, ESF (including HDLC Link support), and transparent framing modes

- Encodes/decodes AMI/B8ZS and forced ones density line codes

- Fractional T1 gapped clock

- Monitor function for frame pulse, clock and data

- Two-frame slip buffers in both receive and transmit directions

- Supports channel associated and robbed-bit signaling (enabled or processor forced on a per DS0 basis)

- Detects and forces Yellow and AIS alarms; detects OOF, Severely Errored Frame, and Change of Frame Alignment, detects AIS-CI

- · Detects, counts and forces line code errors (BPVs and excess zeros), CRC errors (ESF only), and frame bit errors

- Motorola/Intel compatible microprocessor interface

- · One-second interrupt input latches counter values and line events into shadow registers

- Local, line remote, payload remote and DS0 channel loopbacks, per DS0 channel inversion

- · Processor forcing/monitoring of DS0s for maintenance purposes

- Boundary scan capability (IEEE 1149.1)

- Single +3.3 volt or +5.0 volt power supply

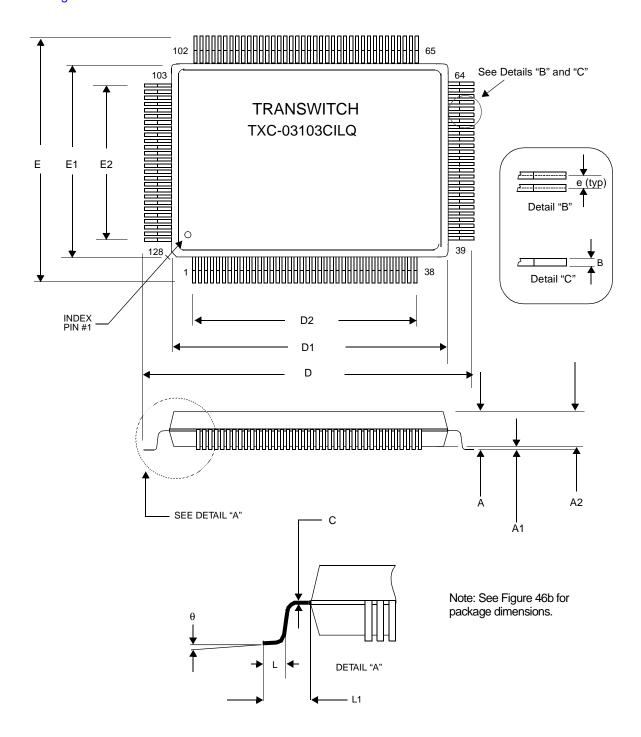

- 128-pin low profile plastic quad flat package

#### DESCRIPTION

The QT1F-Plus (TXC-03103C) is a four-channel DS1 (T1, 1.544 Mbit/s) framer designed with extended features for voice and data communications applications. AMI, B8ZS, and NRZ line codes are supported with full alarm detection and generation per ANSI T1M1.3. The transmit and receive sections of each of the four framers are independent, with individual slip buffers to allow operation in a wide range of switching and transmission products. D4 SF and ESF modes are provided per ANSI T1.403-1998 and AT&T PUB 62411, with per DS0 signaling and DS0 data access and control via a Motorola/Intel-compatible microprocessor interface. For ESF applications, each framer supplies a full duplex HDLC/bit-oriented message controller, supporting back-to-back FDL messages in addition to onboard latching of all required performance parameters; minimal software overhead is required to support either ANSI T1.403-1998 or AT&T PUB 54016 protocols. Diagnostic, test, and maintenance functions are provided, including four loopback modes and boundary scan (IEEE 1149.1).

### APPLICATIONS

- SONET/SDH terminal or add/drop multiplexers supporting DS1 byte synchronous operation

- DCS, digital central office or remote digital terminals

- T1 multiplexers

- T1 and fractional T1 CSUs

- ATM products with integrated DS1 interfaces

- LAN routers with integrated DS1 interfaces

- Multichannel DS1 test equipment

- Internet Access Equipment with T1 and Fractional T1 Interfaces

U.S. Patent No. 5,615,237 and 6,456,595 Copyright © 2004 TranSwitch Corporation PHAST, TEMx28, TranSwitch and TXC are registered trademarks of TranSwitch Corporation MVIP is a registered trademark of GO-MVIP, Inc.

Document Number: PRELIMINARY TXC-03103C-MB, Ed. 3

October 2004

### TABLE OF CONTENTS

| Section                                                | Page |

|--------------------------------------------------------|------|

| Quad T1 Framer-Plus Features                           | 4    |

| Block Diagram                                          | 6    |

| Block Diagram Description                              | 7    |

| Pin Diagram                                            | 10   |

| Pin Descriptions                                       | 11   |

| Absolute Maximum Ratings and Environmental Limitations | 20   |

| Thermal Characteristics                                | 20   |

| Power Requirements                                     | 21   |

| Input, Output and Input/Output Parameters              | 22   |

| Parameters for +3.3 Volts Supply Voltage               | 22   |

| Parameters for +5.0 Volts Supply Voltage               | 24   |

| Operation                                              | 49   |

| Line Interface Selection                               | 49   |

| Line Interface Control                                 | 51   |

| Monitor Mode                                           | 52   |

| System Interface                                       | 52   |

| Transmission Mode                                      | 53   |

| MVIP Mode                                              | 57   |

| Fractional T1 Mode                                     | 59   |

| Per DS0 Inversion Mode                                 | 60   |

| Framing                                                | 60   |

| Signaling                                              | 68   |

| Clocking and Synchronization                           | 71   |

| AIS Detection and Generation                           | 73   |

| ANSI RAI - CI Detector                                 | 74   |

| HDLC Channel                                           | 74   |

| Alarms                                                 | 77   |

| Maintenance                                            | 79   |

| Boundary Scan                                          | 82   |

| Reset Procedure                                        | 88   |

| Memory Map                                             | 89   |

| Per Channel Control and Status Indication Registers    | 91   |

| Memory Map Descriptions                                | 98   |

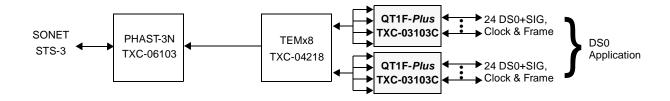

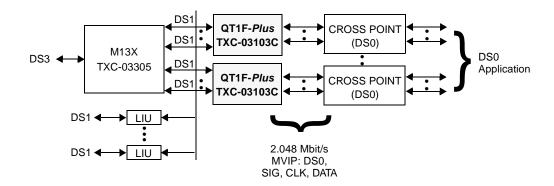

| Application Diagram                                    | 148  |

| Package Information                                    | 149  |

| Ordering Information                                   |      |

| Related Products                                       | 151  |

| Standards Documentation Sources                        | 152  |

| List of Data Sheet Changes                             |      |

|                                                        |      |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at <a href="www.transwitch.com">www.transwitch.com</a>. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# **LIST OF FIGURES**

| Figure |                                                                           | Page |

|--------|---------------------------------------------------------------------------|------|

| 1.     | QT1F-Plus TXC-03103C Block Diagram                                        | 6    |

| 2.     | QT1F-Plus TXC-03103C Pin Diagram                                          | 10   |

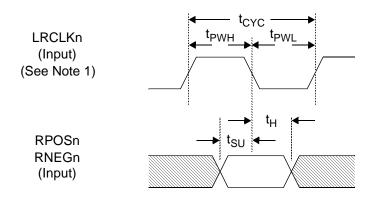

| 3.     | Dual Unipolar (Rail) Receive Interface Timing                             | 26   |

| 4.     | Dual Unipolar (Rail) Transmit Interface Timing                            | 27   |

| 5.     | NRZ Receive Interface Timing (External Transceiver)                       | 28   |

| 6.     | NRZ Transmit Interface Timing (External Transceiver)                      | 29   |

| 7.     | NRZ Receive Interface Timing (Fast Sync Mode)                             | 30   |

| 8.     | NRZ Transmit Interface Timing (Fast Sync Mode)                            | 31   |

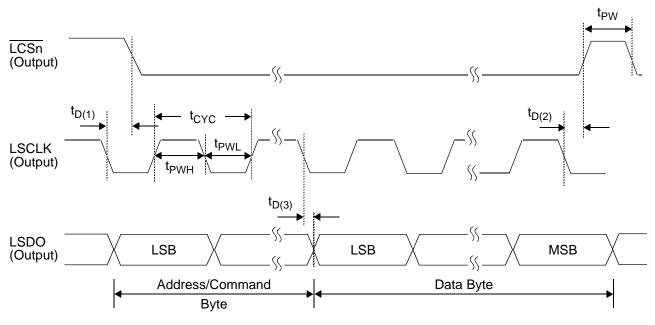

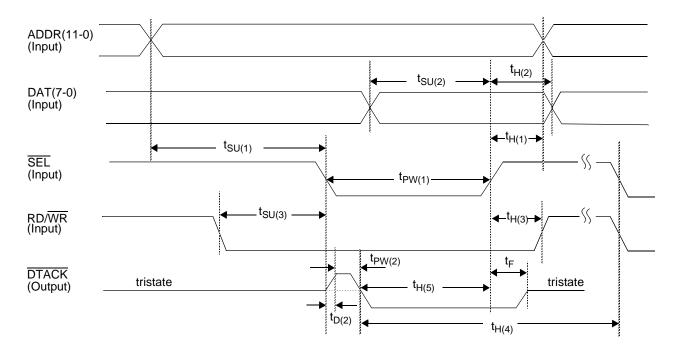

| 9.     | Serial Port Write Timing                                                  | 32   |

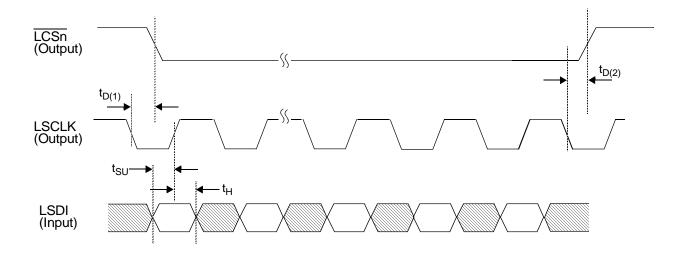

| 10.    | Serial Port Read Timing                                                   | 33   |

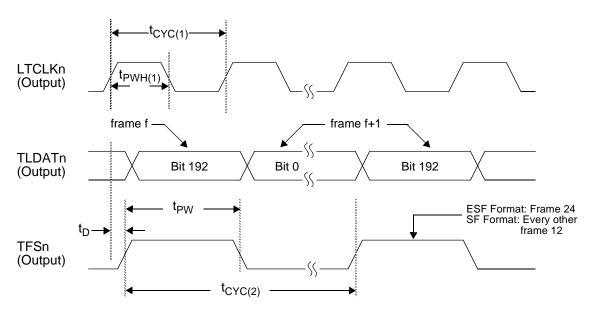

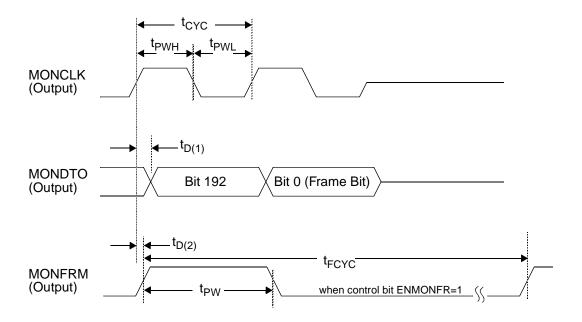

| 11.    | Monitor Mode Timing                                                       | 34   |

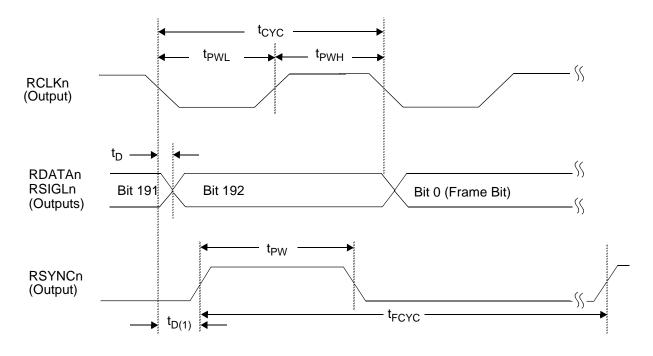

| 12.    | Receive Highway Timing - Transmission Mode (Recovered Receive Line Clock) | 35   |

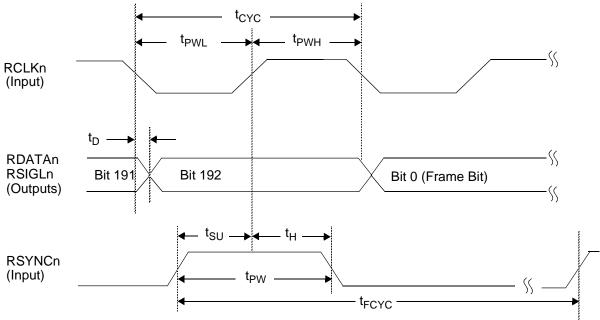

| 13.    | Receive Highway Timing - Transmission Mode (System Clock)                 | 36   |

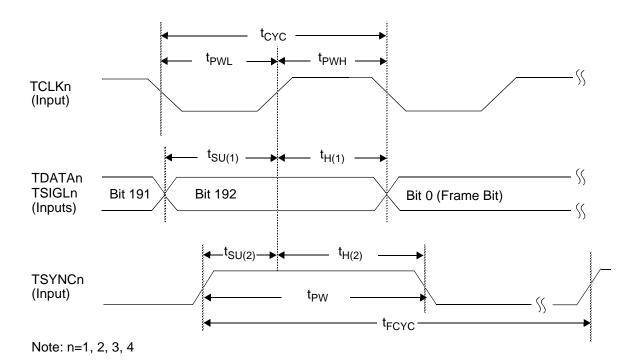

| 14.    | Transmit Highway Timing - Transmission Mode                               | 37   |

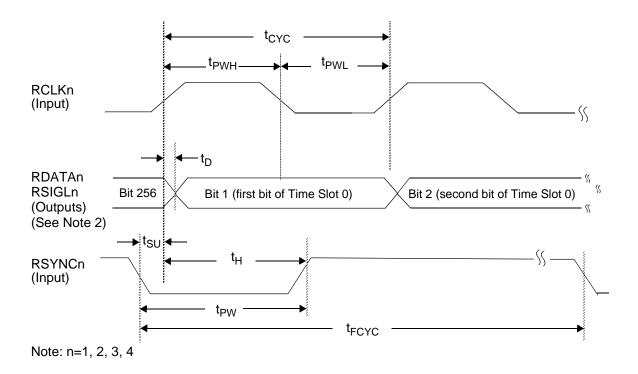

| 15.    | Receive Highway Timing - MVIP Mode                                        | 38   |

| 16.    | Transmit Highway Timing - MVIP Mode                                       | 39   |

| 17.    | Receive Highway Timing - Fractional T1 Gapped Clock (Transmission Mode)   |      |

| 18.    | Transmit Highway Timing - Fractional T1 Gapped Clock (Transmission Mode)  |      |

| 19.    | Shadow Register Timing                                                    | 42   |

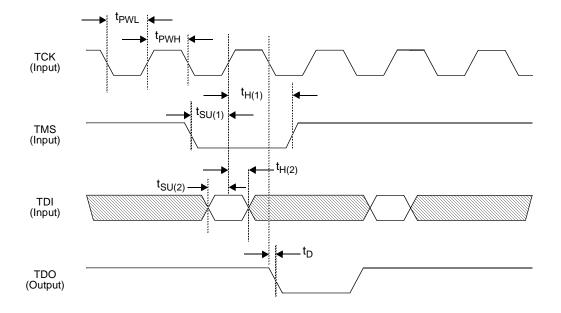

| 20.    | Boundary Scan Timing                                                      | 43   |

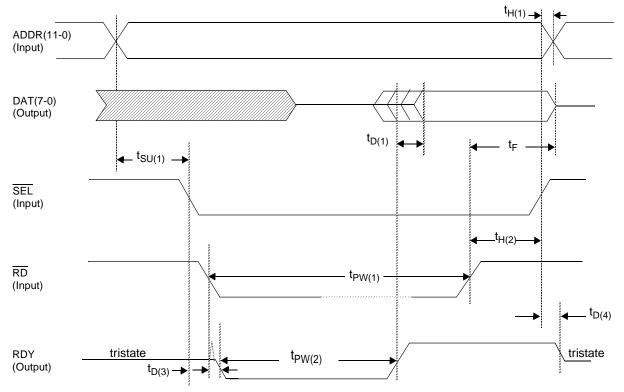

| 21.    | Intel Microprocessor Read Cycle Timing                                    |      |

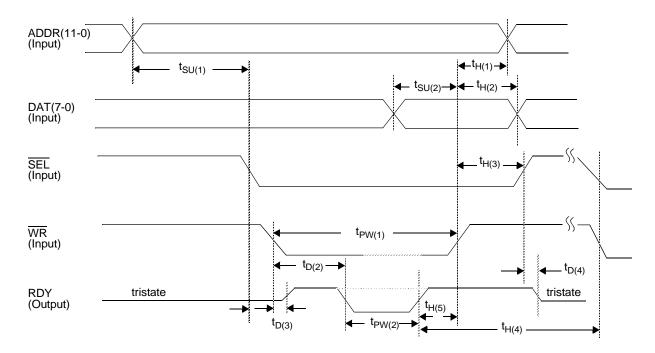

| 22.    | Intel Microprocessor Write Cycle Timing                                   | 45   |

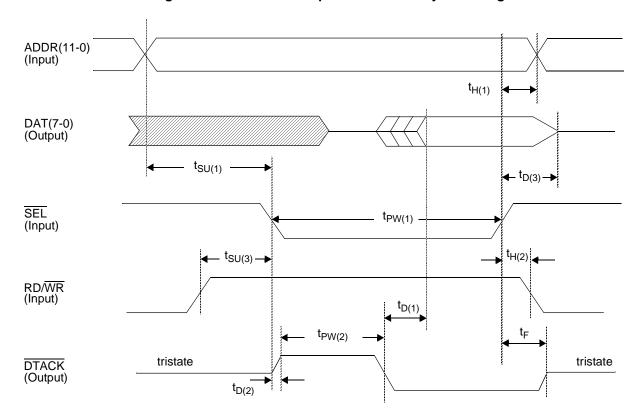

| 23.    | Motorola Microprocessor Read Cycle Timing                                 | 46   |

| 24.    | Motorola Microprocessor Write Cycle Timing                                | 47   |

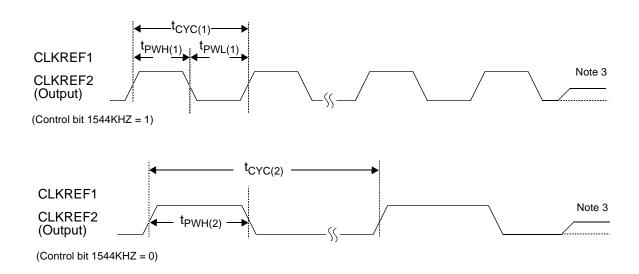

| 25.    | Clock Reference Timing                                                    |      |

| 26.    | Line Interface For Dual Unipolar Mode                                     |      |

| 27.    | Line Interface For NRZ Mode                                               |      |

| 28.    | Transceiver Serial Input/Output Timing                                    |      |

| 29.    | Transmit Highway - Transmission Mode                                      |      |

| 30.    | Receive Highway - Transmission Mode                                       |      |

| 31.    | Transmit Highway - MVIP Mode                                              |      |

| 32.    | Receive Highway - MVIP Mode                                               | 59   |

| 33.    | D4 SF Framing Structure                                                   |      |

| 34.    | ESF Framing Structure                                                     | 62   |

| 35.    | Transmit Slip Buffer                                                      | 66   |

| 36.    | Receive Slip Buffer                                                       | 67   |

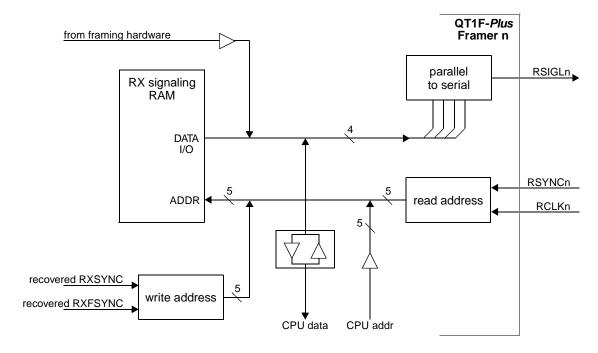

| 37.    | Receive Signaling Buffer                                                  |      |

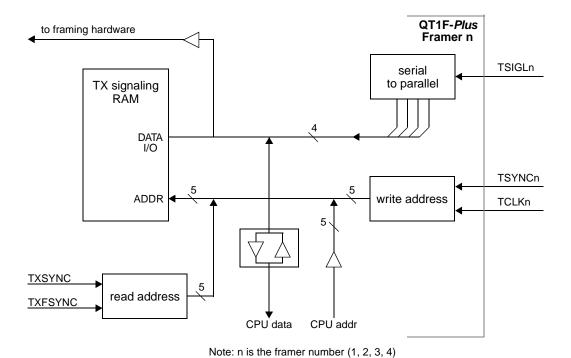

| 38.    | Transmit Signaling Buffer                                                 | 70   |

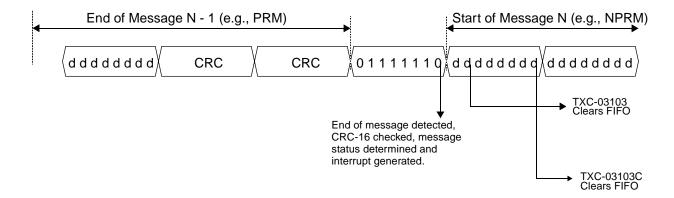

| 39.    | HDLC Format                                                               | 74   |

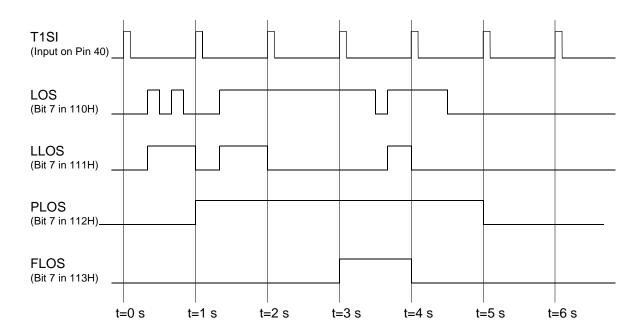

| 40.    | Shadow Register Operation                                                 | 79   |

| 41.    | Local Loopback                                                            | 80   |

| 42.    | Remote Line Loopback                                                      | 80   |

| 43.    | Payload Remote Loopback                                                   |      |

| 44.    | Boundary Scan Schematic                                                   |      |

| 45.    | QT1F-Plus TXC-03103C Application                                          |      |

| 46.    | QT1F-Plus TXC-03103C 128-Pin Package Diagram                              |      |

| 47.    | QT1F-Plus TXC-03103C 128-Pin Package Dimensions                           |      |

### **QUAD T1 FRAMER-PLUS FEATURES**

The Quad T1 Framer-*Plus* device (QT1F-*Plus*, TXC-03103C, see Note on next page) is a highly-featured four-channel DS1 (T1) framer for use in a wide variety of interface, transmission and switching applications. Four independent DS1 framers are provided in a single monolithic VLSI device using sub-micron CMOS technology. Powered from a single +5.0 volt supply, the four framers dissipate less than a watt typically. Powered from a single +3.3 volt supply, the four framers dissipate less than one third of a watt typically. The QT1F-*Plus* is provided in a rectangular 128-pin low profile plastic quad flat package. Its ambient operating temperature range extends from -40 °C to +85 °C.

The QT1F-Plus device has been designed to meet the latest industry standards, namely:

- ANSI T1.403-1998 and T1M1.3-005R1 (April 1993)

- Bellcore GR-499-CORE (Issue 1)

- AT&T Pub. 62411 (Dec. 1990) and Pub. 54016

- IEEE 1149.1- 1990, -1994

- MVIP (Multi-Vendor Integration Protocol)

The following features are independently selectable for each of the four DS1 framers:

#### Framing Modes:

- D4 SF (Superframe Format) programmable for Fs, Ft or both frame bits

- ESF (Extended Superframe Format) FPS bits with or without a valid CRC-6

- Unframed (bypass)

- · T1DM and other SF modes with external logic

#### Line Codes:

- AMI

- B8ZS

- · AMI with forced ones density

- NRZ (bypass)

- Selectable polarity (NRZ) and clock edges

#### Signaling:

- A, AB, 9-state AB signaling for ANSI T.403 Rob and limited support for SLC-96 applications (SF)

- A, AB, ABCD (ESF)

- Per DS0 enable with microprocessor read and substitution in both receive and transmit directions for call control and trunk conditioning

- · Signaling freeze on LOS

#### **Clock Management:**

- Flexible receive and transmit clock selection, including local oscillator

- Two frame slip buffers for each of receive and transmit paths, with independent bypass

- · System side and line side clocks on receive and transmit, each independent

#### Alarms and Errors:

- Detect and force Yellow and blue (AIS) alarms, detect AIS-CI signature

- Detect Out Of Frame, Loss Of Signal, Severely Errored Frame, Change of Frame Alignment, Transmit Slips and Receive Slips

- Detect, count and force CRC errors (ESF only), frame bit errors and line code errors (bipolar violations, with or without excessive zeros)

- · Detect and force frame slips

#### Fractional T1:

- · Gapped Clock programmed DS0 channels

- · Receive and Transmit gapped clocks with selection and direction independent

#### **DS0 Control:**

- Per DS0 enable (independent receive and transmit) with microprocessor read and substitution in both receive and transmit directions

- Per DS0 inversion in transmit and receive directions (after slip buffer) in both Transmission and MVIP Modes.

#### Maintenance:

- · Loopbacks line remote, local, payload remote (ESF only) and DS0 channel

- · Detect and transmit SF loop-up and loop-down codes

- Full duplex HDLC link controller with bit-oriented code support for HDLC link and 16-byte receive and transmit FIFOs, back-to-back message support

- Boundary Scan (IEEE 1149.1) for input/output pin monitoring

### Microprocessor Interface:

- Eight-bit status register for LOS, AIS, OOF, YEL, CFA, SEF, TXSLIP and RXSLIP

- · Eight-bit latched event register and interrupt mask register

- CRC (ESF only), code violation and frame bit error counters

- Shadow registers and counters

- · Full control of framing, alarm generation and propagation, codec features

- HDLC link control, signaling access/control, DS0 access/control

- · Reset, resync, slip buffer and frame bit access

#### The following features are only selectable for the four framers as a group:

- Transmission Mode ("off line" framing) or MVIP Mode system interfaces

- Serial port to read/write control up to four line interface transceivers, or selection of one of four DS1 line interfaces (receive or transmit) to monitor clock, frame pulse and data

- Microprocessor global reset, masks, polling registers, interrupt polarity and latch edge control

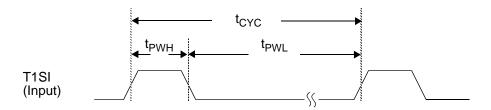

- Two reference clock outputs at 8kHz or 1544 kHz with freeze on LOS

- IEEE 1149.1 boundary scan

- Motorola or Intel microprocessor access with separate address and data buses

- · Ability to tristate all outputs for in-circuit testing

- Ability to place line side transmit clock and data to logic low for protection switching

- Synchronization start position is programmable to any receive or transmit bit position on the system side

- · External shadow register clock input

- Pseudo-Random Binary Sequence (PRBS) generator and analyzer

#### Enhancements over the Quad T1 Framer-Plus TXC-03103:

- SF mode 9-state signaling for ANSI T-403 Rob and limited support for SLC-96 applications

- Per DS0 inversion in Transmission and MVIP modes

- Frame bits available in MVIP mode, and supports bypass FDL feature in MVIP mode

- AIS-CI detector

- FDL back-to-back message support

#### **BLOCK DIAGRAM**

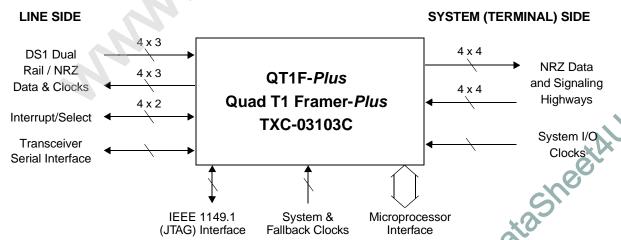

Figure 1. QT1F-Plus TXC-03103C Block Diagram

QT1F-Plus TXC-03103C

### **BLOCK DIAGRAM DESCRIPTION**

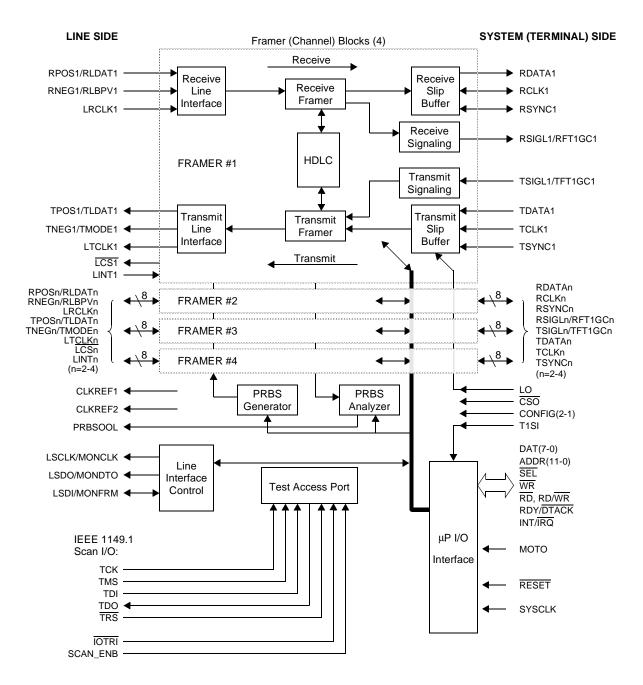

A simplified block diagram of the Quad T1 Framer-Plus (QT1F-Plus) is shown in Figure 1. The QT1F-Plus consists of the following major blocks: four Framer blocks, Line Interface Control, PRBS Generator, PRBS Analyzer, Microprocessor Input/Output Interface, and Test Access Port.

Each of the four identical Framer blocks consists of the following blocks: Receive and Transmit Line Interface blocks, Receive and Transmit Framer blocks, HDLC block, Receive and Transmit Slip Buffer blocks, and Receive and Transmit Signaling blocks.

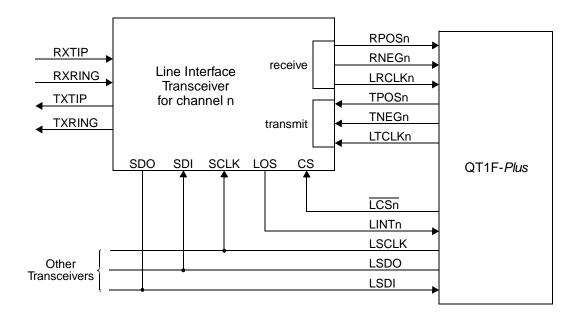

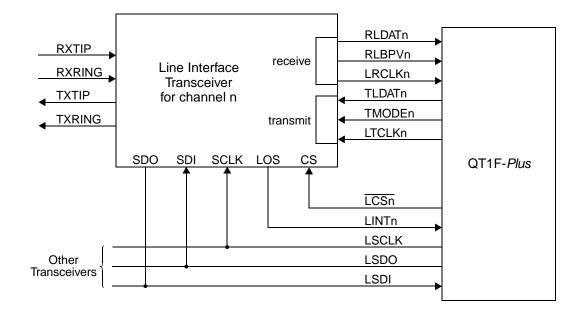

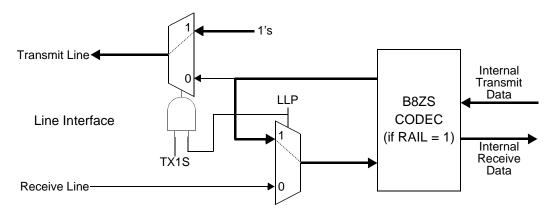

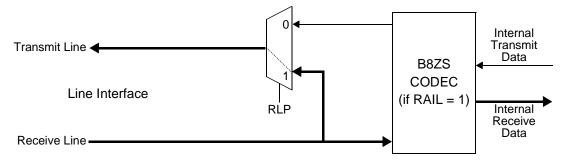

The Receive and Transmit Line Interface blocks connect each of the four framers to an external line interface transceiver, which performs the LIU and clock recovery functions. The interface to the external line interface transceiver can be configured for two interface modes: a dual unipolar (rail) interface or a NRZ interface.

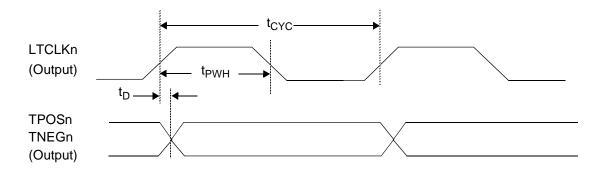

When the dual unipolar interface mode is selected, input data from the external line interface transceiver is clocked into the QT1F-*Plus* on pins RPOSn and RNEGn using the recovered receive clock present on the LRCLKn input pin (where n=1-4 identifies one of the four framers). In the transmit direction, unipolar data is clocked out of the QT1F-*Plus* on pins TPOSn and TNEGn by the transmit line clock present on the LTCLKn output pin. For reduced power dissipation in protection switching applications, the LTCLKn, TPOSn, and TNEGn pins for the four framers may be forced low, by placing a low on the CSO pin. Control bits are provided in the memory map which enable the unipolar data to be clocked in and out of the QT1F-*Plus* on either edge of the clocks. For the dual unipolar interface mode, the QT1F-*Plus* provides either a Bipolar with Eight Zero Substitution (B8ZS), or an Alternate Mark Inversion (AMI), coder and decoder function, and Loss Of Signal detection. The Loss Of Signal detector meets the requirements specified in the ANSI T1M1.3 document listed above in the QT1F-*Plus* Features section. A sixteen-bit performance counter is provided for each framer, for counting B8ZS coding violation errors. An option is provided to also count excessive zeros in the coding violations counter.

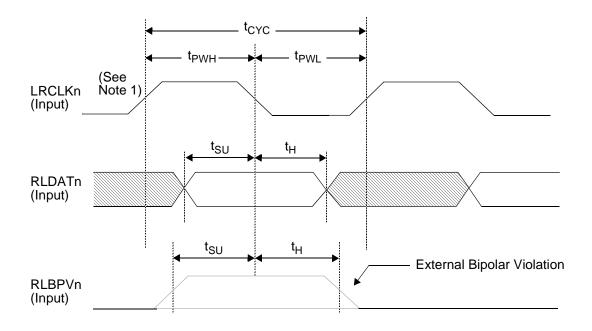

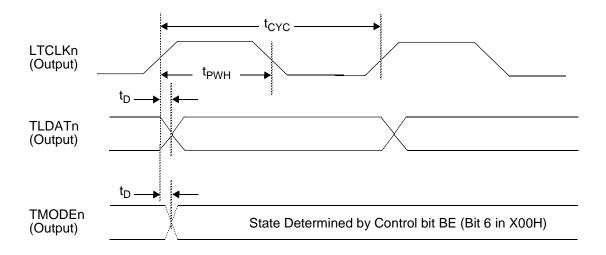

When the NRZ interface mode is selected, NRZ data is clocked in at the RLDATn pin by the recovered received clock present on the LRCLKn pin. The NRZ data is clocked out of the QT1F-Plus on the TLDATn pin by the transmit system clock present on the LTCLKn pin. Control bits are provided in the memory map which enable the NRZ data to be clocked in and out of the QT1F-Plus on either edge of the clocks. In NRZ interface mode, the B8ZS or AMI coder and decoder functions are bypassed. However, bipolar violations which are detected in the external line interface transceiver may be clocked into the QT1F-Plus on the RLBPVn pin and counted in the associated 16-bit coding violation performance counter. The Remote Line Loopback function for each framer is also implemented in the Line Interface blocks.

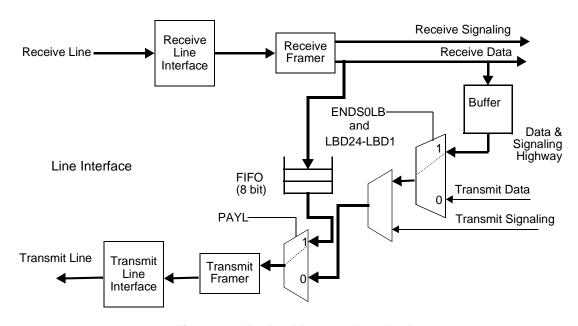

The Receive Framer block for each framer performs frame synchronization alignment. The frame synchronization circuit has framing option for the SF and ESF formats. For the SF format, Fs or Ft, or Fs and Ft bits can be used for frame alignment. For the ESF format, FPS, or FPS and a valid CRC-6, may be used. The frame synchronizing circuit meets the framing requirements specified in the ANSI documents. The Out Of Frame alarm criteria can be programmed to use 2 out of 4, 5, or 6 framing bits in error. Framing bit errors and CRC-6 errors are counted in performance counters. The Receive Framer block also monitors and detects the Yellow alarm for either the SF or ESF formats. A non-framing mode can be enabled when the QT1F-*Plus* is configured in the Transmission Modes. The non-framing mode bypasses the Receive Framer block and the Receive Slip Buffer block.

When frame alignment is acquired, the signaling bits are forwarded to the Receive Signaling block for buffering, microprocessor access, and formatting into the signaling highway data stream.

### QT1F-Plus TXC-03103C

#### **DATA SHEET**

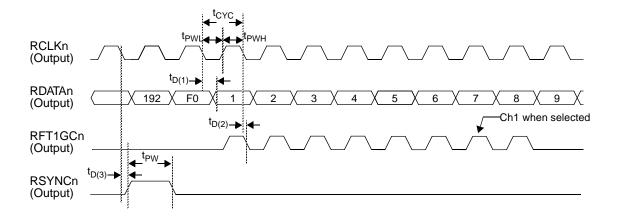

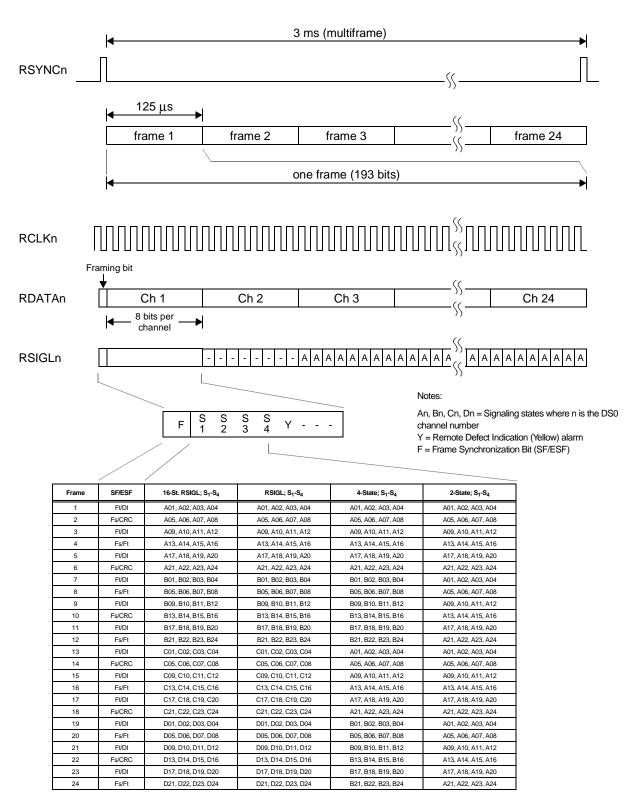

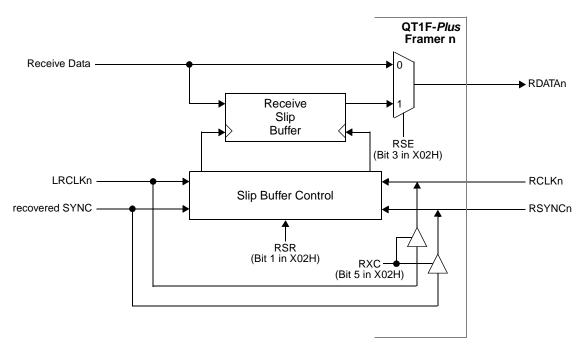

Each Receive Slip Buffer block controls time slot access and retiming for framer n by using a two-frame receive slip buffer that can be optionally bypassed in the Transmission Mode. When the receive slip buffer is enabled, received time slots are written into the buffer by recovered receive clock LRCLKn, and read out as data (RDATAn) from the receive slip buffer by the system input clock RCLKn. A phase shift between the two clocks is detected in this block and a deletion or repetition of one frame of data (24 DS0 channels) is provided when the buffer reaches an almost full or almost empty condition, respectively. Microprocessor access to the read and write pointers is also provided. The framing bits and signaling bits are not affected by a slip. Slip alarm indications are provided for the microprocessor. The receive slip buffer may be recentered by the microprocessor, or automatically. Individual time slots can be accessed by the microprocessor for the insertion of system idle or out of service codes. When the receive slip buffer is bypassed, the receive clock (RCLKn) and data (RDATAn) are provided as outputs, along with a receive sync signal (RSYNCn).

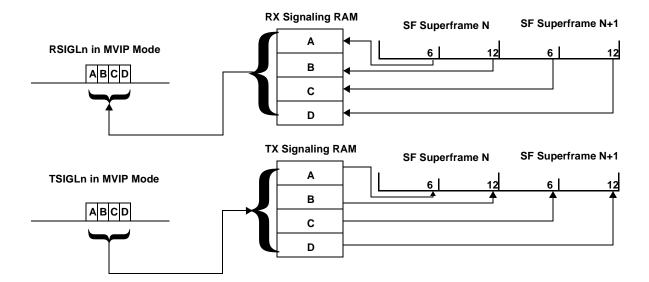

For 2, 4 or 16-state signaling (robbed-bit signaling), a 96-bit signaling buffer is used to store the signaling bits which have been extracted by the Receive Framer. The signaling buffer may be read, frozen and written to by the microprocessor. This feature permits both signaling to or from the microprocessor (call control) as well as trunk conditioning under control of the microprocessor. If signaling is disabled for a particular channel, the ABCD signaling bits for that time slot will be frozen in their present states. When a loss of signal or an out of frame condition is detected, the signaling bits are also automatically frozen in their present states. The signaling bit states are held until framing has been recovered. Nine-state AB signaling for ANSI T.403 Rob is also supported.

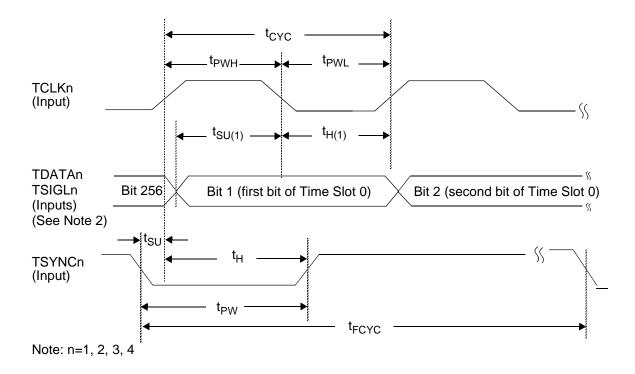

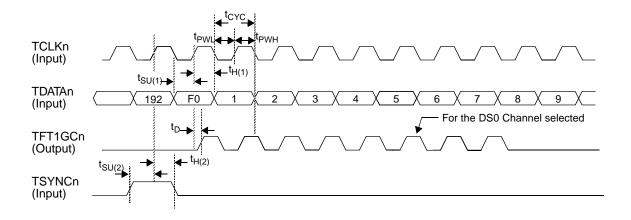

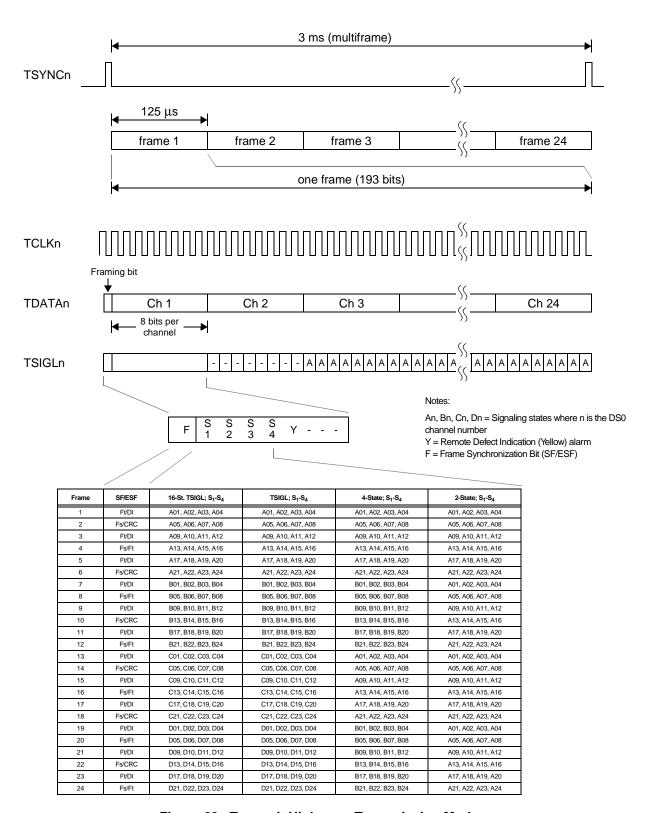

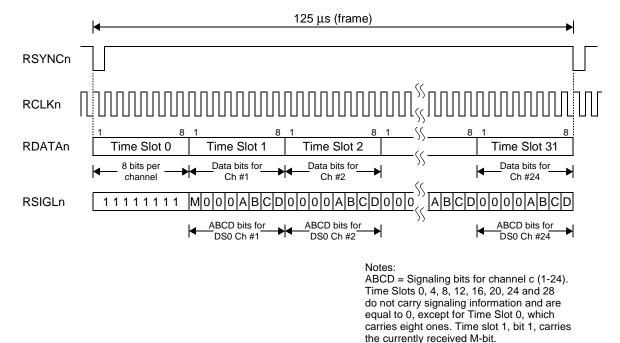

On the terminal side, the system interface interconnects the four framers with the system. For each framer there is a separate receive and transmit highway for the Transmission and MVIP interface modes of operation. The receive highway consists of a data bus (RDATAn), a signaling bus (RSIGLn), a clock (RCLKn), and a synchronization signal (RSYNCn). The transmit highway consists of a data bus (TDATAn), a signaling bus (TSIGLn), a clock (TCLKn), and a synchronization signal (TSYNCn). In the Transmission Mode, the system interface operates at 1.544 MHz, with channels in the data highway, and signaling and alarms on the signaling highway. The receive and transmit system interfaces are synchronized by multiframe pulses that occur at 3-millisecond intervals. Twenty-four frames are sent on the data and signaling highways within the 3-millisecond period, with each of the twenty-four frames consisting of 193 bits (24 DS0 channels plus the framing bit), which correspond to a DS1 frame. The receive and transmit slip buffers can be individually bypassed in this mode.

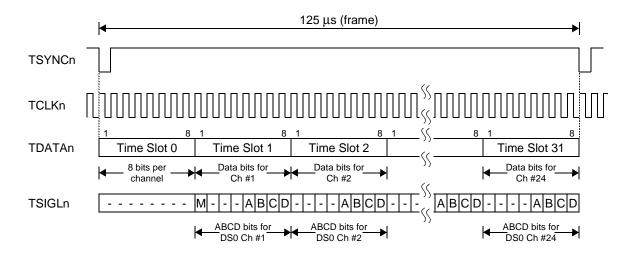

When the MVIP Mode is selected, the system interface also consists of receive and transmit data highways. However, the receive and transmit system interfaces are synchronized by pulses occurring at 125-microsecond intervals in this mode. The receive and transmit slip buffers must always be enabled in this mode. Each frame consists of 32 time slots which carry the DS0 channels in defined time slots on the data highway. The signaling highway also carries 32 time slots, which contain the signaling states for each channel.

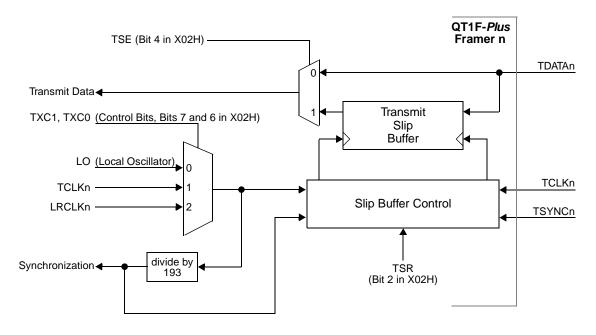

A transmit slip buffer is provided to absorb low speed jitter in the transmit data. Each Transmit Slip Buffer block controls time slot access and retiming for the framer by using a two-frame buffer that can be optionally bypassed in the Transmission Mode. When the transmit slip buffer is enabled, transmit time slots are written into the buffer by the transmit system clock (TCLKn), and they are read out from the buffer by the receive clock (LRCLKn), local oscillator (LO), or transmit system clock (TCLKn). A phase shift between the two clocks is detected in this block, and a deletion or repetition of one frame of data (i.e., 24 DS0 channels) is provided when the buffer reaches an almost full or almost empty condition, respectively. Microprocessor access to the read and write pointers is also provided. Buffer alarm indications are also provided. The slip buffer may be recentered by the microprocessor, or automatically. Individual time slots can be accessed by the microprocessor for the insertion of system idle or out of service codes.

The Transmit Framer block forms the frame (SF or ESF formats) with DS0 channels read from the Transmit Slip Buffer block, and signaling information from the Transmit Signaling block. The HDLC bits (D-bits) in the ESF format can be inserted from the HDLC block or from the system interface (in Transmission Mode only). A 16-bit code word message provided by the microprocessor can also be inserted into the data bits. The CRC-6 is calculated and inserted for the ESF format. The Yellow Alarm Indication is inserted by the microprocessor, or via the signaling highway (TSIGLn). Yellow Alarm for SF format, and loop-up and loop-down codes, can be inserted, if selected. A single frame bit error, or CRC-6 error, can be generated for test purposes. The Transmit Framer and Transmit Slip Buffer can be bypassed if the unframed mode of operation is selected in the Transmission Mode.

QT1F-Plus TXC-03103C

Each framer has a full duplex HDLC link controller. The HDLC link controller can be configured to send and receive messages using the 4 kbit/s D-Bits in the ESF format. A 16-byte FIFO is provided in each direction. Interrupt and status alarm support is provided to facilitate FIFO servicing for long messages. The HDLC link controller supports zero bit stuffing/destuffing, ITU-T CRC generation/checking, flag generation/detection, abort generation/detection, start of frame detection, end of frame detection, and FIFO underflows and overflows.

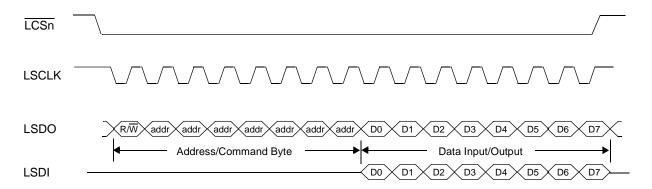

The Line Interface Control block provides a serial port for communicating with an external line interface transceiver. This allows the system microprocessor to control the transceiver through the QT1F-Plus. The interface consists of a data output pin (LSDO), clock output pin (LSCLK), and a data input pin (LSDI). These signals are shared between all of the transceivers. Each transceiver is selected by the QT1F-Plus, using individual chip select output signals (LCSn). In addition, a general purpose input pin (LINTn) can be used to generate a maskable interrupt.

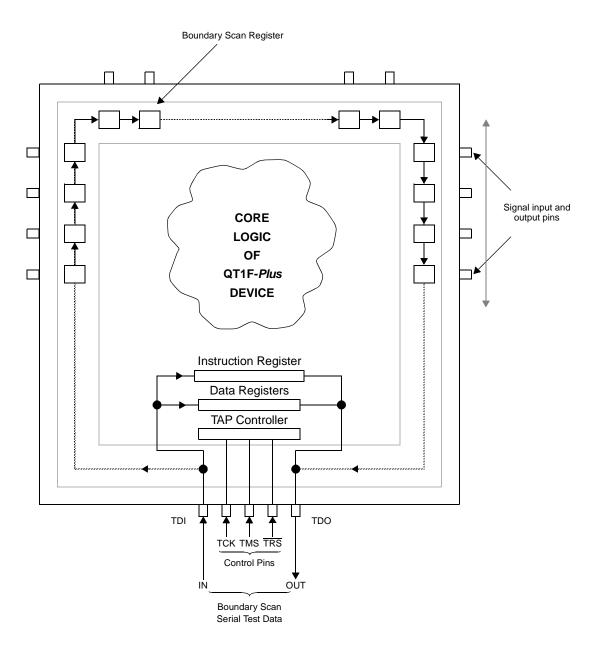

The Test Access Port block includes a five-pin Test Access Port (TAP) that conforms to the IEEE 1149.1 standard. This Test Access Port block provides external boundary scan to read and write the QT1F-Plus input and output pins from the TAP for board and component testing. In addition, a four-byte read only memory location is provided for reading the Tran-Switch manufacturer ID, a five-digit part identification number, and a version number for the part.

To assist in testing, built-in Pseudo Random Binary Sequence (PRBS) Generator and Analyzer blocks are provided. The PRBS Generator and Analyzer support a  $2^{15}$ -1 bit pseudo random binary sequence which is inverted relative to the pattern specified in the ITU-T Recommendation O.151. Each framer may select the PRBS Generator and Analyzer. The output of the Analyzer is provided on pin PRBSOOL. The PRBS framed mode, in which the transmit framer generates framing, is selected by writing a 1 to bit 6 in register 013H (PRBSFR) and is intended for use as a self-test feature. In this mode, the PRBS Generator and Analyzer can only communicate and frame up within the framer itself. The recovered line clock is the clock source for the Analyzer. If the receive slip buffer is enabled, then LRCLK must be its read clock source. The LO pin is the clock source for the Generator. In unframed PRBS mode, which is selected by writing a 0 to PRBSFR, the transmit framer does not generate framing. The QT1F-*Plus* also provides local loopback, remote line loopback, payload remote loopback, automatic remote line loopback (based on loop-up/down patterns received over a 5 second period), and DS0 channel loopback options for each framer.

The QT1F-Plus can be configured to operate with either Intel or Motorola compatible microprocessors via the Microprocessor Input/Output Interface block. Interrupt capability is provided with global and individual framer mask bits. An option is provided in software which permits the interrupt polarity to be inverted. An external system clock is used to run the internal state machines.

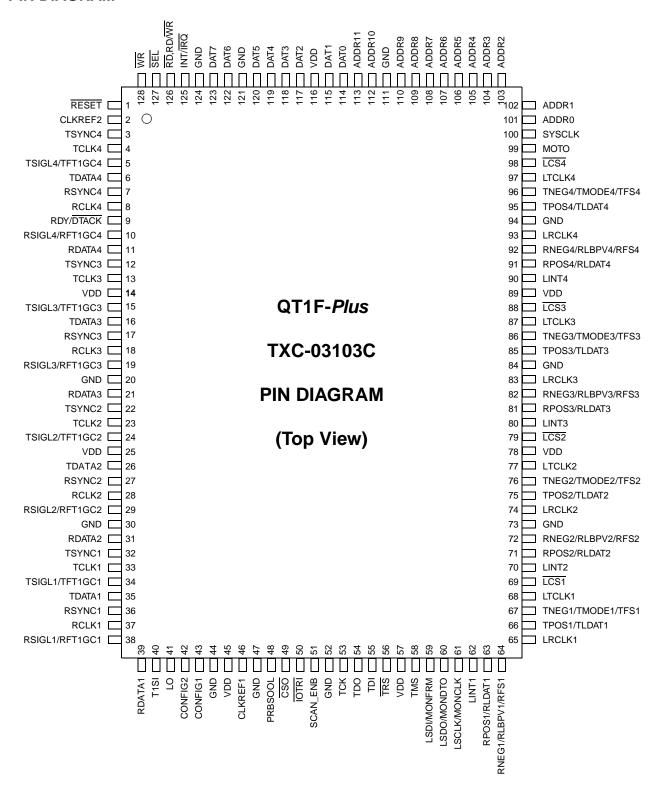

### **PIN DIAGRAM**

Note: This diagram is rotated relative to the top view shown in the Package Diagram in Figure 46a.

Figure 2. QT1F-Plus TXC-03103C Pin Diagram

### **PIN DESCRIPTIONS**

### **Power Supply and Ground**

| Symbol | Pin No.                                          | I/O/P* | Туре | Name/Function                                                                |

|--------|--------------------------------------------------|--------|------|------------------------------------------------------------------------------|

| VDD    | 14, 25, 45, 57,<br>78, 89, 116                   | Р      |      | <b>Power Supply:</b> +3.3 or +5.0 volt, ±5%, V <sub>DD</sub> supply voltage. |

| GND    | 20, 30, 44, 47, 52, 73,<br>84, 94, 111, 121, 124 | Р      |      | Ground: 0 volt reference.                                                    |

<sup>\*</sup> Note: I = Input; O = Output; P = Power; T=Tristate.

### **Line Interface Signals**

| Symbol                               | Pin No.              | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|----------------------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOSn/<br>RLDATn<br>(n=4-1)          | 91<br>81<br>71<br>63 | I     | ΠL     | Receive Unipolar Positive Signal Input: When control bit RAIL (bit 7 in register X00H) is a 1, the dual unipolar (positive/negative rail) mode is selected, and the RPOSn pin carries the receive positive rail input signal. RPOSn is high whenever a positive pulse is received by the external line interface transceiver.  Receive Line (NRZ) Data Input: When control bit RAIL (bit 7 in register X00H) is a 0, the NRZ mode is selected, and the RLDATn pin carries the receive NRZ data input signal. RLDATn is normally active high whenever a positive or negative pulse is received by the external line interface transceiver. When control bit RXNRZP (bit 0 in register X01H) is a 1, the QT1F-Plus accepts an inverted data signal and RLDATn is active low.                                                                                                                                                                                                                                                                                                                                                                                                                         |

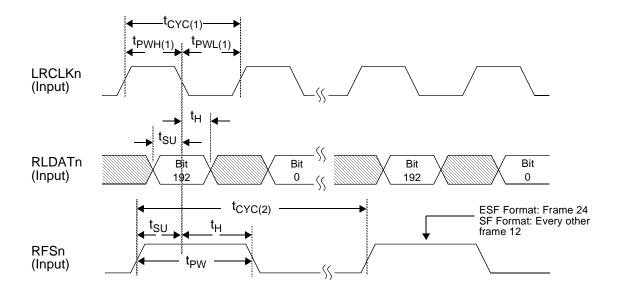

| RNEGn/<br>RLBPVn/<br>RFSn<br>(n=4-1) | 92<br>82<br>72<br>64 | 1     | ΠL     | Receive Unipolar Negative Signal Input: When control bit RAIL (bit 7 in register X00H) is a 1, the dual unipolar (positive/negative rail) mode is selected, and the RNEGn pin carries the receive negative rail input signal. RNEGn is high whenever a negative pulse is received by the external line interface transceiver.  External Receive Bipolar Violation Indication Input: When control bit RAIL (bit 7 in register X00H) is a 0 and the fast sync option is not selected (control bit RXFS, bit 1 in register X06H, is a 0), the RLBPVn pin provides an input for indications of external bipolar violations detected in the external line interface transceiver. A high indicates a bipolar violation, and increments the internal 16-bit coding violation counter once on a clock cycle. A bipolar violation is clocked in on rising edges of the receive line clock LRCLKn.  Receive Fast Sync: When control bit RAIL (bit 7 in register X00H) is a 0 and the fast sync mode is selected (control bit RXFS, bit 1 in register X06H, is a 1), this pin is used for a fast sync feature. A pulse on this pin is interpreted as identifying bit 192 of the last frame of the multiframe. |

$<sup>^{\</sup>star}$  Note: See Input, Output and Input/Output Parameters section for Type definitions, which depend on the value of  $V_{DD}$  selected.

| Symbol                               | Pin No.              | I/O/P | Type *      | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|----------------------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRCLKn<br>(n=4-1)                    | 93<br>83<br>74<br>65 | _     | ΠL          | Receive Line Clock: An input for the 1544 kHz recovered clock from the external line interface transceiver. Control bit RXCP (bit 6 in register X01H) determines the clock edge on which the receive line signals RPOSn/RNEGn and RLDATn are to be clocked in (1 for rising edge).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TPOSn/<br>TLDATn<br>(n=4-1)          | 95<br>85<br>75<br>66 | 0     | CMOS<br>2mA | Transmit Unipolar Positive Signal Output: When control bit RAIL (bit 7 in register X00H) is a 1, the dual unipolar mode is selected, and the TPOSn pin carries the transmit positive rail output signal. TPOSn is high whenever a positive pulse is to be transmitted by the external line interface transceiver.  Transmit Line (NRZ) Data Output: When control bit RAIL (bit 7 in register X00H) is a 0, the NRZ mode is selected, and the TLDATn pin carries the transmit NRZ data output signal. TLDATn is normally active high whenever a positive or negative pulse is to be transmitted by the external line interface transceiver. When control bit TXNRZP (bit 5 in register X01H) is a 1, the data output TLDATn is inverted and it is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TNEGn/<br>TMODEn/<br>TFSn<br>(n=4-1) | 96<br>86<br>76<br>67 | 0     | CMOS<br>2mA | Transmit Unipolar Negative Signal Output: When control bit RAIL (bit 7 in register X00H) is a 1, the dual unipolar mode is selected, and the TNEGn pin carries the transmit negative rail output signal. TNEGn is high whenever a negative pulse is to be transmitted by the external line interface transceiver.  Transmit Mode General Purpose Output: When control bit RAIL (bit 7 in register X00H) is a 0 and the fast sync mode is not selected (control bit TXFS, bit 0 in register X06H, is a 0), the state written into bit BE (bit 6 in register X00H) is clocked out on rising edges of the transmit line clock LTCLKn.  Transmit Fast Sync: When control bit RAIL (bit 7 in register X00H) is a 0 and the fast sync mode is selected (control bit TXFS, bit 0 in register X06H is a 1), this pin is used for a fast sync feature providing a sync pulse every 3 ms whether in SF or ESF mode; a pulse is sent on this pin for bit 192 in frame 24 when the ESF framing mode is selected and every other frame number 12 when the SF framing mode is selected. The ESF mode is selected when control bits FMD1 and FMD0 (bits 2-1 in register X04H) are set to 11. The SF mode is selected when the FMD1 and FMD0 bits are written with 01. |

| LTCLKn<br>(n=4-1)                    | 97<br>87<br>77<br>68 | 0     | CMOS<br>2mA | <b>Transmit Line Clock:</b> A 1544 kHz clock output. Control bit TXCP (bit 7 in register X01H) determines the clock edge on which the transmit line signals TPOSn/TNEGn and TLDATn are to be clocked out (1 for rising edge).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# **Line Interface Control Signals**

| Symbol           | Pin No.              | I/O/P | Туре            | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|----------------------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINTn<br>(n=4-1) | 90<br>80<br>70<br>62 | I     | ΠL              | General Purpose Interrupt Input Port: When enabled by control bit LIE (bit 1 in register X00H) being set to 1, the signal on this pin is logically OR-gated with the internal loss of signal indication to cause a loss of signal alarm and (if enabled) an interrupt. Control bit LPOL (bit 0 in register X00H) selects the input sense of this pin (1 for active low). This pin is active in both dual unipolar and NRZ modes.                                                                                                                                                                                                                                                                                                                                                                  |

| LCSn<br>(n=4-1)  | 98<br>88<br>79<br>69 | 0     | CMOS<br>2mA     | Line Interface Transceiver Chip Select: An active low signal that enables communications in both directions between the external line interface transceiver for channel n and the QT1F-Plus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LSCLK/<br>MONCLK | 61                   | O(T)  | CMOS<br>2mA     | Line Interface Transceiver Clock Signal: The clock for the transceiver is enabled when the CONFIG2 pin (pin 42) is low. This clock is shared between the four external transceivers. It is used to clock input data, and output data, between the external line interface transceiver and the QT1F-Plus. This clock is derived from the signal at pin LO. Output data (LSDO) is clocked out of the QT1F-Plus on falling edges of this clock. Input data (LSDI) is clocked into the QT1F-Plus on rising edges of this clock.  Monitor Clock Signal: The monitor feature is enabled when the CONFIG2 pin (pin 42) is high. The MONCLK pin provides either a receive or transmit NRZ clock. The clock in this mode can be tristated by writing a 0 to control bit ESP/EMON (bit 4 in register 013H). |

| LSDO/<br>MONDTO  | 60                   | O(T)  | CMOS<br>2mA     | Line Interface Transceiver Data Output Signal: The output data signal for the transceivers is enabled when the CONFIG2 pin (pin 42) is low. The output data signal is shared between the four transceivers.  Monitor Data Signal: The monitor feature is enabled when the CONFIG2 pin (pin 42) is high. The MONDTO pin provides either a NRZ receive or transmit data signal. This pin can be tristated in this mode by writing a 0 to control bit ESP/EMON (bit 4 in register 013H).                                                                                                                                                                                                                                                                                                             |

| LSDI/<br>MONFRM  | 59                   | I/O   | TTL/CMOS<br>4mA | Line Interface Transceiver Data Input Signal: The input data signal from the transceivers is enabled when the CONFIG2 pin (pin 42) is low. The input data signal is shared between the four transceivers.  Monitor Frame: This pin becomes an output when the CONFIG2 pin is high and a 1 is written to control bit ENMONFR (bit 2 in register 013H). This bit is active high during the bit time of bit 192 and low during other bit times. The frame pulse is clocked out on the rising edges of MONCLK.                                                                                                                                                                                                                                                                                        |

# **Clock Reference Signals**

| Symbol  | Pin No. | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|---------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKREF1 | 46      | O(T)  | CMOS<br>2mA | Clock Reference 1: This clock reference output is enabled when control bit ENREF1 (bit 3 in register 019H) is a 1. The clock reference signal can be either a 1544 kHz clock or an 8 kHz clock. When control bit 1544KHZ (bit 4 in register 019H) is a 1, the 1544 kHz reference is selected. The framer from which the clock is derived is determined by selection bits CR1S1 and CR1S0 (bits 1 and 0 in register 019H). This pin is forced low when a loss of signal alarm occurs for the framer selected. |

| CLKREF2 | 2       | O(T)  | CMOS<br>2mA | Clock Reference 2: This clock reference output is enabled when control bit ENREF2 (bit 5 in register 019H) is a 1. The clock reference signal can be either a 1544 kHz clock or an 8 kHz clock. When control bit 1544KHZ (bit 4 in register 019H) is a 1, the 1544 kHz reference is selected. The framer from which the clock is derived is determined by selection bits CR2S1 and CR2S0 (bits 7 and 6 in register 019H). This pin is forced low when a loss of signal alarm occurs for the framer selected. |

# **System Interface Signals**

| Symbol            | Pin No.             | I/O/P | Туре |                                                                                                           | Nam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ne/Function               | n                       |                  |

|-------------------|---------------------|-------|------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------|------------------|

| TSYNCn<br>(n=4-1) | 3<br>12<br>22<br>32 | I     | ΠL   | Transmit Synthe frame synthe frame synthem (The Frame synthem) QT1F-Plus frantable is a summarious system | and signaling<br>mer and is sou<br>mary of the syr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | multiframe<br>rced by the | e sync cou<br>e system. | nters within a   |

|                   |                     |       |      | <u>Interface</u>                                                                                          | <u>Width</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u>Polarity</u>           | <u>Period</u>           | <u>Lead Used</u> |

|                   |                     |       |      | Transmission                                                                                              | 1 Clk Cyc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | High                      | 3 ms                    | TSYNCn           |

|                   |                     |       |      | MVIP                                                                                                      | 1 Clk Cyc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Low                       | 125 µs                  | TSYNCn           |

|                   |                     |       |      | Please note: T to the transmit                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | is also pro               | grammabl                | e with respect   |

| TCLKn<br>(n=4-1)  | 4<br>13<br>23<br>33 | I     | ΠL   | to clock in the system. The foclock transition the sync pulse                                             | TSYNCn, TSION TSIO | GLn, and T<br>a summa     | DATAn sig               | lock rates and   |

|                   |                     |       |      |                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Clk in                    | Clk in                  |                  |

|                   |                     |       |      | <u>Interface</u>                                                                                          | <u>Rate</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | D/S                       | <u>SyncL</u>            | <u>Lead Used</u> |

|                   |                     |       |      | Transmission                                                                                              | 1.544 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pos.                      | Pos.                    | TCLKn            |

|                   |                     |       |      | MVIP                                                                                                      | 2.048 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Neg.                      | Pos.                    | TCLKn            |

| Symbol                        | Pin No.             | I/O/P | Туре            | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------|---------------------|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDATAn<br>(n=4-1)             | 6<br>16<br>26       | I     | ΠL              | <b>Transmit Data Highway Input:</b> This lead carries the data time slots from the system interface to the QT1F- <i>Plus</i> . The following table is a summary of the transmit data highway format.                                                                                                                                                                                                                                                                          |

|                               | 35                  |       |                 | Interface Format  Transmission DS1 frame (193 bit positions) repeated 24 times on TDATAn  MVIP DS1 frame mapped into 32 time slots on                                                                                                                                                                                                                                                                                                                                         |