#### **FEATURES**

- Maps DS3 (44.736 Mbit/s) or E3 (34.368 Mbit/s) line formats into SDH/SONET formats as follows:

- DS3 to/from STM-1/TUG-3

- DS3 to/from STS-3/STS-1 SPE or STS-1 SPE

- E3 to/from STM-1/TUG-3 only

- SDH/SONET bus access:

- Drop/add data byte access (with clock, C1J1, SPE, and parity)

- Add bus interface timing derived from drop bus, add bus, or external timing

- · Path overhead byte processing:

- Microprocessor or external interface

- B3 generation and detection with test mask

- B3 performance counter (16-bit) and block error counter (8-bit)

- C2 mismatch and unequipped detection

- G1 processing

- FEBE count by block or bits (16-bit counter)

- · Microprocessor access:

- Motorola or Intel compatible (selected via a lead)

- Hardware/software interrupt capability

- · Line Interface

- Transmit and receive NRZ or rail operation with split operation capability

- Testing functions:

- SONET, facility, or line loopback

- Transmit and receive 2<sup>15</sup>-1 or 2<sup>23</sup>-1 generators and shared analyzer

- Boundary scan capability (IEEE 1149.1)

- 144-lead plastic quad flat package (PQFP) or 208-lead plastic ball grid array package (PBGA)

#### **DESCRIPTION**

The L3M maps a DS3 line signal into an STM-1 TUG-3 or STS-3/ STS-1 SPE or STS-1 SPE SDH/SONET signal. An E3 line signal is mapped into an STM-1 TUG-3 signal only. The L3M provides a TUG-3 formatted signal for STM-1 operation, or an STS SPE for STS-3 or STS-1 operation. The SDH/SONET signal is transmitted via an add bus with timing derived from the drop side, add side or from external timing (STS-1 only). An option is provided to generate the A1, A2 framing pattern, C1 byte and H1, H2 pointer towards the add bus when external timing mode is selected.

Individual POH bytes for the transmitted SDH/SONET signal are mapped from the L3M memory map or an external interface. An option is provided to generate an unequipped status or TUG-3 path AIS signal. External accesses are provided for the communications channel "O"-bits and alarms for ring operation. The received signal is desynchronized from drop bus STM-1/TUG-3, STS-3/STS-1 SPE, or STS-1 signals. Internal pointer processing is performed for the TUG-3 signal. All POH bytes are provided for the microprocessor.

#### **APPLICATIONS**

- Add/drop multiplexers

- Digital cross-connect systems

- Broadband switching systems

- · Transmission equipment

U.S. Patents No.: 4,967,405; 5,040,170; 5,157,655; 5,265,096

U.S. and/or foreign patents issued or pending Copyright © 2001 TranSwitch Corporation

TranSwitch and TXC are registered trademarks of TranSwitch Corporation

Document Number: TXC-03452B-MB Ed. 6, April 2001

L3M TXC-03452B

#### **TABLE OF CONTENTS**

| Section                                                | Page |

|--------------------------------------------------------|------|

| List of Figures                                        | 3    |

| Block Diagram                                          | 5    |

| Block Diagram Description                              | 6    |

| Lead Diagrams                                          | 11   |

| Lead Descriptions                                      | 13   |

| Absolute Maximum Ratings and Environmental Limitations | 24   |

| Thermal Characteristics                                | 24   |

| Power Requirements                                     | 24   |

| Input, Output and Input/Output Parameters              | 25   |

| Timing Characteristics                                 | 27   |

| Operation                                              | 49   |

| L3M Power-Up Reset Sequence                            | 49   |

| PLL Filter Connection to VCXO                          | 51   |

| Testing                                                | 53   |

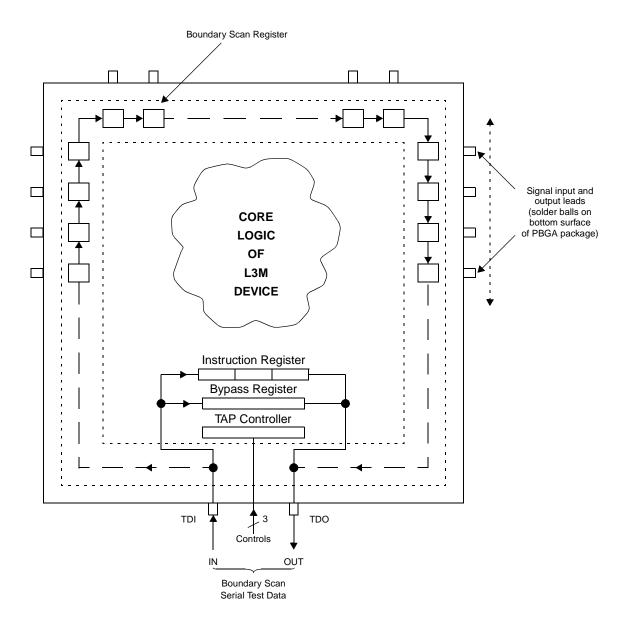

| Boundary Scan                                          | 55   |

| Memory Map                                             | 61   |

| Memory Map Descriptions                                | 63   |

| Package Information                                    | 86   |

| Ordering Information                                   | 88   |

| Related Products                                       | 88   |

| Standards Documentation Sources                        | 89   |

| List of Data Sheet Changes                             | 91   |

| Documentation Update Registration Form*                | 95   |

<sup>\*</sup> Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Website at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

L3M TXC-03452B

## **LIST OF FIGURES**

| Figu | re Pa                                                         | ıge |

|------|---------------------------------------------------------------|-----|

| 1.   | L3M TXC-03452B Block Diagram                                  | . 5 |

| 2.   | L3M Multiplexing Structure                                    |     |

| 3.   | ITU-TSS TUG-3 Build Format                                    | . 8 |

| 4.   | SONET AU-3/STS-1 SPE Build Format                             | . 9 |

| 5.   | Lead Diagram for L3M TXC-03452B 144-Lead Plastic              |     |

|      | Quad Flat Package                                             | 11  |

| 6.   | Lead Diagram foe L3M TXC-03452B 208-Lead Plastic              |     |

|      | Ball Grid Array Package                                       | 12  |

| 7.   | Line Side Transmit Timing                                     | 27  |

| 8.   | Line Side Receive Timing                                      | 28  |

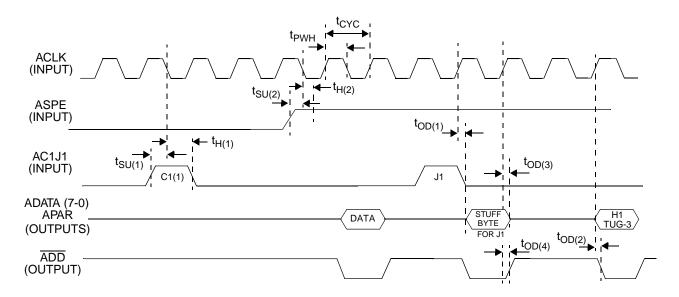

| 9.   | STM-1 Add Bus Derived Interface Timing                        | 29  |

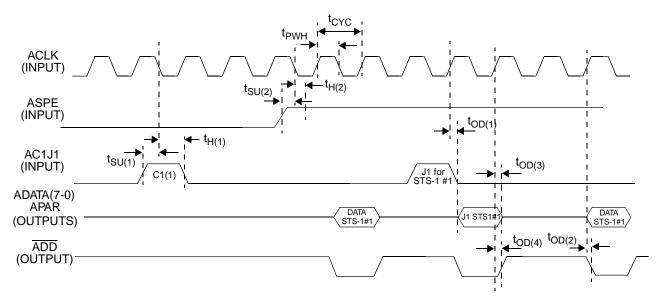

| 10.  | STS-3 Add Bus Derived Interface Timing                        | 30  |

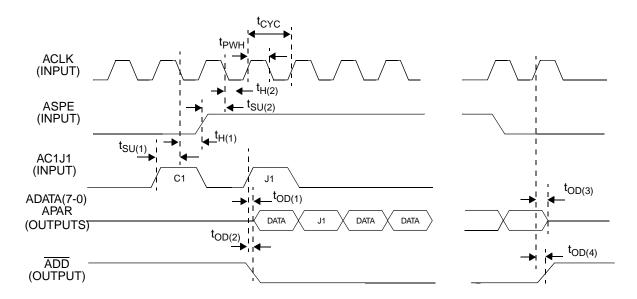

| 11.  | STS-1 Add Bus Derived Interface Timing                        | 31  |

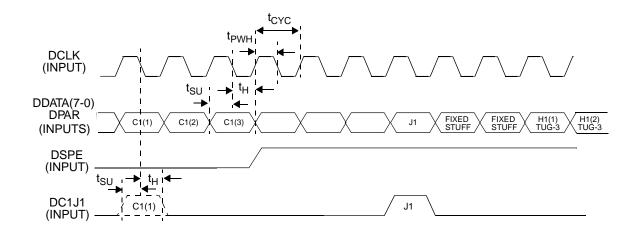

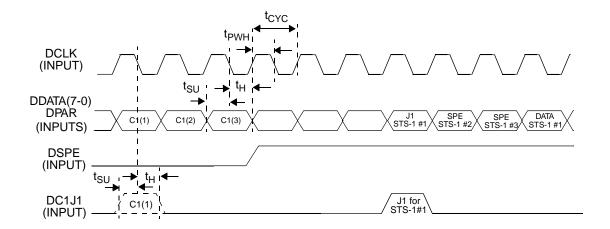

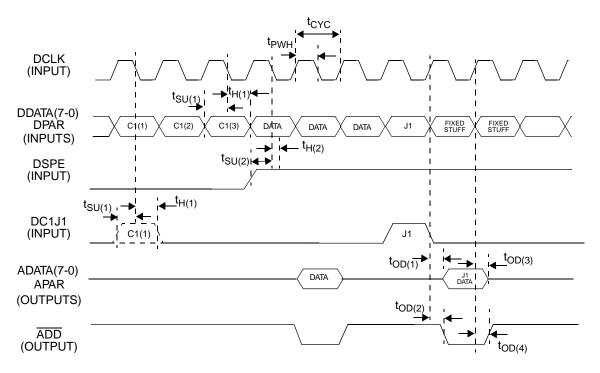

| 12.  | STM-1 Drop Bus Interface Timing                               | 32  |

| 13.  | STS-3 Drop Bus Interface Timing                               | 33  |

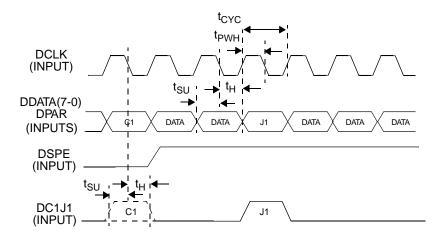

| 14.  | STS-1 Drop Bus Interface Timing                               | 34  |

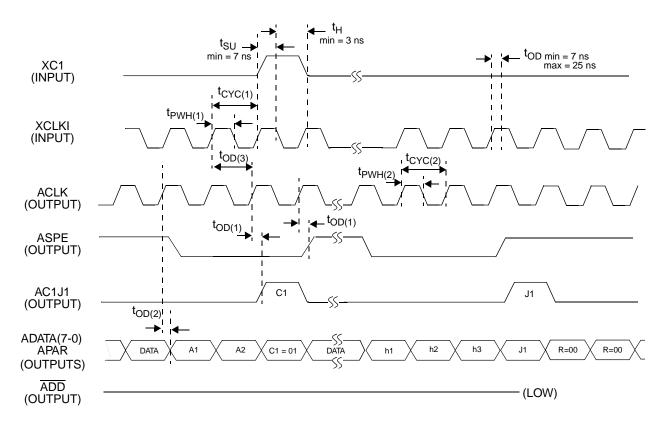

| 15.  | STS-1 Add Bus Interface Timing Using an External Clock        | 35  |

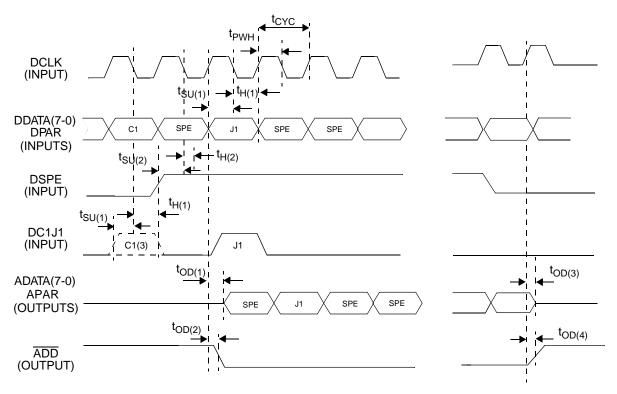

| 16.  | STM-1 Add/Drop Bus Interface Timing                           |     |

| 17.  | STS-3 Add/Drop Bus Interface Timing                           | 37  |

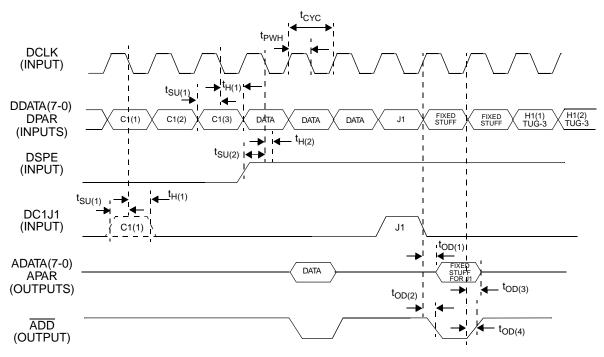

| 18.  | STS-1 Add/Drop Bus Interface Timing                           |     |

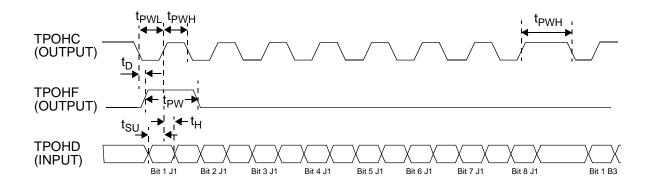

| 19.  | Transmit Path Overhead Timing                                 | 39  |

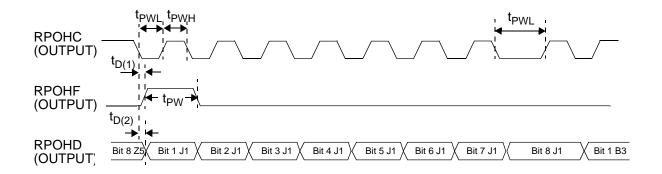

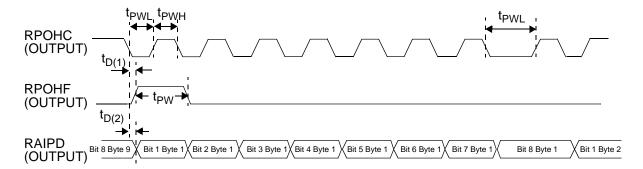

| 20.  | Receive Path Overhead Timing                                  |     |

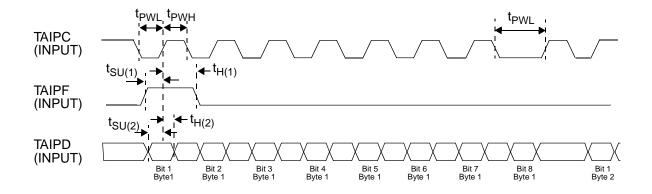

| 21.  | Transmit Alarm Indication Port Timing                         |     |

| 22.  | Receive Alarm Indication Port Timing                          |     |

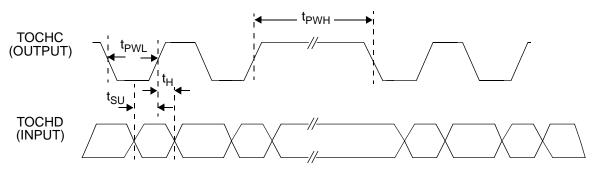

| 23.  | Transmit Overhead Communications Channel Timing               |     |

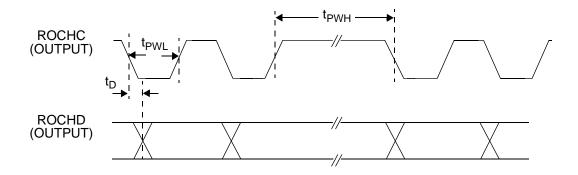

| 24.  | Receive Overhead Communications Channel Interface Timing      |     |

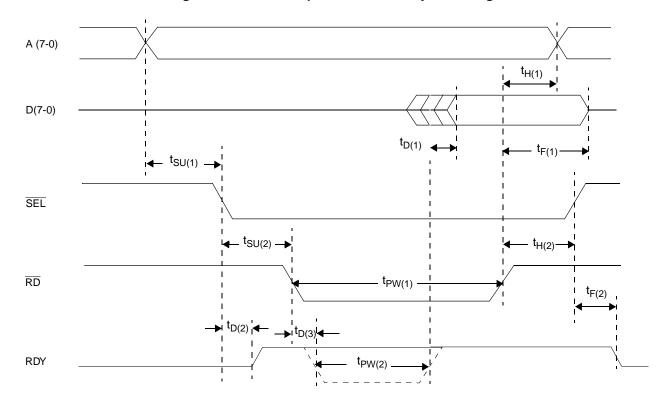

| 25.  | Intel Microprocessor Read Cycle Timing                        |     |

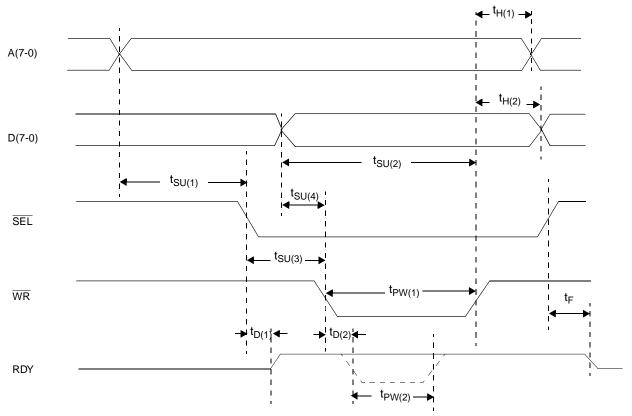

| 26.  | Intel Microprocessor Write Cycle Timing                       |     |

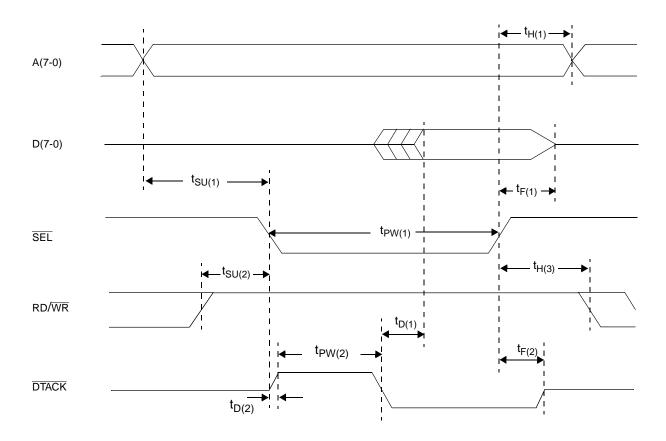

| 27.  | Motorola Microprocessor Read Cycle Timing                     |     |

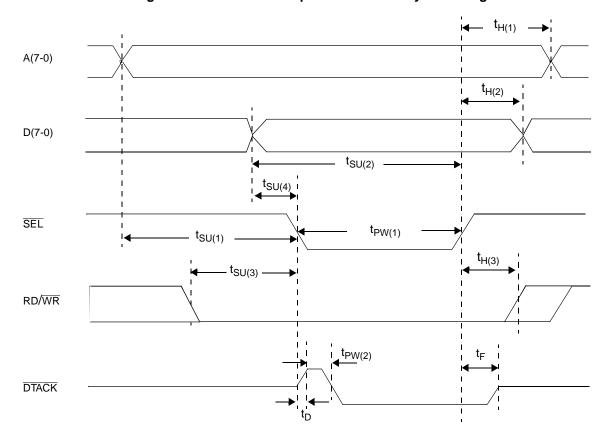

| 28.  | Motorola Microprocessor Write Cycle Timing                    |     |

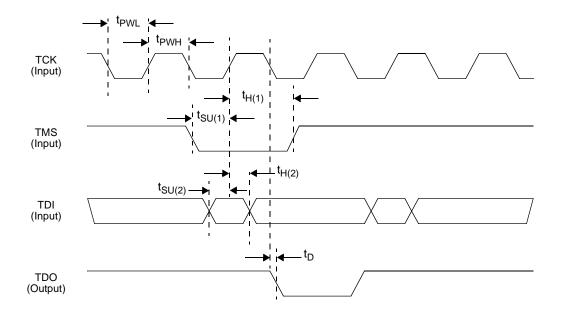

| 29.  | Boundary Scan Timing                                          |     |

| 30.  | L3M Power-Up Reset Sequence                                   |     |

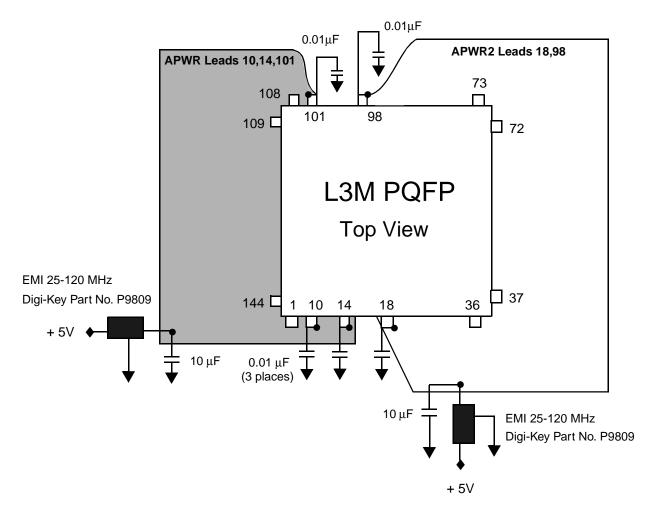

| 31.  | Physical Design For Analog Power Distribution                 |     |

| 32.  | PLL Connection to External VCXO                               |     |

| 33.  | Jitter Results for STS-3/DS3 and TUG-3/E3 Mappings            |     |

| 34.  | Loopbacks, Test Generators and Analyzer                       |     |

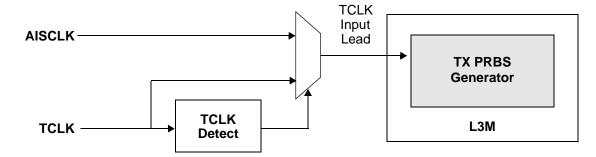

| 35.  | External Circuit to Maintain Clock Input to TX PRBS Generator |     |

| 36.  | Boundary Scan Schematic                                       |     |

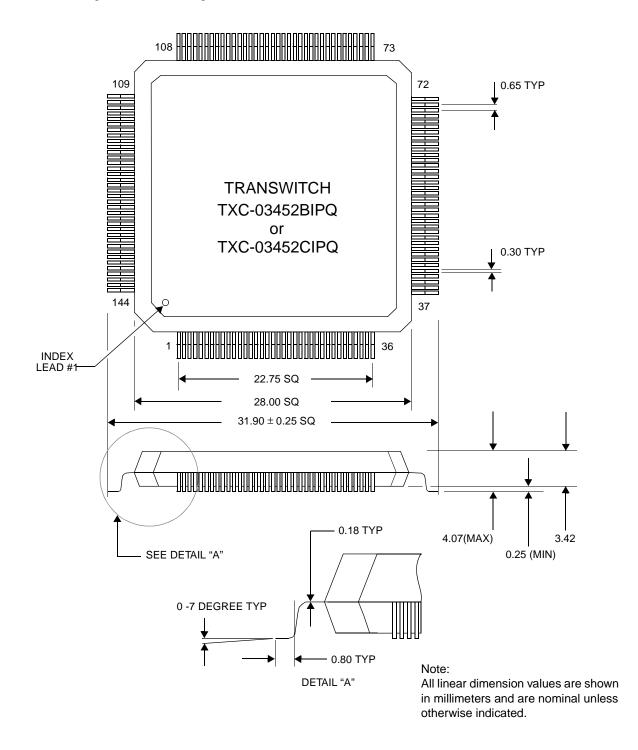

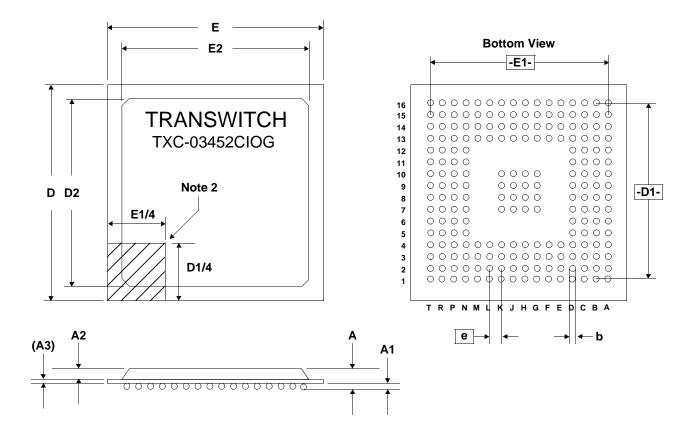

| 37.  | L3M TXC-03452B 144-Lead Plastic Quad Flat Package             | 86  |

| 38.  | L3M TXC-03452B 208-Lead Small Outline                         |     |

|      | Plastic Ball Grid Array Package                               | 87  |

L3M TXC-03452B

This page intentionally left blank.

#### **BLOCK DIAGRAM**

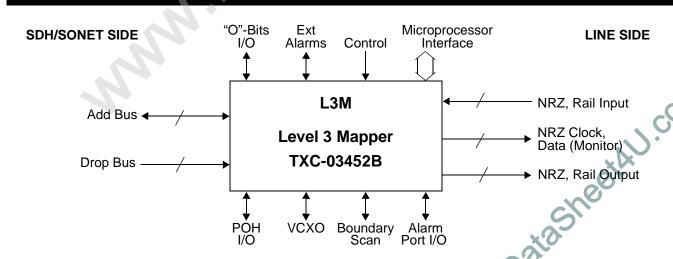

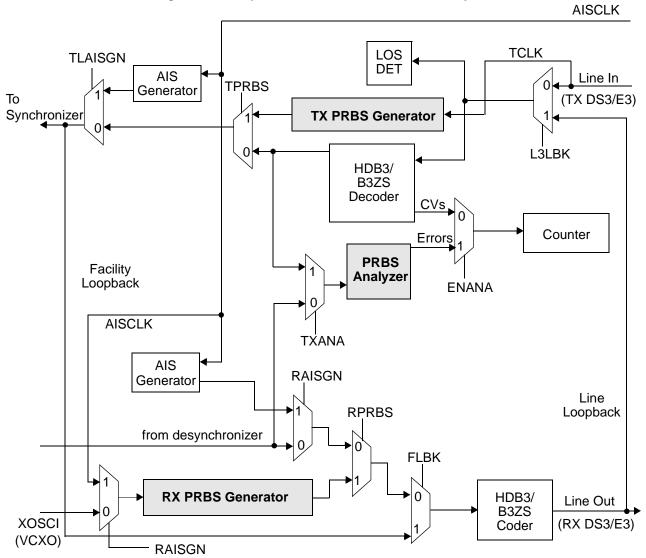

Figure 1. L3M TXC-03452B Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

#### Transmit And Receive Paths, Overhead Communications, Alarms And Control

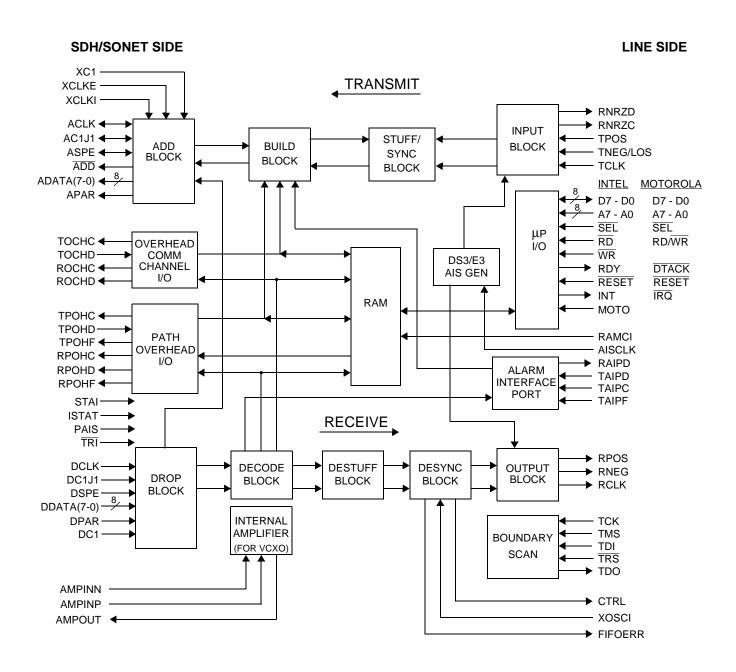

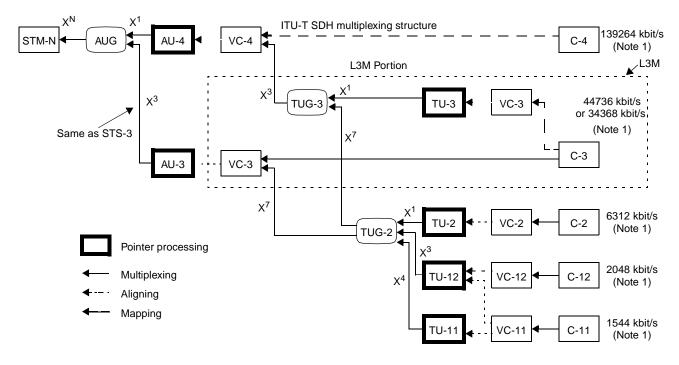

A simplified block diagram of the L3M device is shown in Figure 1. The portion of the ITU-T SDH multiplexing structure implemented by the L3M device is shown in Figure 2. In the Transmit direction, positive/negative (P/N) rail data and clock input signals, or NRZ data and clock input signals, operating at 44.736 Mbit/s (DS3) or 34.368 Mbit/s (E3), are connected to the Input Block. The transmit line input consists of positive rail/NRZ signal lead (TPOS), negative rail signal lead (TNEG), and input clock (TCLK). A control bit is provided in software that inverts the clock signal if required. The Input Block performs either an HDB3 or B3ZS decoder function if the input line termination is a rail signal. Separate NRZ data (RNRZD) and clock (RNRZC) output signals are provided for external performance monitoring circuits. Illegal coding violations are counted in a 16-bit performance counter. When the line termination is NRZ, the negative rail signal lead (TNEG) can be used to clock in an external loss of signal indication. The transmit signal and clock are both monitored for operation, and alarms are reported for failure conditions. Control bits are provided that enable the L3M device to send a line AIS when either signal or clock failure is detected. The Input Block also monitors the line signal for an E3 AIS and it has a  $2^{15}$ -1 or  $2^{23}$ -1 pseudo-random binary sequence (PRBS) test generator for testing.

Note 1: G.702 tributaries associated with containers C-x are shown. Other signals (e.g., ATM) can also be accommodated.

Figure 2. L3M Multiplexing Structure

## <u>TranSwitch</u>°

#### **DATA SHEET**

L3M TXC-03452B

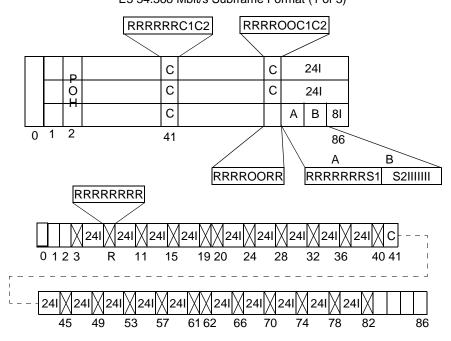

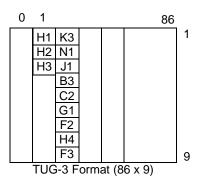

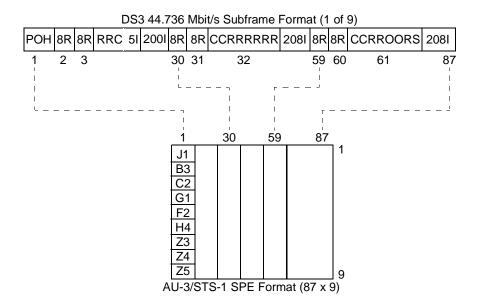

The Stuff/Sync Block and Build Blocks work together for mapping a DS3 signal into a TUG-3 or STS-1 SPE or an E3 signal into a TUG-3. The mapped formats are shown in Figures 3 and 4. The stuffing algorithm for the DS3 signal format uses one set of five control bits (C-bits) with one stuff opportunity bit (S-bit) for frequency justification, per subframe (9 subframes). The E3 format uses five pairs of control bits (C1, C2 bits) to control two stuff opportunity bits (S1 and S2) per subframe (one subframe per three rows for a total of three subframes per frame). A read clock and timing indications are given by the Build Block for reading the transmit FIFO. A FIFO overflow or underflow alarm indication is provided. Should an underflow/overflow condition occur, the FIFO is immediately reset to the start-up preset value. The transmit FIFO also tracks the incoming line signal that can have an average frequency error as high as +/- 20 ppm, and simultaneously accepts this signal with up to 5 UI Peak-to-Peak jitter (where UI = 1/f).

The Build Block, with signals exchanged between itself and the Stuff/Sync Block, constructs one of two 87 column by 9 row formats: an ITU-TSS TUG-3 signal (Figure 3) or a SONET STS-1 (for STS-3) signal (Figure 4). The L3M generates a stuff byte in column 0 when control bit NOPOH is set to 0, to fill out the 87 columns of the SPE such that three L3M devices will provide inputs for a VC-4 of 261 columns, as shown in Figure 2. This column position is overwritten with the VC-4 POH when the device is mapped into the first TUG-3, while fixed stuff is used for the second and third TUG-3s. A fixed pointer value of 6800H is used as the initial value when building a TUG-3 format. There are two levels of pointer movements in TUG-3 mapping. When the TUG-3 mode is selected in drop timing mode, the transmit TUG-3 pointer value will change when there is a receive STM-1 AU-4 pointer increment or decrement. However, this feature may be disabled. Pointer movements on the STM-1 bus, which are detected using the C1J1 and SPE bus signals, are compensated by creating a TUG-3 pointer movement in the opposite direction. An "O"-bit serial interface, or two bits in RAM, are used for mapping the two "O"-bits into the DS3 SONET format subframes. The "O"-bit interface consists of an output clock (TOCHC) and an input data lead (TOCHD). The nine Path Overhead bytes are mapped individually into the SONET format from either the POH interface (except the B3 byte), from microprocessor-written RAM positions, or from internal logic (such as the path RDI state in bit 5 of G1). The POH interface consists of an output clock (TPOHC), a framing pulse (TPOHF) and an input data lead (TPOHD). A control bit enables the POH interface bytes to be written into RAM when transmitted. Enable bits are provided for controlling the FEBE and path RDI states as a result of local alarms or remote status information received during ring operation. A B3 test mask or fixed byte can also be transmitted. Control bits are provided for generating a TUG-3 path AIS, or an unequipped status condition (payload and POH bytes are equal to zero). An alarm interface provides FEBE and path RDI (FERF) input indications from a mate L3M device for ring operation. The alarm interface leads consist of input data (TAIPD), framing pulse (TAIPF), and clock signal (TAIPC).

The Add Block uses an external byte rate clock signal (XCLKI), or the Add or Drop bus clock and the SPE and C1J1 timing signals, for building and adding a TUG-3, STS-3/STS-1 SPE, or STS-1 SPE to the Add bus. The Add Block supports the STM-1/STS-3 bus signaling rate of 19.44 MHz and the STS-1 signaling rate of 6.48 MHz. The external clock is enabled by placing a high on the external clock enable lead (XCLKE), and is intended for STS-1 operation. The external clock generates the Add bus clock (ACLK), C1J1 indication (AC1J1), and SPE indication (ASPE). The output data to the bus is 3-state, active true. A software control bit enables the transport overhead A1, A2, C1, and H1/H2 bytes to be generated. The H1 and H2 bytes will carry the value of 6000H and the C1 byte carries the value of 01H. An optional C1 signal (XC1 signal lead) can be applied to the L3M device to align the start of the frame (A1, A2 bytes).

2 3 4

32

59

60

86

DS3 44.736 Mbit/s Subframe Format (1 of 9)

POH 8R 8R RRC 5I 200I 8R CCRRRRR 208I 8R CCRROORS 208I

31

E3 34.368 Mbit/s Subframe Format (1 of 3)

Figure 3. ITU-TSS TUG-3 Build Format

Figure 4. SONET AU-3/STS-1 SPE Build Format

When Add bus timing is selected, the clock (ACLK), C1J1 indication (AC1J1), and SPE indication (ASPE) become input signals from the Add bus. When Drop timing is selected, the L3M device supports DC1J1 pointer movements on the Drop bus, and adjusts the pointer value in the TUG-3s accordingly. An active low Add indicator (ADD) is also provided to indicate the location of all time slots that are added to the bus by the L3M device (e.g., TUG-3 A, B or C). In TUG-3 mode, the VC-4 path overhead bytes are optionally sent as output to the bus when control bit NOPOH (Address CA, Bit 5) is set to 0. The selected clock is monitored for operation, and an odd parity signal (APAR) is calculated for the bus data, including the SPE and C1J1 signals when these signals are outputs (i.e., in external timing mode).

The Drop Block supports the STM-1/STS-3 bus signaling rate of 19.44 MHz and the STS-1 signaling rate of 6.48 MHz. The Drop Block uses the clock (DCLK), C1J1 indication (DC1J1) and a separate DC1 signal if required, and SPE indication (DSPE) from a Drop bus for determining the location of the Path Overhead J1 byte in the VC-4, the three J1 bytes in the three STS-1 SPEs in the STS-3 signal, and the single SPE for STS-1 operation. The C1 pulse is required, and is synchronous with the first C1 byte in the STM-1 Section Overhead bytes, or in the STS-3 or STS-1 Transport Overhead Bytes. The C1 pulse provides a framing indication for determining the location of the bytes corresponding to the TUG-3 or STS-1 selected, and is also used by the desynchronizer as a frame reference. The C1 pulse can be present in the DC1J1 signal or provided as a separate signal (DC1). The Drop SPE (DSPE) is active during the POH and payload byte times. The Drop Bus clock and composite C1J1 signal are monitored for operation, and odd parity is calculated and compared against the incoming parity bit.

The Decode Block contains the logic for performing pointer interpretation and tracking for the selected TUG-3 signal, removing the Path Overhead bytes and Overhead Communication bits, and detecting the E1 byte for an upstream AIS detection. The E1 byte carries an AIS indication from an associated TranSwitch SOT-3 or SOT-1 device. The SOT-3 or SOT-1 generates an AIS signal in one E1 byte for TUG-3 mode, or in each of the three E1 bytes for the three STS-1s, when a loss of frame, loss of pointer, loss of signal, or line AIS is detected. This indication is used by the L3M device to generate a Path RDI indication, and for generating a received DS3 or E3 AIS. In place of the E1 byte AIS, the L3M device also supports an alarm indication provided on the ISTAT and PAIS signal leads. The TUG-3 pointer is monitored for loss of pointer, New Data Flag, and Path AIS. Performance counters are provided for monitoring pointer movements. All POH bytes are written into RAM locations and are also provided at the POH interface. The POH interface consists of an output data lead (RPOHD),

# TranSwitch

## **DATA SHEET**

L3M TXC-03452B

framing pulse (RPOHF), and clock signal (RPOHC). The L3M device also provides a microprocessor-written location for performing C2 mismatch detection, and unequipped detection based on ANSI and ITU-TSS standards. The received "O"-bits are available at an external interface and a 2-bit RAM location for these bits is updated each frame. The "O"-bit interface consists of a data lead (ROCHD) and clock signal (ROCHC). An alarm indication port is provided for ring operation. The alarm indication port consists of a data lead (RAIPD), which is used with the POH interface framing pulse (RPOHF) and clock signal (RPOHC). The signal on the data lead (RAIPD) consists of the FEBE count and a path RDI (FERF) status indication.

The Desynchronize Block removes the effect on the output DS3 or E3 signals of systemic jitter due to signal mapping and pointer movements. The output has an average frequency equal to the source frequency, and has jitter characteristics that meet ITU-TSS and ANSI standards. The Desynchronize Block consists of two circuits, a Pointer Leak circuit and a Phase-Locked Loop circuit. The function of the Pointer Leak circuit is to absorb the immediate effect of up to eight consecutive pointer movements (any combination of SPE or TUG-3 pointer movements) in either direction, and filter them out in time. A single pointer adjustment is an 8 Unit Interval (UI) phase step. The Pointer Leak circuit turns the phase step into eight 1-UI steps, widely spaced in time, allowing the Phase-Locked Loop circuit to track. In normal operation, the output is one data bit and one clock cycle for each input bit. When a negative stuff occurs 8 extra bits are pulled from the signal and absorbed. Following this operation, the normal operation of one bit in for one bit out continues except that one extra bit is pulled from the FIFO every n frames. In this way, the pointer step is leaked out in 8 x n frames. The value of n is programmed via the microprocessor.

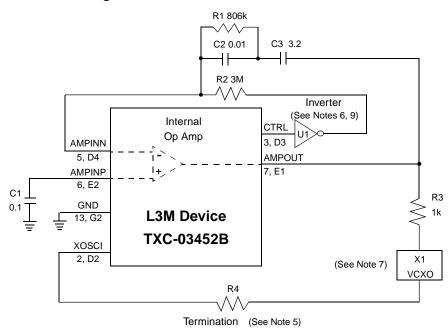

The Phase-Locked Loop (PLL) circuit of the Desynchronize Block is externally connected to a line-frequency voltage controlled crystal oscillator (VCXO) via a filter. Details of the external circuit for the PLL are provided in the Operation section of this Data Sheet under the heading "PLL Filter Connection to VCXO".

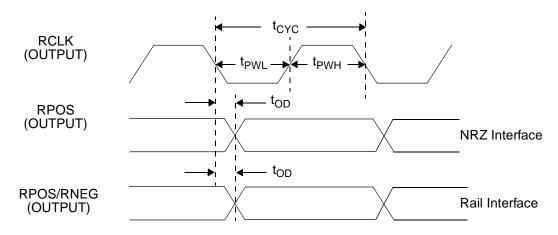

In the Receive direction, the Output Block provides either a positive (RPOS) and negative (RNEG) rail line signal or a NRZ line signal (RPOS), and a clock signal (RCLK). The HDB3/B3ZS coder operates independently of the transmitter. For interface flexibility, a control bit is provided for inverting the output clock. The receive data and clock outputs can be forced to a high impedance state for the purpose of tying two L3M devices together for ring operation or redundancy. An additional 2<sup>15</sup>-1 or 2<sup>23</sup>-1 pseudo-random test generator is provided. The Output Block and the Input Block share a 2<sup>15</sup>-1 or 2<sup>23</sup>-1 analyzer that can compare the desynchronizer output or transmit data against a fixed pattern. An alarm is provided when the analyzer and incoming data are not synchronous. Errors are counted in the 16-bit coding violation counter. Loopbacks between the Input and Output Blocks facilitate board and network debugging.

All of the control registers and performance counters, and the status and alarm indications, are accessible through the L3M device's compatible microprocessor bus interface in the Microprocessor I/O Block. The L3M device supports both Intel and Motorola microprocessor bus interfaces, with both hardware and software interrupt capability. The Motorola compatible microprocessor interface is selected by placing a high on the MOTO signal lead.

The Boundary Scan Block provides a mechanism for external access to the input and output leads of the device, so that they may be observed and tested. The structure and operation of this Block are described in the Operation section.

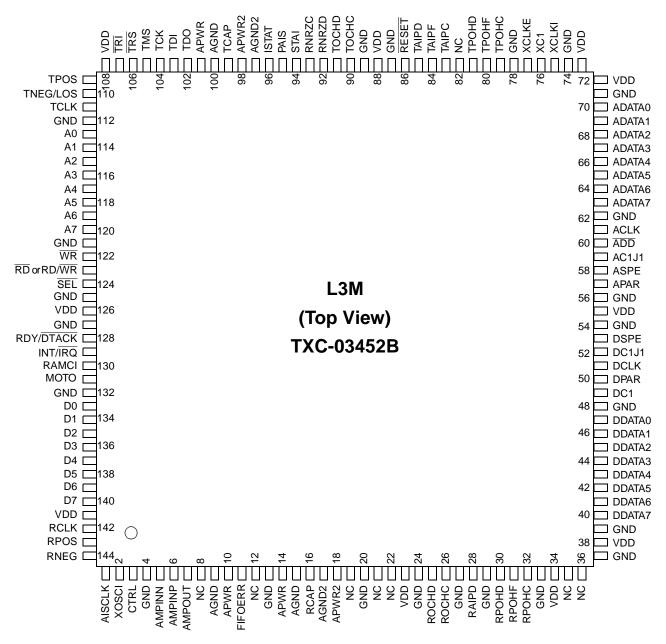

#### **LEAD DIAGRAMS**

Note: See Figure 37 for package information.

Figure 5. Lead Diagram for L3M TXC-03452B 144-Lead Plastic Quad Flat Package

L3M TXC-03452B

| 16 | VDD<br>3  | NC     | NC     | GND    | XCLKE | TPOHD | TAIPD | GND   | STAI  | APWR2 | APWR | NC     | TRI    | VDD    | NC   | NC   |

|----|-----------|--------|--------|--------|-------|-------|-------|-------|-------|-------|------|--------|--------|--------|------|------|

| 15 | NC O      | NC     | NC     | NC     | XC1   | TPOHF | TAIPF | VDD   | PAIS  | TCAP  | NC   | TCK    | TRS    | NC     | NC   | TNEG |

| 14 | ADATA0    | GND    | NC     | VDD    | GND   | NC    | RESET | TOCHC | RNRZC | AGND2 | NC   | TDI    | TMS    | TPOS   | NC   | TCLK |

| 13 | NC O      | ADATA1 | ADATA2 | XCLKI  | TPOHO | TAIPC | GND   | TOCHD | RNRZD | ISTAT | AGND | TDO    | A1     | GND    | NC   | A0   |

| 12 | ADATA3    | NC     | ADATA4 | NC     |       |       |       |       |       |       |      |        | A4     | A3     | A2   | NC   |

| 11 | ADATA6    | ADATA5 | NC     | ADDATA | 7     |       | 2115  | 21.5  | 21.5  | 2     |      |        | A7     | A6     | A5   | NC   |

| 10 | $\bigcup$ | ACLK   | NC     | AC1J1  |       |       | GND   | GND   | GND   | GND   |      |        | SEL    | RD     | NC   | WR   |

| 9  | APAR      | ASPE   | GND    | NC     |       |       | GND   | GND   | GND   | GND   |      |        | NC     | VDD    | NC   | GND  |

| 8  | GND       | DSPE   | NC     | VDD    |       |       | GND   | GND   | GND   | GND   |      |        | GND    | RDY    | INT  | NC   |

| 7  | DPAR      | DC1    | DCLK   | DC1J1  |       |       | GND   | GND   | GND   | GND   |      |        | NC     | RAMCI  | МОТО | NC   |

| 6  | DDATA1    | DDATA2 | NC     | DDATA0 |       |       |       |       |       |       |      |        | D0     | D1     | D3   | D2   |

| 5  | DDATA4    | NC (   | DDATA3 | NC     |       |       |       |       |       |       |      |        | NC     | D4     | D6   | D5   |

| 4  | DDATA6    | DDATA7 | NC O   | DDATA5 | GND   | ROCHD | NC    | APWR2 | NC    | AGND  | NC   | AGND   | AMPINN | D7     | VDD  | NC   |

| 3  | GND       | NC     | NC     | GND I  | RPOHD | ROCHC | VDD   | NC    | AGND2 | NC    | FIFO | NC     | CTRL   | NC     | RCLK | NC   |

| 2  | VDD       | NC     | NC     | NC     | RPOHO | RAIPD | NC    | NC    | RCAP  | GND   | NC   | AMPINE | XOSCI  | AISCLK | NC   | RPOS |

| 1  | NC        | NC     | NC     | VDD    | RPOHF | GND   | NC    | GND   | NC    | APWR  | APWR | AMOUT  | GND    | NC     | NC   | RNEG |

|    | T         | R      | Р      | N      | M     | L     | K     | J     | Н     | G     | F    | E      | D      | С      | В    | Α    |

Note: This is the bottom view. The leads are solder balls. See Figure 38 for package information. Some signal Symbols have been abbreviated to fit the space available. The Symbols are shown in full in the Lead Descriptions section.

Figure 6. Lead Diagram for L3M TXC-03452B 208-Lead Plastic Ball Grid Array Package

L3M TXC-03452B

## **LEAD DESCRIPTIONS**

#### POWER SUPPLY, GROUND AND NO CONNECTS

| Symbol | 144-Lead<br>QFP<br>Lead No.                                                                      | 208-Lead BGA<br>Lead No.                                                                                                                                                                                                                                                                                                                 | I/O/P* | Type** | Name/Function                                                                                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 23,34,38,55,<br>72,73,88,<br>108,126,141                                                         | B4, C9, C16,<br>K3, J15, N1,<br>N8, N14, T2,<br>T16                                                                                                                                                                                                                                                                                      | Р      |        | <b>VDD:</b> +5 volts, ± 5% power supply.                                                                                                                                              |

| APWR   | 10,14,101                                                                                        | F1, F16, G1,                                                                                                                                                                                                                                                                                                                             | Р      |        | Analog VDD: +5 volts, ± 5% power supply.                                                                                                                                              |

| APWR2  | 18,98                                                                                            | G16, J4                                                                                                                                                                                                                                                                                                                                  | Р      |        | <b>Analog VDD2:</b> +5 volts, $\pm$ 5% power supply.                                                                                                                                  |

| GND    | 4,13,20,24,<br>27,29,33,37,<br>39,48,54,56,<br>62,71,74,78,<br>87,89,112,<br>121,125,<br>127,132 | D8, G2, G7,<br>G8, G9, G10,                                                                                                                                                                                                                                                                                                              | Р      |        | Ground: 0 volts reference.                                                                                                                                                            |

| AGND   | 9,15,100                                                                                         | E4, F13, G4                                                                                                                                                                                                                                                                                                                              | Р      |        | Analog Ground: 0 volts reference.                                                                                                                                                     |

| AGND2  | 17,97                                                                                            | G14, H3                                                                                                                                                                                                                                                                                                                                  | Р      |        | Analog Ground2: 0 volts reference.                                                                                                                                                    |

| NC     | 8,12,19<br>21,22,35<br>36,82                                                                     | A3, A4, A7, A8,<br>A11, A12, A16,<br>B1, B2, B9,<br>B10, B13, B14,<br>B15, B16, C1,<br>C3, C15, D5,<br>D7, D9, E3,<br>E16, F2, F4,<br>F14, F15, G3,<br>H1, H4, J2, J3,<br>K1, K2, K4,<br>L14, N2, N5,<br>N9, N12, N15,<br>P1, P2, P3, P4,<br>P6, P8, P10,<br>P11, P14, P15,<br>P16, R1, R2,<br>R3, R5, R12,<br>R15, R16, T1,<br>T13, T15 |        |        | No Connect: NC leads are not to be connected, not even to another NC lead, but must be left floating. Connection of these leads may impair performance or cause damage to the device. |

\*Note: I = Input; O = Output; P = Power; T = Tri-State

<sup>\*\*</sup>Note: See Input, Output and Input/Output Parameters section below for the Type definitions.

L3M TXC-03452B

#### LINE INTERFACE

| Symbol       | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------|-----------------------------|-----------------------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RNRZD        | 92                          | H13                         | 0     | CMOS<br>4mA | Receive Line NRZ Data: Output provided for an optional external performance monitoring circuit. This serial NRZ output is provided after the decoder (transmit direction), independent of whether the input is NRZ or rail. Data is always clocked out on positive transitions of clock (RNRZC). This lead goes to a high impedance state when control bit L3Z is set to 1.                   |

| RNRZC        | 93                          | H14                         | 0     | CMOS<br>4mA | Receive Line Clock: NRZ data on lead RNRZD is clocked out of the L3M device on positive transitions of this clock. This lead goes to a high impedance state when control bit L3Z is set to 1.                                                                                                                                                                                                 |

| TPOS         | 109                         | C14                         | _     | CMOS        | Transmit NRZ Line Data/Positive Rail Data: Serial NRZ input for the 44.736 or 34.368 Mbit/s asynchronous line data. This lead also provides the positive rail data input for an internal decoder.                                                                                                                                                                                             |

| TNEG/<br>LOS | 110                         | A15                         | _     | CMOS        | Transmit Negative Rail Data: When operating in the P/N rail mode, this lead provides a negative rail input for the internal decoder. When operating in the NRZ mode, a high on this lead instead indicates an external loss of signal alarm, so that the lead must be tied to ground if it is not used for input of an external loss of signal indication.                                    |

| TCLK         | 111                         | A14                         | _     | CMOS        | Transmit Line Clock: NRZ or rail data is clocked into the L3M device using the TPOS/TNEG signal leads on positive transitions of this clock when control bit INVCI is set to 0. NRZ or rail data is clocked in on negative transitions when control bit INVCI is set to 1. TCLK is used as the input clock for the transmit PRBS generator and it must be present to generate a test pattern. |

| RCLK         | 142                         | В3                          | 0     | CMOS<br>4mA | Receive Line Clock: Line data present on the RPOS/RNEG signal leads (44.736 or 34.368 Mbit/s) is clocked out of the L3M device on negative transitions of this clock when control bit INVCO is set to 0. NRZ or rail data is clocked out on positive transitions of this clock when control bit INVCO is set to 1. This lead goes to a high impedance state when control bit L3Z is set to 1. |

| RPOS         | 143                         | A2                          | 0     | CMOS<br>4mA | Receive Line NRZ Data/Positive Rail Data: Serial NRZ output for the 44.736 or 34.368 Mbit/s asynchronous line data. This lead also provides the positive rail output when the rail interface is selected. This lead goes to a high impedance state when control bit L3Z is set to 1.                                                                                                          |

| RNEG         | 144                         | A1                          | 0     | CMOS<br>4mA | Receive Negative Rail Data: This lead provides a negative rail interface from the internal coder. This lead goes to a high impedance state when control bit L3Z is set to 1. When the NRZ interface is selected, this lead outputs a 0.                                                                                                                                                       |

L3M TXC-03452B

#### **MICROPROCESSOR INTERFACE**

| Symbol        | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No.                     | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|-----------------------------|-------------------------------------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A(7-0)        | 120 - 113                   | D11, C11,<br>B11, D12,<br>C12, B12,<br>D13, A13 | I     | TTL    | Address Bus: These are address line inputs that are used by the microprocessor for accessing the L3M RAM for a read/write cycle. A0 is defined as the least significant bit. High is logic 1.                                                                                                                                                                                                                                                                                                                          |

| WR            | 122                         | A10                                             | I     | TTL    | Write (I mode): Intel Mode - An active low signal generated by the micro- processor for writing to the L3M RAM locations. Motorola Mode - Not used.                                                                                                                                                                                                                                                                                                                                                                    |

| RD<br>RD/WR   | 123                         | C10                                             | I     | TTL    | Read (I mode) or Read/Write (M mode): Intel Mode - An active low signal generated by the micro- processor for reading the L3M RAM locations. Motorola Mode - A high signal generated by the microprocessor for reading the L3M RAM locations. A low signal is used for writing to L3M RAM locations.                                                                                                                                                                                                                   |

| SEL           | 124                         | D10                                             | I     | TTLp   | <b>Select:</b> A low enables data transfers between the microprocessor and the L3M device during a read/write cycle.                                                                                                                                                                                                                                                                                                                                                                                                   |

| RDY/<br>DTACK | 128                         | C8                                              | O(T)  | TTL8mA | Ready (I mode) or Data Transfer Acknowledge (M mode): Intel Mode - A high is an acknowledgment from the addressed RAM location that the transfer can be completed. A low indicates that the L3M has not completed the transfer cycle, and the microprocessor must wait before latching read data or completing the write cycle.  Motorola Mode - During a read bus cycle, a low signal indicates the information on the data bus is valid. During a write bus cycle, a low signal acknowledges the acceptance of data. |

| INT/IRQ       | 129                         | B8                                              | O(T)  | TTL4mA | Interrupt: Intel Mode - A high on this output lead signals an interrupt request to the microprocessor. The off state is low when control bit INTZ (bit 2, register C2) is 0, and 3-state when INTZ is 1.  Motorola Mode - A low on this lead signals an interrupt request to the microprocessor. The off state is high when INTZ is 0, and 3-state when INTZ is 1.                                                                                                                                                     |

| RAMCI         | 130                         | C7                                              | I     | CMOS   | RAM Clock Input: Clock input for the internal RAM. This clock allows an outside clock to provide an arbitrator function for accessing the internal RAM structure. This clock must operate between 12 and 25 MHz with a duty cycle of 50 +/- 10 percent. This clock and the microprocessor timing signals may operate asynchronously with respect to each other.                                                                                                                                                        |

| МОТО          | 131                         | B7                                              | I     | TTL    | Motorola/Intel Microprocessor Select: A high selects the Motorola microprocessor compatible bus interface. A low selects the Intel microprocessor compatible bus interface.                                                                                                                                                                                                                                                                                                                                            |

L3M TXC-03452B

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No.          | I/O/P | Туре | Name/Function                                                                                                                                                                             |

|--------|-----------------------------|--------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D(7-0) | 140 - 133                   | C4, B5, A5,<br>C5, B6, A6,<br>C6, D6 | I/O   |      | <b>Data Bus:</b> Bi-directional data lines used for transferring data between the L3M device and an external microprocessor. D0 is defined as the least significant bit. High is logic 1. |

#### **DROP BUS INTERFACE**

| Symbol         | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No.          | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                         |

|----------------|-----------------------------|--------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDATA<br>(7-0) | 40 - 47                     | R4, T4, N4,<br>T5, P5, R6,<br>T6, N6 | I     | TTL  | <b>Drop Data Byte:</b> Byte data that corresponds to the STM-1/STS-3/STS-1 signal from the drop bus. The first bit received corresponds to bit 7.                                                                                                                                                                                                     |

| DC1            | 49                          | R7                                   | _     | TTL  | <b>Drop C1 Pulse:</b> External positive C1 pulse that may be provided on this lead instead of in the DC1J1 signal. This signal is ORed internally with the DC1J1 signal to form a composite C1J1 signal. If this lead is not used it must be grounded. This lead is used for special applications.                                                    |

| DPAR           | 50                          | Т7                                   | _     | TTL  | Drop Bus Parity Bit: This is an odd parity input for each data byte, the DSPE signal, and the composite DC1J1 pulses. The status bit BUSERR (bit 5 in registers B0 and B1) indicates when this input differs from an internally-generated odd parity for these signals, but no other action is taken upon occurrence of this drop bus parity error.   |

| DCLK           | 51                          | P7                                   | -     | TTL  | <b>Drop Bus Clock:</b> This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 bus operation. Drop bus byte-wide data (DDATA7-0), parity (DPAR), payload indicator (DSPE), and C1/J1 (DC1J1 and DC1) are clocked into the L3M device on negative transitions of this clock.                                             |

| DC1J1          | 52                          | N7                                   | I     | TTL  | Drop Bus C1 and J1 Indicator: The C1 pulse is an active high, one clock cycle wide timing pulse that indicates the location of the first C1 time slot in the STM-1 or STS-3 frame. If the C1 pulse is not present in this signal, it must be provided at the DC1 lead. A J1 pulse, also one clock cycle wide, identifies the location of the J1 byte. |

| DSPE           | 53                          | R8                                   | I     | TTL  | <b>Drop Bus SPE Indicator:</b> A signal that is high during the STM-1 VC-4, and the STS-3/STS-1 SPE period.                                                                                                                                                                                                                                           |

L3M TXC-03452B

#### **ADD BUS INTERFACE**

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P  | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-----------------------------|-----------------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APAR   | 57                          | Т9                          | O(T)   | TTL4mA | Add Bus Parity Bit: This output bit represents the odd parity calculation for each data byte in the add timing and drop timing modes. In the external timing mode, the parity calculation also includes the ASPE and AC1J1 signals which become outputs. This lead is forced to a high impedance state when the control bit ADDZ is set to 1, or when ADD is inactive (high).                                                                                                                |

| ASPE   | 58                          | R9                          | I/O(T) | TTL4mA | Add Bus SPE Indicator: An input signal that is high during the STM-1 VC-4 period, and STS-3/STS-1 SPE period. When enabled by the external clock enable (XCLKE) control lead, this signal becomes an output. This lead is forced to a high impedance state when the control bit ADDZ is set to 1, or when the drop timing mode is selected.                                                                                                                                                  |

| AC1J1  | 59                          | N10                         | I/O(T) | TTL4mA | Add Bus C1 and J1 Indicator: The C1 pulse is an active high, one clock cycle wide input timing pulse that identifies the location of the first C1 time slot in the STM-1 or STS-3 frame. A J1 pulse, also one clock cycle wide, identifies the location of the J1 byte. When enabled by the external clock enable (XCLKE) control lead, this signal becomes an output. This lead goes to a high impedance state when control bit ADDZ is set to 1, or when the drop timing mode is selected. |

| ĀDD    | 60                          | T10                         | 0      | TTL4mA | Add Indicator: An active low signal that identifies the position of the data time slots being mapped onto the add bus.  This signal will be high when  - Data is not present  - Reset is present  - Add bus loss of clock occurs  - When control bit ADDZ is set to 1.  - Until the first two C1 pulses are received in either the add bus or drop bus timing mode.  This avoids bus contention during start up.  This signal will be a high impedance when the TRI lead is low.             |

| ACLK   | 61                          | R10                         | I/O    | TTL4mA | Add Bus Clock: This clock operates at 19.44 MHz for STM-1/STS-3 operation, and at 6.48 MHz for STS-1 bus operation. The add clock is used for Build Block timing and for sourcing the add bus byte-wide data (ADATA(7-0)), parity (APAR), and add indicator (ADD). When enabled by the external clock enable (XCLKE) control lead, this signal becomes an output. This lead goes to a high impedance state when control bit ADDZ is set to 1.                                                |

| Symbol         | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No.                              | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                             |

|----------------|-----------------------------|----------------------------------------------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADATA<br>(7-0) | 63 - 70                     | N11,<br>T11,<br>R11,<br>P12,<br>T12,<br>P13,<br>R13, T14 | O(T)  | TTL4mA | Add Data Byte: Byte-wide data that corresponds to the STM-1/STS-3/STS-1 time slots that are placed on the add bus. Bit 7 corresponds to bit 1 in the STM-1/SONET transmission format. This bus is forced to a high impedance state when the control bit ADDZ is set to 1, or when ADD is inactive (high). |

#### **OVERHEAD COMMUNICATIONS CHANNEL INTERFACE**

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----------------------------|-----------------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROCHD  | 25                          | L4                          | 0     | TTL4mA | Receive Overhead Comm Channel Data: Unaligned data output for the overhead communications channel "O"-bits from the DS3 or E3 formats. The "O"-bits are clocked out of the L3M device on negative transitions of the ROCHC clock signal.                                                                                                                                                                                                                                                |

| ROCHC  | 26                          | L3                          | 0     | TTL4mA | Receive Overhead Comm Channel Clock: A gapped 720 kHz output clock with an average frequency of 144 kHz for clocking out the transmit overhead communications channel bits to external circuitry.                                                                                                                                                                                                                                                                                       |

| TOCHC  | 90                          | J14                         | 0     | TTL4mA | Transmit Overhead Comm Channel Clock: A gapped 720 kHz output clock with an average frequency of 144 kHz for sourcing the transmit overhead communications channel bits from external circuitry.                                                                                                                                                                                                                                                                                        |

| TOCHD  | 91                          | J13                         | I     | TTL    | Transmit Overhead Comm Channel Data: Data input for the overhead communications channel in the DS3 or E3 formats. Data is clocked into the L3M device on positive transitions of the TOCHC clock signal. The bits are multiplexed into the "O"-bit positions unaligned regarding bit position and subframe number. This input is enabled by the EXOO control bit. When enabled, the lead must be grounded if it is desired to insert zeroes in the corresponding fixed stuff locations. |

L3M TXC-03452B

#### PATH OVERHEAD INTERFACE

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                   |

|--------|-----------------------------|-----------------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RPOHD  | 30                          | M3                          | 0     | TTL4mA | Receive Path Overhead Data: The serial output for the nine path overhead bytes. The POH bytes are clocked out on negative transitions of the clock signal (RPOHC).                                                                                                                                                              |

| RPOHF  | 31                          | M1                          | 0     | TTL4mA | Receive Path Overhead Framing: A positive one clock cycle (RPOHC) wide output framing pulse that is synchronous with the J1 data of RPOHD. This signal is also used as the framing pulse for the receive alarm indication port data (RAIPD).                                                                                    |

| RPOHC  | 32                          | M2                          | 0     | TTL4mA | Receive Path Overhead Clock: A gapped clock used for clocking out the path overhead bytes, and receive alarm indication port data (RAIPD).                                                                                                                                                                                      |

| TPOHC  | 79                          | M13                         | 0     | TTL4mA | <b>Transmit Path Overhead Clock:</b> A gapped clock used for clocking the path overhead bytes from an external circuit into the L3M device.                                                                                                                                                                                     |

| TPOHF  | 80                          | L15                         | 0     | TTL4mA | <b>Transmit Path Overhead Framing:</b> A positive one clock cycle (TPOHC) wide output framing pulse that determines the start of the J1 byte in TPOHD.                                                                                                                                                                          |

| TPOHD  | 81                          | L16                         | I     | TTL    | <b>Transmit Path Overhead Data:</b> A serial input for the following path overhead bytes: J1, C2, G1, F2, H4, Z3, Z4, and Z5 bytes. The POH bytes are clocked into the L3M device on positive transitions of the TPOHC clock signal. Eight bits are clocked in during the B3 byte time, but they are ignored by the L3M device. |

L3M TXC-03452B

#### **ALARM INDICATION PORT**

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|--------|-----------------------------|-----------------------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RAIPD  | 28                          | L2                          | 0     | TTL4mA | Receive Alarm Indication Port Data: A serial output tha provides the 4-bit FEBE count (B3 error count) and Path RDI alarm indication to a mate L3M device for ring operation. This lead is normally connected to the TAIPD lead at the mate L3M device. The RPOHC signal is used to clock this signal out of the L3M device. The RPOHF signal provides the frame reference signal. The bits are sent in the following format:  Bits 1 2 3 4 5 6 7 8 |  |  |  |  |

|        |                             |                             |       |        | B3 Count RDI 0 0 1  Bit 1 is the MSB and is sent first in the bit stream.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| TAIPC  | 83                          | L13                         | I     | TTL    | Transmit Alarm Indication Port Clock: This clock input is normally connected to the RPOHC clock lead at the mate L3M device for ring operation. Transmit alarm data (TAIPD) is clocked into the L3M device on positive transitions of the RPOHC clock.                                                                                                                                                                                              |  |  |  |  |

| TAIPF  | 84                          | K15                         | I     | TTL    | Transmit Alarm Indication Port Framing Pulse: Normally connected to RPOHF lead at the mate L3M device for ring operation. Used to indicate the first bit in the first byte for the external alarm indications.                                                                                                                                                                                                                                      |  |  |  |  |

| TAIPD  | 85                          | K16                         | I     | TTL    | Transmit Alarm Indication Port Data: This serial input lead is normally connected to the RAIPD lead at the mate L3M device for ring operation. Provides an input for the four bit FEBE count (B3 error count), and Path RDI alarm indication (as shown above for RAIPD).                                                                                                                                                                            |  |  |  |  |

#### **ADDITIONAL SIGNALS**

| Symbol | QFP | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                              |

|--------|-----|-----------------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AISCLK | 1   | C2                          | I     | CMOS | AIS Clock Input: Clock input for the L3M device's AIS generator. This clock must be present for the AIS generator to function. The clock must have the operating line rate of either 44.736 or 34.368 MHz, and have a frequency stability of +/- 20 ppm.                                   |

| XCLKI  | 75  | N13                         | I     | TTL  | External Clock Input: Used to derive output timing and data for the add bus. Enabled by placing a high on the lead labeled XCLKE. A byte clock frequency of 6.48 MHz is required for STS-1 operation. This clock is monitored for loss of clock when the external timing mode is selected. |

L3M TXC-03452B

| Symbol  | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре         | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|---------|-----------------------------|-----------------------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XC1     | 76                          | M15                         | I     | TTL          | <b>External C1 Input:</b> Optional C1 input signal used to synchronize the frame start when the external timing mode is selected for the add bus. This lead must be held low when the external timing mode is not used.                                                                                                                                                                                                                                                                                  |  |  |

| XCLKE   | 77                          | M16                         | Ι     | TTL          | <b>External Clock Enable:</b> A high on this lead enables add bus timing to be derived from the XCKLI lead (external clock signal). The ASPE, AC1J1, and ACLK signal leads become output leads.                                                                                                                                                                                                                                                                                                          |  |  |

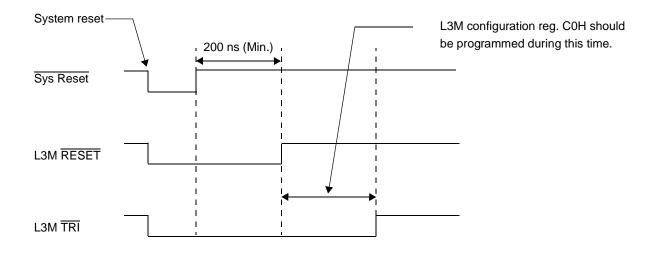

| RESET   | 86                          | K14                         | _     | TTLp         | Hardware Reset: A low clears all counters and initiates reframing in the transmit direction upon its release. This lead is provided with an internal pull-up resistor. The resistant must be low for a minimum of 200 nanoseconds. The bus clocks, line clocks, microprocessor clock and VCXO clock must be present during the reset signal. The add bus outputs are held in a high impedance state during the reperiod. The add bus high impedance state is released of the occurrence of the C1 pulse. |  |  |

| FIFOERR | 11                          | F3                          | 0     | TTL8mA<br>OD | '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| STAI    | 94                          | H16                         | I     | TTL          | STS Network Alarm Indication: A high on this lead will generate a count of 9 in bits 1 through 4 of G1 when control bit FEBE9EN is equal to 1. An indication is also provided as the XSTAI status bit. The lead is normally grounded.                                                                                                                                                                                                                                                                    |  |  |

| PAIS    | 95                          | H15                         | I     | TTL          | External Path AIS Indication: A high on this lead may be used to indicate an external Path AIS has occurred. It causes the XPAIS status bit to be set to 1. This lead is enabled when control bit XALM2AIS is a 1. When enabled, the in-band upstream AIS indication provided via the TOH E1 byte is disabled.                                                                                                                                                                                           |  |  |

| ISTAT   | 96                          | G13                         | I     | TTL          | External STS-1 Alarm Indication: A high on this lead may be used to indicate an external SONET/SDH alarm has occurred. It causes the XISTAT status bit to be set to 1.                                                                                                                                                                                                                                                                                                                                   |  |  |

| TRI     | 107                         | D16                         | ı     | TTLp         | High Impedance Enable: A low causes all L3M device digital outputs and bi-directional leads to be set to a high impedance state for test purposes. This lead is provided with an internal pull-up resistor.                                                                                                                                                                                                                                                                                              |  |  |

L3M TXC-03452B

#### **RECEIVE AND TRANSMIT PHASE LOCKED LOOPS**

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре   | Name/Function                                                                                                                                          |

|--------|-----------------------------|-----------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCAP   | 16                          | H2                          | I     | Analog | Receiver Internal Phase Locked Loop Capacitor: Optional capacitor used for an internal receive phase locked loop. This lead must be left floating.     |

| TCAP   | 99                          | G15                         | I     | Analog | Transmitter Internal Phase Locked Loop Capacitor: Optional capacitor used for an internal transmit phase locked loop. This lead must be left floating. |

#### **RECEIVE DESYNCHRONIZER**

| Symbol | 144-Lead<br>QFP<br>Lead No. | 208-Lead<br>BGA<br>Lead No. | I/O/P | Туре        | Name/Function                                                                                                                                      |  |  |

|--------|-----------------------------|-----------------------------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XOSCI  | 2                           | D2                          | I     | CMOS        | <b>External Oscillator Input:</b> This input is connected to the output of the external VCXO, as shown in the PLL connections diagram (Figure 32). |  |  |

| CTRL   | 3                           | D3                          | 0     | CMOS<br>4mA | <b>Phase Detector Output</b> : Normally connected to the exte nal low pass filter consisting of external components and the internal amplifier.    |  |  |

| AMPINN | 5                           | D4                          | I     | Analog      | Internal Amplifier - Negative Port Input: Negative port of an internal amplifier which can be used in the desynchronizer loop filter.              |  |  |

| AMPINP | 6                           | E2                          | I     | Analog      | Internal Amplifier - Positive Port Input: Positive port of an internal amplifier which can be used in the desynchronizer loop filter.              |  |  |

| AMPOUT | 7                           | E1                          | 0     | Analog      | Internal Amplifier - Output: Output of an internal amplifier which can be used in the desynchronizer loop filter.                                  |  |  |

L3M TXC-03452B

#### **BOUNDARY SCAN TESTING**

| Symbol | 144-Lead<br>QFP<br>Lead No. | BGA | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------|-----------------------------|-----|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TDO    | 102                         | E13 | O(T)  | TTL4mA | <b>Boundary Scan Test Data Output:</b> Serial data clocked out on negative transitions of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| TDI    | 103                         | E14 | I     | TTL    | <b>Boundary Scan Test Data Input:</b> Serial data input for boundary scan test messages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TCK    | 104                         | E15 | I     | TTL    | <b>Boundary Scan Test Clock:</b> The input clock for boundary scan testing. The TDI and TMS states are clocked in on positive transitions.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| TMS    | 105                         | D14 | I     | TTLp   | <b>Boundary Scan Test Mode Select:</b> The signal present on this lead is used to control test operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| TRS    | 106                         | D15 | I     | TTLp   | Boundary Scan Test Reset: To asynchronously reset the Test Access Port (TAP) controller, this lead must either be held low or asserted low for at least 200 ns and then held high (i.e., pulsed low). The TAP controller may also be reset by holding the TMS signal lead high for at least five clock cycles of TCK. Failure to perform this reset may cause the TAP controller to take control of the output leads. In applications which will not be using the boundary scan feature, this lead must be tied low, thereby holding the TAP controller reset. |  |  |

L3M TXC-03452B

### ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS

| Parameter                          | Symbol          | Min        | Max                   | Unit   | Conditions                     |

|------------------------------------|-----------------|------------|-----------------------|--------|--------------------------------|

| Supply voltage                     | $V_{DD}$        | -0.3       | +7.0                  | V      | Note 1                         |

| DC input voltage                   | V <sub>IN</sub> | -0.5       | V <sub>DD</sub> + 0.5 | V      | Notes 1, 3                     |

| Storage temperature range          | T <sub>S</sub>  | -55        | 150                   | °C     | Note 1                         |

| Ambient Operating Temperature      | T <sub>A</sub>  | -40        | 85                    | °C     | 0 ft/min linear airflow        |

| Component Temperature x Time       | TI              |            | 270 x 5               | °C x s | Note 1                         |

| Moisture Exposure Level            | ME              | 5          |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A |

| Relative Humidity, during assembly | RH              | 30         | 60                    | %      | Note 2                         |

| Relative Humidity, in-circuit      | RH              | 0          | 100                   | %      | non-condensing                 |