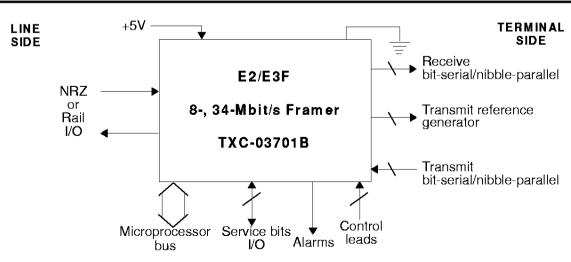

E2/E3F Device 8-, 34-Mbit/s Framer TXC-03701B

**DATA SHEET**

#### FEATURES

- Framer for ITU-TSS Recommendations:

- G.742 (8448 kbit/s)

- G.745 (8448 kbit/s)

- G.751 (34368 kbit/s)

- G.753 (34368 kbit/s)

- · Line side interface:

- Rail or NRZ

- · HDB3 codec for rail I/O

- Terminal side interface:

- Nibble-parallel

- Bit-serial

- · Transmit reference generator for serial I/O

- · Microprocessor or control leads

- · Service bit I/O port

- · Pin-selectable transmit line clock polarity

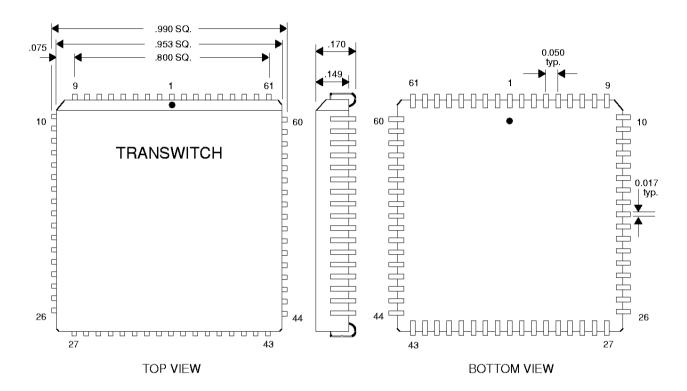

- 68-pin plastic leaded chip carrier

#### DESCRIPTION =

The E2/E3 Framer (E2/E3F) is a CMOS VLSI device that provides the functions needed to frame a wideband payload to one of four ITU-TSS Recommendations: G.742, G.745, G.751, or G.753. The E2/E3F interfaces to line circuitry with either rail or NRZ signals. On the terminal side, the interface can be either nibble-parallel or bit-serial. The nibble interface clocks are gapped for the service bits, framing bits and the BIP-4 option, if selected. For the serial interface, a transmit reference generator is provided.

The E2/E3F can be operated with or without a microprocessor. When interfaced with a microprocessor, the E2/E3F provides an 8-byte memory map for control, performance counters and alarm status. The E2/E3F provides a transmit and receive interface port for accessing the overhead bits from each of the four recommendations. The overhead bits can also be accessed by the microprocessor via the memory map.

#### APPLICATIONS ≡

- · Line terminals

- Wideband data or video transport

- · Test equipment

- · Multiplexer systems

Copyright © 1995 TranSwitch Corporation

TXC and TranSwitch are registered trademarks of TranSwitch Corporation

Document Number: TXC-03701B-MB Ed. 1, August 1995

# TABLE OF CONTENTS

| SECTION     |                                                      | PAGE         |  |  |  |  |  |  |  |

|-------------|------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| Block Diag  | k Diagram                                            |              |  |  |  |  |  |  |  |

| Block Diag  | ram Description                                      | 3            |  |  |  |  |  |  |  |

| Pin Diagra  | m                                                    | 6            |  |  |  |  |  |  |  |

| Pin Descrip | otions                                               | <del>6</del> |  |  |  |  |  |  |  |

| Absolute M  | Maximum Ratings                                      | 14           |  |  |  |  |  |  |  |

| Thermal C   | haracteristics                                       | 14           |  |  |  |  |  |  |  |

| Power Red   | quirements                                           | 14           |  |  |  |  |  |  |  |

| Throughpu   | t Delays                                             | 14           |  |  |  |  |  |  |  |

| Input, Outp | out and I/O Parameters                               | 15           |  |  |  |  |  |  |  |

| Timing Cha  | aracteristics                                        | 17           |  |  |  |  |  |  |  |

| Operation   |                                                      | 33           |  |  |  |  |  |  |  |

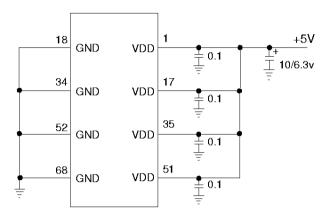

| Power       | r Suppl <b>y C</b> onnections                        | 33           |  |  |  |  |  |  |  |

| Memory M    | ap                                                   | 33           |  |  |  |  |  |  |  |

| Memory M    | ap Descriptions                                      | 34           |  |  |  |  |  |  |  |

| Package Ir  | nformation                                           | 37           |  |  |  |  |  |  |  |

| Ordering Ir | nformation                                           | 38           |  |  |  |  |  |  |  |

| Related Pr  | oducts                                               | 38           |  |  |  |  |  |  |  |

| Standards   | Documentation Sources                                | 39           |  |  |  |  |  |  |  |

| Document    | ation Update Registration Form                       | 43           |  |  |  |  |  |  |  |

|             | LIST OF FIGURES                                      |              |  |  |  |  |  |  |  |

| Figure 1.   | E2/E3F TXC-03701B Block Diagram                      | 3            |  |  |  |  |  |  |  |

| Figure 2.   | G.7XX Frame Contents Summary                         | 4            |  |  |  |  |  |  |  |

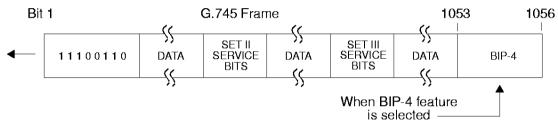

| Figure 3.   | G.745 BIP-4 Location                                 | 5            |  |  |  |  |  |  |  |

| Figure 4.   | E2/E3F TXC-03701B Pin Diagram                        | 6            |  |  |  |  |  |  |  |

| Figure 5.   | Line Side Receive NRZ Timing                         | 17           |  |  |  |  |  |  |  |

| Figure 6.   | Line Side Transmit NRZ Timing                        | 18           |  |  |  |  |  |  |  |

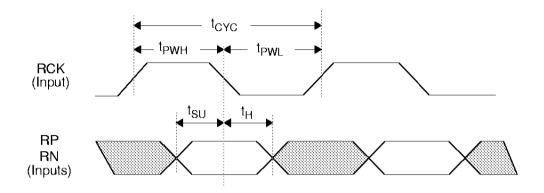

| Figure 7.   | Line Side Receive Rail Timing                        |              |  |  |  |  |  |  |  |

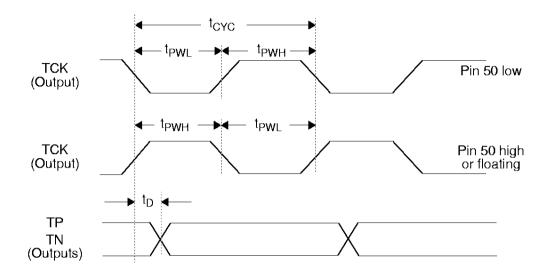

| Figure 8.   | Line Side Transmit Rail Timing                       |              |  |  |  |  |  |  |  |

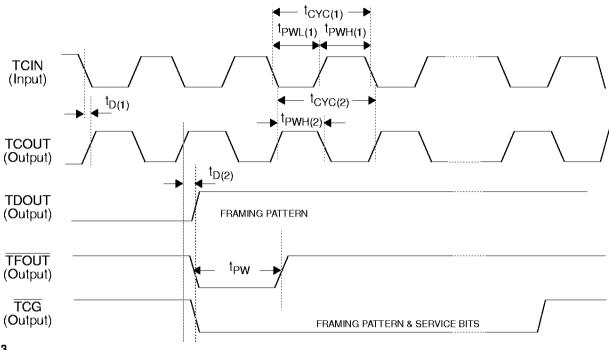

| Figure 9.   | Transmit Reference Generator Timing                  |              |  |  |  |  |  |  |  |

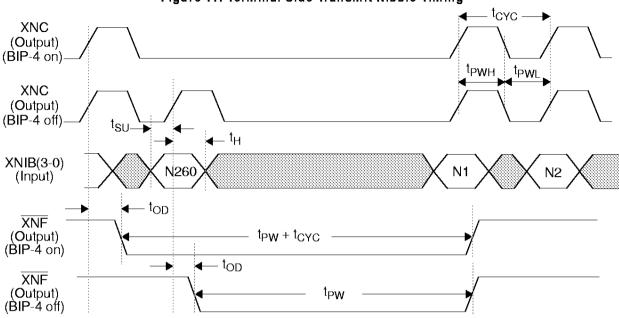

| Figure 10.  | Terminal Side Receive Nibble Timing                  |              |  |  |  |  |  |  |  |

| Figure 11.  | G                                                    |              |  |  |  |  |  |  |  |

| Figure 12.  | Terminal Side Receive Serial Timing                  |              |  |  |  |  |  |  |  |

| Figure 13.  | Terminal Side Transmit Serial Timing                 |              |  |  |  |  |  |  |  |

| Figure 14.  | G.742/G.751 Service Bit Receive Timing               |              |  |  |  |  |  |  |  |

| Figure 15.  | G.745/G.753 Service Bit Receive Timing               |              |  |  |  |  |  |  |  |

| Figure 16.  | G.742/G.751 Service Bit Transmit Timing              |              |  |  |  |  |  |  |  |

| Figure 17.  | G.745/G.753 Service Bit Transmit Timing              |              |  |  |  |  |  |  |  |

| Figure 18.  | BIP-4 Error Timing                                   |              |  |  |  |  |  |  |  |

| Figure 19.  | Microprocessor Read Cycle                            |              |  |  |  |  |  |  |  |

| Figure 20.  | Microprocessor Write Cycle                           |              |  |  |  |  |  |  |  |

| Figure 21.  | Power Supply Connections                             |              |  |  |  |  |  |  |  |

| Figure 22.  | E2/E3F TXC-03701B 68-Pin Plastic Leaded Chip Carrier | 37           |  |  |  |  |  |  |  |

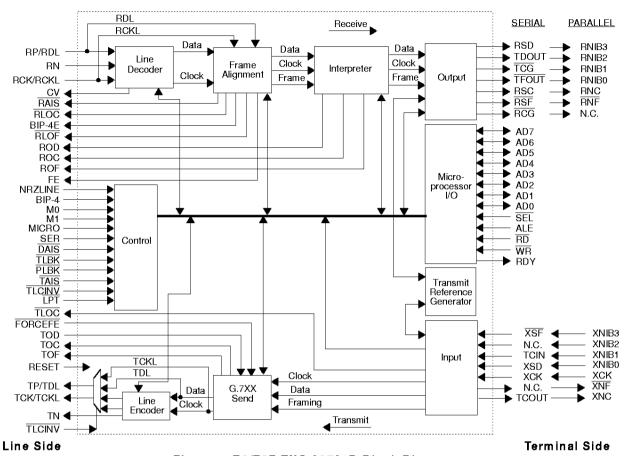

#### **BLOCK DIAGRAM**

Figure 1. E2/E3F TXC-03701B Block Diagram

#### **BLOCK DIAGRAM DESCRIPTION**

The block diagram for the E2/E3F is shown in Figure 1. The E2/E3F receives a line side NRZ data signal (RDL) and clock signal (RCKL), or a positive (RP) and negative (RN) rail signal and clock signal (RCK), from a TranSwitch MRT, or from another line interface circuit. The selection of the line interface, rail or NRZ, is controlled by the external lead labeled NRZLINE. Indications of HDB3 coding violation errors are detected in the Line Decoder Block and are provided on an external signal lead (CV) as pulses. Coding violation errors are also counted in an 8-bit saturating counter accessed by the microprocessor through the memory map. A coding violation is not part of the standard HDB3 zero-substitution code, and occurs because of noise or other impairments on the line.

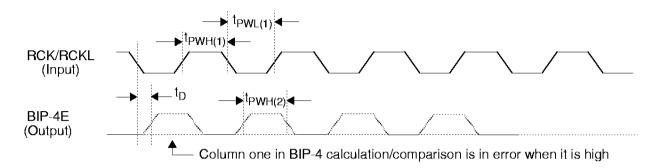

The selection of one of the four G.7XX framing formats (G.742, G.745, G.751, and G.753), which are supported by the E2/E3F, is determined by external control leads (M1 and M0), or states written into the memory map by the microprocessor. The Frame Alignment Block performs frame alignment and alarm detection. It detects Loss of Frame (RLOF), Loss of Clock (RLOC), and performs AIS detection (RAIS) and BIP-4 (Bit Interleaved Parity-4) detection (BIP-4E) when this feature is enabled in the nibble-parallel mode. Loss of clock is detected whether the clock is stuck high or low. A framing error (FE) output is also provided to indicate when any of the framing bits in the G. 7XX frame are in error. Loss of the receive clock or framing normally causes AIS to be inserted into the terminal side data stream. However, for some applications, receive data is required on the terminal side regardless of frame alignment. The disable AIS (DAIS) control lead permits the E2/E3F to provide receive data in the presence of loss of frame. The external alarm indications (latched and unlatched states) are provided in the memory map, and unlatched alarm indications are provided at signal leads.

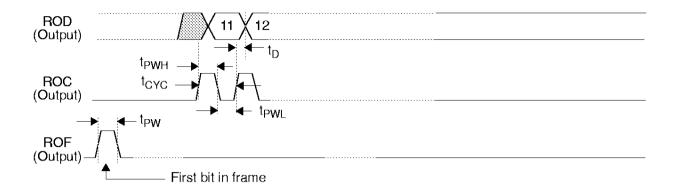

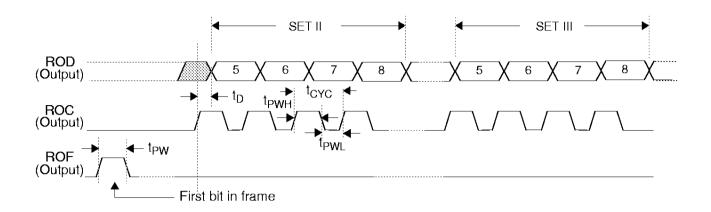

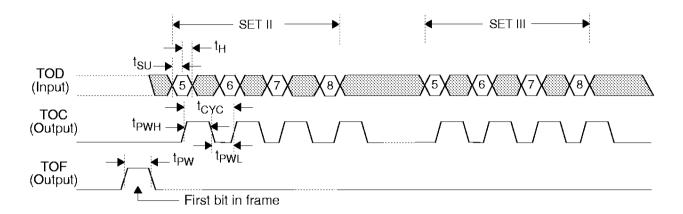

The service bits are defined as bits 11 and 12 for G.742 and G.751, as listed in Figure 2. The service bits for G.745 and G.753 are defined as bits 5 through 8 in sets II and III. The receive service bit interface consists of the following signals: data output signal (ROD), clock output signal (ROC), and framing pulse (ROF). The clock signal (ROC) is gapped and is provided for clocking out the service bits. The service bit states are also written by the Interpreter Block into E2/E3F memory locations, which can be read by the microprocessor if the signaling rate is low.

| G.742        |     |      |         |          |      |         |     |                   |               |         |      |                   |

|--------------|-----|------|---------|----------|------|---------|-----|-------------------|---------------|---------|------|-------------------|

| 1            | 11  | 12   | 21      | 2(Set I) | 42   | 24(II)  |     |                   | 636           | (III)   | 844  | 848(IV)           |

| 1111010000   | s   | s    | DATA    |          | DATA |         |     | DATA              |               | DATA    |      | BIP-4 if selected |

| G.745        |     | 00   | 441) 00 | 0 070    | 500  | (II) E. |     | 0.0               | 70            | 10/III) | 405  | 4050(00           |

| 1            |     | 26   | 4(I) 26 | 8 272    | 528  | (II) 53 | 2 5 | 36                | 79            | 92(III) | 105  | 2 1056(IV)        |

| 11100110     | DA٦ | Α    | jc      | S        | DATA | jc      | s   | DATA              | 4             | DATA    |      | BIP-4 if selected |

| G.751        | 11  | 12   | 38      | 4(Set I) | 70   | 68(II)  |     |                   | 115           | 2(III)  | 153: | 2 1536(IV)        |

| 1111010000   | S   | s    | DATA    |          | DATA |         |     | DATA              |               | DATA    |      | BIP-4 if selected |

| G.753        |     |      | 716(l)  | 720      | 724  |         | 143 | 2(II) <b>1</b> 43 | 36 <b>1</b> 4 | 40      | 214  | 4 2148(III)       |

| 111110100000 |     | DAT. | Α .     | jc s     |      | ATA     |     | jc                | s             | DATA    |      | BIP-4 if selected |

#### Note:

- 1. The leading segment of the frame (starting at bit 1) is the frame alignment signal pattern.

- 2. s indicates the service bits.

- jc indicates four justification control bits. In sets where DATA is not preceded by service bits, the first 4 or 8 bits of DATA may be associated with justification.

| Specifications | Service Bits                                    | No. of Bits in<br>Frame | Frame Alignment<br>Signal Pattern | Bit Rate<br>(kbit/s) |

|----------------|-------------------------------------------------|-------------------------|-----------------------------------|----------------------|

| G.742          | 11,12                                           | 848                     | 1111010000                        | 8448                 |

| G.745          | 5-8 Set II (269-272)<br>5-8 Set III (533-536)   | 1056                    | 11100110                          | 8448                 |

| G.751          | 11,12                                           | 1536                    | 1111010000                        | 34368                |

| G.753          | 5-8 Set II (721-724)<br>5-8 Set III (1437-1440) | 2148                    | 111110100000                      | 34368                |

Figure 2. G.7XX Frame Contents Summary

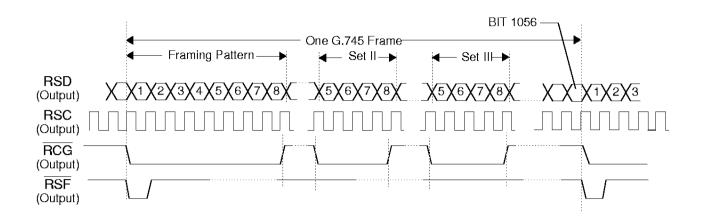

The E2/E3F terminal side Output Block provides either a bit-serial or a nibble-parallel interface. The interface is selected by an external control lead (SER) or by setting a control bit in the memory map. The bit-serial interface consists of the following signals: a data output signal (RSD), a clock output signal (RSC), a receive clock gapped output signal (RCG), and a framing pulse (RSF). The receive clock gapped signal (RCG) is active low during the framing and service bit times. The nibble-parallel interface consists of the following signals: a data output signal having a nibble format (RNIB3 through RNIB0), a clock output signal (RNC), and a framing pulse (RNF). Signal leads are shared for the two interfaces (RSD and RNIB3, RSC and RNC, RSF and RNF) and with the transmit reference generator, which is used in the serial mode only. The RNIB3 bit corresponds to the first bit received in a four-bit bit-serial stream segment. In the nibble mode, the framing pattern, service bits and BIP-4 nibble are not provided at the interface. The receive nibble clock (RNC) is gapped during framing pattern, service bit and BIP-4 times.

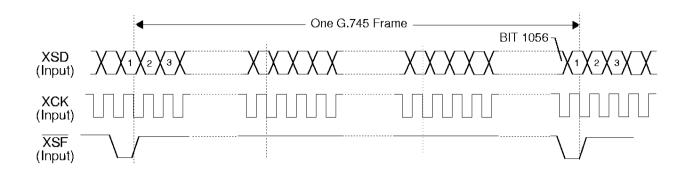

The transmitter operates independently of the receiver, unless the loop timing feature is selected. When the loop timing feature is selected, the receive clock becomes the transmitted clock. In the transmit direction, the terminal side bit-serial interface consists of the following signals: a data input signal (XSD), a clock input signal (XCK), and a framing pulse  $(\overline{XSF})$ . The nibble-parallel interface consists of the following signals: a data input signal having a nibble format (XNIB3 - XNIB0), a clock input signal (XCK), a framing output pulse  $(\overline{XNF})$ , and a nibble output clock signal (XNC). The leads are shared between the two interfaces and with the E2/E3F transmit reference generator in order to minimize the pin count. The XNIB3 bit corresponds to the first bit transmitted in a four-bit bit-serial stream segment. The transmit nibble clock (XNC) is stretched to accommodate the framing pattern, service bit and BIP-4 times. The E2/E3F also detects loss of clock (TLOC) whether the input clock is stuck high or low.

The transmitter has control leads for BIP-4 generation (BIP-4) and inserting AIS (TAIS). When the E2/E3F is operating with a microprocessor, the BIP-4 and AIS functions are controlled by the microprocessor. When the BIP-4 option is selected, the BIP-4 is transmitted as the last nibble in the frame format, as shown in Figures 2 and 3.

Figure 3. G.745 BIP-4 Location

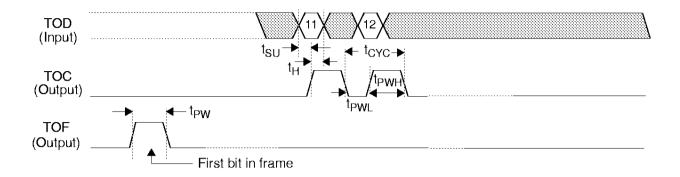

The transmitted service bits are inserted into the frame format from either an external interface or from memory map locations. The transmit service bit interface consists of the following signals: a data in signal (TOD), a clock output signal (TOC), and a framing pulse (TOF).

To facilitate transmit side multiplexing while operating in the bit-serial mode, the E2/E3F provides a transmit frame reference generator. The transmit frame reference generator accepts an external 8.448 or 34.368 MHz clock signal (TCIN) and produces a clock out signal (TCOUT), a framing pulse (TFOUT), a clock gap signal (TCG), and a data signal (TDOUT). The data signal consists of G.7XX framing bits and zeros elsewhere. The purpose of the transmit reference signals is to fix the transmit time-base for the terminal payload multiplexer circuitry.

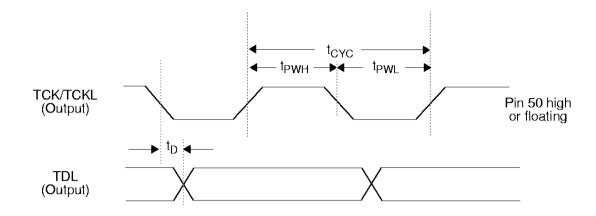

The selection of the transmit line interface, rail or NRZ, is controlled by the state present on the NRZLINE control lead, which also controls the receive interface selection. When the internal HDB3 Encoder Block is bypassed, the transmit line interface consists of a data signal (TDL) and a clock signal (TCKL). When the HDB3 encoder is enabled, the transmit line interface consists of positive (TP) and negative (TN) rail signals and a clock signal (TCK). The TCK/TCKL clock may be inverted by setting TLCINV low.

Input pins are provided for activating terminal loopback (TLBK) and payload loopback (PLBK).

A high placed on the microprocessor control lead (MICRO) selects the microprocessor interface. All the external control leads, except the loop timing (LPT), receive AIS disable (DAIS), and the line interface (NRZLINE) control leads are disabled when the microprocessor interface is selected. The E2/E3F provides pull-up resistors for the active low control leads.

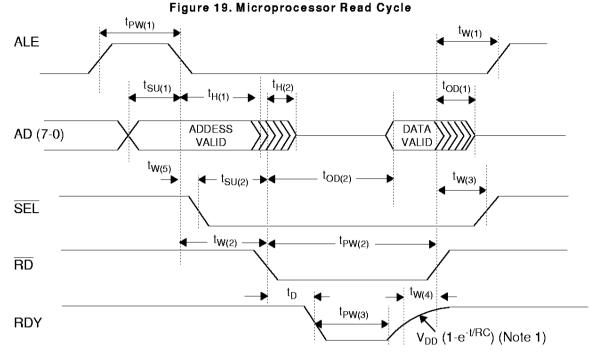

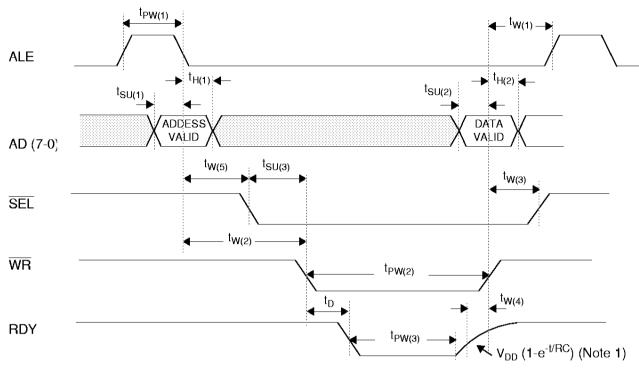

The microprocessor interface consists of eight bidirectional data and address leads (AD7 - AD0), along with four microprocessor control input leads and a ready (RDY) output signal.

#### **PIN DIAGRAM**

Figure 4. E2/E3F TXC-03701B Pin Diagram

#### PIN DESCRIPTIONS

#### **POWER SUPPLY AND GROUND**

| Symbol | Pin No.     | I/O/P* | Type | Name/Function                       |

|--------|-------------|--------|------|-------------------------------------|

| VDD    | 1,17,35,51  | Р      |      | VDD: +5-volt supply voltage, +/- 5% |

| GND    | 18,34,52,68 | Р      |      | Ground: 0 volts reference.          |

\*Note: I = Input; O = Output; P = Power

## LINE SIDE RECEIVE SIGNALS

| Symbol   | Pin No. | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RP/RDL   | 2       | I     | TTLp   | Receive Positive Rail/Receive NRZ Data: Positive rail input data is clocked into the E2/E3F on negative transitions of the clock signal RCK/RCKL. The HDB3 codec for rail operation is enabled by applying a low to the NRZLINE signal lead. Receive NRZ data is clocked into the E2/E3F on positive transitions of the clock signal RCK/RCKL. The NRZ mode is enabled by applying a high to the NRZLINE signal lead. |

| RN       | 3       | I     | TTLp   | Receive Negative Rail Data: Negative rail input data is clocked into the E2/E3F on negative transitions of the clock signal RCK/RCKL. The HDB3 codec for rail operation is enabled by applying a low to the NRZ-LINE signal lead.                                                                                                                                                                                     |

| RCK/RCKL | 4       | I     | TTLp   | Receive Clock Rail/NRZ: The receive clock is used for clocking in the rail/NRZ data signals and is used as the time base for receiver operation.                                                                                                                                                                                                                                                                      |

## LINE SIDE TRANSMIT SIGNALS

| Symbol   | Pin No. | I/O/P | Type   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|---------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TP/TDL   | 31      | 0     | TTL8mA | Transmit Positive Rail/Transmit NRZ Data: Positive rail data is clocked out of the E2/E3F on positive transitions of the clock signal TCK/TCKL when pin 50 is high and on negative transitions of the clock when pin 50 is low. The HDB3 codec for rail operation is enabled by applying a low to the NRZLINE signal lead. Transmit NRZ data is clocked out of the E2/E3F on negative transitions of the clock signal TCK/TCKL. The NRZ mode is enabled by applying a high to the NRZLINE signal lead. |

| TCK/TCKL | 32      | 0     | TTL8mA | Transmit Clock Rail/NRZ: The transmit clock is used for clocking out the rail/NRZ data signals. The TCK/TCKL clock signal is derived from the XCK clock. Note: When XCK is removed, the framer then uses TCIN to generate TCK/TCKL (in serial mode only). If both XCK and TCIN are removed, TCK/TCKL is derived from RCK/RCKL. This clock may be inverted by using control pin 50 (TLCINV).                                                                                                            |

| TN       | 33      | 0     | TTL8mA | Transmit Negative Rail Data: Negative rail output data is clocked out of the E2/E3F on positive transitions of the clock signal TCK/TCKL when pin 50 is high and on negative transitions of the clock when pin 50 is low. The HDB3 codec for rail operation is enabled by applying a low to the NRZLINE signal lead.                                                                                                                                                                                   |

<sup>\*</sup> Note: See Input, Output and I/O Parameters section for Type definitions.

# TERMINAL INTERFACE SIGNALS

| Symbol          | Pin No. | I/O/P | Type   | Name/Function                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCG             | 61      | 0     | TTL4mA | Receive Clock Gapped: An active low signal which indicates the receive framing and service bit locations. The RCG signal is provided in the serial mode only.                                                                                                                                                                               |

| RNF/RSF         | 62      | 0     | TTL4mA | Receive Framing Pulse: This active low framing pulse is synchronous with the last data nibble RNIB(3-0) for the terminal side nibble-parallel interface, and with the first bit in the frame for the bit-serial interface.                                                                                                                  |

| RNIB3/RSD       | 63      | 0     | TTL4mA | Receive Nibble Bit 3/Receive Serial Data: Bit 3 is the most significant bit in the nibble and corresponds to the first bit received in the nibble. The framing pattern, service bits, and BIP-4 nibble are not provided as parallel data. In the serial mode, all bits, including the framing pattern and service bits, are provided.       |

| RNIB2/<br>TDOUT | 64      | 0     | TTL4mA | Receive Nibble Bit 2/Transmit Reference Generator Data Output: Bit 2 in nibble mode. The reference generator is enabled in the serial mode. The output data signal consists of all ones in place of the framing bits and zeros elsewhere in the frame. The TDOUT signal is generated from the input clock (TCIN).                           |

| RNIB1/TCG       | 65      | 0     | TTL4mA | Receive Nibble Bit 1/Transmit Reference Generator Clock Gap Signal: Bit 1 in nibble mode. The reference generator is enabled in the serial mode. The active low TCG signal indicates the location of the framing pattern and the service bits in the frame. The TCG signal is generated from the input clock (TCIN).                        |

| RNIB0/<br>TFOUT | 66      | 0     | TTL4mA | Receive Nibble Bit 0/Transmit Reference Generator Framing Pulse: Bit 0 is the least significant bit in the nibble and is the last bit received. The reference generator is enabled in the serial mode. The active low TFOUT signal is one clock cycle (TCOUT) wide, and is synchronous with the first bit in the frame.                     |

| RNC/RSC         | 67      | 0     | TTL4mA | Receive Nibble Clock/Receive Serial Clock: The nibble and serial clocks are derived from the line side rail/NRZ clock signal (RCK/RCKL). A received nibble is clocked out on positive transitions of RNC. RNC is gapped during framing pattern, service bit and BIP-4 bit times. Serial data is clocked out on positive transitions of RSC. |

| Symbol     | Pin No. | I/O/P | Type | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|---------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XNIB3/XSF  | 53      |       | ПГР  | Transmit Nibble Bit 3/Transmit Serial Framing Pulse: For the terminal side parallel interface, bit 3 in the transmitted nibble is the most significant bit and corresponds to the first bit transmitted in the nibble. When the terminal interface is serial, the negative framing pulse is synchronous with the first bit in the frame. It is recommended that the framing pulse (TFOUT) and other signals generated by the transmit reference generator be used as the transmit framing pulse, and for multiplexing the data into the frame.                                                                                                                                       |

| XNIB2      | 54      | I     | ПLр  | Transmit Nibble Bit 2: Bit 2 in the transmit nibble.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XNIB1/TCIN | 55      |       | ПГР  | Transmit Nibble Bit 1/Transmit Reference Generator Clock In: Bit 1 in the transmit nibble. For a serial interface, the reference clock (TCIN) is used to derive the clock out (TCOUT), data signal (TDOUT), framing pulse (TFOUT), and gapped clock signal (TCG). The reference generator signals are provided for multiplexing the external payload data into the serial frame. The E2/E3F requires a transmit clock having a frequency of 8448 kHz with a stability of +/- 30 ppm to meet the clock tolerance specified in ITU-TSS Recommendations G.742 and G.745. For Recommendations G.751 and G.753, the required clock frequency is 34368 kHz with a stability of +/- 20 ppm. |

| XNIB0/XSD  | 56      | I     | TTLp | Transmit Nibble Bit 0/Transmit Serial Data: For the terminal side parallel interface, bit 0 is the least significant bit in the nibble and the last bit from the nibble that is transmitted. For a serial interface, the input must consist of all the bits in the frame. The E2/E3F inserts a new framing pattern and the service bits (from the external interface or the memory map) into the transmit data stream determined by the location of the framing pulse (XSF).                                                                                                                                                                                                         |

| XCK        | 57      |       | ПЦρ  | Transmit Clock: For the terminal side parallel interface, the transmit clock is used for all transmit timing functions, including deriving the nibble output clock (XNC) and framing pulse (XNF). The E2/E3F requires a transmit clock having a frequency of 8448 kHz with a stability of +/- 30 ppm to meet the clock tolerance specified in ITU-TSS Recommendations G.742 and G.745. For Recommendations G.751 and G.753, the required clock frequency is 34368 kHz with a stability of +/- 20 ppm. For the serial interface, this clock may be derived from the transmit reference generator clock output (TCOUT). The duty cycle must be 50 ± 5%.                                |

| Symbol    | Pin No. | I/O/P | Type   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XNF       | 58      | 0     | TTL4mA | Transmit Nibble Framing Pulse: The nibble framing pulse and clock signal (XNC) are provided for multiplexing nibble data into the E2/E3F from external circuitry. The negative framing pulse identifies the first bit in the frame.                                                                                                                                                                                         |

| XNC/TCOUT | 59      | 0     | TTL8mA | Transmit Nibble Clock/Transmit Reference Generator Clock Out: The nibble clock is derived from the transmit clock (XCK) and is used as a time base for clocking data out of the external multiplexer and into the E2/E3F. XNC is gapped during the framing pattern, service bit and BIP-4 bit times. Data is clocked in on positive transitions. TCOUT is derived from the input clock (TCIN), and has the same duty cycle. |

# SERVICE BIT INTERFACE SIGNALS

| Sym bol | Pin No. | I/O/P | Type   | Name/Function                                                                                                                                                                                                                                                                                       |

|---------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROD     | 9       | 0     | TTL8mA | Receive Service Data Bits: The service bits for the G.742 and G.751 recommendations are defined as bits 11 and 12. For the G.745 and G.753 recommendations, the service bits are defined as 5 through 8 in Sets II and III.                                                                         |

| ROC     | 10      | 0     | TTL8mA | Receive Service Bits Clock: A gapped clock that clocks out the service bits on positive transitions.                                                                                                                                                                                                |

| ROF     | 11      | 0     | TTL8mA | Receive Service Bits Framing Pulse: A positive framing pulse that is synchronous with the first bit in the frame.                                                                                                                                                                                   |

| TOD     | 27      | ı     | TTLp   | Transmit Service Data Bits: The service bits for G.742 and G.751 are bits 11 and 12. For G.745 and G.753, the service bits are 5 through 8 in Sets II and III. When the E2/E3F is configured to work with a microprocessor, bit 0 (OHI/O) in location 00H must be written with a one to enable TOD. |

| TOC     | 28      | 0     | TTL8mA | Transmit Service Bits Clock: A gapped clock that clocks in the service bits on positive transitions. The clock is active only for clocking in the transmit service data bits (TOD).                                                                                                                 |

| TOF     | 29      | 0     | TTL8mA | Transmit Service Bits Framing Pulse: A positive framing pulse that is synchronous with the first bit in the frame.                                                                                                                                                                                  |

## MICROPROCESSOR INTERFACE SIGNALS

| Symbol  | Pin No. | I/O/P | Туре              | Name/Function                                                                                                                                                                                                       |

|---------|---------|-------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD(7-0) | 36-43   | I/O   | TTL I/O           | Address/Data Bus: These leads constitute the time-multiplexed address and data bus for accessing the registers which reside in the E2/E3F. Only AD(2-0) are required for address input.                             |

| SEL     | 44      | I     | TTLp              | Select: A low enables the microprocessor to access the E2/E3F memory map for control, status, and alarm information (Note 1).                                                                                       |

| ALE     | 45      | I     | TTLp              | Address Latch Enable: An active high signal generated by the microprocessor. Used by the microprocessor to hold an address stable during a read/write bus cycle (Note 1).                                           |

| RD      | 46      | I     | TTLp              | <b>Read:</b> An active low signal generated by the microprocessor for reading the registers which reside in the memory map. The E2/E3F memory map is selected by placing a low on the select lead (Note 1).         |

| WR      | 47      | I     | TTLp              | Write: An active low signal generated by the micro-<br>processor for writing to the registers which reside in<br>the memory map. The E2/E3F memory map is<br>selected by placing a low on the select lead (Note 1). |

| RDY     | 48      | 0     | TTL<br>Open Drain | Ready: An active high is an E2/E3F acknowledgment to the microprocessor that the addressed memory map location can complete the data transfer.                                                                      |

<sup>\*</sup>Note 1: When MICRO (pin 19) is tied low, the microprocessor interface is disabled. This microprocessor interface input pin has an internal pull-up resistor and can be left open.

# CONTROL SIGNALS

| Symbol  | Pin No. | I/O/P | Type | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NRZLINE | 13      | I     | ТТЬр | Non-Return to Zero Line Selection: A high enables an NRZ line interface (RP/TP), and causes the HDB3 decoder/encoder to be bypassed. An active low enables the rail interface (RP/RN, and TP/TN) and the HDB3 decoder/encoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIP-4   | 14      | I     | ПLр  | Bit Interleaved Parity - 4: A high enables the BIP-4 function. In the transmit direction, the BIP-4 is calculated for data nibbles only, and is sent as the last nibble in the frame format. In the receive direction, the BIP-4 is calculated for the data bits only and compared against the received value which is present in the last four bits of the frame. An output indication (BIP-4E) occurs when one or more columns do not match. A BIP-4 error mask is provided in the memory map which permits up to four errors to be transmitted. At the terminal interface, the transmit and receive nibble clocks are gapped to accommodate the time that corresponds to the BIP-4 nibble. |

| Sym bol  | Pin No.  | I/O/P | Type | Name/Function                                                                                                                                                                                                                                                                                                                                              |          |                                                                          |                   |  |  |  |

|----------|----------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|-------------------|--|--|--|

| M1<br>M0 | 16<br>15 | I     | ПLр  |                                                                                                                                                                                                                                                                                                                                                            |          | The two controls selected according to the ta                            |                   |  |  |  |

|          |          |       |      | M1                                                                                                                                                                                                                                                                                                                                                         | МО       | Recommendation                                                           | Rate (kbit/s)     |  |  |  |

|          |          |       |      | low                                                                                                                                                                                                                                                                                                                                                        | low      | G.745                                                                    | 8448              |  |  |  |

|          |          |       |      | low                                                                                                                                                                                                                                                                                                                                                        | high     | G.742                                                                    | 8448              |  |  |  |

|          |          |       |      | high                                                                                                                                                                                                                                                                                                                                                       | low      | G.753                                                                    | 34368             |  |  |  |

|          |          |       |      | high                                                                                                                                                                                                                                                                                                                                                       | high     | G.751                                                                    | 34368             |  |  |  |

| MICRO    | 19       | ı     | ΠLp  | Microprocessor Mode: A high enables the microprocessor interface. When the microprocessor is enabled the following hardware control leads are disabled: BIP 4, Mode (M0 and M1), Serial I/O (SER), and transmit AIS (TAIS). Bits are provided in Address 00H of the memory map for controlling these functions. These bits are inactive when MICRO is low. |          |                                                                          |                   |  |  |  |

| SER      | 20       | ı     | ПLр  |                                                                                                                                                                                                                                                                                                                                                            | rminal s | : A high selects the bi<br>side interface. A low s<br>s.                 |                   |  |  |  |

| TLBK     | 21       | I     | TTLp | <b>Terminal Loopback:</b> A low enables a transmit-to-receive loopback at the line side.                                                                                                                                                                                                                                                                   |          |                                                                          |                   |  |  |  |

| PLBK     | 22       | ı     | ТТLр | Payload Loopback: A low enables a receive-to-transmit loopback at the terminal side in the serial mode of operation only.                                                                                                                                                                                                                                  |          |                                                                          |                   |  |  |  |

| TAIS     | 23       | ı     | TTLp |                                                                                                                                                                                                                                                                                                                                                            |          | Indication Signal: A ) to be sent in place o                             |                   |  |  |  |

| <u> </u> | 24       | I     | TTLp | Loop timi                                                                                                                                                                                                                                                                                                                                                  | ing disa | low enables the loop<br>bles the transmit clocl<br>be used as the transn | k and enables the |  |  |  |

| FORCEFE  | 26       | I     | TTLp |                                                                                                                                                                                                                                                                                                                                                            | into the | Error: An errored frar transmit framing patte                            |                   |  |  |  |

| RESET    | 30       | I     | ΠLp  | Reset: A positive pulse having a duration of at least 10 transmit clock cycles (XCK) applied to this pin resets the internal counters, logic circuits, and the performance counters and control bits in the memory map to zero. The reset pulse is applied after the power becomes stable.                                                                 |          |                                                                          |                   |  |  |  |

| DAIS     | 49       | I     | TTLp | Disable AIS: A low disables the automatic insertion of AIS into the terminal side receive nibble/serial bit stream.                                                                                                                                                                                                                                        |          |                                                                          |                   |  |  |  |

| TLCINV   | 50       | I     | TTLp | Transmit Line Clock Invert: A low inverts the output clock TCK/TCKL when operating in the P and N rail mode.                                                                                                                                                                                                                                               |          |                                                                          |                   |  |  |  |

# STATUS AND ALARM SIGNALS

| Symbol | Pin No. | I/O/P | Туре   | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CV     | 5       | 0     | TTL8mA | Coding Violation: A positive pulse, one clock cycle wide, is generated when an illegal coding violation is detected. A coding violation is not part of the HDB3 zero-substitution code. A CV occurs because of noise or other impairments occurring on the line. This output is only valid in the P and N rail mode of operation.                                                                                                                                                                                                                                                                                                                                                                                                            |

| RAIS   | 6       | 0     | TTL8mA | Receive Alarm Indication Signal: An active low alarm occurs within one millisecond after the E2/E3F detects an all ones condition, including in the presence of a 10 <sup>-5</sup> bit error rate. An incoming signal with a framing pattern and all ones in the data field is not mistaken as an AIS.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RLOC   | 7       | 0     | TTL8mA | Receive Loss of Clock: An active low alarm occurs when there are no transitions in the received clock (RCK/RCKL) for 10 clock cycles. Recovery occurs on the first clock transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RLOF   | 8       | 0     | TTL8mA | Receive Loss of Frame: An active low alarm occurs when frame cannot be detected in the following modes and conditions:  G.742: Four consecutive frames lost. Recovery occurs when three consecutive frames are detected. The framing pattern is 1111010000 (10-bit pattern).  G.745: Five consecutive frames lost. Recovery occurs when two consecutive frames are detected. The framing pattern is 11100110 (8-bit pattern).  G.751: Four consecutive frames lost. Recovery occurs when three consecutive frames are detected. The framing pattern is 1111010000 (10-bit pattern).  G.753: Three consecutive frames lost. Recovery occurs when three consecutive frames are detected. The framing pattern is 111110100000 (12-bit pattern). |

| FE     | 12      | 0     | TTL8mA | Framing Error: An active high alarm occurs when one or more framing bits are in error. The framing error alarm occurs at the end of the framing pattern and remains high until an error-free framing pattern is received or a loss of frame occurs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TLOC   | 25      | 0     | TTL8mA | Transmit Loss of Clock: An active low alarm occurs when there are no transitions in the transmit clock (TCK) for 10 clock cycles. Recovery occurs on the first clock transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BIP-4E | 60      | 0     | TTL8mA | <b>BIP-4E:</b> A positive pulse occurs when the comparison between the received BIP-4 value and the calculated value does not match in a column.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol          | Min * | Max *                 | Unit  |

|--------------------------------|-----------------|-------|-----------------------|-------|

| Supply voltage                 | V <sub>DD</sub> | -0.3  | +7.0                  | V     |

| DC input voltage               | V <sub>IN</sub> | -0.5  | V <sub>DD</sub> + 0.5 | V     |

| Continuous power dissipation   | P <sub>C</sub>  |       | 1                     | Watts |

| Ambient operating temperature  | T <sub>A</sub>  | -40   | +85                   | °C    |

| Operating junction temperature | T <sub>J</sub>  |       | 150                   | °C    |

| Storage temperature range      | T <sub>S</sub>  | -55   | 150                   | °C    |

<sup>\*</sup>Note: Operating conditions exceeding those listed in Absolute Maximum Ratings may cause permanent failure. Exposure to absolute maximum ratings for extended periods may impair device reliability.

# THERMAL CHARACTERISTICS

| Param eter                               | Min | Тур | Max | Unit | Test Conditions         |

|------------------------------------------|-----|-----|-----|------|-------------------------|

| Thermal resistance - junction to ambient |     | 46  | 48  | °C/W | 0 ft/min linear airflow |

| Thermal resistance - junction to case    |     |     | 12  | °C/W | 0 ft/min linear airflow |

# **POWER REQUIREMENTS**

| Param eter      | Min  | Тур | Max  | Unit       | Test Conditions  |

|-----------------|------|-----|------|------------|------------------|

| $V_{DD}$        | 4.75 | 5.0 | 5.25 | V          |                  |

| I <sub>DD</sub> |      |     | 125  | m <b>A</b> |                  |

| P <sub>DD</sub> |      |     | 675  | m <b>W</b> | Inputs switching |

# THROUGHPUT DELAYS

## **E2**

| Path                                | Delay (bit times) |

|-------------------------------------|-------------------|

| Rx line input to Rx terminal output | TBD               |

| Tx terminal input to Tx line output | TBD               |

| Path                                | Delay (bit times) |

|-------------------------------------|-------------------|

| Rx line input to Rx terminal output | TBD               |

| Tx terminal input to Tx line output | TBD               |

# INPUT, OUTPUT AND I/O PARAMETERS

# INPUT PARAMETERS FOR TTLp

| Param eter            | Min | Тур   | Max | Unit | Test Conditions              |

|-----------------------|-----|-------|-----|------|------------------------------|

| V <sub>IH</sub>       | 2.0 |       |     | ٧    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| V <sub>IL</sub>       |     |       | 0.8 | ٧    | 4.75 ≤V <sub>DD</sub> ≤ 5.25 |

| Input leakage current |     | -70.0 |     | μA   |                              |

| Input capacitance     |     | 4.0   |     | рF   |                              |

Note: Input has a 72k (nominal) internal pull-up resistor.

#### **OUTPUT PARAMETERS FOR TTL4m A**

| Param eter        | Min | Тур | Max  | Unit       | Test Conditions                   |

|-------------------|-----|-----|------|------------|-----------------------------------|

| V <sub>OH</sub>   | 2.4 |     |      | V          | $V_{DD} = 4.75; I_{OH} = 4.0$     |

| V <sub>OL</sub>   |     |     | 0.5  | V          | $V_{DD} = 4.75$ ; $I_{OL} = -4.0$ |

| I <sub>OL</sub>   |     |     | -4.0 | m <b>A</b> |                                   |

| I <sub>OH</sub>   |     |     | 4.0  | mA         |                                   |

| t <sub>RISE</sub> |     | 1.2 |      | ns         | C <sub>LOAD</sub> = 15 pF         |

| t <sub>FALL</sub> |     | 1.7 |      | ns         | C <sub>LOAD</sub> = 15 pF         |

# **OUTPUT PARAMETERS FOR TTL8m A**

| Param eter        | Min | Тур | Max  | Unit       | Test Conditions                               |

|-------------------|-----|-----|------|------------|-----------------------------------------------|

| V <sub>OH</sub>   | 2.4 |     |      | V          | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = 8.0 |

| V <sub>OL</sub>   |     |     | 0.5  | V          | $V_{DD} = 4.75$ ; $I_{OL} = -8.0$             |

| I <sub>OL</sub>   |     |     | -8.0 | m <b>A</b> |                                               |

| I <sub>OH</sub>   |     |     | 8.0  | m <b>A</b> |                                               |

| t <sub>RISE</sub> |     | 2.0 |      |            | C <sub>LOAD</sub> = 15 pF                     |

| t <sub>FALL</sub> |     | 1.9 |      | ns         | C <sub>LOAD</sub> = 15 pF                     |

# OUTPUT PARAMETERS FOR TTL OPEN DRAIN

| Param eter        | Min | Тур  | Max  | Unit       | Test Conditions                   |

|-------------------|-----|------|------|------------|-----------------------------------|

| $V_{OL}$          |     |      | 0.5  | V          | $V_{DD} = 4.75$ ; $I_{OL} = -8.0$ |

| I <sub>OL</sub>   |     |      | -8.0 | m <b>A</b> |                                   |

| t <sub>FALL</sub> |     | 11.0 |      | ns         | C <sub>LOAD</sub> = 15 pF         |

Note: V<sub>OH</sub>, I<sub>OH</sub> and t<sub>RISE</sub> will depend on external resistance and capacitance.

# INPUT/OUTPUT PARAMETERS FOR TTL I/O

| Param eter            | Min | Тур   | Max  | Unit | Test Conditions                                   |

|-----------------------|-----|-------|------|------|---------------------------------------------------|

| V <sub>IH</sub>       | 2.0 |       |      | V    | 4.75 <u>&lt;</u> V <sub>DD</sub> <u>&lt;</u> 5.25 |

| $V_{IL}$              |     |       | 0.8  | V    | 4.75 ≤V <sub>DD</sub> ≤ 5.25                      |

| Input leakage current |     | -70.0 |      | μА   |                                                   |

| Input capacitance     |     | 7.1   |      | pF   |                                                   |

| V <sub>OH</sub>       | 2.4 |       |      | V    | $V_{DD} = 4.75$ ; $I_{OH} = 8.0$                  |

| V <sub>OL</sub>       |     |       | 0.5  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = -8.0    |

| I <sub>OL</sub>       |     |       | -8.0 | mA   |                                                   |

| Гон                   |     |       | 8.0  | mA   |                                                   |

| † <sub>RISE</sub>     |     | 3.3   |      | ns   | $C_{LOAD} = 15 \text{ pF}$                        |

| t <sub>FALL</sub>     |     | 7.9   |      | ns   | $C_{LOAD} = 15 \text{ pF}$                        |

## TIMING CHARACTERISTICS

Detailed timing diagrams for the E2/E3F are illustrated in Figures 5 through 20, with values of the timing intervals tabulated below the diagrams. All output times are measured with a maximum 75 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or  $(V_{OH} + V_{OL})/2$  for output signals.

RCKL (Input)

RDL (Input)

Figure 5. Line Side Receive NRZ Timing

#### **E3**

| Param eter                | Symbol           | Min  | Тур  | Max | Unit |

|---------------------------|------------------|------|------|-----|------|

| RCKL clock period         | tcyc             | 29.0 |      |     | ns   |

| RCKL high time            | t <sub>PWH</sub> | 12.1 | 14.6 |     | ns   |

| RCKL low time             | t <sub>PWL</sub> | 12.1 | 14.6 |     | ns   |

| RDL set-up time to RCKL↑  | t <sub>su</sub>  | 4.0  |      |     | ns   |

| RDL hold time after RCKL1 | t <sub>H</sub>   | 4.0  |      |     | ns   |

| Parameter                 | Symbol           | Min   | Тур  | Max | Unit |

|---------------------------|------------------|-------|------|-----|------|

| RCKL clock period         | tcyc             | 116.0 |      |     | ns   |

| RCKL high time            | t <sub>PWH</sub> | 46.0  | 59.2 |     | ns   |

| RCKL low time             | t <sub>PWL</sub> | 46.0  | 59.2 |     | ns   |

| RDL set-up time to RCKL↑  | t <sub>SU</sub>  | 4.0   |      |     | ns   |

| RDL hold time after RCKL1 | t <sub>H</sub>   | 4.0   |      |     | ns   |

Figure 6. Line Side Transmit NRZ Timing

| Parameter             | Symbol           | Min  | Тур  | Max | Unit |

|-----------------------|------------------|------|------|-----|------|

| TCKL clock period     | tcyc             | 29.1 | 29.1 |     | ns   |

| TCKL high time        | t <sub>PWH</sub> | 13.1 |      |     | ns   |

| TCKL low time         | t <sub>PWL</sub> | 13.1 |      |     | ns   |

| TDL delay after TCKL↓ | t <sub>D</sub>   |      |      | 7.0 | ns   |

| Param eter            | Symbol                  | Min   | Тур   | Max | Unit |

|-----------------------|-------------------------|-------|-------|-----|------|

| TCKL clock period     | toyo                    | 118.4 | 118.4 |     | ns   |

| TCKL high time        | t <sub>PWH</sub>        | 53.3  |       |     | ns   |

| TCKL low time         | † <sub>P<b>W</b>L</sub> | 53.3  |       |     | ns   |

| TDL delay after TCKL↓ | t <sub>D</sub>          |       |       | 7.0 | ns   |

Figure 7. Line Side Receive Rail Timing

| Parameter                  | Symbol           | Min  | Тур  | Max | Unit |

|----------------------------|------------------|------|------|-----|------|

| RCK clock period           | tcyc             | 29.0 |      |     | ns   |

| RCK high time              | t <sub>PWH</sub> | 12.1 | 14.6 |     | ns   |

| RCK low time               | t <sub>PWL</sub> | 12.1 | 14.6 |     | ns   |

| RP/RN set-up time to RCK↓  | t <sub>su</sub>  | 4.0  |      |     | ns   |

| RP/RN hold time after RCK↓ | t <sub>H</sub>   | 4.0  |      |     | ns   |

| P aram eter                | Symbol           | Min   | Тур  | Max | Unit |

|----------------------------|------------------|-------|------|-----|------|

| RCK clock period           | t <sub>CYC</sub> | 116.0 |      |     | ns   |

| RCK high time              | t <sub>PWH</sub> | 46.0  | 59.2 |     | ns   |

| RCK low time               | t <sub>PWL</sub> | 46.0  | 59.2 |     | ns   |

| RP/RN set-up time to RCK↓  | t <sub>SU</sub>  | 4.0   |      |     | ns   |

| RP/RN hold time after RCK↓ | t <sub>H</sub>   | 4.0   |      |     | ns   |

Figure 8. Line Side Transmit Rail Timing

| P aram eter                       | Symbol           | Min  | Тур  | Max  | Unit |

|-----------------------------------|------------------|------|------|------|------|

| TCK clock period                  | tcyc             | 29.1 | 29.1 |      | ns   |

| TCK high time                     | t <sub>PWH</sub> | 13.1 |      | 16.0 | ns   |

| TCK low time                      | t <sub>PWL</sub> | 13.1 |      | 16.0 | ns   |

| TP/TN delay after TCK active edge | t <sub>D</sub>   |      |      | 7.0  | ns   |

| Parameter                         | Symbol           | Min   | Тур   | Max  | Unit |

|-----------------------------------|------------------|-------|-------|------|------|

| TCK clock period                  | tcyc             | 118.4 | 118.4 |      | ns   |

| TCK high time                     | t <sub>PWH</sub> | 53.3  |       | 65.1 | ns   |

| TCK low time                      | t <sub>PWL</sub> | 53.3  |       | 65.1 | ns   |

| TP/TN delay after TCK active edge | t <sub>D</sub>   |       |       | 7.0  | ns   |

Figure 9. Transmit Reference Generator Timing

| Param eter                           | Symbol              | Min  | Тур                   | Max  | Unit |

|--------------------------------------|---------------------|------|-----------------------|------|------|

| TCIN clock period                    | t <sub>CYC(1)</sub> | 29.1 |                       |      | ns   |

| TCIN high time                       | t <sub>PWH(1)</sub> | 13.1 |                       |      | ns   |

| TCIN low time                        | t <sub>PWL(1)</sub> | 13.1 |                       |      | ns   |

| TCOUT clock period                   | t <sub>CYC(2)</sub> | 29.1 |                       |      | ns   |

| TCOUT high time                      | t <sub>PWH(2)</sub> | 13.1 |                       |      | ns   |

| TCOUT↑ delay after TCIN↓             | t <sub>D(1)</sub>   |      |                       | 15.0 | ns   |

| TDOUT, TFOUT, TCG delay after TCOUT↑ | t <sub>D(2)</sub>   |      |                       | 7.0  | ns   |

| TFOUT pulse width                    | t <sub>PW</sub>     |      | 1 t <sub>CYC(1)</sub> |      | ns   |

| Param eter Param eter                | Symbol                 | Min   | Тур                   | Max  | Unit |

|--------------------------------------|------------------------|-------|-----------------------|------|------|

| TCIN clock period                    | t <sub>CYC(1)</sub>    | 118.4 | 118.4                 |      | ns   |

| TCIN high time                       | t <sub>PWH(1)</sub>    | 53.3  |                       |      | ns   |

| TCIN low time                        | t <sub>PWL(1)</sub>    | 53.3  |                       |      | ns   |

| TCOUT clock period                   | t <sub>CYC(2)</sub>    | 118.4 |                       |      | ns   |

| TCOUT high time                      | t <sub>PWH(2)</sub>    | 53.3  |                       |      | ns   |

| TCOUT↑ delay after TCIN↓             | t <sub>D(1)</sub>      |       |                       | 15.0 | ns   |

| TDOUT, TFOUT, TCG delay after TCOUT↑ | t <sub>D(2)</sub>      |       |                       | 7.0  | ns   |

| TFOUT pulse width                    | t <sub>P<b>W</b></sub> |       | 1 t <sub>CYC(1)</sub> |      | ns   |

RNC (Output)

RNIB(3-0) (Output)

N258

N259

N260

N1

RNF (Output)

Figure 10. Terminal Side Receive Nibble Timing

This waveform diagram shows a G.745 frame with the BIP-4 feature off. The gapped clock period corresponds to the 8-bit (two nibbles) framing pattern.

#### **E2**

| Parameter               | Symbol            | Min    | Тур | Max | Unit |

|-------------------------|-------------------|--------|-----|-----|------|

| RNC clock period        | t <sub>CYC</sub>  | 473.0  |     |     | ns   |

| RNC high time           | t <sub>PWH</sub>  | 213.0  |     |     | ns   |

| RNC low time            | t <sub>PWL</sub>  | 213.0  |     |     | ns   |

| RNIB delay after RNC1   | t <sub>D(1)</sub> |        |     | 7.0 | ns   |

| RNF delay after RNC1    | t <sub>D(2)</sub> |        |     | 7.0 | ns   |

| RNF pulse width (G.745) | t <sub>PW</sub>   | 947.0  |     |     | ns   |

| RNF pulse width (G.742) | t <sub>PW</sub>   | 1184.0 |     |     | ns   |

| Recommendation | BIP-4 On<br>Number of Nibbles | Bip-4 Off<br>Number of Nibbles | Nibble Rate<br>k nibbles/s |

|----------------|-------------------------------|--------------------------------|----------------------------|

| G.742          | 208                           | 209                            | 2112                       |

| G.745          | 259                           | 260                            | 2112                       |

| G.751          | 380                           | 381                            | 8592                       |

| G.753          | 531                           | 532                            | 8592                       |

| Parameter               | Symbol            | Min   | Тур | Max | Unit |

|-------------------------|-------------------|-------|-----|-----|------|

| RNC clock period        | tcyc              | 116.4 |     |     | ns   |

| RNC high time           | t <sub>PWH</sub>  | 52.4  |     |     | ns   |

| RNC low time            | t <sub>PWL</sub>  | 52.4  |     |     | ns   |

| RNIB delay after RNC1   | t <sub>D(1)</sub> |       |     | 7.0 | ns   |

| RNF delay after RNC1    | t <sub>D(2)</sub> |       |     | 7.0 | ns   |

| RNF pulse width (G.753) | t <sub>PW</sub>   | 349.0 |     |     | ns   |

| RNF pulse width (G.751) | t <sub>PW</sub>   | 291.0 |     |     | ns   |

Figure 11. Terminal Side Transmit Nibble Timing

This waveform diagram shows a G.745 frame with the BIP-4 feature on and off. The gapped clock period corresponds to the 8-bit (two nibbles) framing pattern.

## E2

| Parameter                          | Symbol           | Min    | Тур | Max | Unit |

|------------------------------------|------------------|--------|-----|-----|------|

| XNC clock period                   | tcyc             | 473.0  |     |     | ns   |

| XNC high time                      | t <sub>PWH</sub> | 213.0  |     |     | ns   |

| XNC low time                       | t <sub>PWL</sub> | 213.0  |     |     | ns   |

| XNIB set-up time to XNC↑           | t <sub>SU</sub>  | 4.0    |     |     | ns   |

| XNIB hold time after XNC↑          | t <sub>H</sub>   | 4.0    |     |     | ns   |

| XNF output delay after XNC↑        | t <sub>OD</sub>  | 4.0    |     |     | ns   |

| XNF pulse width (BIP-4 off, G.745) | t <sub>PW</sub>  | 947.0  |     |     | ns   |

| XNF pulse width (BIP-4 off, G.742) | t <sub>PW</sub>  | 1184.0 |     |     | ns   |

| Parameter                          | Symbol           | Min   | Тур | Max | Unit |

|------------------------------------|------------------|-------|-----|-----|------|

| XNC clock period                   | t <sub>CYC</sub> | 116.4 |     |     | ns   |

| XNC high time                      | t <sub>PWH</sub> | 52.4  |     |     | ns   |

| XNC low time                       | t <sub>PWL</sub> | 52.4  |     |     | ns   |

| XNIB set-up time to XNC↑           | t <sub>SU</sub>  | 4.0   |     |     | ns   |

| XNIB hold time after XNC↑          | t <sub>H</sub>   | 4.0   |     |     | ns   |

| XNF output delay after XNC↑        | t <sub>OD</sub>  | 4.0   |     |     | ns   |

| XNF pulse width (BIP-4 off, G.753) | t <sub>PW</sub>  | 349.0 |     |     | ns   |

| XNF pulse width (BIP-4 off, G.751) | t <sub>PW</sub>  | 291.0 |     |     | ns   |

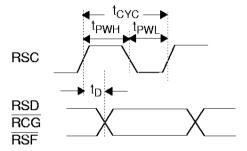

Figure 12. Terminal Side Receive Serial Timing

| Parameter                      | Symbol           | Min  | Тур  | Max | Unit |

|--------------------------------|------------------|------|------|-----|------|

| RSC clock period               | toyo             | 29.0 | 29.1 |     | ns   |

| RSC high time                  | t <sub>PWH</sub> | 11.5 |      |     | ns   |

| RSC low time                   | t <sub>PWL</sub> | 11.5 |      |     | ns   |

| RSD, RCG, RSF delay after RSC↑ | t <sub>D</sub>   |      |      | 7.0 | ns   |

| Parameter                      | Symbol           | Min   | Тур   | Max | Unit |

|--------------------------------|------------------|-------|-------|-----|------|

| RSC clock period               | t <sub>CYC</sub> | 116.0 | 118.4 |     | ns   |

| RSC high time                  | t <sub>PWH</sub> | 46.0  |       |     | ns   |

| RSC low time                   | t <sub>PWL</sub> | 46.0  |       |     | ns   |

| RSD, RCG, RSF delay after RSC↑ | t <sub>D</sub>   |       |       | 7.0 | ns   |

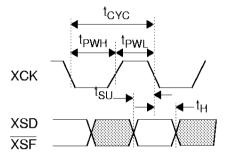

Figure 13. Terminal Side Transmit Serial Timing

| Parameter                               | Symbol           | Min  | Тур | Max | Unit |

|-----------------------------------------|------------------|------|-----|-----|------|

| XCK clock period                        | t <sub>CYC</sub> | 29.1 |     |     | ns   |

| XCK high time                           | t <sub>PWH</sub> | 13.1 |     |     | ns   |

| XCK low time                            | t <sub>PWL</sub> | 13.1 |     |     | ns   |

| XSD, <del>XSF</del> set-up time to XCK↓ | t <sub>SU</sub>  | 4.0  |     |     | ns   |

| XSD, XSF hold time after XCK↓           | t <sub>H</sub>   | 4.0  |     |     | ns   |

| Parameter                               | Symbol           | Min   | Тур | Max | Unit |

|-----------------------------------------|------------------|-------|-----|-----|------|

| XCK clock period                        | tcyc             | 118.4 |     |     | ns   |

| XCK high time                           | t <sub>PWH</sub> | 53.3  |     |     | ns   |

| XCK low time                            | t <sub>PWL</sub> | 53.3  |     |     | ns   |

| XSD, <del>XSF</del> set-up time to XCK↓ | t <sub>SU</sub>  | 4.0   |     |     | ns   |

| XSD, XSF hold time after XCK↓           | t <sub>H</sub>   | 4.0   |     |     | ns   |

Figure 14. G.742/G.751 Service Bit Receive Timing

# G.751 (E3)

| Param eter Param eter | Symbol           | Min  | Тур  | Max | Unit |

|-----------------------|------------------|------|------|-----|------|

| ROC clock period      | t <sub>CYC</sub> | 29.0 | 29.1 |     | ns   |

| ROC high time         | t <sub>PWH</sub> | 11.0 |      |     | ns   |

| ROC low time          | t <sub>PWL</sub> | 11.0 |      |     | ns   |

| ROF pulse width       | t <sub>PW</sub>  | 11.0 |      |     | ns   |

| ROD delay after ROC↑  | t <sub>D</sub>   |      |      | 7.0 | ns   |

# G.742 (E2)

| Parameter            | Symbol           | Min   | Тур   | Max | Unit |

|----------------------|------------------|-------|-------|-----|------|

| ROC clock period     | t <sub>CYC</sub> | 116.0 | 118.4 |     | ns   |

| ROC high time        | t <sub>PWH</sub> | 46.0  |       |     | ns   |

| ROC low time         | t <sub>PWL</sub> | 46.0  |       |     | ns   |

| ROF pulse width      | t <sub>PW</sub>  | 46.0  |       |     | ns   |

| ROD delay after ROC↑ | t <sub>D</sub>   |       |       | 7.0 | ns   |

Figure 15. G.745/G.753 Service Bit Receive Timing

## G.753 (E3)

| Param eter           | Symbol                  | Min  | Тур  | Max | Unit |