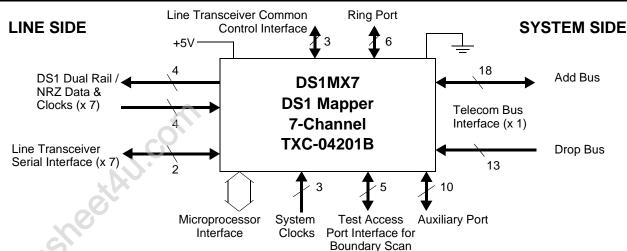

DS1MX7 Device DS1 Mapper 7-Channel TXC-04201B

**DATA SHEET**

### **FEATURES**

- Seven independent 1.544 Mbit/s DS1 mappers

- Single byte-parallel Telecom Bus @ 6.48 MHz (28 Slots) or 19.44 MHz (84 Slots)

- Floating VT1.5 byte-synchronous mapping with signaling only for use with or without a slip buffer

- Asynchronous mapping for DS1

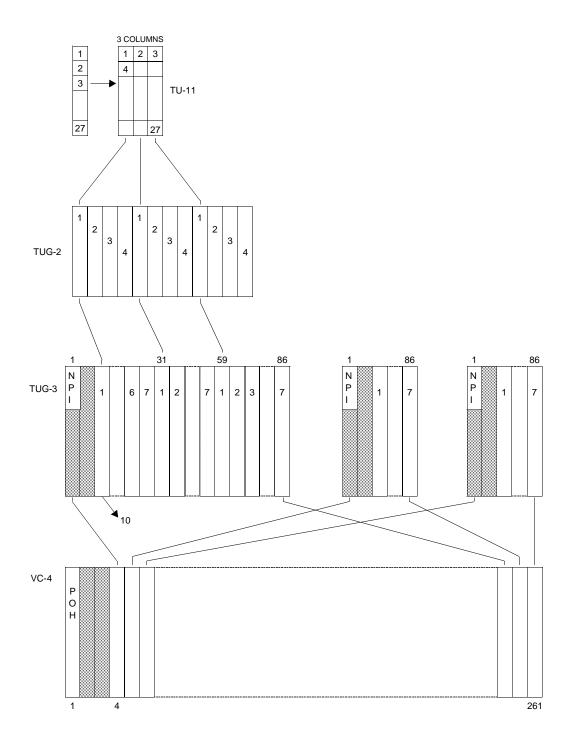

- SONET mapping (VT1.5) or SDH mapping (TU-11 in AU-3 or TU-11 in TUG-3)

- · AMI, B8ZS or NRZ codec for DS1s

- Serial I/O for control of DS1 line interface transceivers or framers

- Telecom Bus and DS1 loopbacks with integral PRBS generator and analyzer

- VT1.5/TU-11 pointer tracking and generation

- VT1.5/TU-11 overhead processing and insertion

- one-second latched performance registers and counters

- DS1 alarm detection and generation

- Auxiliary port for J2, V5, Z6/N2, Z7/K4 and O-bit access

- Ring port for USHR/P support

- Gapped clock option for Internet Applications without need for a framer

- Intel / Motorola-compatible microprocessor interface

- 3-bit RDI support

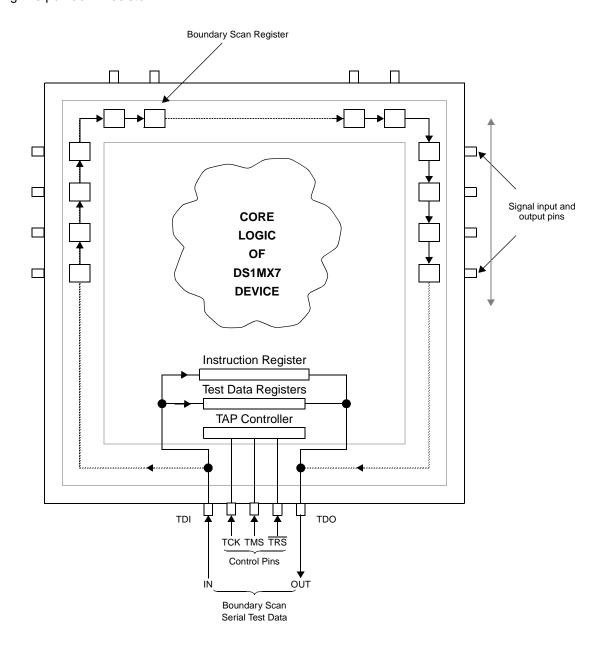

- Boundary Scan capability (IEEE 1149.1)

- Single +5 V, ±5 % power supply

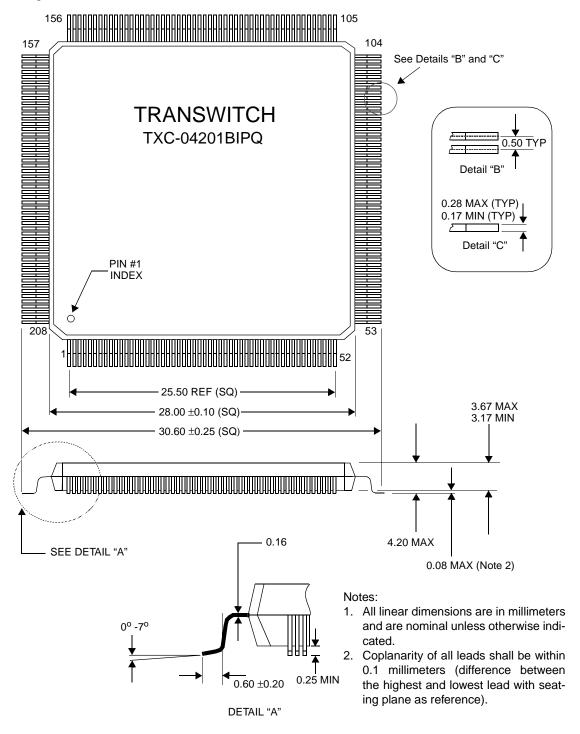

- 208-pin plastic quad flat package

#### **DESCRIPTION**

The DS1MX7 is a seven-channel byte-synchronous and asynchronous DS1 mapper. Both SONET and SDH mappings are provided per Bellcore GR-253-CORE (VT1.5) and ITU-T G.707 3-96 (TU-11). A single add/drop Telecom Bus is provided that can operate at either 6.48 or 19.44 MHz, which is compatible with other TranSwitch devices. VT1.5/TU-11 pointer tracking and overhead extraction/processing with full error and alarm control is provided. VT1.5/TU-11 pointer calculation and overhead assembly is also provided. Alarm and error mappings from drop to add and SONET/SDH to/from DS1 are provided. Jitter performance is achieved with a fully digital threshold modulator and DPLL that meets GR-253-CORE MTIE requirements without external de-jitter buffers. For the DS1 line, AMI, B8ZS and NRZ line codes are supported with full alarm detection and generation per ANSI T1.231-1997 draft. Each channel is independently programmable for mixed service applications. Access to status and control bits is provided via an Intel/Motorolacompatible microprocessor interface. Diagnostic, test, and maintenance functions are provided, including boundary scan, PRBS generator/analyzer and loopbacks.

### **APPLICATIONS I**

- SONET/SDH terminal or add/drop multiplexers supporting both asynchronous and byte-synchronous modes

- Unidirectional or bidirectional ring applications

- SONET Remote Digital Terminal Equipment

- SONET CPE Equipment requiring access to DS0s

- SONET/SDH Test Equipment

- Internet Access Equipment

U.S. Patents No. 4,967,405; 5,033,064; 5,040,170; 5,265,096; 5,289,507; 5,297,180; 5,528,598; 5,535,218 U.S. and/or foreign patents issued or pending Copyright © 2001 TranSwitch Corporation TranSwitch and TXC are registered trademarks of TranSwitch Corporation

Document Number: TXC-04201B-MB Ed. 4, September 2001

### **TABLE OF CONTENTS**

| Section                                                            | Page |

|--------------------------------------------------------------------|------|

| List of Figures                                                    | 3    |

| Feature List                                                       | 4    |

| Features that are Independently Selectable for each of the Mappers | 4    |

| Features that are only Selectable for the Seven Mappers as a Group | 7    |

| Block Diagram                                                      | ç    |

| Block Diagram Description                                          | 10   |

| Pin Diagram                                                        | 15   |

| Pin Descriptions                                                   | 16   |

| Absolute Maximum Ratings and Environmental Limitations             |      |

| Thermal Characteristics                                            | 25   |

| Power Requirements                                                 |      |

| Input, Output and Input/Output Parameters                          | 26   |

| Timing Characteristics                                             | 29   |

| Operation                                                          | 46   |

| General Mapper Application Overview                                | 46   |

| Line Interface Selection                                           | 46   |

| Asynchronous Operation with the Line Interface                     |      |

| Byte-synchronous Operation with the Line Interface                 |      |

| Receive Data and Signaling Highway Operation                       | 49   |

| Transmit Data and Signaling Highway Operation                      |      |

| The Synchronizer, Mapper and Overhead Generator                    |      |

| Pointer Generation and Telecom Bus Slot Selection                  | 57   |

| VT/TU Pointer Tracking and Telecom Bus Slot Selection              |      |

| The Demapper                                                       | 63   |

| Desynchronization and Pointer Leak Rate Calculations               |      |

| Jitter Measurements                                                |      |

| Microprocessor Interface and Common Control/Status I/O             |      |

| Serial Port Control Interface                                      |      |

| DS1MX7 Channel Testing using the PRBS Generator and Analyzer       |      |

| Telecom Bus Interface                                              |      |

| Multiplex Format and Mapping Information                           | 83   |

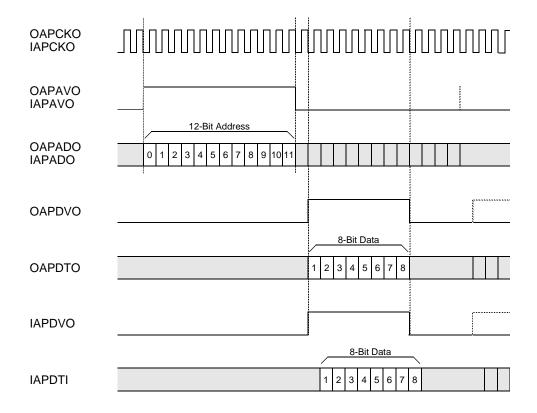

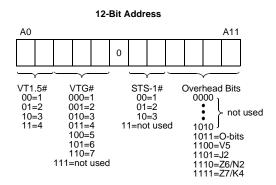

| Auxiliary Port                                                     |      |

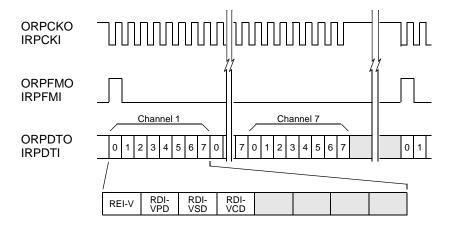

| Ring Port                                                          |      |

| Test Access Port                                                   |      |

| Boundary Scan Support                                              |      |

| Device Reset Procedure                                             |      |

| Memory Map                                                         |      |

| Memory Map Descriptions                                            |      |

| Common Memory Map                                                  |      |

| Per Channel Control Registers                                      |      |

| Per Channel Status Registers                                       | 131  |

| Application Diagrams                                               |      |

| Package Information                                                |      |

| Ordering Information                                               |      |

| Related Products                                                   |      |

| Standards Documentation Sources                                    |      |

| List of Data Sheet Changes                                         | 150  |

| Documentation Update Registration Form*                            | 153  |

\* Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# TRANSWITCH'

## **DATA SHEET**

# **LIST OF FIGURES**

| Figu           | ire                                                              | Page |

|----------------|------------------------------------------------------------------|------|

| 1              | DS1MX7 TXC-04201B Block Diagram                                  | 9    |

| 2              | VT1.5/ TU-11 Asynchronous and Byte-synchronous Mappings          | 12   |

| 3              | DS1MX7 TXC-04201B Pin Diagram                                    | 15   |

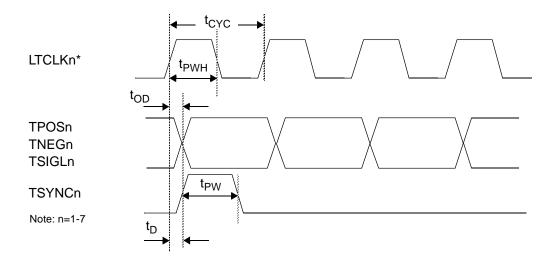

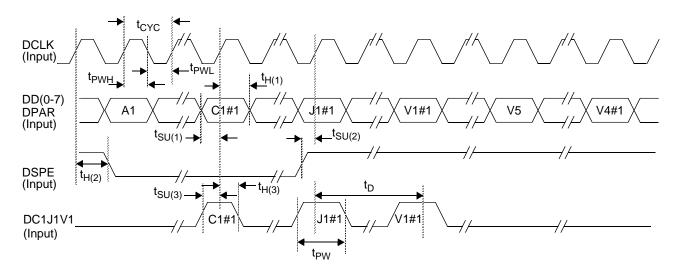

| 4              | Tributary Input Timing                                           | 29   |

| 5              | Tributary Output Timing                                          | 30   |

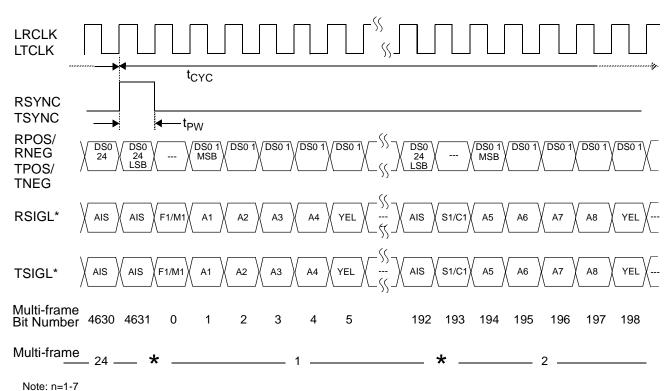

| 6              | Signaling Highway Structure                                      | 31   |

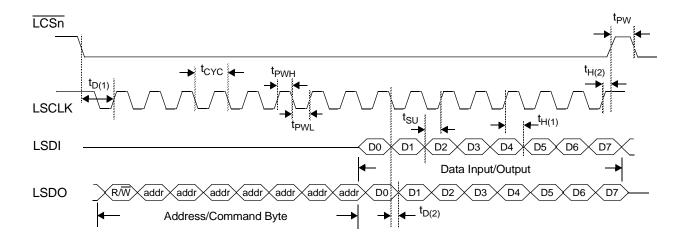

| 7              | Serial Control Port Structure and Timing                         |      |

| 8              | Telecom Bus Input Timing - 6.48 MHz Operation                    |      |

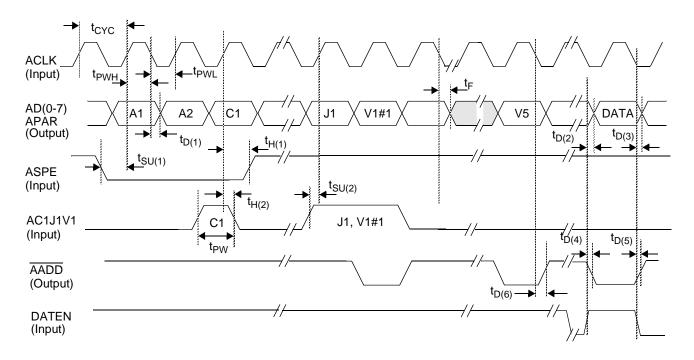

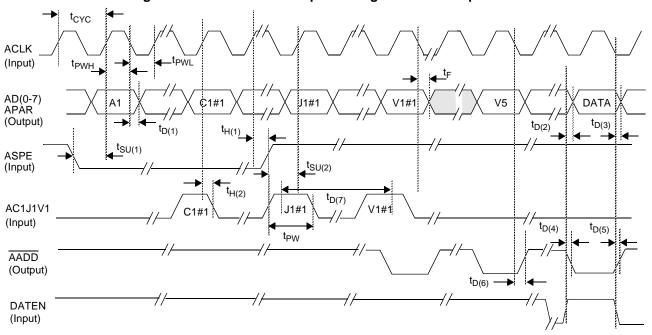

| 9              | Telecom Bus Input Timing - 19.44 MHz Operation                   |      |

| 10             | Telecom Bus Output Timing - 6.48 MHz Operation                   |      |

| 11             | Telecom Bus Output Timing - 19.44 MHz Operation                  |      |

| 12             | Auxiliary Port Timing                                            |      |

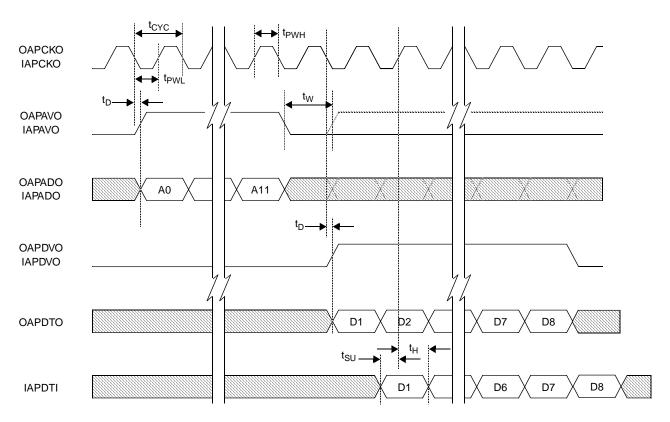

| 13             | Ring Port Timing                                                 |      |

| 14             | Datacom Mode Output Timing                                       |      |

| 15             | Datacom Mode Input Timing                                        |      |

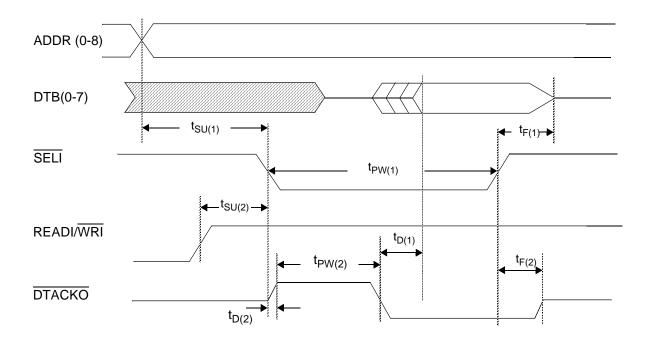

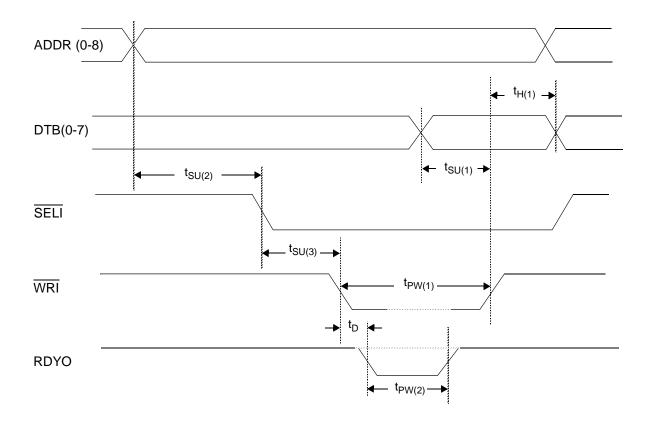

| 16             | Intel Microprocessor Read Cycle Timing                           |      |

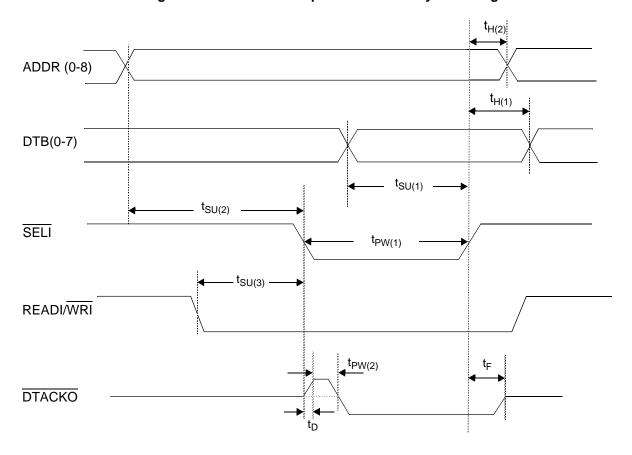

| 17             | Motorola Microprocessor Read Cycle Timing                        |      |

| 18             | Intel Microprocessor Write Cycle Timing                          |      |

| 19             | Motorola Microprocessor Write Cycle Timing                       |      |

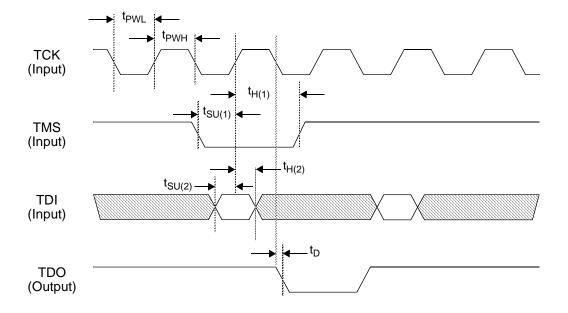

| 20             | Boundary Scan Timing                                             |      |

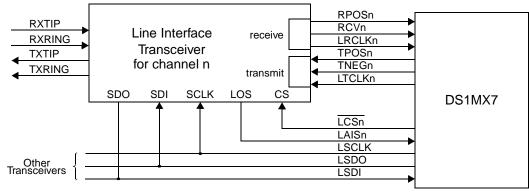

| 21             | Line Interface for Dual Unipolar Mode                            |      |

| 22             | Line Interface for NRZ Mode                                      |      |

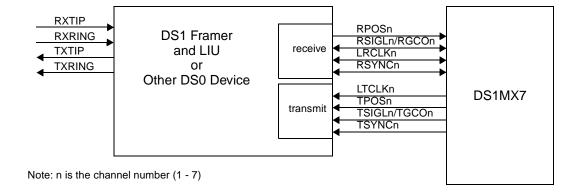

| 23             | Byte-synchronous Interface to a DS1 Framer                       |      |

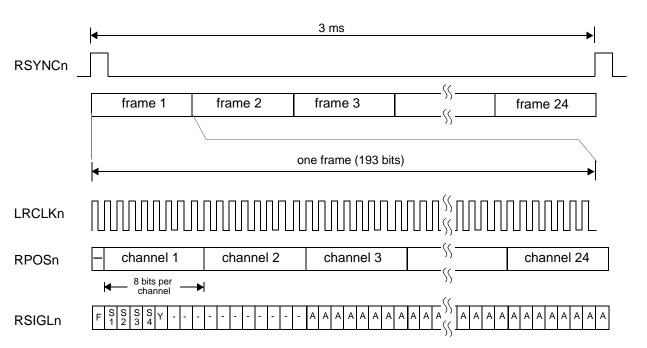

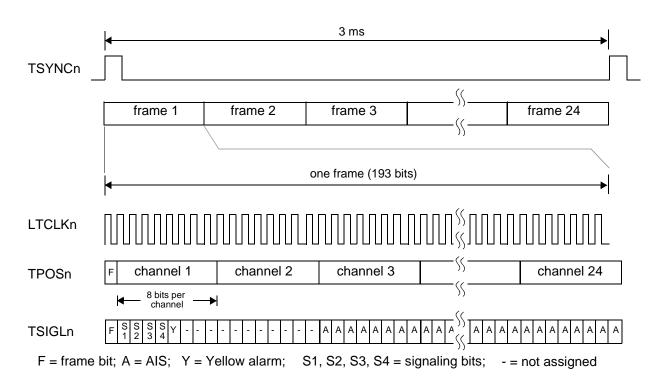

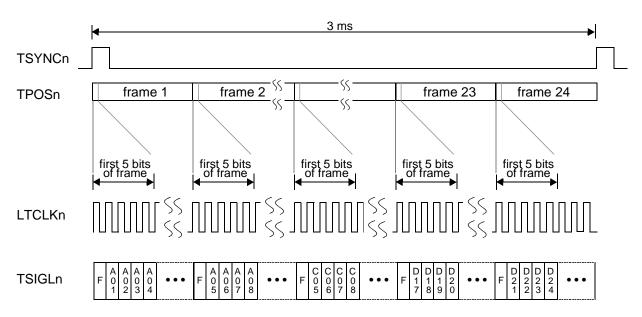

| 24             | System Interface Receive Framing Format                          |      |

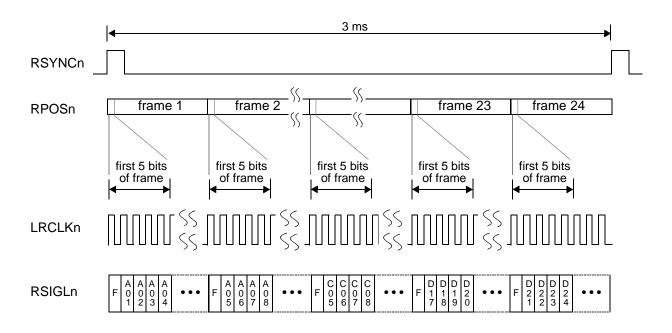

| 25             | System Interface Receive Signaling Format                        |      |

| 26             | System Interface Transmit Framing Format                         |      |

| 27             | System Interface Transmit Signaling Format                       |      |

| 28             | VT/TU Pointer Tracking State Machine                             |      |

| 29             | Pointer Leak Rate Algorithm                                      |      |

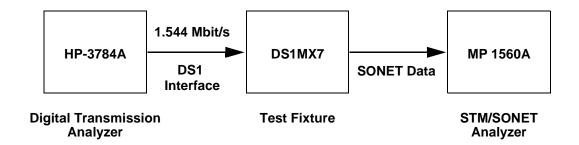

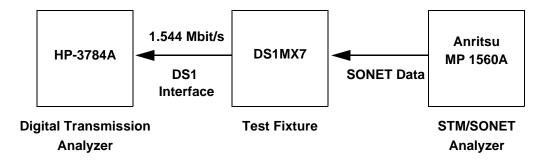

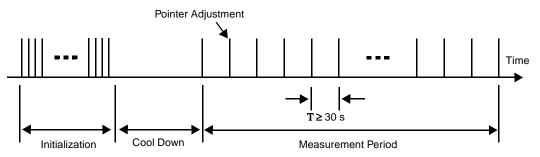

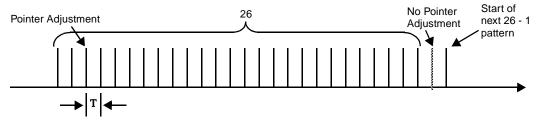

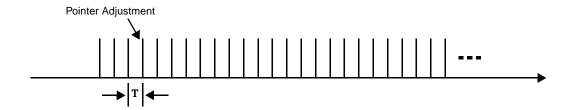

| 30             | Jitter Tolerance Test Setup                                      |      |

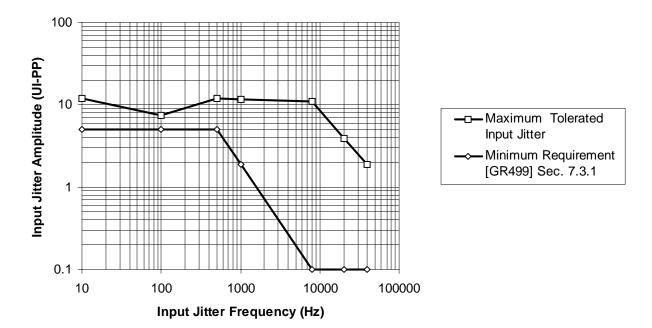

| 31             | Jitter Tolerance Measurements                                    |      |

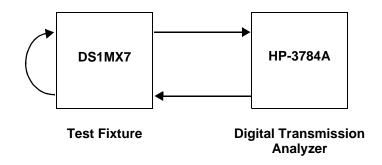

| 32             | Jitter Transfer Test Setup                                       |      |

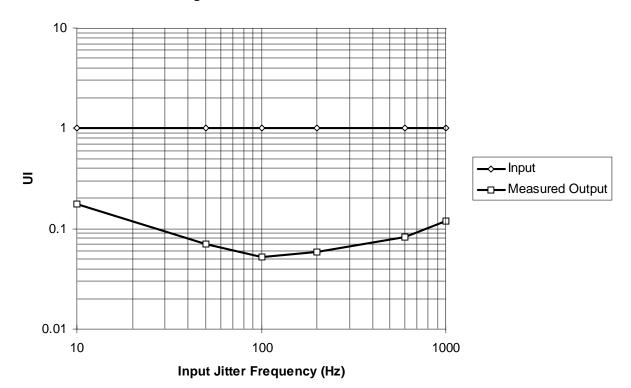

| 33             | Jitter Transfer Measurements                                     |      |

| 34             |                                                                  |      |

| 3 <del>4</del> | Jitter Generation Test Setup                                     |      |

| 36             | Shadow Register Operation                                        |      |

| 37             | Serial Interface Operation                                       |      |

|                | Loopbacks and Built-in PRBS Testing of the DS1MX7                |      |

| 38             | Telecom Bus Structure; SONET or VC-3 SDH; Telecom Bus @ 6.48 MHz |      |

| 39             | ·                                                                |      |

| 40<br>41       | Telecom Bus Structure; TUG-3 SDH; Telecom Bus @ 19.44 MHz        |      |

|                | STS-1 SPE Mapping                                                |      |

| 42             | STS-3/AU-3 Mapping                                               |      |

| 43             | STM-1/VC-4 Mapping                                               |      |

| 44             | Auxiliary Port Operation                                         |      |

| 45             | Auxiliary Port Address Designation                               |      |

| 46             | Ring Port Operation                                              |      |

| 47             | Boundary Scan Schematic                                          |      |

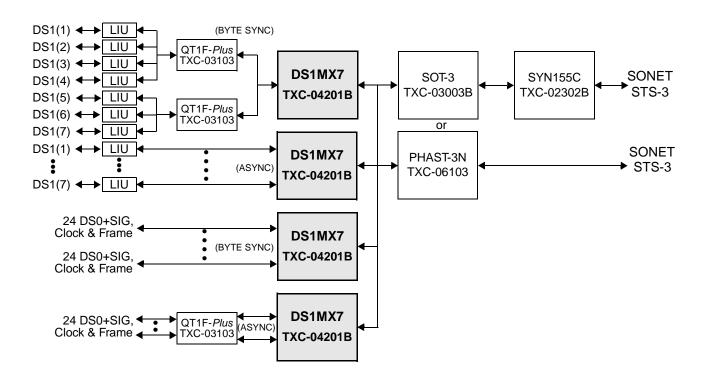

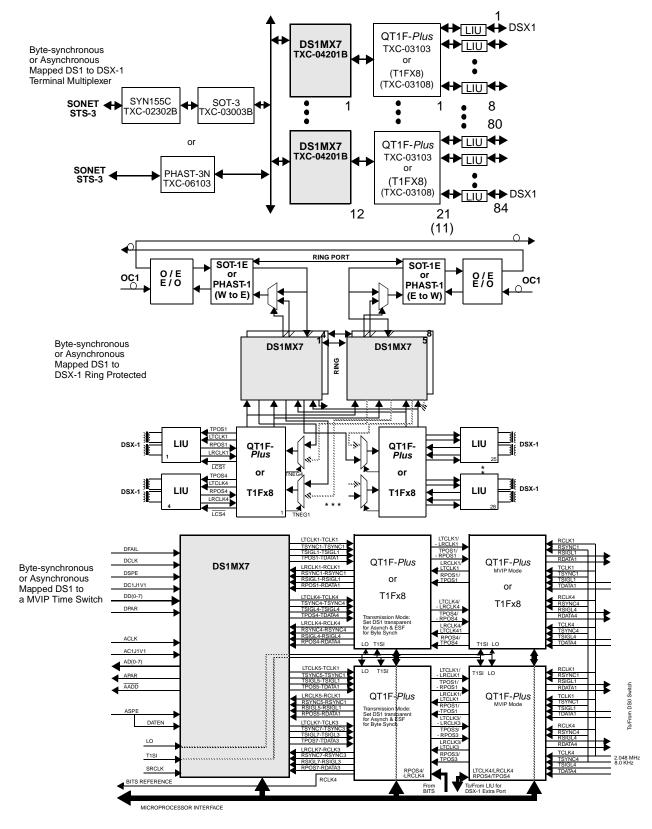

| 48             | DS1MX7 TXC-04201B Applications                                   |      |

| 49             | Some DS1MX7 TXC-04201B Byte-synchronous Applications             |      |

| 50             | DS1MX7 TXC-04201B 208-Pin Plastic Quad Flat Package              | 146  |

### **DATA SHEET**

#### **FEATURE LIST**

The DS1MX7 device is a highly-featured seven-channel DS1 (T1) mapper for use in a wide variety of interface, transmission and switching applications. Seven independent DS1 asynchronous / byte-synchronous mappers are provided in a single monolithic VLSI device using sub-micron CMOS technology. Powered from a single +5.0 volt supply, the device dissipates less than one watt typically. The DS1MX7 is provided in a 208-pin plastic quad flat package. Its ambient operating temperature range extends from -40 xC to 85 xC with 0 ft/min airflow.

The DS1MX7 device has been designed to meet the latest industry standards, namely:

- ANSI T1.102- 1993

- ANSI T1.105- 1991

- ANSI T1.107- 1995

- ANSI T1.231 (1993 and 1997 draft)

- ANSI T1.403-1995

- AT&T Pub. 62411 (December 1990)

- Bellcore GR-253-CORE (Issue 2)

- Bellcore TR-NWT-000496 (Issue 3)

- Bellcore GR-499-CORE (Issue 1)

- IEEE 1149.1- 1990, -1994

- ITU-T G.707 3-96

- ITU-T G.783

#### FEATURES THAT ARE INDEPENDENTLY SELECTABLE FOR EACH OF THE MAPPERS

### **Line Interface Options**

- Meets ANSI and Bellcore input jitter requirements

- Rail (for asynchronous mapping only)

B8ZS or AMI

ANSI compliant LOS detector

ANSI compliant AIS detector

12-Bit BPV counters with excessive zeros option

NRZ option (for asynchronous and byte-synchronous mapping)

Clock polarity selection for clock in/out

NRZ data inversion and clock edge options (separate transmit and receive control) For asynchronous use, negative rail can be used to count externally detected code violations

- Programmable clock edges for transmit and receive data

- External pin per channel for status (may be programmed to combine with internal AIS and LOS to support external LOC detector)

- Clock slave for asynchronous input; clock and multiframe synchronization (3 ms), master or slave, for byte-synchronous input

- Separate signaling highway for byte-synchronous, carries ABCD signaling bits and AIS / Yellow alarm information in and out of the DS1MX7

- · External pin-controlled shut down of all DS1 line drive pins for card protection

- Gapped clock option in place of signaling for 1536 kHz datacom in byte-synchronous operation

- CRC-6 generation (DS1 input) and error counting (DS1 output) in byte-synchronous mapping

#### **Mapping And Synchronizer Features**

- Mapping to SONET or SDH columns according to GR-253-CORE or ITU G.709

- Per channel selectable asynchronous and byte-synchronous mapping to a floating VT1.5 or TU-11 for both mapping and demapping

- Overhead assembly with BIP-2 calculation, REI-FEBE (microprocessor or received BIP-2 error), signal label (microprocessor value), RDI (microprocessor value or via received signal label mismatch, VT AIS, VT LOP, or unequipped) and RFI (microprocessor value or DS1 Yellow from signaling highway)

- Pointer calculation (fixed at 78 for asynchronous, calculated for byte-synchronous mode) with generated pointer increment and decrement counters (4 bits each)

- In byte-synchronous mode, line clock may be an input ('modified byte-synchronous') or an output ('true byte-synchronous')

- Multiplexing of signaling bits from the signaling highway with P<sub>0</sub>/P<sub>1</sub> bit generation

- Unequipped and Unassigned VT payload generation

- VT AIS generation (microprocessor value, AIS from signaling highway, loss of frame on bytesynchronous, or AIS / LOS / external pin from line decoder)

- · Threshold modulator to reduce demapping jitter and wander

- Tracking of input multiframe pulses by pointer movements in byte-synchronous mode

### **Demapping And Desynchronizer Features**

- Asynchronous or byte-synchronous per channel, programmable to match mapper mode

- Digital PLL with 2 Hz low pass filter to track up to <u>+</u> 250 Hz nominal DS1 signal providing a smooth clock output with no need for an external de-jitter buffer

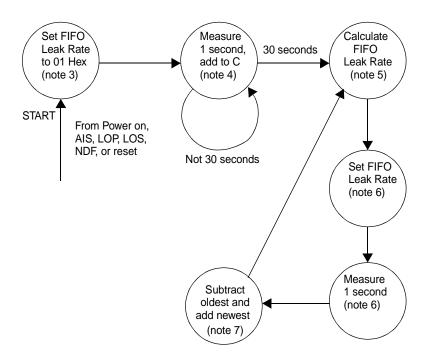

- Separate <u>+5</u> byte pointer leak buffer with programmable dual slope leak rate

(8 ms to 2048 ms per bit in 8 ms steps, automatically doubled to 16 ms to 4096 ms per bit in

16 ms steps within +12 bits of center of pointer leak buffer)

- · Power down with all-zeros or all-ones sent to line interface

- Demapping of SONET or SDH columns according to GR-253-CORE or ITU G.709

- Asynchronous and byte-synchronous demapping of a floating VT1.5 / TU-11

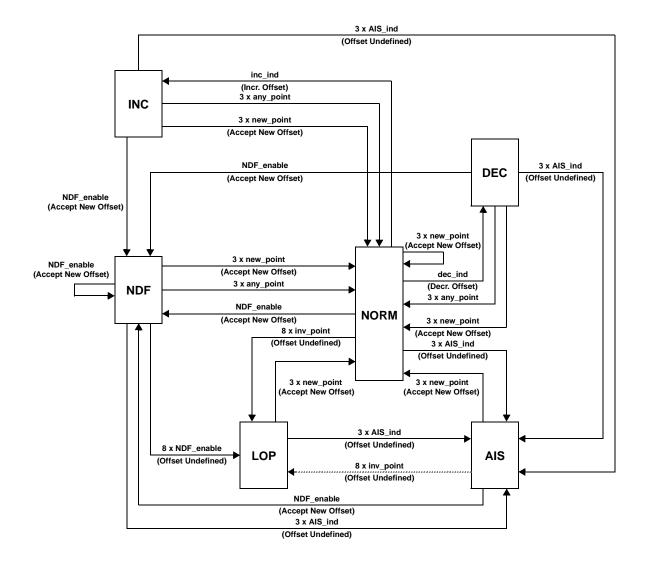

- Pointer tracking and extraction of overhead (V5 and Z7/K4), LOP, AIS, SS and NDF with received pointer increment and decrement counters (4 bits each)

- Overhead processing with BIP-2 calculation and error counting (12-bit, with overflow), REI (FEBE) counting (12-bit, with overflow), RDI (1- and 3-bit)/ RFI / signal label de-bouncing and detection, signal label mismatch / unequipped detection

- De-multiplexing of signaling bits to the signaling highway with multiframe generation for bytesynchronous

- DS1 AIS from microprocessor value, VT AIS, VT LOP, signal label mismatch or unequipped

- DS1 Yellow to signaling highway from RFI

### Fractional T1 For Frame Relay, ATM AAL1 Access

- · Framer not required for many applications

- Receive and transmit gapped clock (1536 kbit/s) per mapper in byte-synchronous mode

- · CRC-6 generation and checking

- Direct connection to multichannel HDLC or ATM devices for N x 56 or N x 64 kbit/s service

- Internal DPLL to minimize received jitter

#### Signaling Support For Byte-synchronous Mapping

- Receive and transmit temporary buffers to align VT1.5/TU-11 payloads to signaling highway

- Signaling bits mapped to and demapped from specific locations per GR-253-CORE and G.709

- · A, AB, ABCD signaling bit support

- Byte synchronous operation with TranSwitch QT1F-Plus VLSI device:

Signaling bit positions in received DS0s optionally replaced with ones by QT1F-Plus

VT AIS and VT RFI to DS1 AIS and DS1 RAI (Yellow) respectively

DS1 AIS and DS1 RAI (Yellow) to VT AIS and VT RFI respectively

- Unicode support (DS0 alarms) for byte-synchronous operation planned in future framers

#### **Alarms And Errors**

- Detection of VT AIS, VT RFI, unequipped, signal label mismatch, VT loss of pointer, single-bit RDI, 3-bit RDI, and demap error in the demap direction

- Detection of DS1 AIS, loss of signal, map error, and external pin alarm, in the mapping direction

- Counting of code violations (with or without excessive zeros) or CRC-6 errors, BIP-2, REI (FEBE), pointer generation and receive pointers with presets and overflow indications

- Microprocessor enable and insert of all alarms detected from line, calculated, or in overhead

#### **Maintenance**

- Loopbacks DS1 line remote (toward DS1 line), DS1 line local (toward Telecom Bus), and Telecom Bus (toward DS1 line for all seven channels at once)

- PBRS generator in transmit framer and analyzer in receive path per T1 channel 2<sup>15</sup>-1 pattern.

Separate control bits with software indication

· Power-down modes force transmit leads to low, high or tristate

#### **Microprocessor Interface**

- Nineteen-bit status register for VT AIS, VT RFI, unequipped, signal label mismatch, VT loss

of pointer, single-bit RDI, 3-bit RDI, DS1 AIS, loss of signal, map error, demap error, external

pin alarm, and counter overflow bits for code violation/CRC-6, BIP-2, REI (FEBE), pointer

generation and receive pointers

- Latched event registers and interrupt mask registers to individually control each condition

- Twelve-bit CRC-6 (byte-synchronous)/ code violation (asynchronous), BIP-2, and REI (FEBE) error counters

- Four-bit increment and decrement pointer generation and receive pointer counters

- · Shadow registers for all counters

- · Full control of alarm mapping through enable bits

- · Microprocessor forcing of alarm conditions

- · Per channel reset and resynchronization

- Register access to J2, V5, Z6/N2, Z7/K4 bytes and O-bits for read and write

#### **Performance and Fault Monitoring**

- · One second basis, via backplane one second clock

- Shadow registers for all 19 alarms and 7 counters

- Separate registers to indicate alarm changes (performance) and hard conditions (faults) are updated every second to simplify performance report generation

#### FEATURES THAT ARE ONLY SELECTABLE FOR THE SEVEN MAPPERS AS A GROUP

#### **Telecom Bus Interface**

- · Single add bus and drop bus with individual timing

- Operation at 6.48 Mbyte/s or 19.44 Mbyte/s

- Compatible with TranSwitch SOT-1E and SOT-3 functional "B" version devices

- Parity generation and detection with device alarm (odd or even) on data and SPE / C1J1V1

- SONET mapping via VT1.5 at 6.48 and 19.44 Mbyte/s

- SDH mappings via TU-11 to AU-3 or to TUG-3 at 19.44 Mbyte/s

- Uses SPE and C1J1V1 to locate individual VTs

- Separate STS-1 phases permitted in an STS-3 for asynchronous and modified bytesynchronous operation

- Each transmit and receive time slot is programmable to one of 28 or 84 including internal and external add bus contention monitors with global alarm

- Add bus timing programmable to zero or one clock delay

- · Drop or add bus clock edges programmable

- Add bus enable pin plus control pins for optional POH and/or TOH drive

- Per VT/ TU signal failure input via common pin

- Clock and SPE / C1J1V1 presence detectors on system in and system out buses, which generate device alarms on failure

#### **External Line Interface Transceiver Support**

- Three-wire serial port to read/write control up to seven line interface transceivers ('host mode')

- Designed to support integrated microprocessor control of loopbacks, alarms and line build out

- · Per channel or broadcast for data out

- · Internal registers to drive and read external devices

### **Common Microprocessor Support**

- · Microprocessor global reset, masks, polling registers, interrupt polarity and latch edge control

- Motorola split address/data or Intel split address/data

- Global alarm Indications ('or' of per channel alarms of the same type) with a channel pointer register indicating channels with any active alarms

- Global interrupt mask bits, one per alarm type

- Interrupt on alarm changes: on positive edge, negative edge or both edges

- Device level alarms for Telecom Bus signals and reference clocks using status and latched event registers with interrupt mask registers

- Device level alarms can be enabled to appear on separate interrupt line for card protection via hardware or software mechanisms

- · Error insertion via the microprocessor for parity testing on the Telecom Bus

- Timed error insertion for REI (FEBE) and BIP-2 global value

- · Hardware interrupt polarity selection

- Common hardware reset pin and global software reset register

TXC-04201B-MB Ed. 4, September 2001

#### **DATA SHEET**

### **Auxiliary Port Common**

- · Access to or from optional overhead bytes for special purposes with microprocessor enables

- Access to J2, V5, Z6/N2, Z7/K4 bytes and O-bits received via a shared serial port

- Insertion of J2, Z6/N2, Z7/K4 bytes and O-bits to mapping direction via a shared serial port

### **Ring Port Common**

- Permits REI (FEBE) and single/three-bit RDI values to be sent from one DS1MX7 to another

- USHR/P support

- · Shared serial port with clock and frame for transmit and receive

- Pair of DS1MX7s provides for dual Telecom Bus applications

### **Protection, Test and Maintenance Support**

- IEEE 1149.1 boundary scan

- Ability to tristate all outputs for in-circuit testing with a single control pin

- · Loss of clock detectors and parity generator/error detector for add and drop Telecom Buses

- Internal alarm output programmable to a variety of bus fault and clock fault conditions and a card switch-off feature to assist in implementing protection switching

- External shadow register clock input (1Hz ± 32 ppm)

- PRBS generator and analyzer switchable to any of the seven mapper channels

# TRANSWITCH'

### **BLOCK DIAGRAM**

Figure 1. DS1MX7 TXC-04201B Block Diagram

### **DATA SHEET**

#### **BLOCK DIAGRAM DESCRIPTION**

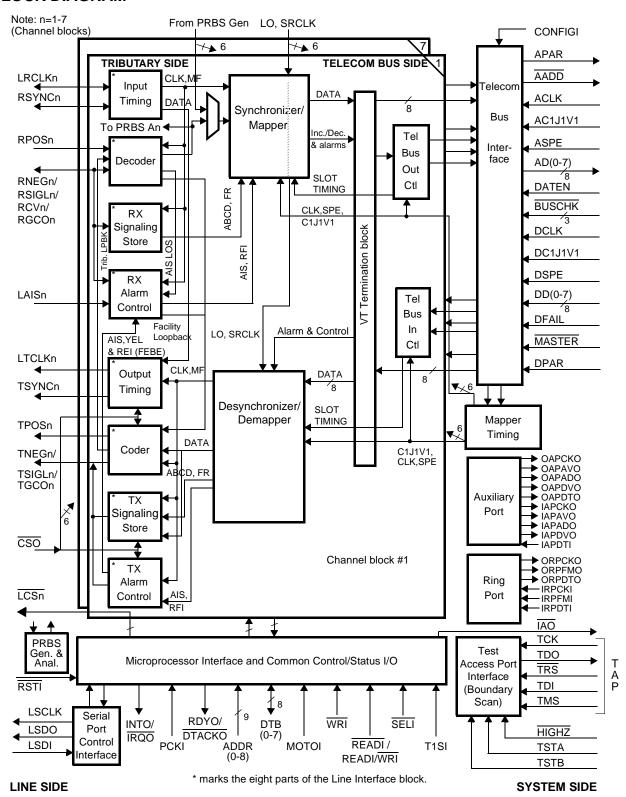

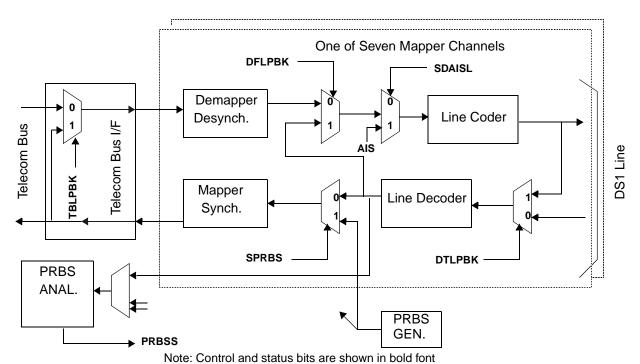

A simplified block diagram of the DS1MX7 device is shown in Figure 1. The major blocks are the seven Channel blocks, the Microprocessor Interface, the Serial Port Control Interface, the Ring port, the Auxiliary port, the PRBS (Pseudo-Random Binary Sequence) Generator and Analyzer, the Test Access Port Interface, the Mapper Timing block and the Telecom Bus Interface.

Each of the seven Channel blocks consists of the following component blocks: Decoder/Coder and Input/Output Timing (for Receive and Transmit Line Interfaces), Receive and Transmit Alarm Control, Receive and Transmit Signaling Store, Synchronizer/ Mapper and Desynchronizer/ Demapper, VT Termination, and Telecom Bus Input and Output Control blocks.

The Receive and Transmit Line Interface blocks connect each of the seven mapper channels to an external line interface transceiver, which performs the LIU and clock recovery functions for the asynchronous mode of operation. The interface to the transceiver can be configured for two interface modes: a dual unipolar (rail) interface or a NRZ interface. When the byte-synchronous mode of operation is used, the clock and synchronization signals to and from an external DS1 framer are handled by these blocks; data is always in the NRZ mode. These blocks also provide a tributary (transmit to receive) loopback and a facility or remote (receive line to transmit line) loopback.

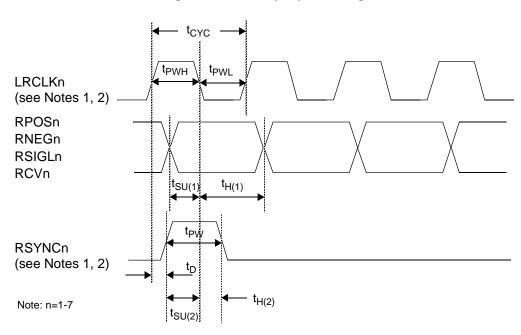

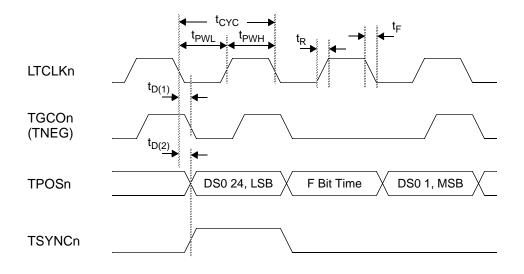

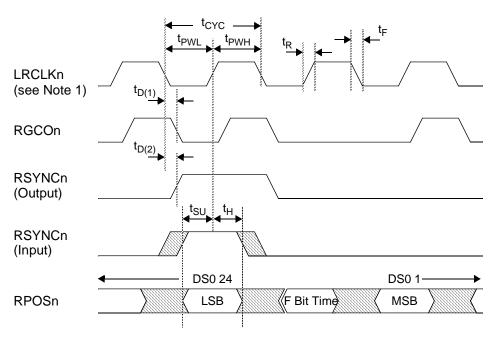

When the dual unipolar interface mode is selected, input data from the external line interface transceiver is clocked into the DS1MX7 on pins RPOSn and RNEGn using the recovered receive clock present on the LRCLKn input pins, where n=1-7 identifies one of the seven mappers (note: RNEGn is one of several pins that has multiple functions, with a signal symbol for each). In the transmit direction, unipolar data is clocked out of the DS1MX7 on pins TPOSn and TNEGn by the transmit line clock present on the LTCLKn output pins. Global control bits are provided in the memory map which enable the unipolar data to be clocked in and out of the DS1MX7 on either edge of the clocks. For the dual unipolar interface mode, the DS1MX7 provides either a Bipolar with Eight Zero Substitution (B8ZS), or an Alternate Mark Inversion (AMI), coder and decoder function, and Loss Of Signal detection. The Loss Of Signal detector meets the requirements specified in the ANSI T1.231 document listed above in the DS1MX7 Features section. An unframed AIS detector is also provided to assist in network fault isolation. A 12-bit performance counter is provided for each mapper, for counting B8ZS coding violation errors. An option is provided to also include excessive zeros in the coding violations counter.

When the NRZ interface mode is selected and the mapper channel is programmed for asynchronous mapping, NRZ data is clocked in at the RPOSn pin by the recovered received clock input on the LRCLKn pin. The NRZ data is clocked out of the DS1MX7 on the TPOSn pins by the transmit system clock present on the LTCLKn pins. Global control bits are provided in the memory map which enable the NRZ data to be inverted or clocked in and out of the DS1MX7 on either edge of the clocks. Bipolar violations which are detected in the external line interface transceiver may be clocked into the DS1MX7 on the RNEGn/RCVn pins and counted in the associated 12-bit coding violation performance counter. The TNEGn output may be used in NRZ mode as a spare drive bit. The Remote Line Loopback function for each framer is also implemented in the Line Interface blocks.

When the NRZ interface mode is selected and the mapper channel is programmed for byte-synchronous mapping, NRZ data is clocked in at the RPOSn pins by the clock present on pins LRCLKn. The DS1MX7 can generate a clock on LRCLKn and a 3.0 ms multiframe synchronization signal on pins RSYNCn if an external slip buffer is provided in the framer or if the source of the signal is a clock slaved to the DS1MX7. If LRCLKn and RSYNCn are inputs, the DS1MX7 translates any clock phase movements with respect to the SONET/SDH clock via VT/TU pointer movements. For applications that do not require a framer but where the DS1 ESF CRC-6 performance monitoring function is desired (true byte-synchronous mode only), the DS1MX7 calculates and inserts CRC-6 into the defined frame bit positions in the VT1.5/ TU-11 structure in the mapping direction. After demapping, the CRC-6 is checked and any errors found are counted in the 12-bit counter shared for code violation counting.

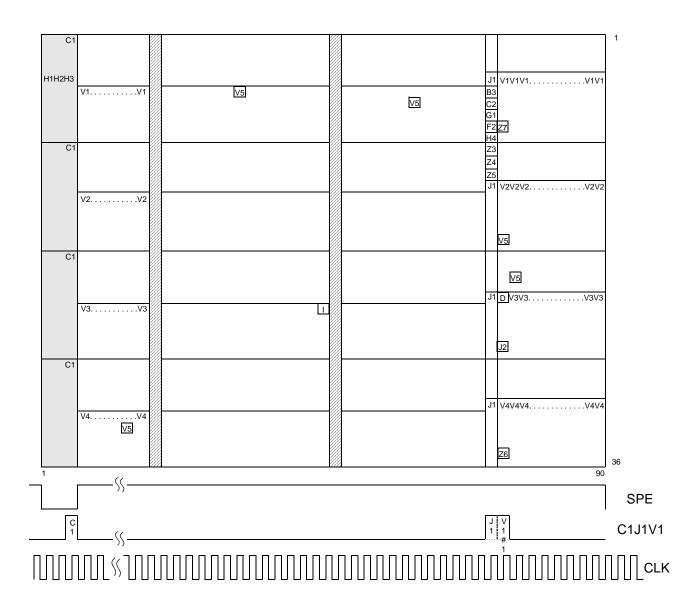

Byte-synchronous mapping supports the independent transmission of signaling through defined nibbles in the VT1.5/ TU-11 structure, as shown in Figure 2. The DS1MX7 provides Receive and Transmit Signaling Stores to synchronize signaling and framing bits to and from a DS1 Framer or switching stage with the Mapper and

DS1MX7 TXC-04201B

Demapper blocks. Signaling is received through the RNEGn/RSIGLn pins in byte-synchronous mode, being clocked in with LRCLKn. Signaling is sent out on the TNEGn/TSIGLn pins in byte-synchronous mode, using LTCLKn. TranSwitch framers like the QT1F-*Plus* (TXC-03103) can utilize the signaling bits on the signaling highways for automatic signaling propagation between SONET/SDH byte-synchronous mapping and DS1 lines. For applications using the full DS1 payload in byte-synchronous mode, the RNEGn/RSIGLn pins can be programmed to supply gapped clock (RGCOn), as can the TNEGn/TSIGLn pins (TGCOn).

The Receive and Transmit Alarm Control blocks work in conjunction with the Receive and Transmit Line Interface blocks as well as the Receive and Transmit Signaling Store blocks to move DS1 alarm signals in and out of the DS1MX7. The Receive Alarm Control block detects specific bits from the receive signaling highway, such as AIS or RAI (Yellow), for forwarding to the Mapper block as AIS and RFI. It also gathers LOS and AIS from the Receive Line Interface. The LAISn input pin may be used for forwarding an externally detected Loss of Signal or Loss of Clock, or as a general interrupt input. The Transmit Alarm Control block translates RFI and AIS from the Demapper block along with microprocessor controls to set specific bits on the transmit signaling highway. TranSwitch framers like the QT1F-*Plus* (TXC-03103) can utilize the control bits on the signaling highways for automatic alarm propagation between SONET/SDH and DS1 lines. For card protection schemes, control input pin CSO, when driven low, causes all of the output pins for the seven Line Interfaces to go low.

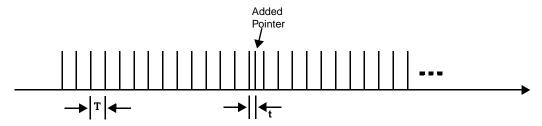

The Synchronizer/ Mapper block takes the clock and data from the Receive Line Interface in asynchronous mode, threshold modulates it with SRCLK, buffers it in a FIFO and inserts the data bits in the information bit positions of the asynchronous VT1.5/ TU-11, and stuffs it using the two stuff opportunity bits with indication in the C1 and C2 bits, as shown in Figure 2. The stuffing matches the received DS1 clock to the bit positions available based on the SONET/SDH network clock supplied to the DS1MX7 in the Add Telecom Bus Clock, ACLK and the AC1J1V1 signal. Optional overhead bytes J2, Z6/N2, O and part of Z7 are taken from microprocessor-written values or the Auxiliary Port.

The Synchronizer/ Mapper block takes the clock, frame and data from the Receive Line Interface in byte-synchronous mode, buffers it in a FIFO and writes it to defined byte positions in the byte-synchronous VT1.5/TU-11 along with the optional overhead bytes J2, Z6/N2 and part of Z7 which are taken from microprocessor-written values or the Auxiliary Port. For byte-synchronous mode the signaling bits are taken from the Receive Signaling Store and mapped to the correct positions in the VT1.5/TU-11. The 500-microsecond long VT superframe shown in Figure 2 is repeated six times, being synchronized to the RSYNCn 3.0 millisecond input. The P<sub>1</sub>P<sub>0</sub> bits are generated to indicate which signaling bits are being carried in a specific VT superframe and are related to RSYNCn. FIFO conditions are monitored and can lead to increment or decrement requests of the VT Termination block. Synchronization changes in RSYNCn are monitored for possible NDF requests.

The VT Termination block takes the mapped data and optional overhead together with any frame, increment or decrement indications associated with byte-synchronous mode from the Synchronizer/ Mapper block. The V5 and Z7 bytes are built from one of several received DS1 alarm sources (the receive alarms, Ring Port error conditions, or microprocessor-written values). Parity is then calculated over the payload. V1 and V2 are set to 78, positioning V5 just after V1 for asynchronous mode only. For byte-synchronous mode (true byte-synchronous or modified byte-synchronous), the V1 and V2 bytes are generated to track the phase of the incoming DS1 signal relative to ACLK; two four-bit counters are provided to keep track of pointer increments and pointer decrements generated. If a new position for the RSYNCn pulse is generated, this block will generate an NDF along with the new pointer. If the DS1MX7 acts as a clock source, the LO pin will be used to provide this clock and it must be frequency locked to the STS-1 or STM-1 clock, or pointer justifications and/or mapping errors will result. If AIS is to be generated the entire payload is ones. If unassigned (Idle) is to be generated, an all-zeros payload including V5 is generated.

The VT termination block also provides the pointer tracking, V5 and Z7 overhead location and VT1.5/ TU-11 alarm detection and de-bouncing functions. The alarms (RDI in four flavors, RFI, Unequipped, Signal Label Mismatch, LOP, AIS, REI, BIP-2 errors, etc.) are made available to the common microprocessor block for latching, shadowing, counting and interrupting purposes. Alarms are provided on the Ring Port for RDI and REI to support ring applications. It also identifies the payload for the Desynchronizer/ Demapper block as well as any pointer movements.

| Byte-synchronous Floating VT<br>Mode                                                          | Legend:                                         | Asynchronous Floating VT<br>Mode                                      |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------|

| V <sub>1</sub>                                                                                | C <sub>n</sub> = Stuff Control                  | V <sub>1</sub>                                                        |

| V <sub>5</sub>                                                                                | F = DS1 Frame Bit                               | V <sub>5</sub>                                                        |

| P <sub>1</sub> P <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> F R | I = Information                                 | RRRRRIR                                                               |

| DS0 Channels 1 - 24                                                                           | J <sub>2</sub> = VT Path Trace                  | 24 Information Bytes                                                  |

| $V_2$                                                                                         | O = Overhead Bits                               | $V_2$                                                                 |

| $J_2$                                                                                         | P <sub>1</sub> P <sub>0</sub> = Signaling Phase | J <sub>2</sub>                                                        |

| P <sub>1</sub> P <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> F R | R = Fixed Stuff                                 | C <sub>1</sub> C <sub>2</sub> O O O O I R                             |

| DS0 Channels 1 - 24                                                                           | S <sub>n</sub> = Signaling                      | 24 Information Bytes                                                  |

| $V_3$                                                                                         | St <sub>n</sub> = Stuff Opportunity             | V <sub>3</sub>                                                        |

| Z <sub>6</sub>                                                                                | V <sub>1</sub> and V <sub>2</sub> = pointer     | Z <sub>6</sub>                                                        |

| P <sub>1</sub> P <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> F R | V <sub>3</sub> = Inc/Dec<br>opportunity         | C <sub>1</sub> C <sub>2</sub> O O O O I R                             |

| DS0 Channels 1 - 24                                                                           |                                                 | 24 Information Bytes                                                  |

| $V_4$                                                                                         | V <sub>4</sub> = unused                         | $V_4$                                                                 |

| Z <sub>7</sub>                                                                                | V <sub>5</sub> = VT Overhead                    | Z <sub>7</sub>                                                        |

| P <sub>1</sub> P <sub>0</sub> S <sub>1</sub> S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> F R | Z <sub>6</sub> = Reserved Byte                  | C <sub>1</sub> C <sub>2</sub> R R R St <sub>1</sub> St <sub>2</sub> R |

| DS0 Channels 1 - 24                                                                           | Z <sub>7</sub> = Reserved and 3-bit<br>RDI Byte | 24 Information Bytes                                                  |

| V1 Byte |        |         |   |    |    |                                 | V2 Byte |   |   |   |   |   |   |   |   |

|---------|--------|---------|---|----|----|---------------------------------|---------|---|---|---|---|---|---|---|---|

| ١       | New Da | ata Fla | g | Si | ze | I                               | D       | I | D | I | D | I | D | I | D |

| 0       | 1      | 1       | 0 | S1 | S2 | Pointer Range = 0 - 103 decimal |         |   |   |   |   |   |   |   |   |

A normal NDF is shown (new data flag = 1001); S1S2 = 11; Positive Justification = Invert the 5 I-bits; Negative Justification = Invert the 5 D-bits; shown MSB (bit 1) first.

| 1     |       | 8     |              |       |

|-------|-------|-------|--------------|-------|

| BIP-2 | REI-V | RFI-V | Signal Label | RDI-V |

Shown MSB (bit 1) first. REI-V is also known as FEBE. RDI-V set to a 1 for Unequipped, AIS-V and LOP-V.

| 1 | Z7 Byte 8 |   |   |             |   |  |  |

|---|-----------|---|---|-------------|---|--|--|

| R | R         | R | R | 3-bit RDI-V | R |  |  |

3-bit RDI-V Codes: 001 = no defects; 010 = Signal label mismatch; 101 = AIS-V or LOP-V; 110 = Unequipped.

Figure 2. VT1.5/ TU-11 Asynchronous and Byte-synchronous Mappings

DS1MX7 TXC-04201B

The Desynchronizer/ Demapper block takes the data and alarm information, along with pointer information. and extracts the DS1 signal. This block extracts the optional overhead bytes and sends V5, Z6/N2, O and Z7/ K4 to the Auxiliary Port for asynchronous mode. For byte-synchronous mode, the O bytes are omitted and the signaling bits are sent to the Transmit Signaling Store instead. In both modes the data is sent to a pointer leak buffer which is programmable for leak out rate. This is used to minimize jitter and wander on asynchronously mapped signals as well as to smooth out byte-synchronously mapped signals that utilize pointer movements for frequency adjustment. The pointer leak rate may be adjusted to meet MTIE requirements with a simple software algorithm which uses the one second latched pointer increment and decrement counters. The Desynchronizer uses a DPLL operated from the signal on SRCLK (48.636 MHz) that smooths out the stuffing jitter and compensates for the demapping gapped positions used for all orders of overhead. The Desynchronizer outputs a DS1 clock along with the DS1 data to the Transmit Line Interface block ready for transmission or framing without additional de-jittering. In byte-synchronous mode the Frame pulse (3.0 ms) is decoded from the P<sub>1</sub>P<sub>0</sub> bits and is used to align the signaling highway to the Transmit Signaling Store, and it becomes the signal on TSYNCn. A correct P<sub>1</sub>P<sub>0</sub> pattern must be supplied for proper operation even if signaling is not used. Alarm information (RFI and AIS) is sent to the Transmit Alarm block for forwarding on the signaling highway. AIS is used to cause the DPLL to output an in-frequency-range all-ones signal.

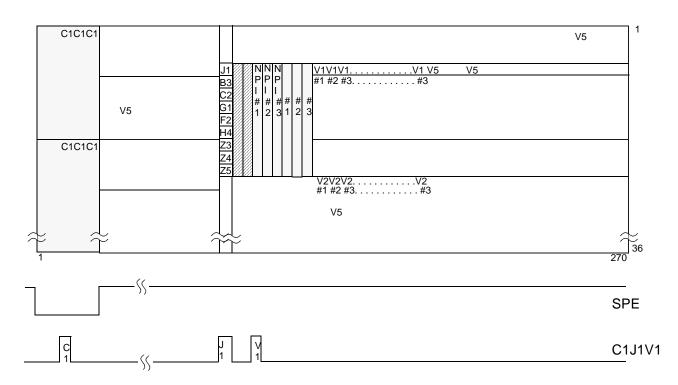

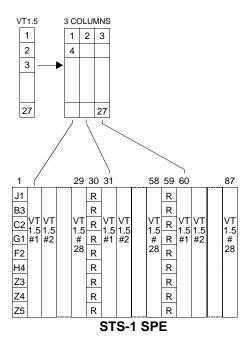

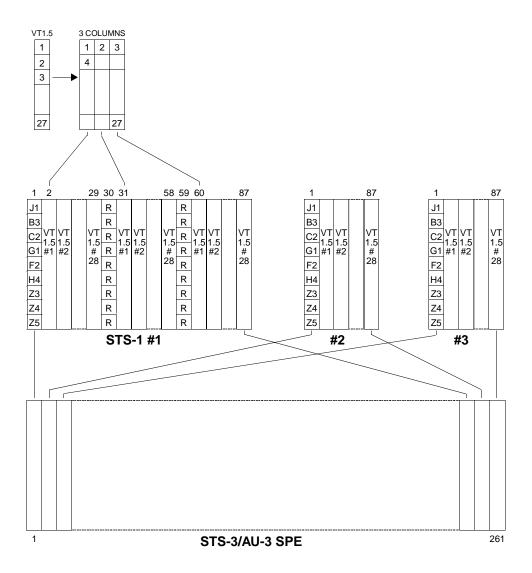

The Telecom Bus Input and Output Control blocks buffer the assembled VT1.5/ TU-11 bytes for insertion to or extraction from the Telecom Bus Interface. Each of the seven mapper channels can independently be placed on or independently taken from any one of three STS-1s or TUG-3s (19.44 MHz Telecom bus only), any one of seven VT groups or TUG-2s, and any one of four VT1.5 or TU-11s. Enable control bits allow a channel to be disconnected in transmit and/or receive from the Telecom Bus.

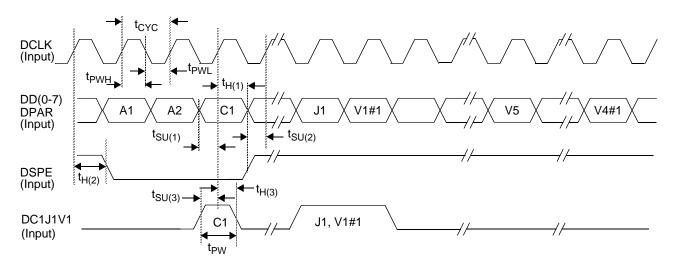

The Telecom Bus Interface block combines the signals from the seven mapper channels and synchronizes them to the Add Bus half of the Telecom Bus based on the ACLK, AC1J1V1 and ASPE signals. It can be configured as a single STS-1 (6.48 MHz), an STS-3 (19.44 MHz) or an STM-1 (19.44 MHz). Contention checks are made for the seven mapper channels; this feature is extended using the BUSCHK pins to up to 3 additional DS1MX7 devices sharing an Add Bus. Parity (pin APAR) and an add indication (pin AADD) are included with the byte-wide data (pins AD(0-7)). The DATEN and MASTER pins allow optional drive of overhead and stuff columns, when the data delay option is not used. The Drop Bus part of the Telecom Bus provides DCLK, DC1J1V1 and DSPE signals along with a failure indication (pin DFAIL) to indicate to the seven mapper channels that the received data is errored due to higher order path, section or line failures. Parity (pin DPAR) is included with the data (pins DD(0-7)). Parity covers add and drop data and optionally SPE and C1J1V1 signals. All signals are monitored for failure and maskable interrupts may be generated both to the microprocessor interrupt pin and to a separate failure pin (IAO).

The DS1MX7 has a PRBS Generator and Analyzer block. The Generator and Analyzer supports the 2<sup>15</sup>-1 pattern. The Generator output may be substituted in place of the NRZ data stream output from each Receive Line Interface Decoder. The Analyzer monitors one of the NRZ data stream outputs from the seven Receive Line Interface Decoders. By setting the Telecom Bus Loopback (a function of the Telecom Bus Interface block) and a Tributary Loopback for one of the seven channels, the entire channel's transmit and receive path can be verified (Synchronizer/ Mapper, VT Termination, Telecom Bus Interface, Desynchronizer/ Demapper, Transmit Line Interface and Receive Line Interface). By moving the loopbacks to Framers, LIUs, VT Switches or remote end Mappers an entire path can be verified.

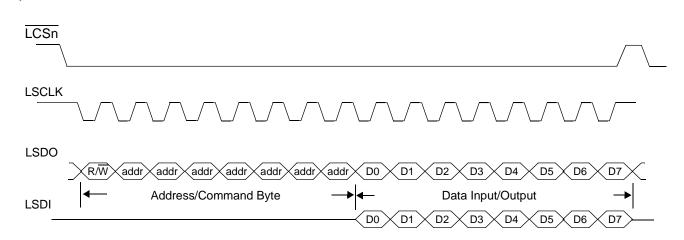

The Line Interface Control block is a common block to all seven mapper channels that provides a serial port for communicating with an external line interface transceiver that supports 'Host Mode' operation. This allows the system microprocessor to control the transceiver through the DS1MX7. The interface consists of a data output pin (LSDO), clock output pin (LSCLK), and a data input pin (LSDI). These signals are shared between all of the transceivers. Each transceiver is selected by the DS1MX7, using chip select output signals (LCSn). In addition, a general purpose input pin (LAISn) can be used in NRZ mode to generate a maskable interrupt.

#### **DATA SHEET**

The Test Access Port block is common to all seven mapper channels and includes a five-pin Test Access Port (TAP) that conforms to the IEEE 1149.1 standard. This block provides external boundary scan to read and write the DS1MX7 input and output pins from the TAP for board and component testing. In addition, a four-byte read only memory location is provided for reading the JEDEC manufacturer ID, DS1MX7 part number, and version number of the part. For non-boundary scan testing a HIGHZ pin is provided to tristate all output pins.

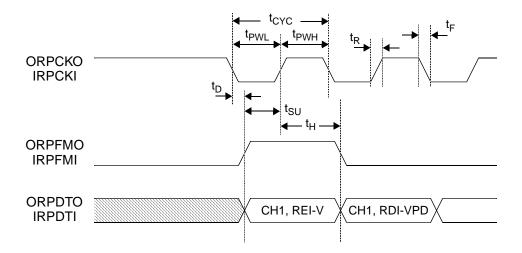

The DS1MX7 provides a common six-wire Ring Port block. A pair of DS1MX7 devices can operate on a dual bus-based Add Drop Multiplexer. Since each DS1MX7 is configured to operate in a single one direction of the ring, RDI and REI (FEBE) values need to be sent to the mate DS1MX7 so that they are returned in the opposite direction. The Ring Port is shared among the seven mapper channels to facilitate the function of sending, receiving and buffering REI (FEBE) and RDI values from and for each of the seven mapper channels. The REI (FEBE) and RDI information used by the Mapper may either come from the demap direction within the DS1MX7 (non-ring mode), from a microprocessor-forced value, or from the Ring Port. The Ring Port outputs clock, data and frame (pins ORPCKO, ORPDTO and ORPFMO), and it expects clock, data and frame as inputs (pins IRPCKI, IRPDTI and IRPFMI).

A common Auxiliary Port block is provided that makes the optional and reserved overhead bytes to and from each of the seven mapper channels available on multiplexed DS1MX7 device pins. The Auxiliary Port outputs the V5, J2, Z6/N2, Z7/K4 and O bytes as they arrive, if enabled. When mapping opportunities for J2, Z6/N2, Z7/K4 and O bytes come up the Auxiliary Port requests and inputs these bytes, if enabled. Microprocessor read and write access of these bytes is also provided.

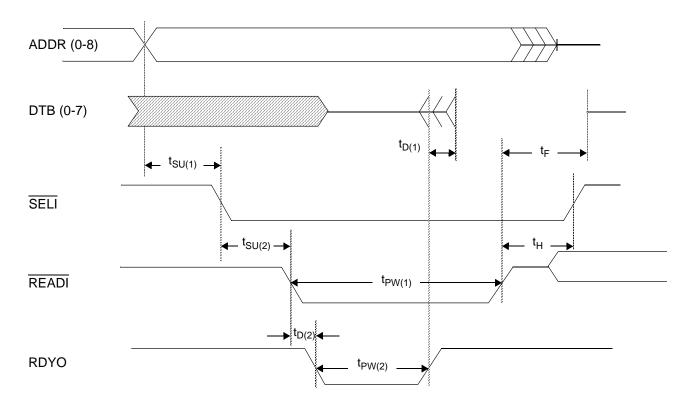

The DS1MX7 can be configured to operate with either Intel or Motorola-compatible microprocessors via the Microprocessor Input/Output Interface block. Separate address, data and control pins are provided. Interrupt capability is provided with global and individual framer mask bits as well as activity registers to guide software to the exact cause of an interrupt in the most expeditious manner. A wide variety of alarms is provided on a global level as well as on a per mapper channel level. Each alarm or error is reflected in a current status register or counter as well as a latched value register that may be set on the rising, falling or both edges of an alarm. Shadow registers for alarms and counters are provided, with the alarm shadow registers doubled to indicate either a change (performance item) or a persistent condition (fault). Any latched value may trigger an interrupt, unless it is masked to prevent it causing an interrupt. An option is provided in software which permits the interrupt polarity to be inverted. An external system clock provided at pin PCKI is used to run the internal state machines.

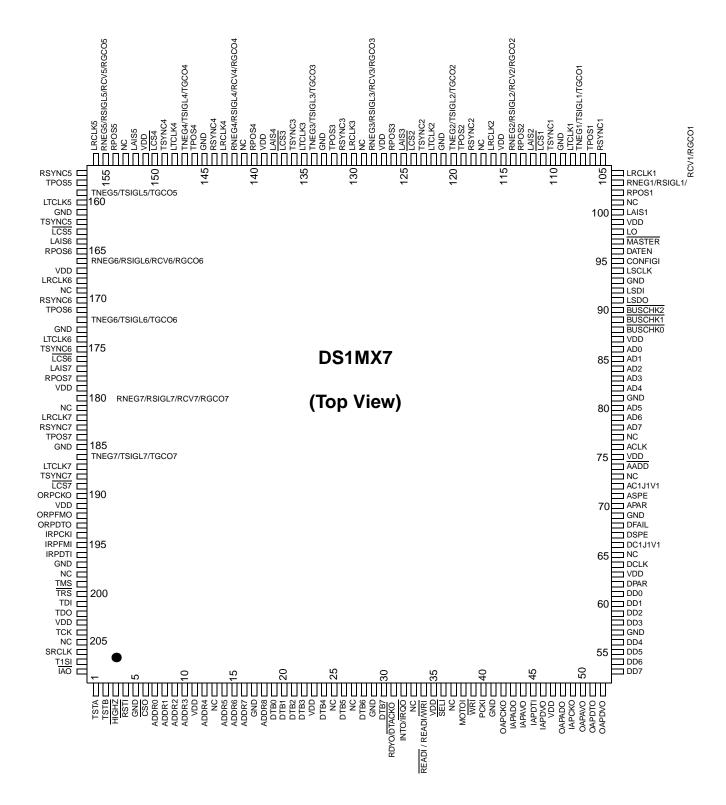

### **PIN DIAGRAM**

Figure 3. DS1MX7 TXC-04201B Pin Diagram

# **PIN DESCRIPTIONS**

### **Power Supply and Ground**

| Symbol | Pin No.                                                                              | I/O/P* | Туре | Name/Function                                                                                                                                                                          |

|--------|--------------------------------------------------------------------------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD    | 11, 23, 35, 47, 63, 75,<br>87, 99, 115, 127, 139,<br>151, 167, 179, 191, 203         | Р      |      | <b>VDD:</b> +5 volt supply, ± 5%                                                                                                                                                       |

| GND    | 5, 17, 29, 41, 57, 69,<br>81, 93, 109, 121, 133,<br>145, 161, 173, 185, 197          | Р      |      | GND: Ground                                                                                                                                                                            |

| NC     | 13, 25, 27, 33, 37,<br>65, 73, 77, 101, 117,<br>129, 141, 153, 169,<br>181, 198, 205 |        |      | NC: Not Connected. Leave floating. Do not make any external connections to these pins or connect them to one another. Connection may impair performance or cause damage to the device. |

<sup>\*</sup>Note: I = Input; O = Output; P = Power; T = Tristate

### Per Channel Tributary I/O (n = 1 to 7)

| Symbol | Pin No.                                    | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|--------------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LRCLKn | 104, 116,<br>130, 143,<br>156, 168, 182    | I/O   | CMOS   | Line Receive Clock Input: 1.544 MHz ± 200 Hz clock from DSX-1 receiver for asynchronous mapping mode; (tolerance is ± 50 Hz per ANSI and Bellcore for byte-synchronous operation). Global control bit RCAE (bit 6) in register 007H determines the active edge of this clock. Input jitter tolerance is 5 UI peak to peak from 10 Hz to 500 Hz and 0.1 UI peak to peak from 8 kHz to 40 kHz. See Bellcore TR-TSY-000499. For byte-synchronous operation with an external slip buffer for which control bits MODE1,0 (bits 1 and 0) in register X+00H are set to 10, LRCLKn is an output derived from pin LO. |

| RSYNCn | 105, 118,<br>131, 144,<br>157, 170, 183    | I/O   | CMOS   | Receive Frame Sync.: 3.0 millisecond multi-frame sync from framer, or to framer for byte-synchronous mode. Sampled on LRCLKn falling edge if global control bit RCAE (bit 6) in register 007H is set to a 0. For byte-synchronous operation with an external slip buffer for which control bits MODE1,0 (bits 1 and 0) in register X+00H are set to 10, RSYNCn is an output derived from pin LO.                                                                                                                                                                                                             |

| RPOSn  | 102, 113,<br>126, 140,<br>154, 165,<br>178 | ı     | CMOS   | Tributary Receive Data (Positive): NRZ/Positive rail. DS1 data from framer or DSX-1 Receiver. RPOSn is sampled on LRCLKn falling edge if global control bit RCAE (bit 6) in register 007H is set to a 0. In NRZ mode, global control bit RXNRZP (bit 4) in register 007 selects the polarity (a 1 selects a low as a logical one).                                                                                                                                                                                                                                                                           |

$<sup>{}^\</sup>star \text{Note:}$  See Input, Output and Input/Output Parameters section below for Type definitions.

|         | ·                                       |       |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Pin No.                                 | I/O/P | Type | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RNEGn/  | 103, 114,<br>128, 142,<br>155, 166, 180 | I/O   | CMOS | <b>Tributary Receive Data (Negative):</b> Negative rail DS1 data from DSX-1 receiver. This pin is sampled on LRCLKn falling edge if global control bit RCAE (bit 6) in register 007H is set to a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RSIGLn/ |                                         |       |      | Receive Signaling Highway Input: Signaling Highway from framer. Sampled on LRCLKn falling edge if global control bit RCAE (bit 6) in register 007H is set to a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RCVn    |                                         |       |      | <b>Tributary Receive Code Violations:</b> Code violation counter input. Sampled on LRCLKn falling edge if global control bit RCAE(bit 6) in register 007H is set to a 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RGCOn   |                                         |       |      | Receive Gapped Clock Output: When the datacom mode is selected (only available for byte-synchronous operation) via control bit DATACOM (bit 5) in per channel register X+00H being set to a 1, this pin provides a gapped clock output in which the gap appears at the Frame bit times on RPOSn.                                                                                                                                                                                                                                                                                                                                                                                      |

| LAISn   | 100, 112,<br>125, 138,<br>152, 164, 177 | I     | CMOS | Line Alarm Input: Line transceiver interrupt, AIS or Loss of Signal / Clock from DSX-1 receiver. The active level is determined by global control bit RXNRZP (bit 4) in register 007, which selects the polarity (a 1 selects a low as a logical one). A per channel control bit EXPLOS (bit 6) in register X+00H enables this pin to act as LOS if set to a 1. Control bit LOS2AIS (bit 6) in register X+01H, when set to a 1, causes this signal to propagate VT AIS upstream. When EXPLOS is set to a 0, status bit XPS (bit 7) in register X+10H becomes a separate status indication with latched, mask, performance and fault registers plus global mask and status capability. |

| LTCLKn  | 108, 122,<br>135, 148,<br>160, 174, 187 | 0     | CMOS | Line Transmit Clock Output: 1.544 MHz ± 200 Hz clock to DSX-1 line driver or framer. Global control bit TCAE (bit 7) in register 007H determines the active edge of this clock. See CSO below. The output frequency tracks the input frequency as defined by the synchronized payload. Output jitter caused by desynchronization and single pointer movements is 0.4 Ul or less peak to peak at 10 Hz and above (0.075 UI peak to peak or less from 8 kHz to 40 kHz).                                                                                                                                                                                                                 |

| TPOSn   | 106, 119,<br>132, 146,<br>158, 171, 184 | 0     | CMOS | Tributary Transmit Data (Positive): NRZ/Positive DS1 data to DSX-1 line driver or framer. Output on LTCLKn rising edge if global control bit TCAE (bit 7) in register 007H is set to a 1. In NRZ mode, global control bit TXNRZP (bit 0) in register 007H selects the polarity (a 1 selects a low as a logical one). Also see CSO below.                                                                                                                                                                                                                                                                                                                                              |

# **DATA SHEET**

| Symbol | Pin No.                                 | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------------------------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNEGn/ | 107, 120,<br>134, 147,<br>159, 172, 186 | 0     | CMOS | Tributary Transmit Data (Negative): Negative rail DS1 data to DSX-1 line driver output on LTCLKn rising edge if global control bit TCAE (bit 7) in register 007H is set to a 1. When NRZ mode is used in asynchronous mode this pin can be used as a spare output (e.g., select B8ZS/AMI in line I/F transceiver). Also see CSO below.                                                                                                        |

| TSIGLn |                                         |       |      | <b>Transmit Signaling Highway Output:</b> Signaling highway to framer. Output on LTCLKn rising edge if global control bit TCAE (bit 7) in register 007H is set to a 1. Also see CSO below.                                                                                                                                                                                                                                                    |

| TGCOn  |                                         |       |      | <b>Transmit Gapped Clock Output:</b> When the Datacom mode is selected (only available for byte-synchronous operation) via control bit DATACOM (bit 5) in per channel register X+00H being set o a 1, this pin provides a gapped clock output in which the gap appears at the frame bit times on TPOSn.                                                                                                                                       |

| TSYNCn | 110, 123,<br>136, 149,<br>162, 175, 188 | 0     | CMOS | Transmit Frame Sync: 3.0 millisecond multi-frame sync to framer. Output on LTCLKn rising edge if global control bit TCAE (bit 7) in register 007H is set to a 1. Also see CSO below.                                                                                                                                                                                                                                                          |

| LCSn   | 111, 124,<br>137, 150,<br>163, 176, 189 | 0     | CMOS | Line Interface Transceiver Chip Select: An active low signal that enables communications in both directions between the external line interface transceiver for channel n and the DS1MX7. This pin is under control of global register 01AH where ENSRP (bit 4) enables transmission to channel n, which is selected by BDCST (bit 7) to select all channels or the channel selection controls (bits 2-0) which select one of the 7 channels. |

# **Tributary Common Control**

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                   |

|--------|---------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LO     | 98      | I     | CMOS | Local Oscillator: 1.544 MHz ± 32 ppm system clock input used for byte-synchronous mode. 1.544 MHz synchronized to system (ASPE, ACLK and a specific J1 of AC1J1V1) for byte-synchronous operation where LRCLKn and RSYNCn are outputs. This signal is also used to generate the serial port clock output LSCLK. |

| SRCLK  | 206     | I     | CMOS | System Reference Clock: $48.636~\text{MHz} \pm 32~\text{ppm}$ (31.5 times 1.544 MHz) system clock input used to operate the synchronizer, desynchronizer, PRBS generator/ analyzer, and to generate DS1 AIS.                                                                                                    |

| _      |         | l     | _                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|---------|-------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol | Pin No. | I/O/P | Туре                      | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LSDO   | 91      | 0     | CMOS                      | Line Interface Transceiver Data Output Signal: Common serial control data bus output shared by the seven channels. A command byte followed by a data byte, as stored in control registers 017H and 018H respectively, is transmitted to the line interface transceiver selected by LCSn.                                                                                                                                                                                                                                                                                                                                               |

| LSDI   | 92      | I     | CMOS                      | Line Interface Transceiver Data Input Signal: Common serial control data bus input. A data byte coincident with the data byte on LSDO is clocked into the DS1MX7 and stored in register 019H from the line interface transceiver selected by LCSn.                                                                                                                                                                                                                                                                                                                                                                                     |

| LSCLK  | 94      | 0     | CMOS                      | Line Interface Transceiver Clock Signal: Common serial control bus clock output. A 1.544 MHz clock derived from LO. LSDO is clocked out of the DS1MX7 on the falling edge of LSCLK and LSDI is clocked into the DS1MX7 on the rising edge of LSCLK.                                                                                                                                                                                                                                                                                                                                                                                    |

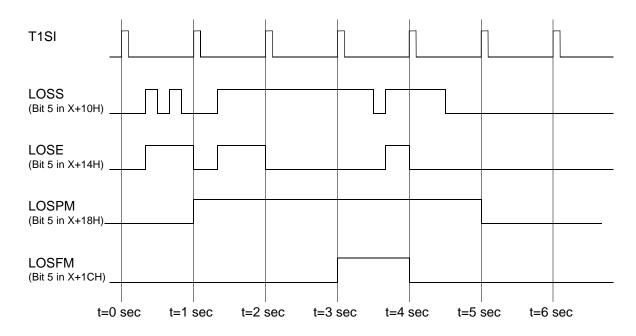

| T1SI   | 207     | I     | TTL                       | One Second Performance Clock Input: Shadow register latch. This input operates the latched counters and PM/FM registers. The following parameter value limits are suggested to prevent counters from overflowing when operating in noisy environments or other unfavorable conditions: min. high time 0.50 ms; min. low time 3.0 ms; max. low time 1.5 s. Operation at 1.0 Hz ± 32 ppm, 1.0 ms high time, is recommended. This clock is used in conjunction with global control bit ENPMFM (bit 3) in register 006H to clear per channel event registers (not device event registers) after the PM and FM registers have been updated. |

| ĪAO    | 208     | 0     | CMOS open<br>drain (4 mA) | Internal Alarm Output: Internal Alarm detected, active low output. Control bits in registers 01BH and 01CH, if set to a 1, enable Telecom Bus clock, payload and synch. failures, as well as parity errors and PRBS out of lock, to generate an alarm or interrupt on this pin.                                                                                                                                                                                                                                                                                                                                                        |

| CSO    | 6       | I     | TTL                       | Card Switch Off: When driven low, LTCLKn, TPOSn, TNEGn/TSIGLn and TSYNCn are driven to a logic low level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# **DATA SHEET**

# **System Interface**

| Symbol  | Pin No.                              | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|---------|--------------------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DCLK    | 64                                   | I     | TTL  | <b>Drop Bus Clock:</b> Telecom Bus clock for data from system; 6.48 MHz for pin CONFIGI tied high or 19.44 MHz for pin CONFIGI tied low. Control bit TBRCI (bit 4) in register 01EH set to a 0 selects the rising edge of DCLK as the active edge.                                                                                                                                                                                                                                  |  |  |

| DC1J1V1 | 66                                   | I     | TTL  | Drop Bus C1J1V1 Indicator: Telecom Bus C1#1, J1#1 or V1#1 valid from system. Valid on the rising edge of DCLK when control bit TBRCI (bit 4) in register 01EH i set to a 0. Used with DSPE to identify the start of the payload.                                                                                                                                                                                                                                                    |  |  |

| DSPE    | 67                                   | I     | TTL  | <b>Drop Bus SPE Indicator:</b> Telecom Bus SPE valid from system. Valid on rising edge of DCLK when control bit TBRCI (bit 4) in register 01EH is set to a 0. This signal is high during all VT1.5 or TU-11 bytes from the system.                                                                                                                                                                                                                                                  |  |  |

| DD(0-7) | 61, 60, 59,<br>58, 56, 55,<br>54, 53 | I     | TTL  | <b>Drop Bus Data:</b> Telecom Bus data from system; DD0 is LSB. Valid on rising edge of DCLK when control bit TBRCI (bit 4) in register 01EH is set to a 0.                                                                                                                                                                                                                                                                                                                         |  |  |

| DPAR    | 62                                   | I     | TTL  | Drop Bus Parity Bit: Telecom Bus parity received over DD(0-7), DSPE and DC1J1V1. Valid on rising edge of DCLK when control bit TBRCI (bit 4) in register 01EH is set to a 0; odd/even selectable by control bit TBPE (bit 2) in register 007H; when set to a 1, even parity is selected. When control bit TBPIS (bit 3) in register 007H is set to a 0 only DD(0-7) is checked for parity.                                                                                          |  |  |

| DFAIL   | 68                                   | I     | TTL  | Drop Bus Signal Fail: Signal fail indication valid on the rising edge of DCLK when control bit TBRCI (bit 4) in register 01EH is set to a 0. If DFAIL is high the specific VT slot contains invalid data (DD(0-7)); the per VT alarms are invalid and are masked; DS1 AIS is generated.                                                                                                                                                                                             |  |  |

| ACLK    | 76                                   | I     | TTL  | Add Bus Clock: Telecom Bus clock for data to system; 19.44 MHz for pin CONFIGI tied high or 6.48 MHz for pin CONFIGI tied low. When control bit TBTCI (register 01EH, bit 5) is set to a 0, the ASPE and AC1J1V1 signals are clocked in on the rising edge of ACLK. The falling edge of ACLK is used to clock the AD(0-7), APAR and AADD signals out to the Add Bus so that these signals can be sampled on the next rising edge. When TBTCI = 1 the opposite clock edges are used. |  |  |

| AC1J1V1 | 72                                   | I     | TTL  | Add Bus C1J1V1 Indicator: Telecom Bus C1#1, J1#1, V1#1 valid for data to system. This signal is sampled on the rising edge of ACLK when control bit TBTCI (register 01EH, bit 5) is set to a 0. Used with ASPE to indicate the start of the payload to the system.                                                                                                                                                                                                                  |  |  |

# TRANSWITCH'

| Symbol      | Pin No.                              | I/O/P | Туре    | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |