EtherMap®-3 Plus Device **OC-3 Ethernet over SONET Mapper** with Rapid Restoration TXC-04236 **DATA SHEET**

#### **FEATURES**

- Eight 10/100 Mbit/s Ethernet ports, each using a SMII interface

- Single 1000 Mbit/s Ethernet port, using a parallel GMII interface (lead shared with SMII interfaces)

- Ethernet Management interface for control and configuration

- of externally connected PHYs Provides IEEE 802.3 Half Duplex mode on 10/100 Mbit/s and Full Duplex mode on 10/100/1000 Mbit/s Ethernet ports

- Provides IEEE 802.3 Management Statistics (RMON)

- Provides IEEE 802.3 Management Statistics (RMON) Ethernet frame encapsulation/decapsulation protocols:

ITU-T G.7041, Generic Framing Procedure (GFP)

ITU-T X.86/X.85, Link Access Procedure SDH (LAPS)

ITU-T Q.922, Link Access Procedure Frame Mode (LAPF)

RFC1662/3518, PPP Bridging Control Protocol (BCP)

Performs mapping/demapping of encapsulated Ethernet frames into/from low order (VT1.5 SPE/VT2 SPE/VC-11/VC-12) and high order (STS-1 SPE/VC-3) virtually concatenated payloads

- payloads

Performs mapping/demapping of encapsulated Ethernet

frames into/from a single contiguous concatenated (STS-3cSPE/VC-4) payload or a single Low/High order

(VT1.5/VT2/VC-11/VC-12/STS-1/VC-3) payload

Dynamic bandwidth allocation using on-chip LCAS

processing (ITU-T G.7042) for low and high order virtual

concatenated payloads

Clueless memory interface to external 64/128/256 Mbit

- Glueless memory interface to external 64/128/256 Mbit

- SDRAMs Low Order POH and Pointer processing for 84/63 VT1.5/VT2/TU-11/TU-12 and 3 TU-3

- High Order POH processing for STS-1 SPE/VC-3/STS-3c

- Byte-wide 19 MHz parallel Add and Drop Telecom Bus

- Per-port Ethernet side and SONET/SDH system side loopback for system level diagnostics

- 16-bit wide microprocessor interface, selectable between Motorola or Intel

- Boundary scan (IEEE 1149.1 standard)

- + 3.3V and +1.8V power supplies, 5V tolerant I/O leads

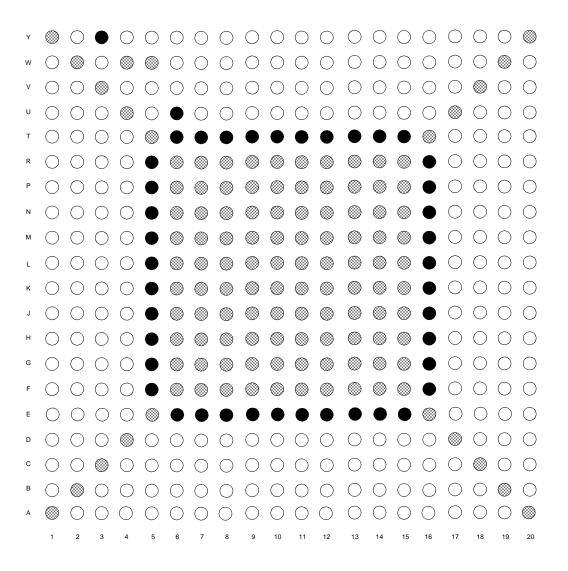

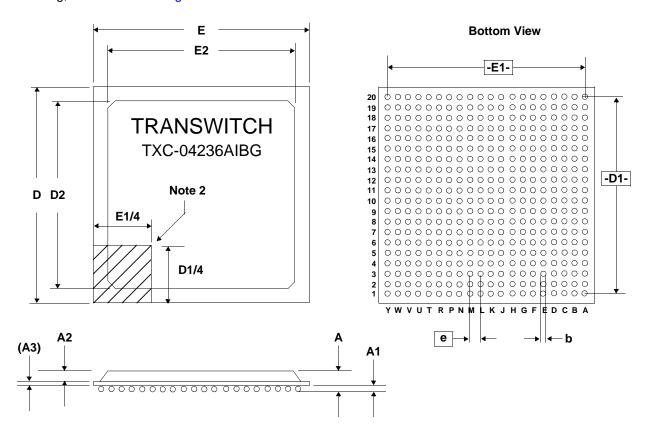

- 400-lead plastic ball grid array package (PBGA, 27 mm x 27 mm) Device Driver

#### DESCRIPTION

The EtherMap®-3 Plus is a highly integrated EoS device that provides for mapping of 10/100/1000 Mbit/s Ethernet into SONET/SDH STS-3/STM-1 Transport payloads. The device supports connection for up to eight 10/100 Mbit/s Ethernet ports, using SMII interfaces, or a single 1000 Mbit/s Ethernet port, using a GMII interface. Ethernet frames are encapsulated using either GFP, LAPS, LAPF or PPP/BCP protocol. The encapsulated Ethernet frames are then mapped into either virtually concatenated low or high order payloads, such as VT1.5 SPE/VT2 SPE/VC-11/VC-12/STS-1 SPE/VC-3, or into contiguously concatenated payloads such as STS-3c SPE/VC-4. Low and high order SONET/SDH POH generation and processing/termination is performed. A byte-wide parallel interface Telecom Bus format provides the SONET/SDH interface and may support either Drop bus or Add bus timing modes.

In addition to support for full-rate Ethernet transfer, over-subscribed In addition to support for full-rate Ethernet transfer, over-subscribed Ethernet transfers are also supported using back pressure mechanisms (half and full duplex flow control) in order to prevent frame loss. External SDRAM is used for buffering Ethernet frames to support bandwidth oversubscription and flow control operation as well as receive SONET/SDH container alignment and differential delay compensation of low and high order with talk concentrated particular. low and high order virtually concatenated payloads.

For both low and high order virtually concatenated payloads, optional onchip standards based LCAS processing is provided to allow hitless dynamic bandwidth adjustments.

A powerful hardware and RTOS independent EtherMap device driver provides full access to all the features of the device through APIs. It utilizes matched get/set functions and can be easily ported.

#### APPLICATIONS

- SONET/SDH add/drop and terminal multiplexers

- Multi-service access platforms (MSAP)

- Compact Access or CPE platforms

- IP DSLAMS

- Wireless Backhaul Electronics (RNC/BSC)

U.S. and/or foreign patents issued or pending Copyright © 2004 TranSwitch Corporation EtherMap, PHAST, TEMx28, TranSwitch and TXC are registered trademarks of TranSwitch Corporation

**Document Number:** PRELIMINARY TXC-04236-MB, Ed. 3 July 2004 PRELIMINARY information documents contain information on products in the pre-production or early production phases of the product life cycle. **Fran Switch** sampling,

## **TABLE OF CONTENTS**

| Section                                                                                             | Page  |

|-----------------------------------------------------------------------------------------------------|-------|

| List of Figures                                                                                     |       |

| List of Tables                                                                                      |       |

| Features                                                                                            | _     |

| Encapsulation Protocols                                                                             | 15    |

| Ethernet Ports                                                                                      | 16    |

| 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) Block                                     | 16    |

| SDRAM Interface                                                                                     | 16    |

| Telecom Bus Timing                                                                                  | 16    |

| Alarm Indication Port Interface                                                                     | 17    |

| POH Port Interface                                                                                  | 17    |

| Microprocessor Interface                                                                            |       |

| JTAG Interface                                                                                      |       |

| Block Diagram                                                                                       |       |

| Data Processing/Flow                                                                                | 19    |

| 10/100/1000 Mbit/s Ethernet Media Access Controller (MAC) Block                                     | 19    |

| SONET/SDH Mapping                                                                                   | 23    |

| Mapper Block                                                                                        | 23    |

| Demapper Block                                                                                      | 25    |

| Ethernet Ports                                                                                      | 27    |

| Microprocessor Interface                                                                            | 27    |

| SDRAM Memory Interface                                                                              | 27    |

| Parallel Telecom Bus Interface                                                                      | 27    |

| High and Low Order POH (Path Overhead Byte) Port Interface                                          | 29    |

| High and Low Order Alarm Indication Port Interface                                                  | 29    |

| JTAG Interface                                                                                      | 29    |

| Power-Up Sequencing                                                                                 | 29    |

| Application Example                                                                                 | 30    |

| Lead Diagram                                                                                        |       |

| Lead Descriptions                                                                                   | 32    |

| Absolute Maximum Ratings and Environmental Limitations (Referenced to VSS)                          | 47    |

| Thermal Characteristics                                                                             | 47    |

| Power Requirements                                                                                  | 48    |

| Input, Output and Input/Output Parameters                                                           | 49    |

| Timing Characteristics Operation                                                                    | 54    |

| SONET/SDH Processing                                                                                | 93    |

| General                                                                                             |       |

| Transmit High Order Path Termination (VC-3/VC-4/STS-1/STS-3C POH Generator)                         | 97    |

| General                                                                                             |       |

| J1                                                                                                  | 97    |

| B3                                                                                                  |       |

| C2                                                                                                  | -     |

| G1                                                                                                  |       |

| H4                                                                                                  |       |

| F2, F3/Z3, K3/Z4, and N1/Z5Receive High Order Path Termination (VC-3/VC-4/STS-1/STS-3C POH Monitor) | 98    |

| General                                                                                             | 98    |

| J1                                                                                                  |       |

| B3                                                                                                  |       |

| C2                                                                                                  |       |

| G1                                                                                                  |       |

| H4                                                                                                  | . 100 |

| F2, F3/Z3, K3/Z4, and N1/Z5                                                                         |       |

| High Order POH Port Interface                                                                       | . 100 |

| High Order Alarm Indication Port Interface                                                          |       |

| AU-4 and AU-3 Pointer Generation                                                                    |       |

| Drop Bus Timing Mode                                                                                |       |

| Add Bus Timing Mode 1                                                                               |       |

| TU-3 Pointer Generation                                                                             |       |

| TU-3 Pointer Tracking                                                                               |       |

| VC-3/STS-1/TUG-3 Timeslot Interchange                                                               |       |

| VT/TU Pointer Tracking                                                                              | . 103 |

| VT/TU Pointer Generation                                                                            | . 103 |

| Low Order Timeslot Interchange                                                                      |       |

# TABLE OF CONTENTS (cont.)

| Section F                                                     | a   | ge   |

|---------------------------------------------------------------|-----|------|

| Transmit Low Order Path Termination (Low Order POH Generator) | . 1 | 04   |

| General                                                       | . 1 | 104  |

| J2                                                            |     |      |

| BIP-2                                                         |     |      |

| Signal Label                                                  |     |      |

| REI/RDI                                                       |     |      |

| K4/Z7 Bit 2                                                   |     |      |

| V5 RFI                                                        |     |      |

| Receive Low Order Path Termination (Low Order POH Monitor)    |     |      |

| General                                                       |     |      |

| J2                                                            |     |      |

| BIP-2                                                         |     |      |

| Signal Label                                                  |     |      |

| RĚI/RDI/RFI                                                   |     |      |

| K4/Z7 Bit 2                                                   |     |      |

| N2/Z6                                                         |     |      |

| Low Order and High Order Path Monitor Alarm Registers         | . 1 | 108  |

| Low Order POH Port Interface                                  | . 1 | 110  |

| Low Order Alarm Indication Port Interface                     | . 1 | 111  |

| Virtual Concatenation and LCAS                                | . ! | 112  |

| Low Order Virtual Concatenation without LCAS                  | . ¦ | 115  |

| Low Order Virtual Concatenation with LCAS                     | . ¦ | 115  |

| High Order Virtual Concatenation without LCAS                 | . 1 | 116  |

| High Order Virtual Concatenation with LCAS                    | . 1 | 119  |

| Configuration for Virtual concatenation and LCAS              | . 1 | 120  |

| General                                                       | . 1 | 20   |

| Configuring Transmit VCAT (Ethernet to SONET/SDH)             | . 1 | 21   |

| Configuring Receive VCAT (SONET/SDH to Ethernet)              | . 1 | 122  |

| LCAS-Specific Configuration - Transmit                        | . 1 | 123  |

| Dynamic Mapping and Virtual Concatenation Changes             | . ! | 124  |

| VCG Tributary Assignments (Adding and Removing Members)       | . ¦ | 124  |

| Changing VCG Encapsulation/Decapsulation Mode                 | . i | 126  |

| Changing VCG SONET/SDH Structure                              | . i | 126  |

| Differential Delay Compensation                               | . 1 | 129  |

| Maximum Differential Delay Allowed                            | . 1 | 129  |

| Maximum Differential Delay Detected                           | . 1 | 30   |

| Ethernet Support                                              |     |      |

| SMII and GMII Interfaces                                      |     |      |

| Ethernet MAC Blocks                                           |     |      |

| Ethernet Frame Size                                           |     |      |

| Carrier Sense                                                 |     |      |

| Collision Detection                                           |     |      |

| Alternate BEB Truncation                                      |     |      |

| Excessive Collisions                                          |     |      |

| Half-Duplex Flow Control                                      | . 1 | 135  |

| Flow Control Operation                                        | . 1 | 36   |

| Overview                                                      |     |      |

| Full Duplex flow control                                      |     |      |

| Definitions                                                   |     |      |

| Flow Control Algorithm                                        |     |      |

| External Pause Frames                                         |     |      |

| Configuring Full Duplex Flow Control                          | .   | 137  |

| Changing Configurations                                       |     |      |

| Encapsulation/Decapsulation                                   |     |      |

| Setting the Encapsulation Mode                                | . i | 139  |

| Changing the Encapsulation Mode                               | . 1 | 140  |

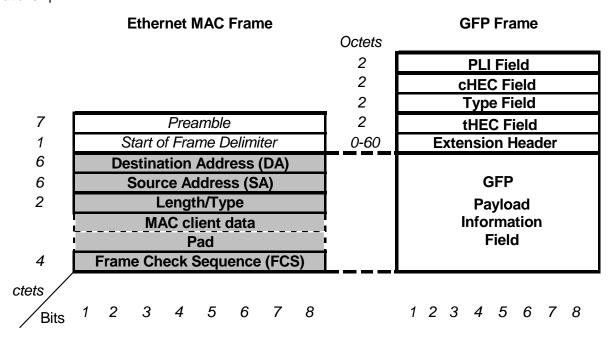

| GFP                                                           | . 1 | 141  |

| GFP Host Insertion/Extraction of Management/Control Frames    |     |      |

| GFP Linear Frame Mode Operation                               | . 1 | 50   |

| Transmit Side Linear Extension Header                         | . 1 | 15() |

| Receive Side Linear Extension Header                          |     |      |

| Receive Side CID Configuration Tables                         |     |      |

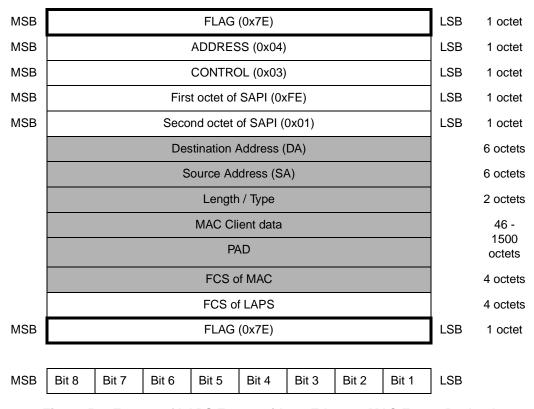

| LAPS                                                          |     |      |

# TABLE OF CONTENTS (cont.)

| Section                                                                                            | Page  |

|----------------------------------------------------------------------------------------------------|-------|

| LAPF                                                                                               |       |

| PPP (with BCP and LCP Support)                                                                     | . 170 |

| SDRAM Controller                                                                                   |       |

| SDRAM Memory Interface                                                                             | . 183 |

| CAS LatencyBANK/ROW Activation                                                                     | . 103 |

| Commands                                                                                           |       |

| Reset Configuration of SDRAM Controller                                                            | 184   |

| Configuration Changes/Initialization                                                               | 184   |

| Microprocessor Access to SDRAM                                                                     | . 185 |

| Reset Operation                                                                                    | . 186 |

| General External Lead Controlled Hardware Reset                                                    | . 186 |

| Microprocessor Controlled Hardware Reset                                                           | 186   |

| Microprocessor Controlled Soft Reset                                                               | 186   |

| Microprocessor Controlled Global Performance Counter Reset                                         | . 186 |

| Telecom Bus Operation                                                                              | . 187 |

| General                                                                                            | 187   |

| Drop Bus Interface                                                                                 | . 187 |

| Drop Bus Parity Selection                                                                          |       |

| Add Bus Interface                                                                                  | 188   |

| Add Bus Parity Selection                                                                           | 189   |

| Add Bus Delay                                                                                      |       |

| Telecom Bus Tributary Activation/Tri-State Control                                                 | 191   |

| VC-3/VC-4                                                                                          |       |

| TUG-3                                                                                              |       |

| TUG-2                                                                                              |       |

| TU-11/TU-12                                                                                        |       |

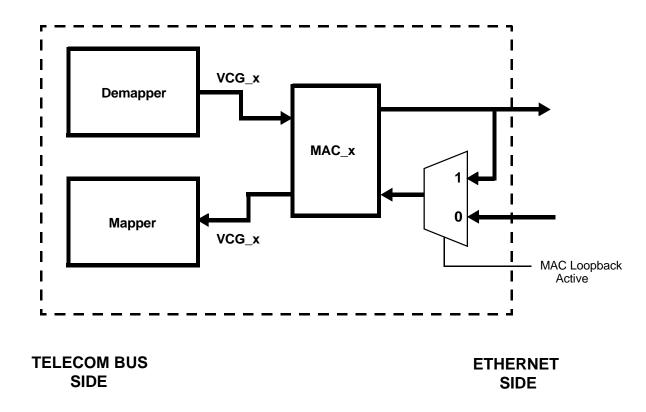

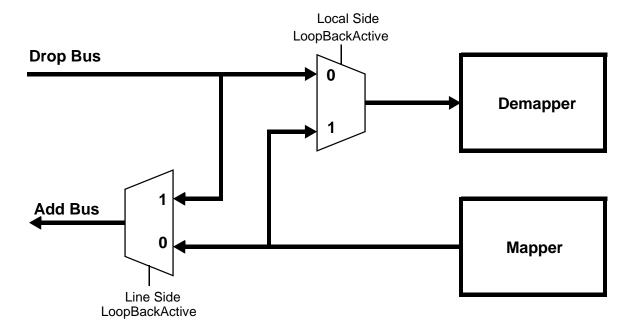

| MAC Loopback                                                                                       |       |

| Telecom Bus Loopbacks                                                                              |       |

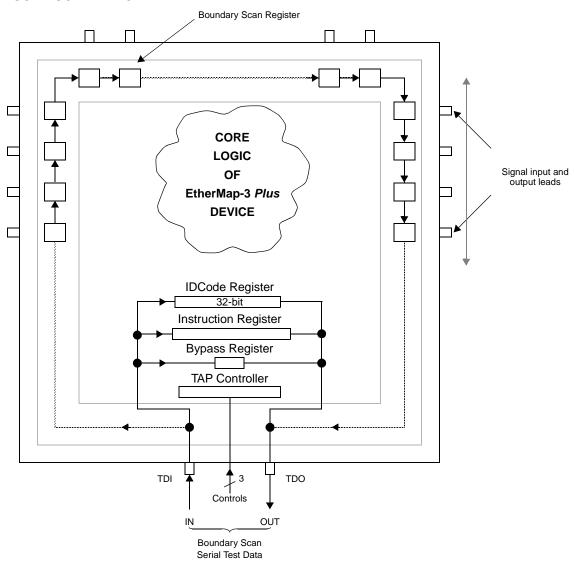

| Boundary Scan                                                                                      | . 195 |

| Introduction                                                                                       | . 195 |

| Boundary Scan Operation                                                                            |       |

| Boundary Scan Schematic                                                                            | . 196 |

| Boundary Scan Chain                                                                                | 107   |

| General Device Registers                                                                           | 200   |

| Table 10 through 12 - General Configuration and Status of the Device                               | . 200 |

| Ethernet MAC Registers                                                                             | 201   |

| Tables 13 through 17 - Status Information of the MAC                                               | . 201 |

| Tables 18 through 23 - Configuration of the MAC                                                    | . 210 |

| Ethernet MAC Registers                                                                             | . 215 |

| Tables 30 through 34 - Configuration, Alarms and Interrupts of the Ethernet MACs                   | 217   |

| Tx Encapsulation Registers                                                                         | 219   |

| Tables 35 through 47 - Configuration, Status and Alarms of the Encapsulation Block                 | . 219 |

| Rx Decapsulation Registers                                                                         | 236   |

| Tables 48 through 61 - Configuration, Status and Alarms of the Decapsulation Block                 | . 236 |

| SDRAM Control Registers                                                                            | . 268 |

| Table 62 - SDRAM Control and SDRAM Interface Configuration                                         | . 268 |

| Tx Virtual Concatenation Registers                                                                 | 270   |

| Tables 65 through 75 - Configuration, Status and Alarms of the Transmit (Ethernet to SONET)        | . 210 |

| Virtual Concatenation Block                                                                        | 270   |

| Rx Virtual Concatenation Registers                                                                 | . 283 |

| Tables 76 through 85 - Configuration, Status and Alarm of the Receive                              |       |

| (SONET to Ethernet) Virtual Concatenation Block                                                    | . 283 |

| Ethernet to SONET Handling Registers                                                               | . 295 |

| (Output of the Ethernet MAC)                                                                       | 205   |

| Table 91 through 103 - Ethernet Buffering and Flow Control in Transmit (Ethernet to SONET)         | . 200 |

| and Receive (SONET to Ethernet) Paths                                                              | . 296 |

| Tx Mapper Block Registers                                                                          | 302   |

| Tables 104 through 107 - Configuration, Status and Interrupt handling of the Transmit Mapper Block | . 302 |

| Tables 108 through 118 - Configuration of the Transmit Mapper Block                                |       |

| Rx DeMapper Block Registers                                                                        | . 306 |

| rabios fro allough for - conliguration, claus and Alamb for the Necetive Demapper Diock            | . 500 |

## **TABLE OF CONTENTS** (cont.)

| Section                                                                                                                                | age          |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Tables 132 through 154 - Configuration, Status and Alarms of the Low Order POH Monitor                                                 | . 308        |

| Tables 155 through 162 - Configuration, Status and Alarms of the Low Order                                                             |              |

| Tx Alarm Indication (RING) Port                                                                                                        | . 316        |

| Table 163 - Configuration of the Low Order Rx Alarm Indication (RING) Port                                                             | . 317        |

| Tables 164 through 166 - Configuration and Status of the general Low Order Interrupt Controller                                        | . 318        |

| Table 167 - Configuration of the High Order Rx Alarm Indication (RING) Port                                                            | . 318        |

| Tx Alarm Indication (RING) Port                                                                                                        | 318          |

| Tables 177 through 209 - Configuration, Status and Alarms of the High Order POH Monitor                                                | . 310<br>320 |

| Tables 210 through 222 - Configuration, Status and Alarms of the TU-3 PTR Tracker                                                      | . 332        |

| Tables 223 and 224 - Configuration of TU-3 Cross Connect                                                                               |              |

| Tables 225 through 237 - Configuration, Status and Alarms of the TU-3 PTR Generator                                                    | . 335        |

| Tables 238 through 242 - Configuration of High Order (VC-3 and VC-4) POH Generator                                                     | . 337        |

| Tables 243 through 250 - Configuration, Status and Alarms of the TU-3 Retimer                                                          | . 339        |

| Tables 251 through 258 - Configuration, Status and Alarms of the AU-3/4 Retimer                                                        |              |

| Tables 259 through 261 - Configuration and Status of the General High Order Interrupt Controller                                       | . 342        |

| Tables 262 through 280 - Configuration, Status and Alarms of the Rx Combus Interface                                                   |              |

| Tables 303 through 305 - Configuration and Status of the General Combus Interface Interrupt Controller                                 |              |

| Tables 306 through 308 - Configuration and Status of the General VTMAPPER Interrupt Controller                                         | 351          |

| Alarms, Performance and Fault Monitoring                                                                                               | . 353        |

| Terminology                                                                                                                            | . 353        |

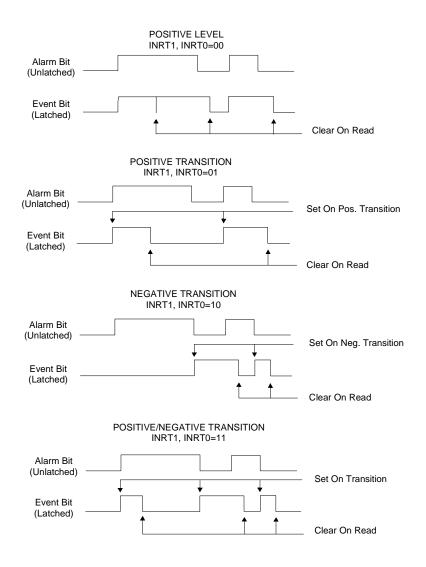

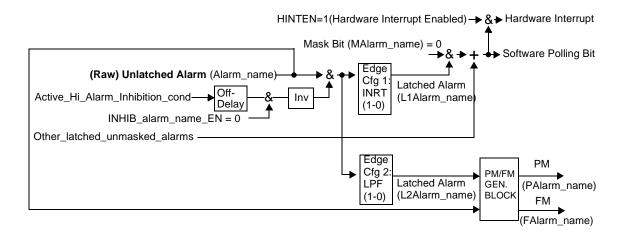

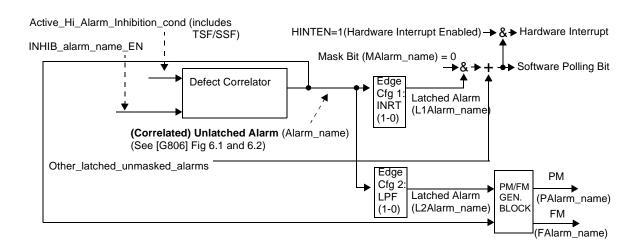

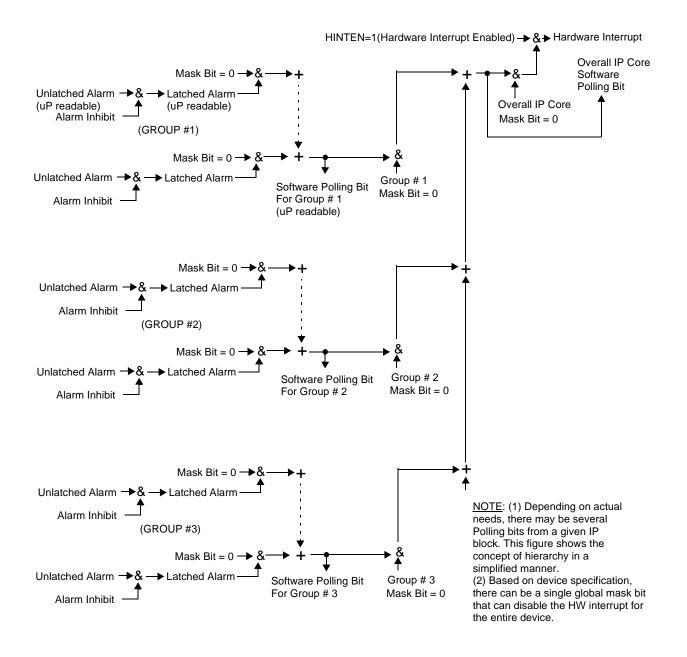

| System Alarm (Raw, Unlatched Alarm)                                                                                                    | . 353        |

| Alarm Event                                                                                                                            |              |

| Latched Alarm                                                                                                                          |              |

| Secondary Alarm Inhibition                                                                                                             |              |

| Interrupt Mask                                                                                                                         | . 354        |

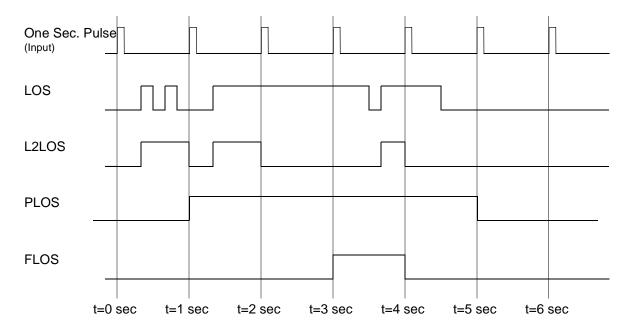

| Performance and Fault Monitoring (PM and FM)                                                                                           | . 354<br>354 |

| Performance Monitoring (PM) Fault Monitoring (FM)                                                                                      | . 354<br>351 |

| 1-Second Clock                                                                                                                         |              |

| Performance Counters                                                                                                                   |              |

| Unlatched Alarms                                                                                                                       |              |

| Inhibition of Secondary Unlatched Alarm Generation                                                                                     | . 355        |

| Latched Alarms                                                                                                                         | . 355        |

| Latched Alarm Bits for Interrupt Generation (Lalarm_name/L1alarm_name)                                                                 | . 356        |

| Latched Alarm Masking Bits (Malarm_name)                                                                                               | . 357        |

| Secondary Latched Alarm Inhibition                                                                                                     | . 358        |

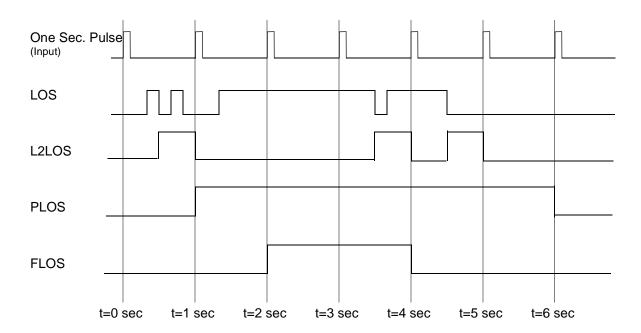

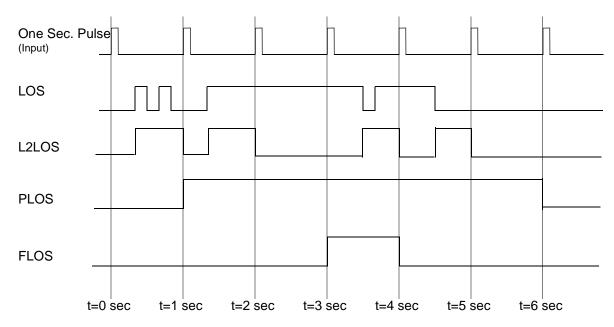

| Latched Alarm Bits for PM/FM (L2ALARM_name), Performance Monitoring (PM Bits; Palarm_name) and Fault Monitoring (FM Bits; Falarm_name) | 350          |

| Positive Edge Events                                                                                                                   | . 339<br>360 |

| Negative Edge Events                                                                                                                   | . 361        |

| Positive or Negative Edge Events                                                                                                       | . 362        |

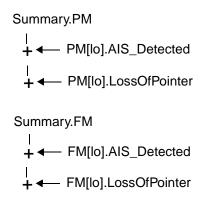

| Overall Alarm Generation and PM/FM Process Diagram                                                                                     | . 363        |

| Performance Counters                                                                                                                   |              |

| Scheme A - Counters with Roll-Over/Saturation Option                                                                                   | . 364        |

| Scheme B - Performance Counters with 1-second Shadow Register Option                                                                   |              |

| Alarm Feature Combinations                                                                                                             | . 365        |

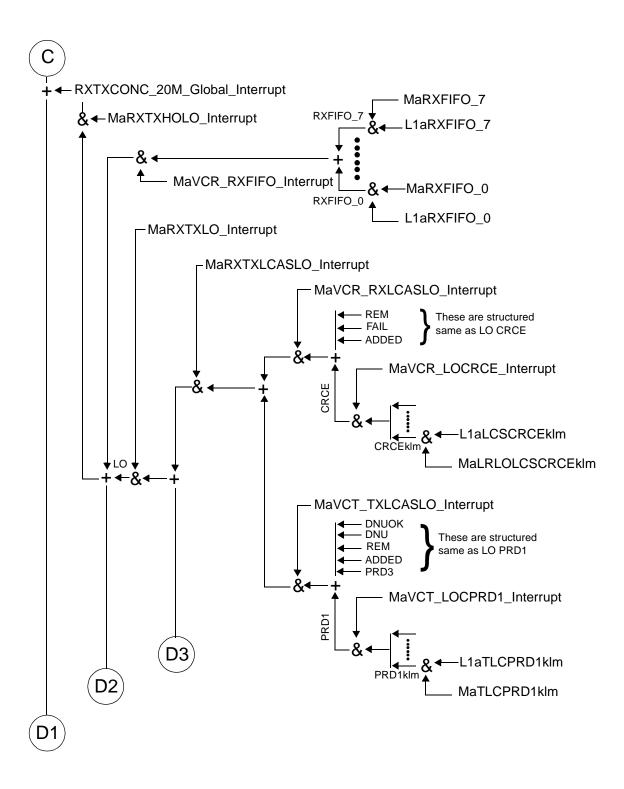

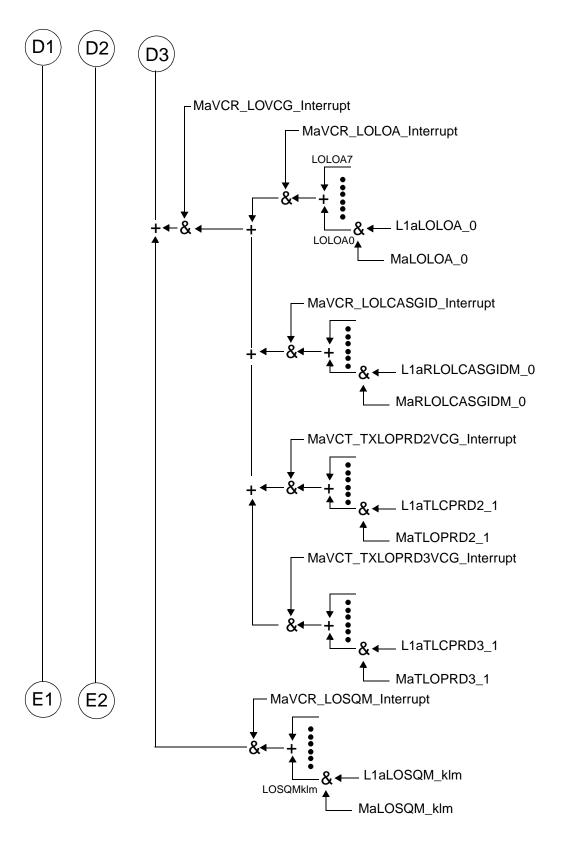

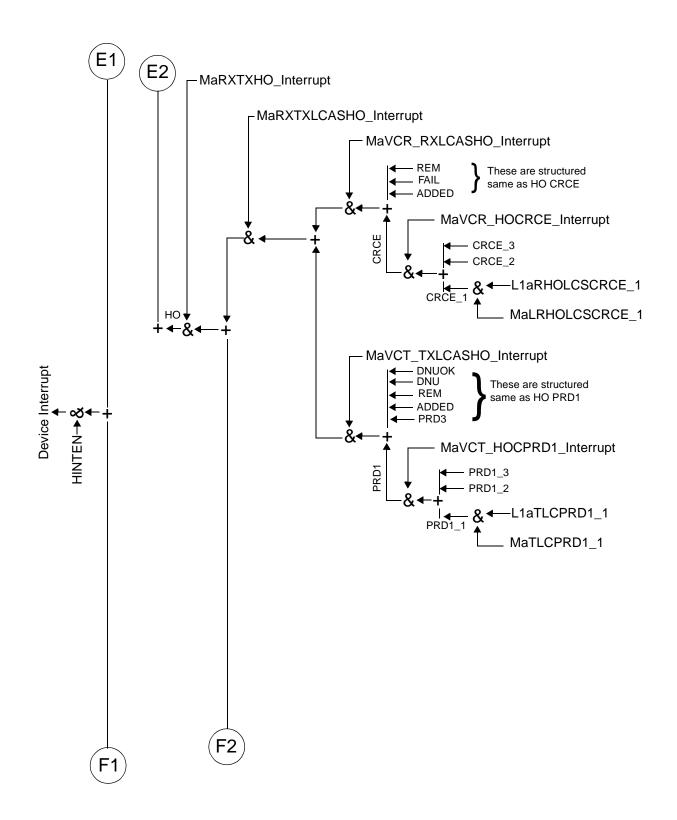

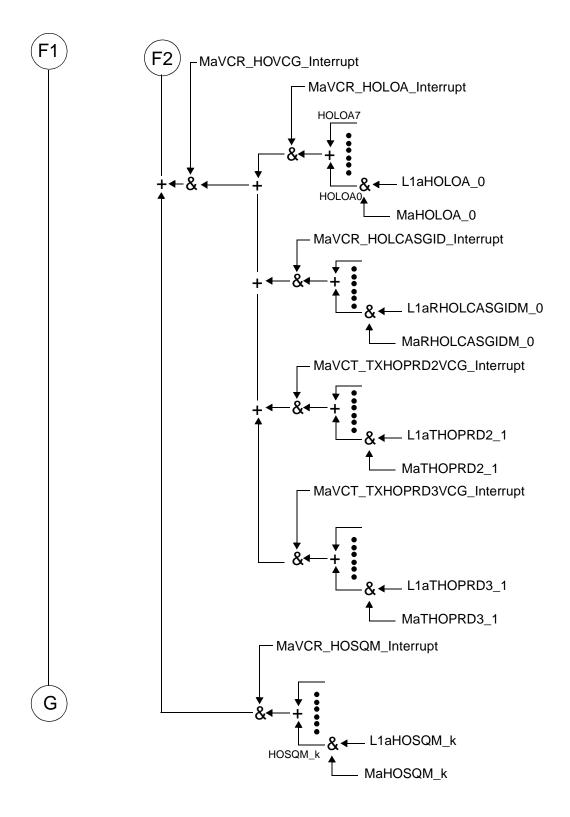

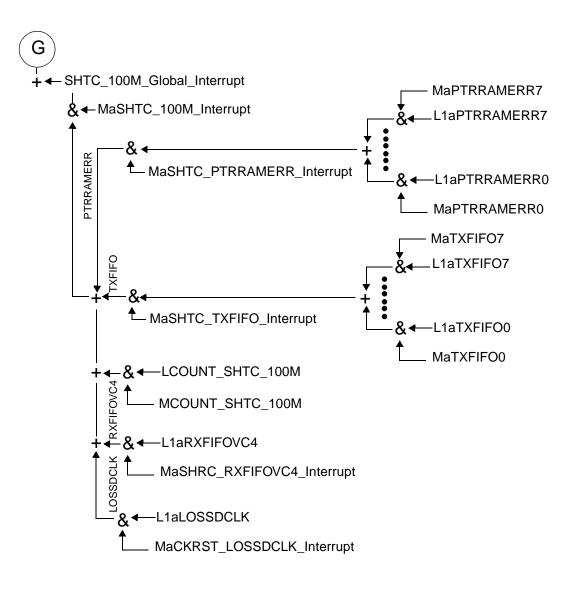

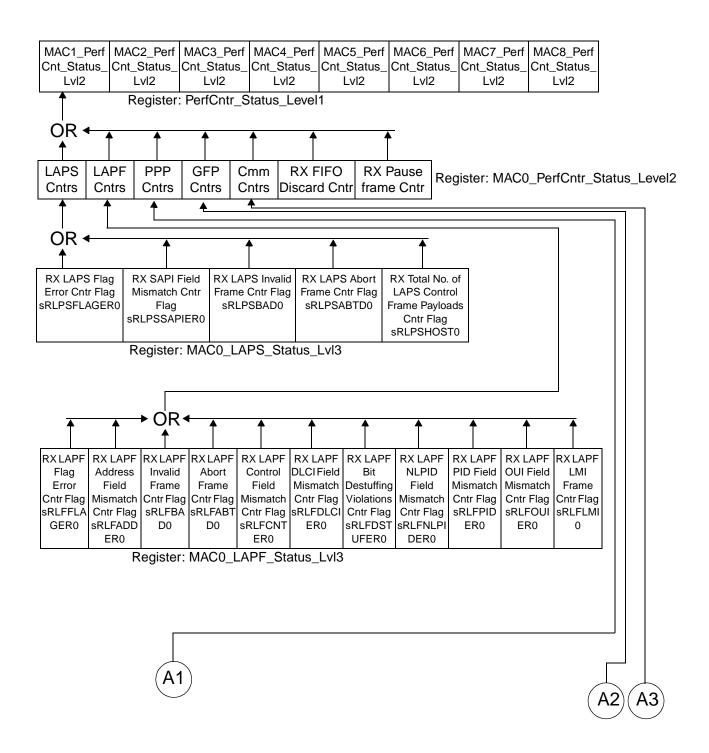

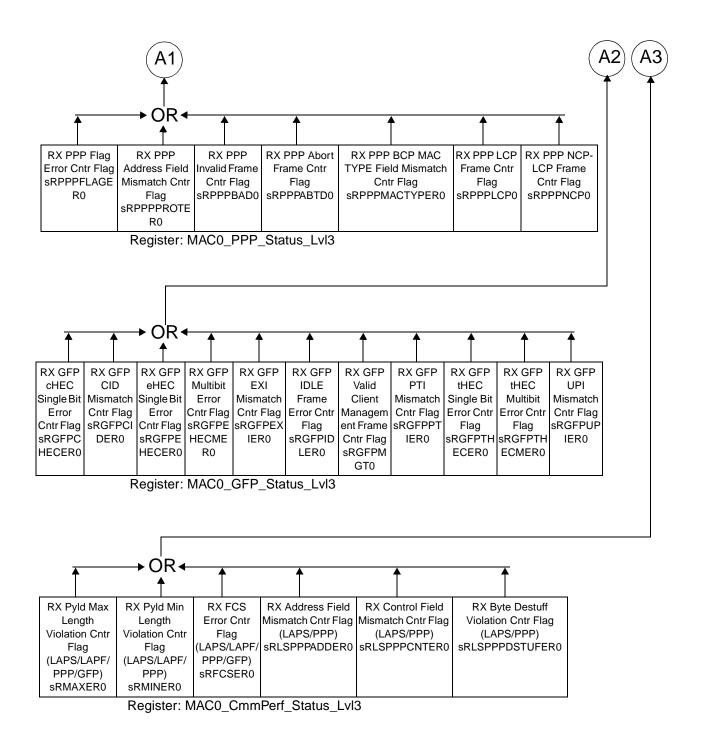

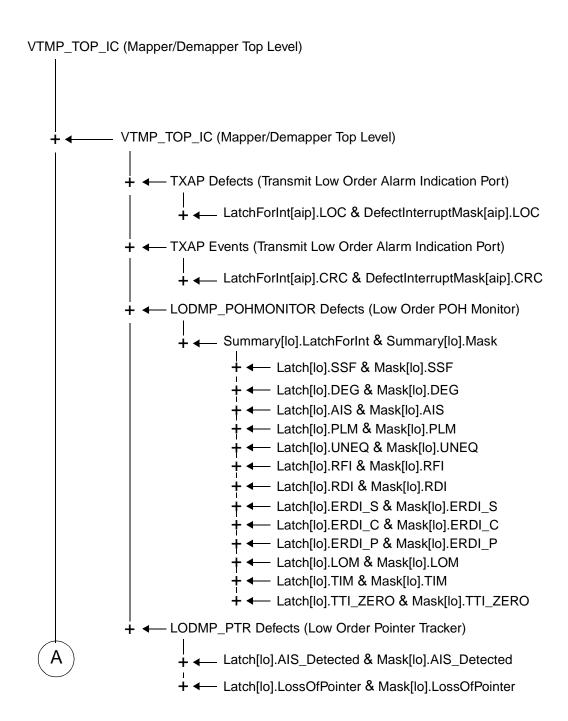

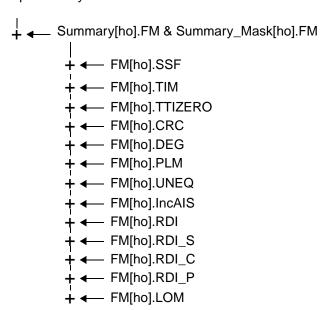

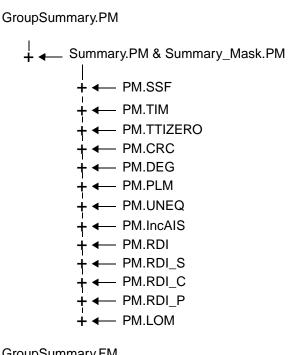

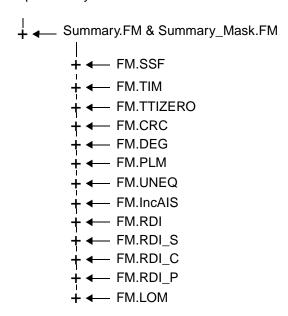

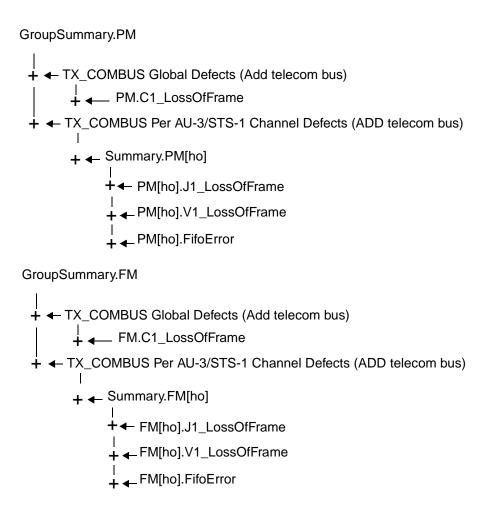

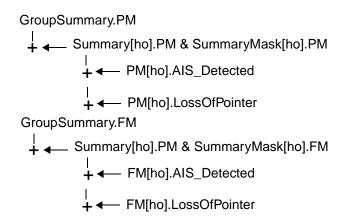

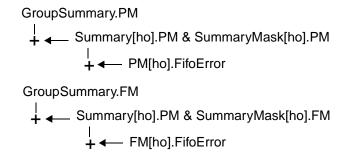

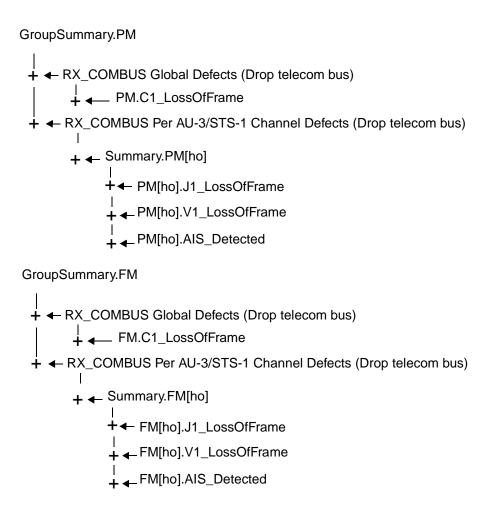

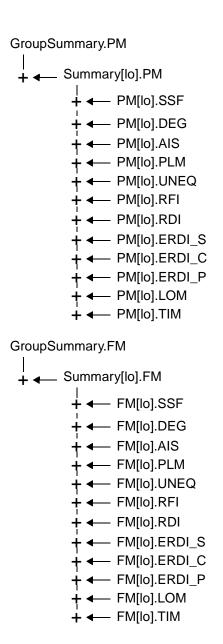

| System Alarm, Interrupt, and PM/FM Hierarchy                                                                                           | . 300        |

| Register Tree                                                                                                                          |              |

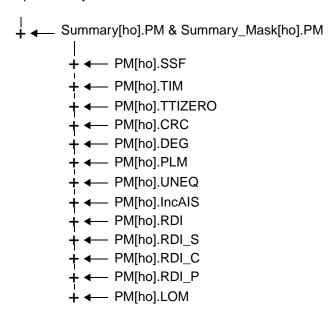

| Mapper/Demapper Performance Monitoring                                                                                                 | . 378        |

| Mapper/Demapper Interrupt Tree                                                                                                         | 379          |

| Mapper/Demapper PM/FM Tree per Block                                                                                                   | . 383        |

| Mapper/Demapper Consequent Actions per Block                                                                                           | . 390        |

| Package Information                                                                                                                    | . 394        |

| Ordering Information                                                                                                                   | . 395        |

| Related Products                                                                                                                       |              |

| Standards Documentation Sources                                                                                                        | . 396<br>จดล |

| USCOCIATA GOER CARAGORS                                                                                                                | - 14X        |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at <a href="https://www.transwitch.com">www.transwitch.com</a>. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

## **LIST OF FIGURES**

| Figure |                                                                               | age  |

|--------|-------------------------------------------------------------------------------|------|

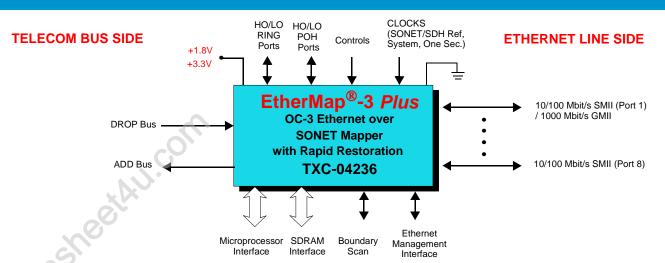

| 1      | Functional Block Diagram of the EtherMap-3 Plus                               | . 18 |

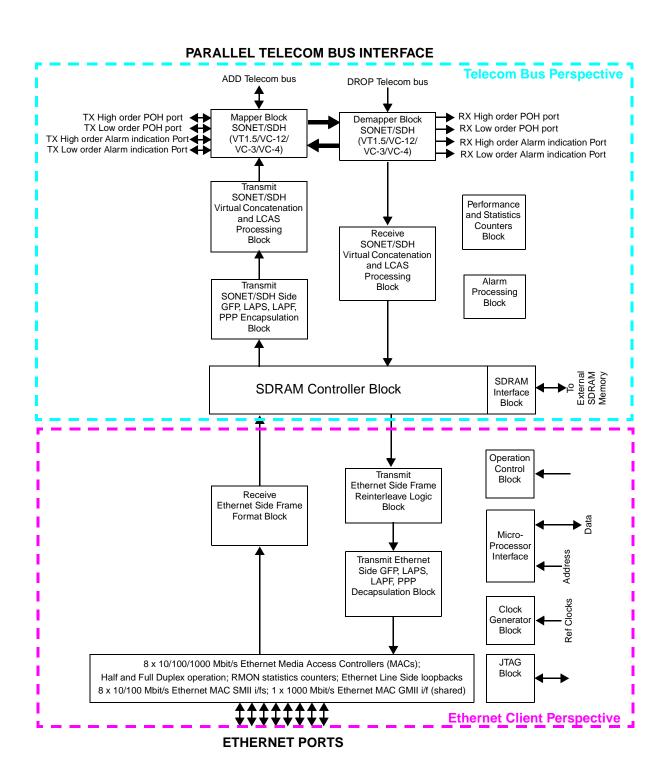

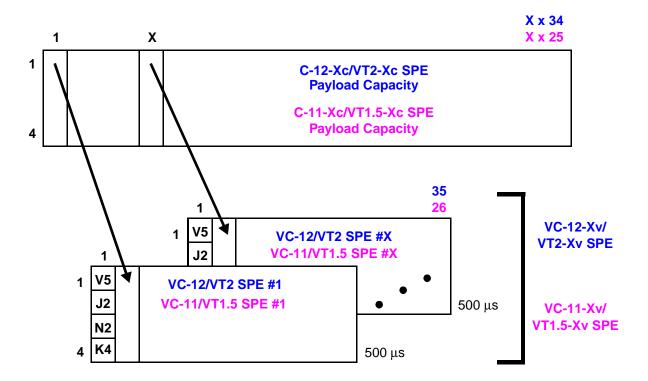

| 2      | Low Order Virtual Concatenation Structure for SONET/SDH                       |      |

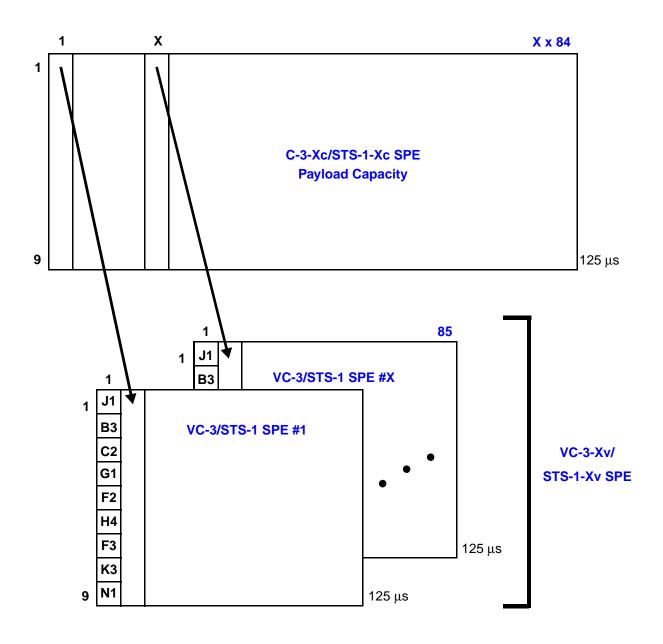

| 3      | High Order Virtual Concatenation Structure for SONET/SDH                      | . 20 |

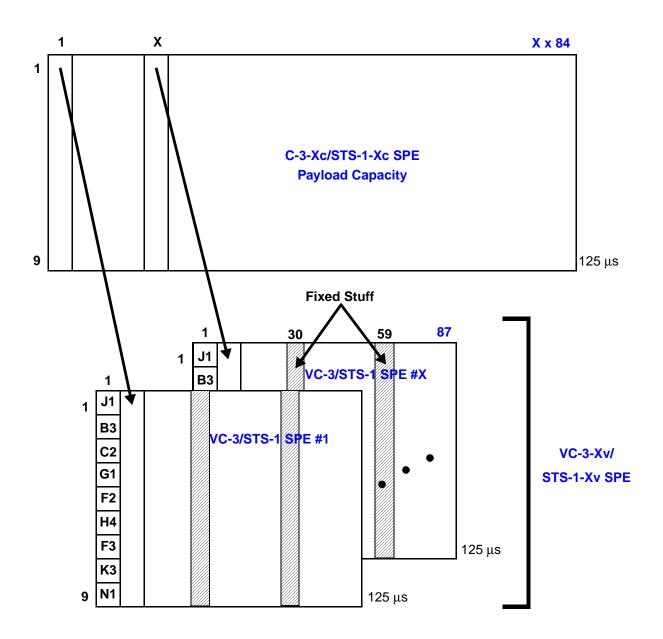

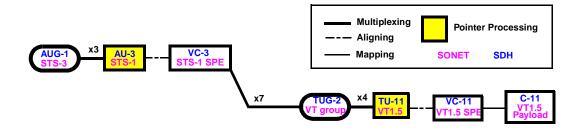

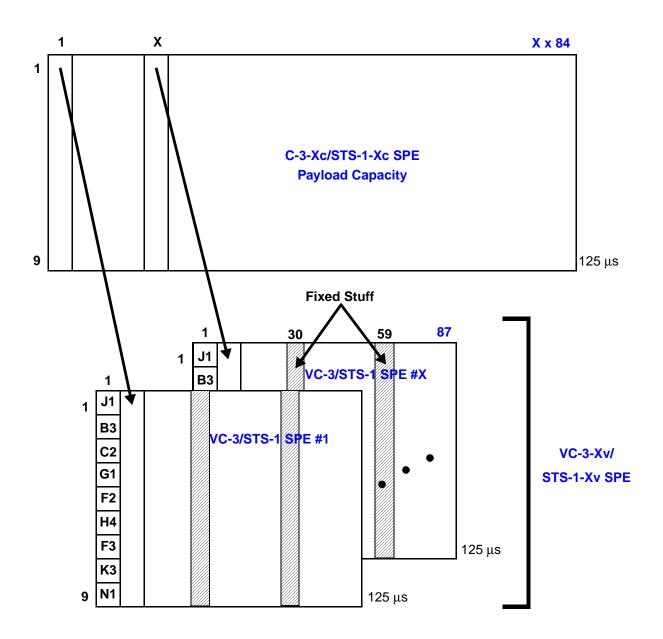

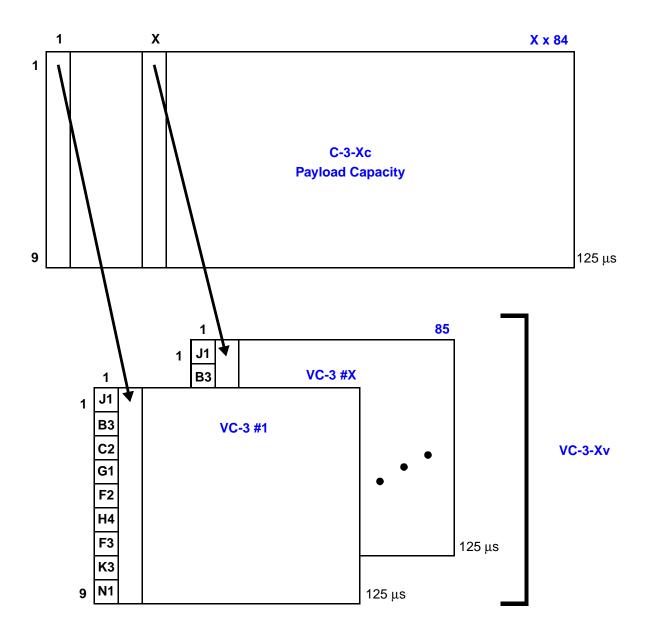

| 4      | Fixed stuff columns in High Order VC-3-Xv/STS-1-Xv SPE                        | . 21 |

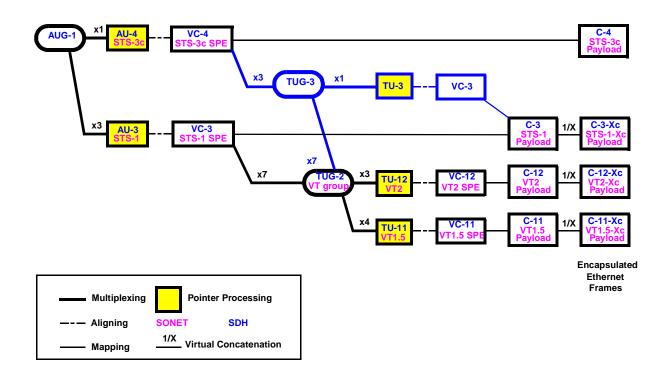

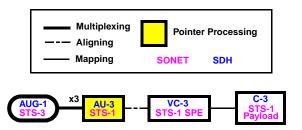

| 5      | Mapping of Ethernet Frames Over SONET/SDH                                     |      |

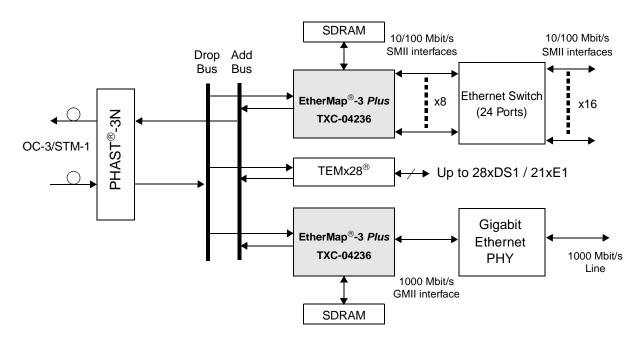

| 6      | Typical Application using the EtherMap-3 Plus and PHAST-3N Devices            |      |

| 7      | EtherMap-3 Plus TXC-04236 Lead Diagram                                        |      |

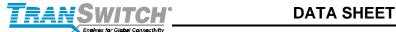

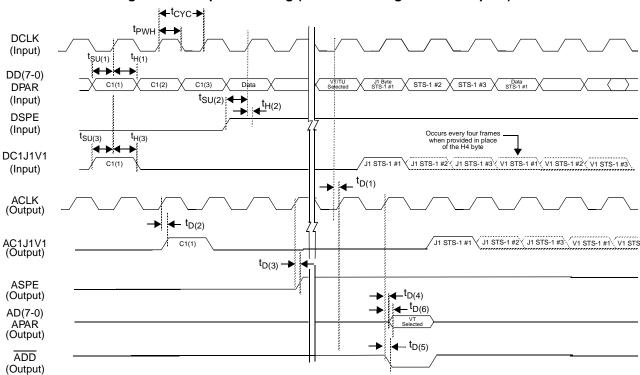

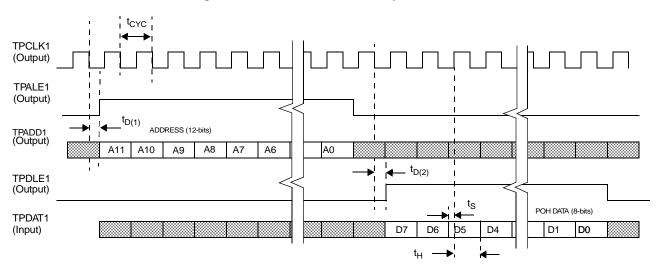

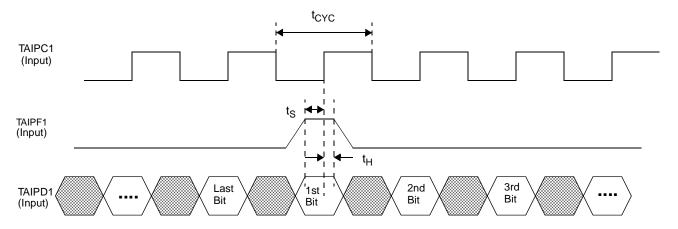

| 8      | Drop Bus Timing (Only AD, APAR, and ADD are Output)                           | . 54 |

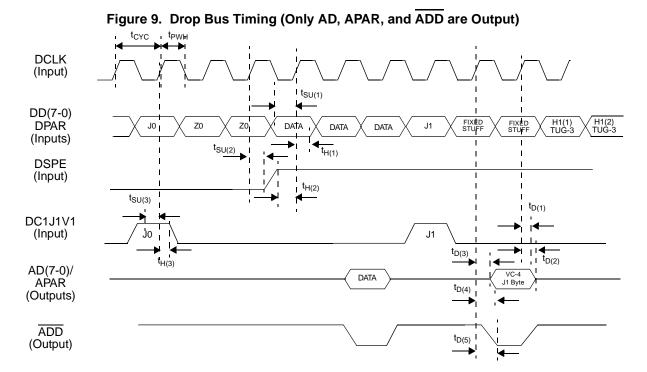

| 9      | Drop Bus Timing (Only AD, APAR, and ADD are Output)                           | . 56 |

| 10     | Drop Bus Timing (all ADD Bus Signals are Outputs)                             | . 58 |

| 11     | Drop Bus Timing (all ADD Bus Signals are Outputs)                             | . 59 |

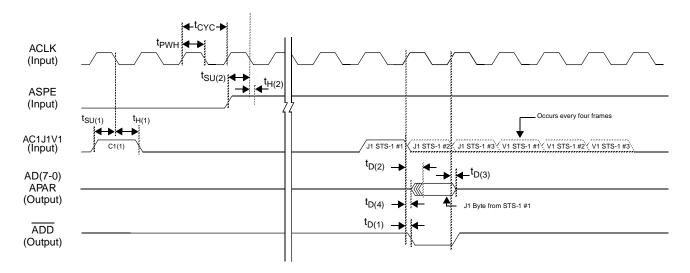

| 12     | ADD Bus Timing (Timing Signals are Inputs)                                    | . 60 |

| 13     | ADD Bus Timing (Timing Signals are Inputs)                                    | . 61 |

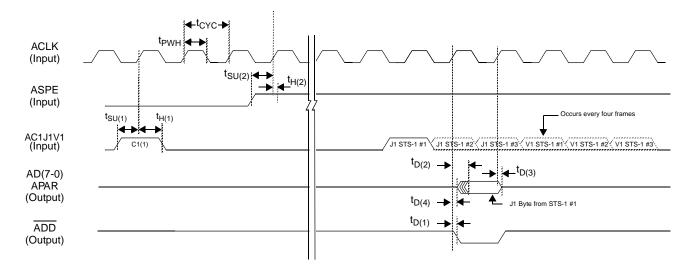

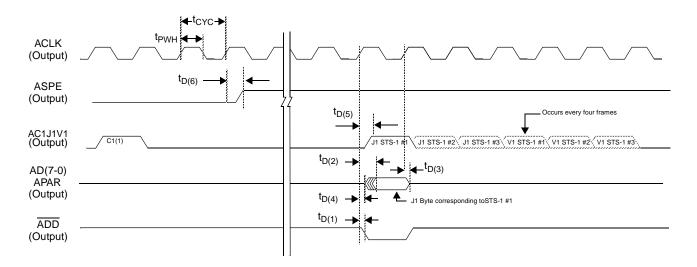

| 14     | ADD Bus Timing (Timing Signals are Outputs)                                   | . 62 |

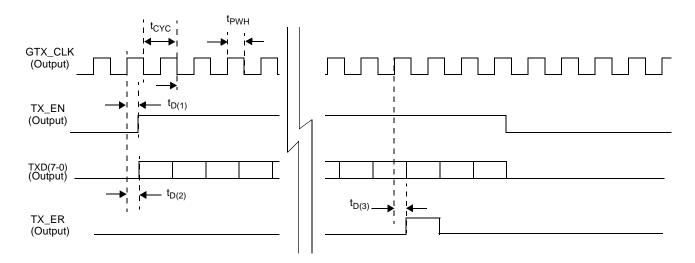

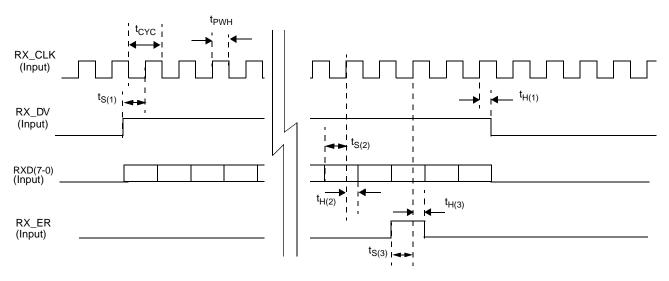

| 15     | Tx GMII Ethernet Interface                                                    | . 63 |

| 16     | Rx GMII Ethernet Interface                                                    | . 64 |

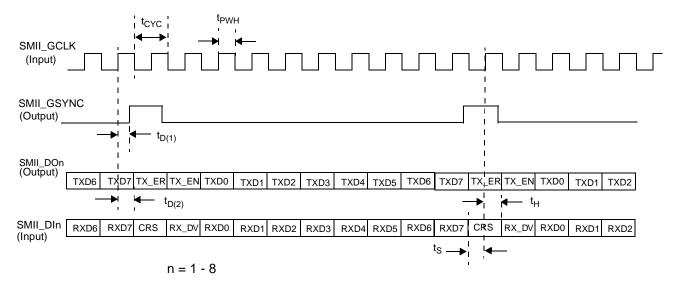

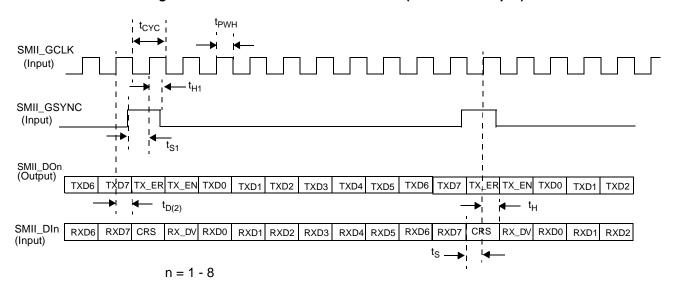

| 17     | Tx/Rx SMII Ethernet Interface (SYNC as an Output)                             | . 65 |

| 18     | Tx/Rx SMII Ethernet Interface (SYNC as an Input)                              | . 66 |

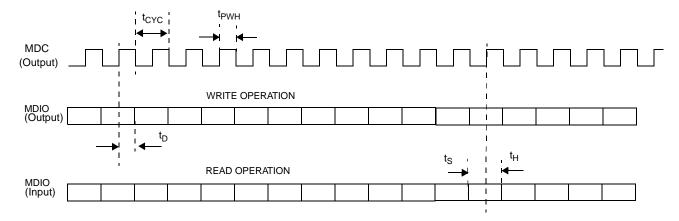

| 19     | Ethernet Management Interface                                                 | . 67 |

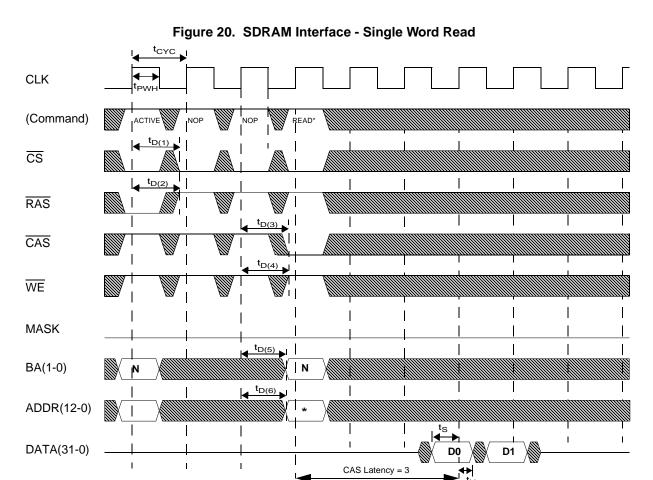

| 20     | SDRAM Interface - Single Word Read                                            | . 68 |

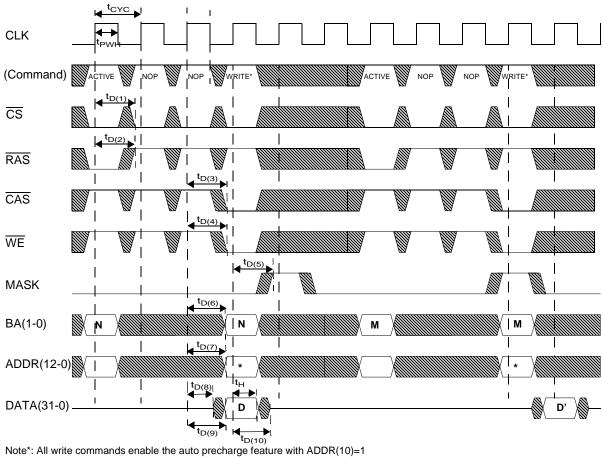

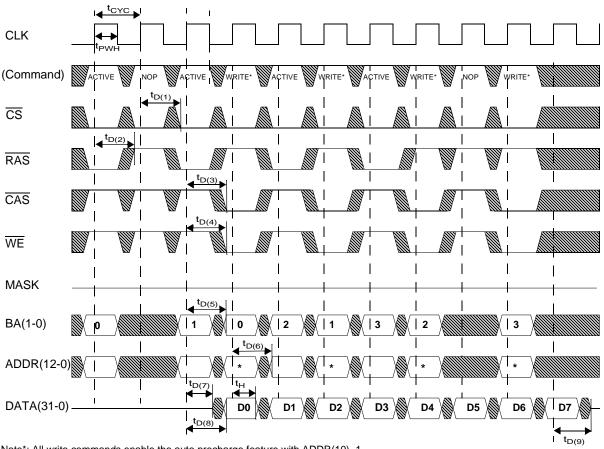

| 21     | SDRAM Interface - Single Word Write                                           | . 69 |

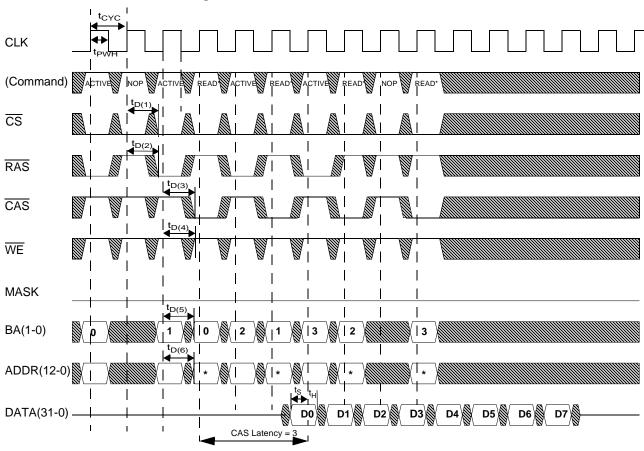

| 22     | SDRAM Interface - Burst Read                                                  | . 70 |

| 23     | SDRAM Interface - Burst Write                                                 | . 71 |

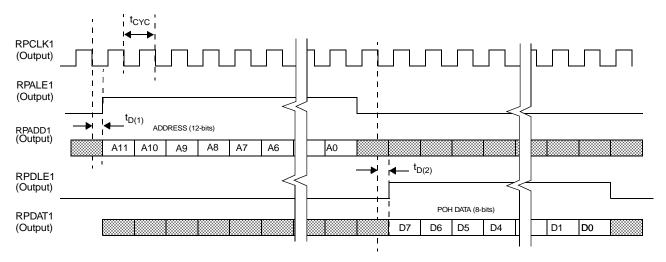

| 24     | Rx VC-3 POH Byte Interface                                                    | . 72 |

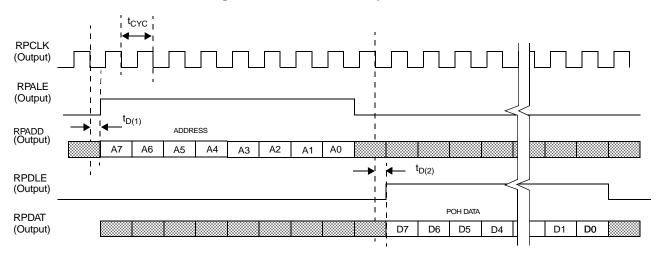

| 25     | Tx VC-3 POH Byte Interface                                                    | . 73 |

| 26     | Rx Low Order POH Byte Interface                                               | . 74 |

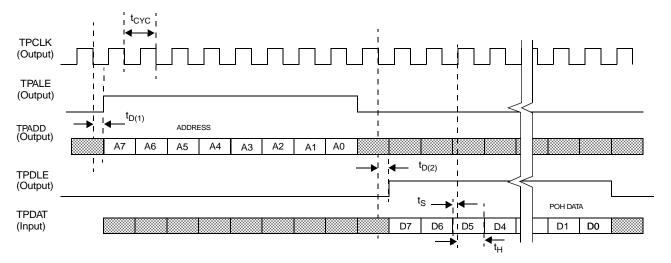

| 27     | Tx Low Order POH Byte Interface                                               | . 75 |

| 28     | Rx VC-3 Alarm Indication Port Interface                                       | . 76 |

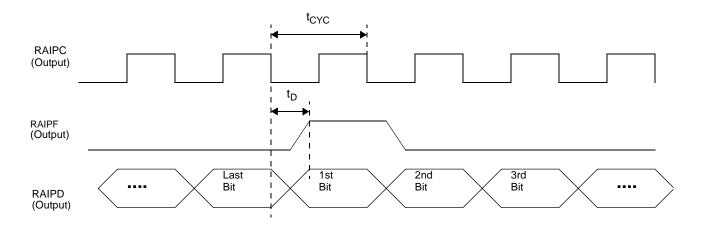

| 29     | Tx VC-3 Alarm Indication Port Interface                                       |      |

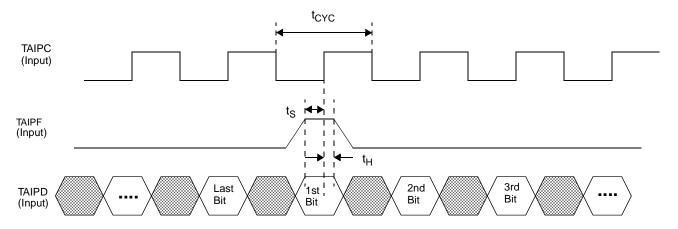

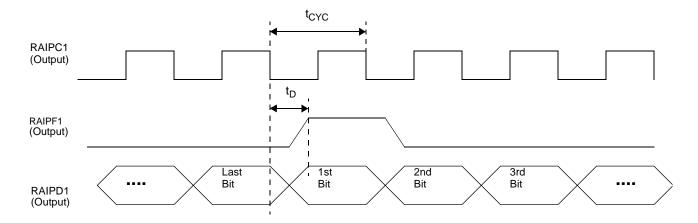

| 30     | Rx Low Order Alarm Indication Port Interface                                  |      |

| 31     | Tx Low Order Alarm Indication Port Interface                                  |      |

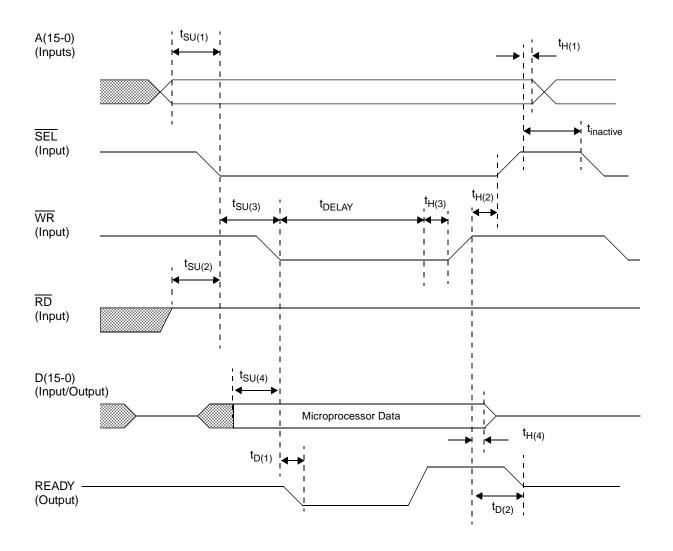

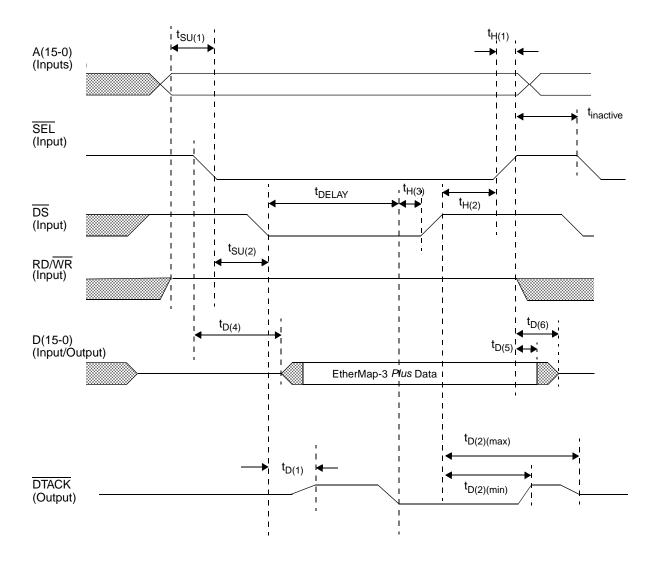

| 32     | Asynchronous Microprocessor Interface: Intel-type Write Cycle Timing          |      |

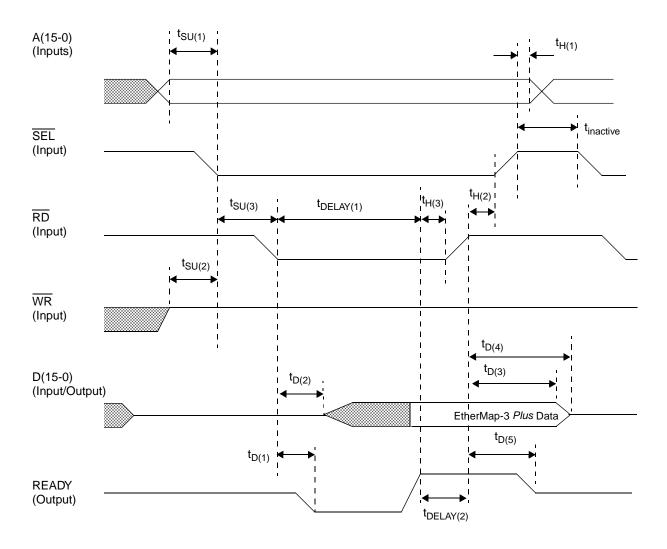

| 33     | Asynchronous Microprocessor Interface: Intel-type Read Cycle Timing           |      |

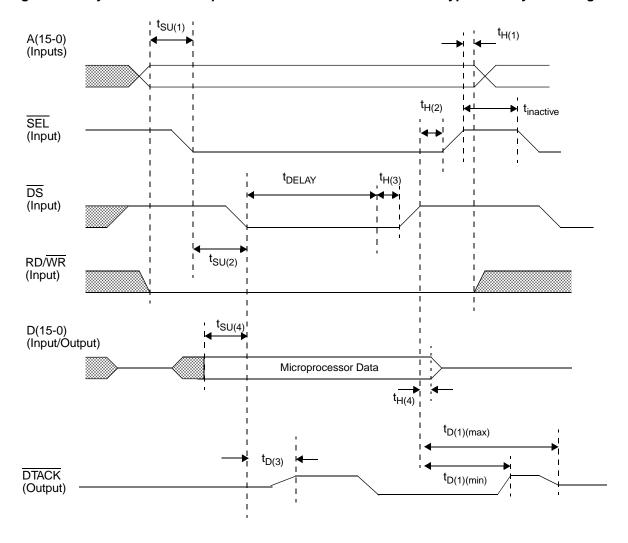

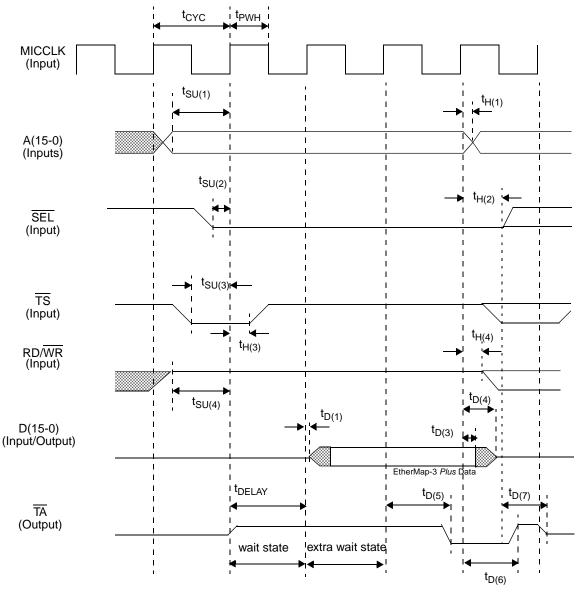

| 34     | Asynchronous Microprocessor Interface: Motorola 68360-type Write Cycle Timing |      |

| 35     | Asynchronous Microprocessor Interface: Motorola 68360-type Read Cycle Timing  |      |

| 36     | Synchronous Microprocessor Interface: Motorola MPC860-type Read Cycle Timing  |      |

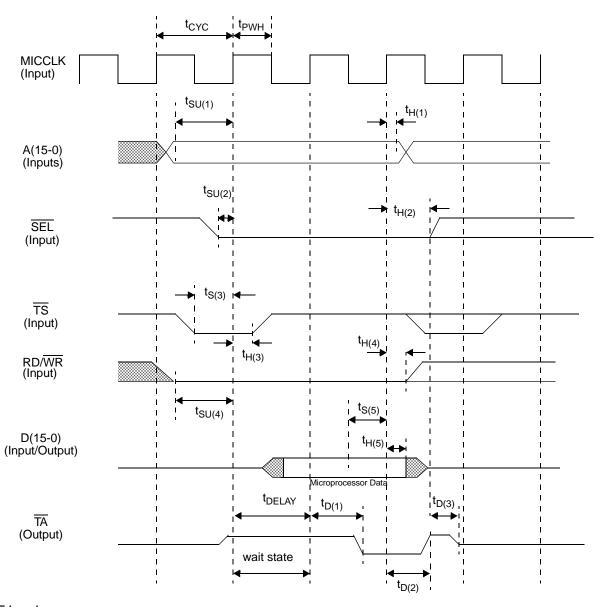

| 37     | Synchronous Microprocessor Interface: Motorola MPC860-type Write Cycle Timing |      |

| 38     | Boundary Scan Timing                                                          |      |

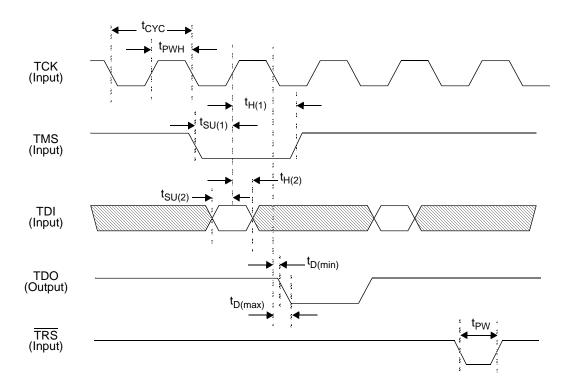

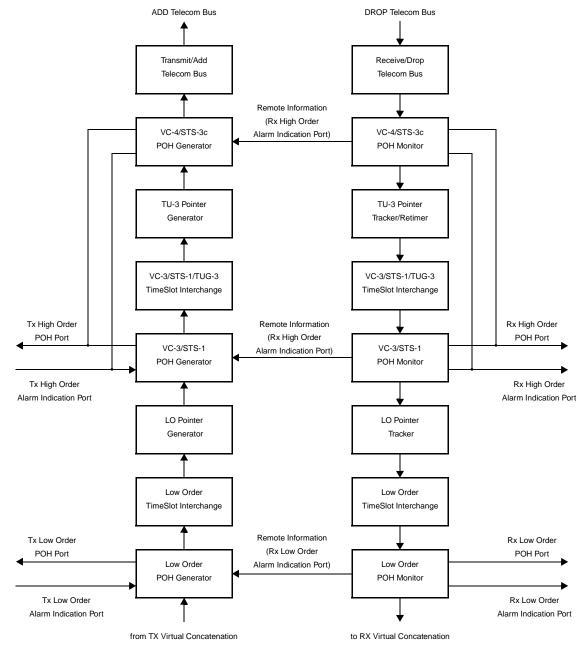

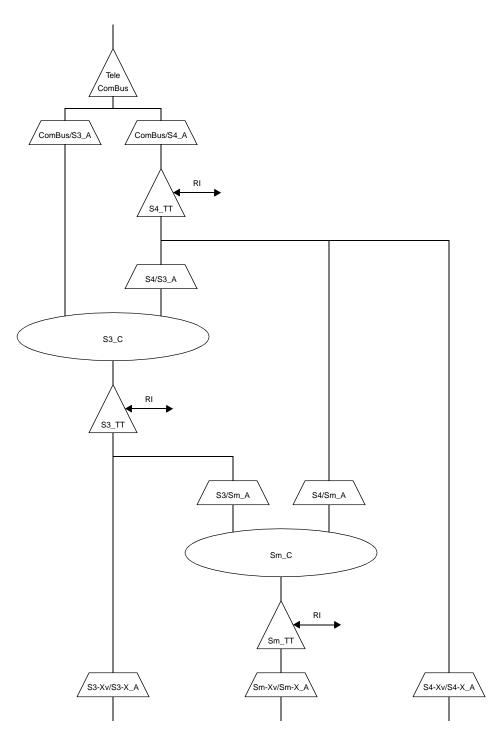

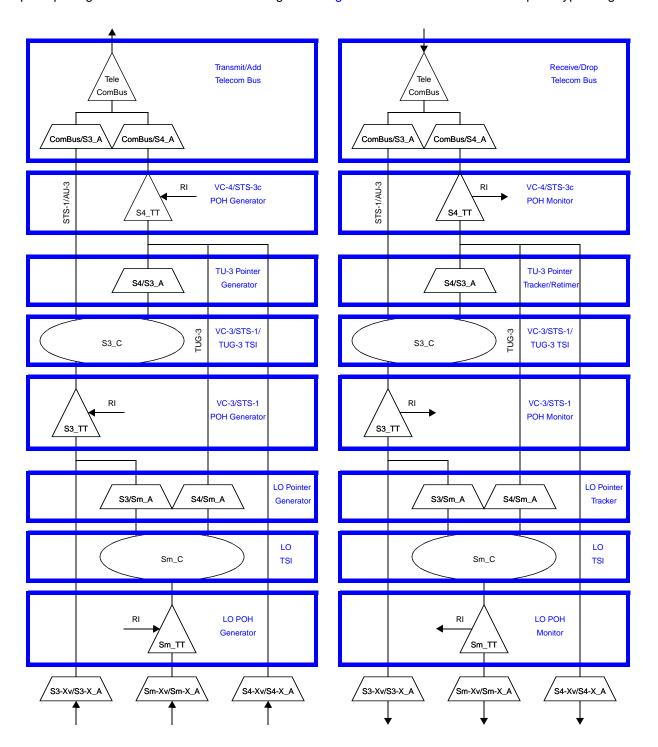

| 39     | Functional Block Diagram of the Mapper/Demapper                               |      |

| 40     | Functional Model of the Mapper/Demapper                                       |      |

| 41     | Mapper/Demapper Bypass Modes                                                  |      |

| 42     | VT1.5-Xv-SPE Structure                                                        |      |

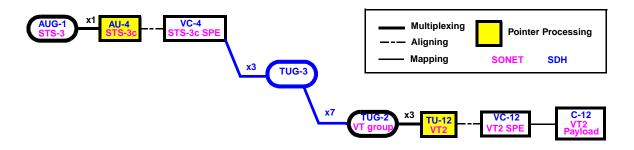

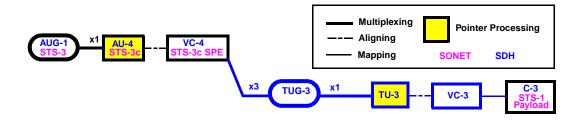

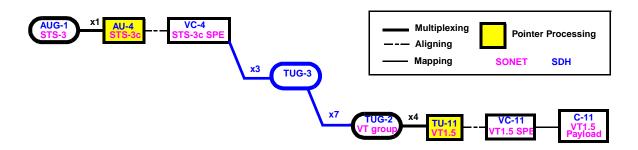

| 43     | LO SDH Multiplexing Structure 1 Supported by the EtherMap-3 Plus              |      |

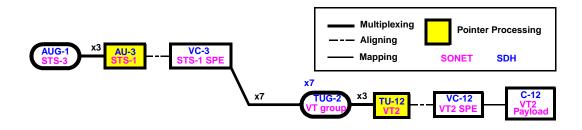

| 44     | LO SDH Multiplexing Structure 3 Supported by the EtherMap-3 Plus              |      |

| 45     | LO SDH Multiplexing Structure 2 Supported by the EtherMap-3 Plus              |      |

| 46     | LO SDH Multiplexing Structure 4 Supported by the EtherMap-3 Plus              |      |

| 47     | LO SONET Multiplexing Structure Supported by the EtherMap-3 Plus              |      |

| 48     | High Order STS-1-Xv-SPE/VC-3-Xv Structure                                     |      |

| 49     | Low Order VC-3-Xv Structure                                                   |      |

| 50     | HO SONET/SDH Multiplexing Structure Supported by the EtherMap-3 Plus          |      |

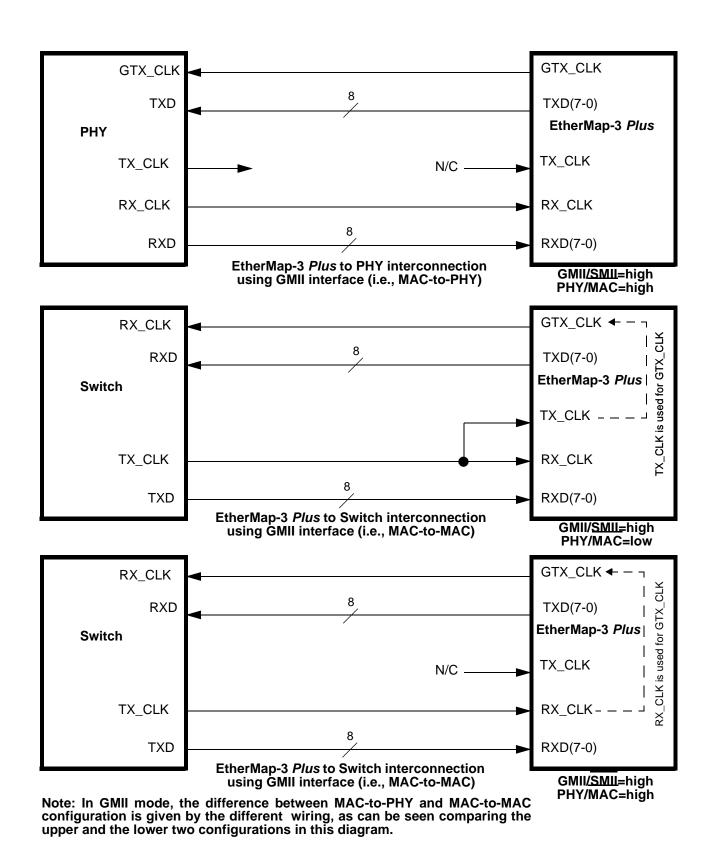

| 51     | EtherMap-3 Plus to PHY or Switch Interconnection Using GMII Interface         |      |

| 52     | Format of GFP Frame with an Ethernet MAC Frame Payload                        | 141  |

# LIST OF FIGURES (cont.)

| Fig | ure                                                                 | Page |

|-----|---------------------------------------------------------------------|------|

| 53  | Format of LAPS Frame with an Ethernet MAC Frame Payload             | 153  |

| 54  | Format of LAPF Bridged Frame with an Ethernet MAC Frame Payload     | 162  |

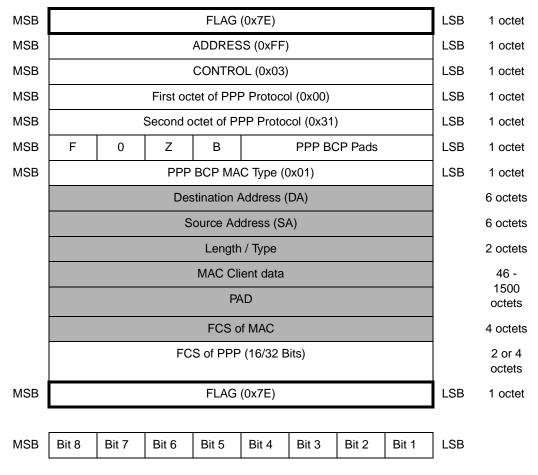

| 55  | Format of PPP Frame with an Ethernet MAC Frame Payload              | 170  |

| 56  | MAC Loopback                                                        | 193  |

| 57  | Telecom Bus Loopbacks                                               | 194  |

| 58  | Boundary Scan Schematic                                             | 196  |

| 59  | Latched Alarm Bit (L1Alarm_name) Transitions                        | 357  |

| 60  | Positive Edge Event - PM/FM Signal Generation                       | 360  |

| 61  | Negative Edge Event - PM/FM Signal Generation                       | 361  |

| 62  | Positive/Negative Edge Event - PM/FM Signal Generation              | 362  |

| 63  | Alarm, Interrupt and PM/FM Generation Process                       | 363  |

| 64  | Alarm, Interrupt and PM/FM Generation Process (Inhibition Function) | 363  |

| 65  | Alarm Interrupt Hierarchy                                           | 367  |

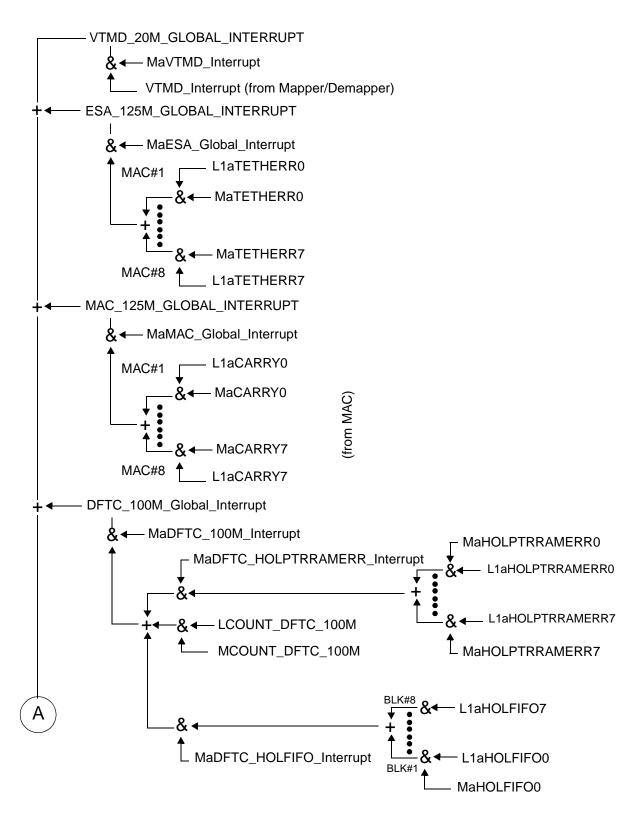

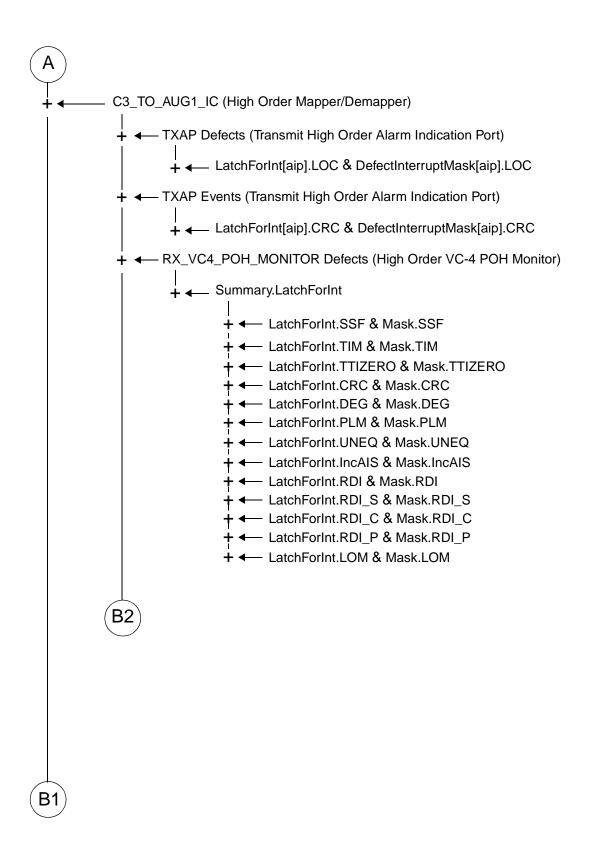

| 66  | Alarm Interrupt Tree Part A                                         | 368  |

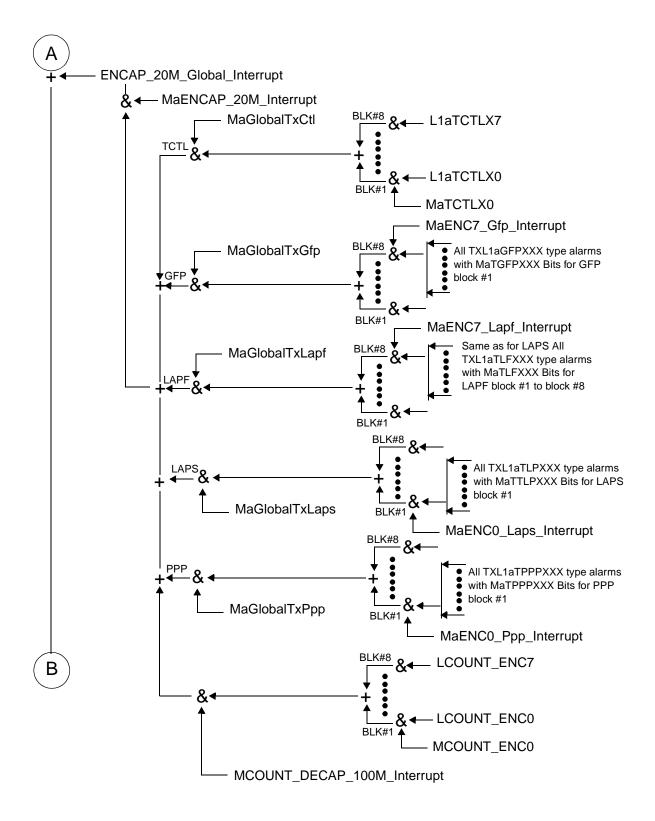

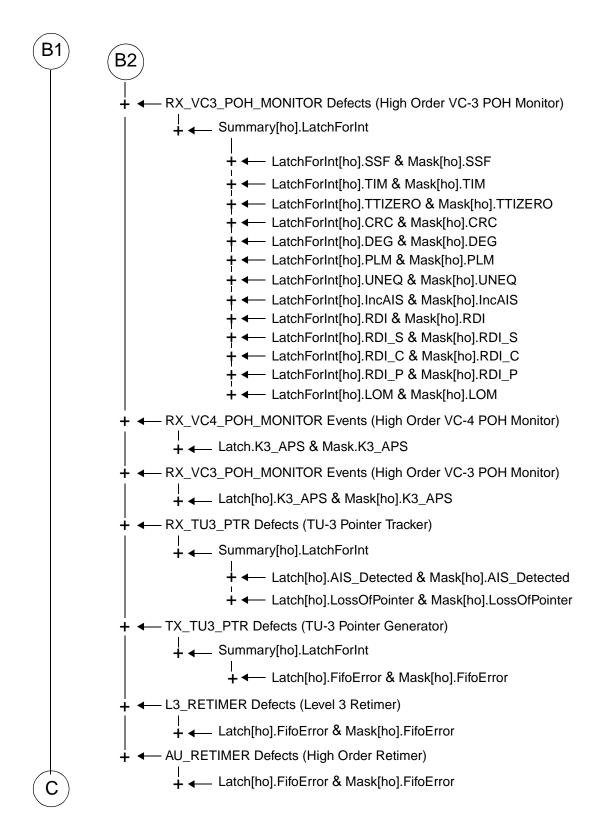

| 67  | Alarm Interrupt Tree Part A to Part B                               | 369  |

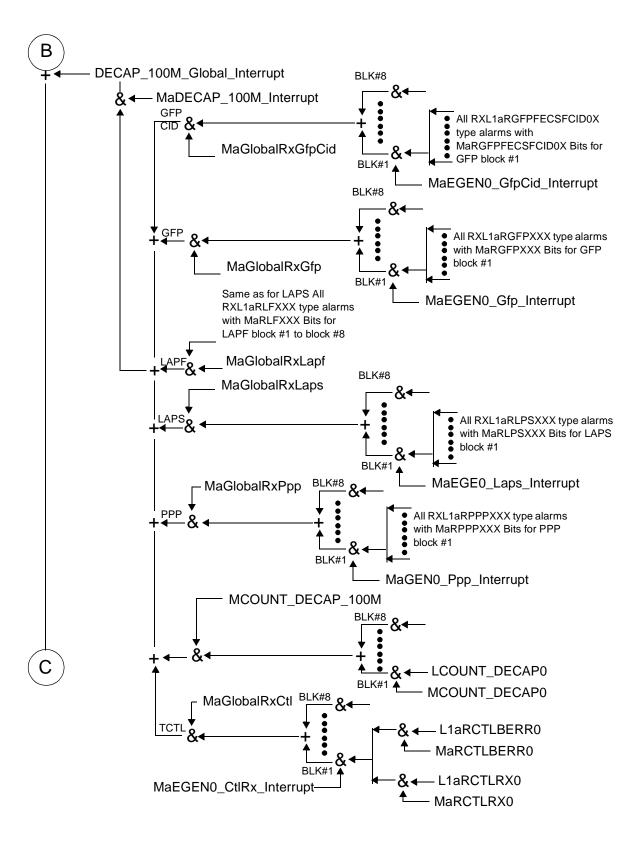

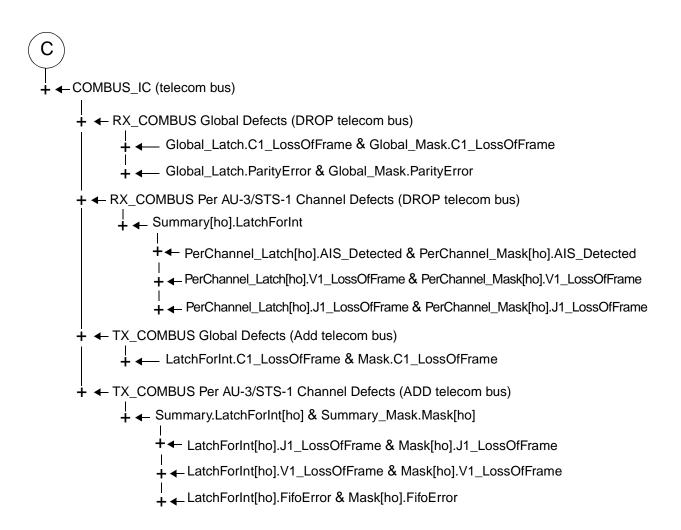

| 68  | Alarm Interrupt Tree Part B to Part C                               | 370  |

| 69  | Alarm Interrupt Tree Part C to Parts D1, D2 and D3                  | 371  |

| 70  | Alarm Interrupt Tree Parts D1, D2 and D3 to Parts E1 and E2         | 372  |

| 71  | Alarm Interrupt Tree Parts E1 and E2 to Parts F1 and F2             | 373  |

| 72  | Alarm Interrupt Tree Parts F1 and F2 to Part G                      | 374  |

| 73  | Alarm Interrupt Tree Part G                                         | 375  |

| 74  | Register Tree Parts A1, A2 and A3                                   | 376  |

| 75  | Register Tree Parts A1, A2 and A3 (continued)                       | 377  |

| 76  | Mapper/Demapper Interrupt Tree Part A                               | 379  |

| 77  | Mapper/Demapper Interrupt Tree Part A to Parts B1 and B2            | 380  |

| 78  | Mapper/Demapper Interrupt Tree Parts B1 and B2 to Part C            | 381  |

| 79  | Mapper/Demapper Interrupt Tree Part C                               | 382  |

| 80  | Mapper/Demapper RX_VC3_POH_MONITOR PM/FM Trees                      | 383  |

| 81  | Mapper/Demapper RX VC-4 POH MONITOR PM/FM Trees                     | 384  |

| 82  | Mapper/Demapper TX COMBUS PM/FM Trees                               | 385  |

| 83  | Mapper/Demapper RX_TU3_PTR PM/FM Trees                              | 386  |

| 84  | Mapper/Demapper TX_TU3_PTR PM/FM Trees                              |      |

| 85  | Mapper/Demapper RX COMBUS PM/FM Trees                               |      |

| 86  | Mapper/Demapper LODMP_POHMONITOR PM/FM Trees                        | 388  |

| 87  | Mapper/Demapper LODMP_Ptr PM/FM Trees                               | 389  |

| 88  | EtherMap-3 Plus TXC-04236 Package Diagram                           | 394  |

## **LIST OF TABLES**

| Table    |                                                                                                | age  |

|----------|------------------------------------------------------------------------------------------------|------|

| 1        | TU-3 Pointer Tracker/Retimer Modes                                                             | . 96 |

| 2        | TU-3 Pointer Generator Modes                                                                   |      |

| 3        | SONET/SDH Protection Switching Recovery Time                                                   | 112  |

| 4        | Configuration of rMAXDELVCG_x in Low Order VC                                                  |      |

| 5        | Configuration of rMAXDELVCG_x in High Order VC                                                 |      |

| 6        | Allowed Range for High/Low Watermark Registers                                                 |      |

| 7        | Scheduling Matrix                                                                              |      |

| 8        | Scheduling Matrix Mapped in the EtherMap-3 Plus Register Map                                   |      |

| 9        | Memory Map Overview                                                                            |      |

| 10       | General Device Configuration (RW)                                                              |      |

| 11       | General Device Status (RO)                                                                     | 200  |

| 12       | ID Registers (RO)                                                                              | 200  |

| 13       | MAC Combined Receive and Transmit Counters                                                     | 201  |

| 14       | MAC Receive Counters                                                                           | 202  |

| 15       | MAC Transmit Counters                                                                          | 204  |

| 16       | MAC Interface Status Registers                                                                 | 206  |

| 17       | MAC Carry and Carry Mask Registers                                                             | 207  |

| 18       | MAC Configuration Registers                                                                    | 210  |

| 19       | MAC Station Address Registers                                                                  | 211  |

| 20       | MAC IPG / IFG Registers                                                                        | 212  |

| 21       | MAC Half Duplex Registers                                                                      | 213  |

| 22       | MAC Maximum Frame Registers                                                                    | 213  |

| 23       | MAC Test Registers                                                                             |      |

| 24       | MAC MII Mgmt Configuration Registers                                                           | 215  |

| 25       | MAC MII Mgmt Command Registers                                                                 | 215  |

| 26       | MAC MII Mgmt Address Registers                                                                 |      |

| 27       | MAC MII Mgmt Control Registers                                                                 |      |

| 28       | MAC MII Mgmt Status Registers                                                                  |      |

| 29       | MAC MII Mgmt Indicators Registers                                                              |      |

| 30       | MAC Block - General Configuration (RW)                                                         |      |

| 31       | MAC Block - Alarms (RO)                                                                        |      |

| 32       | MAC Block - Alarm and Interrupt Masks (RW)                                                     |      |

| 33       | MAC Block - Latched Alarms (RR)                                                                |      |

| 34       | MAC Block - Interrupts (RO)                                                                    |      |

| 35       | Encapsulation Block - General Configuration (RW)                                               |      |

| 36       | Encapsulation Block - LAPS Configuration (RW)                                                  |      |

| 37       | Encapsulation Block - LAPF Configuration (RW)                                                  |      |

| 38       | Encapsulation Block - GFP Configuration (RW)                                                   |      |

| 39<br>40 | Encapsulation Block - PPP Configuration (RW)  Encapsulation Block - Control Frame Buffers (RW) |      |

| 41       | Encapsulation Block - Control Frame Buriers (RW)                                               |      |

| 42       | Encapsulation Block - Status (RW)                                                              |      |

| 43       | Encapsulation Block - Status Registers (RO)                                                    |      |

| 44       | Encapsulation Block - Performance Counters  Encapsulation Block - Alarms (RO)                  |      |

| 45       | Encapsulation Block - Alarms (NO)  Encapsulation Block - Alarms and Interrupt Masks (RW)       |      |

| 46       | Encapsulation Block - Alarm and Interrupt Wasks (KW)                                           |      |

| 47       | Encapsulation Block - Interrupts (RO)  Encapsulation Block - Latched Alarms (RR)               |      |

| 48       | Decapsulation Block - General Configuration (RW)                                               |      |

| 49       | Decapsulation Block - LAPS Configuration (RW)                                                  |      |

| 50       | Decapsulation Block - LAPF Configuration (RW)                                                  |      |

| Table | e                                                                        | Page |

|-------|--------------------------------------------------------------------------|------|

| 51    | Decapsulation Block - Control Buffer Status (RW)                         | 242  |

| 52    | Decapsulation Block - Link Status (RO)                                   | 242  |

| 53    | Decapsulation Block - GFP Configuration (RW)                             | 243  |

| 54    | Decapsulation Block - PPP Configuration (RW)                             | 245  |

| 55    | Decapsulation Block - LMI Buffers (RO)                                   | 247  |

| 56    | Decapsulation Block - Alarms (RO)                                        | 247  |

| 57    | Decapsulation Block - Alarm and Interrupt Masks (RW)                     | 251  |

| 58    | Decapsulation Block - Latched Alarms (RR)                                | 255  |

| 59    | Decapsulation Block - Interrupts (RO)                                    | 258  |

| 60    | Decapsulation Block - Performance Counters                               | 259  |

| 61    | Decapsulation Block - Status (RR)                                        | 266  |

| 62    | SDRAM Control - General Configuration (RW)                               | 268  |

| 63    | SDRAM - Access Control Registers (RW)                                    | 269  |

| 64    | SDRAM - Access Results Registers (RO)                                    | 269  |

| 65    | Tx Virtual Concatenation Block - General Configuration (RW)              |      |

| 66    | Tx Virtual Concatenation Block - LCAS Alarms (RO)                        | 272  |

| 67    | VT/VC Address Offsets                                                    |      |

| 68    | Tx Virtual Concatenation Block - LCAS Alarm and Interrupt Masks (RW)     | 275  |

| 69    | Tx Virtual Concatenation Block - LCAS Latched Alarms (RR)                | 277  |

| 70    | Tx Virtual Concatenation Block - LCAS Interrupts (RO)                    | 278  |

| 71    | Tx Virtual Concatenation Block - Low Order Tributary Configuration (RW)  | 279  |

| 72    | Tx Virtual Concatenation Block - High Order Tributary Configuration (RW) | 279  |

| 73    | Tx Virtual Concatenation Block - LCAS Configuration (RW)                 | 279  |

| 74    | VT/VC Address Offsets (cTLOK4VCEN_x and cTLOCRCERR_x Only)               |      |

| 75    | Tx Virtual Concatenation Block - Status (RO)                             | 282  |

| 76    | Rx Virtual Concatenation Block - General Configuration Registers (RW)    | 283  |

| 77    | Rx Virtual Concatenation Block - Alarms (RO)                             | 285  |

| 78    | Rx Virtual Concatenation Block - Alarm and Interrupt Masks (RW)          | 286  |

| 79    | Rx Virtual Concatenation Block - Latched Alarms (RR)                     | 290  |

| 80    | Rx Virtual Concatenation Block - Interrupts (RO)                         | 291  |

| 81    | Rx Virtual Concatenation Block - Low Order Tributary Configuration (RW)  | 292  |

| 82    | Rx Virtual Concatenation Block - High Order Tributary Configuration (RW) | 293  |

| 83    | Rx Virtual Concatenation Block - Status (RO)                             | 293  |

| 84    | Rx Virtual Concatenation Block - Frame Counter Status (RO)               | 294  |

| 85    | Rx Virtual Concatenation Block - Differential Delay Status (RO)          | 294  |

| 86    | Ethernet Frame Format Block - General Configuration (RW)                 | 295  |

| 87    | Ethernet Frame Format Block - Alarms (RO)                                | 295  |

| 88    | Ethernet Frame Format Block - Alarm and Interrupt Masks (RW)             | 295  |

| 89    | Ethernet Frame Format Block - Latched Alarms (RR)                        | 295  |

| 90    | Ethernet Frame Format Block - Interrupts (RO)                            | 295  |

| 91    | SONET to Ethernet - General Configuration and Watermarks (RW)            | 296  |

| 92    | SONET to Ethernet - SDRAM Alarms (RO)                                    | 297  |

| 93    | SONET to Ethernet - SDRAM Alarm and Interrupt Masks (RW)                 | 297  |

| 94    | SONET to Ethernet - SDRAM Latched Alarms RR)                             | 297  |

| 95    | SONET to Ethernet - SDRAM Interrupts (RO)                                | 298  |

| 96    | SONET to Ethernet - SDRAM Performance Counters (RR)                      | 298  |

| 97    | SONET to Ethernet - SDRAM FIFO Status (RO)                               | 298  |

| 98    | Ethernet to SONET - Flow Control Configuration (RW)                      | 298  |

| 99    | SDRAM Controller Alarm (Tx and Rx) (RO)                                  | 299  |

| 100   | SDRAM Controller (Tx and Rx Direction) (RW)                              | 300  |

| 101   | SDRAM Controller (Tx and Rx Directions) (RR)                             | 300  |

| Table | e P                                                             | age |

|-------|-----------------------------------------------------------------|-----|

| 102   | Ethernet to SONET, SDRAM Output - Interrupts (RO)               | 301 |

| 103   | Ethernet to SONET, SDRAM Output - Performance Counters          | 301 |

| 104   | Mapper Block - Reset (RW)                                       | 302 |

| 105   | Mapper Block - Interrupt Configuration (RO)                     |     |

| 106   | Mapper Block - Interrupt Mask (RW)                              |     |

| 107   | Mapper and Demapper Block - Status (RO)                         |     |

| 108   | Mapper Block - Timing Configuration (RW)                        |     |

| 109   | Mapper Block - TUG-3/VC-3 Configuration (RW)                    |     |

| 110   | Mapper Block - TUG-2 Configuration (RW)                         |     |

| 111   | Mapper Block - Pointer Configuration (RW)                       |     |

| 112   | Mapper Block - General Configuration, Low Order (RW)            | 303 |

| 113   | Mapper Block - TUG-2 Configuration (RW)                         |     |

| 114   | Mapper Block - POH Configuration (RW)                           |     |

| 115   | Mapper Block - Cross Connect Configuration (RW)                 |     |

| 116   | Mapper Block - V4 Configuration (RW)                            |     |

| 117   | Mapper Block - POH Byte Values (RW)                             |     |

| 118   | Mapper Block - Bypass Control (RW)                              |     |

| 119   | Demapper Block - General Configuration (RW)                     |     |

| 120   | Demapper Block - Bypass Control (RW)                            |     |

| 121   | Demapper Block - TUG-2 Configuration (RW)                       |     |

| 122   | Demapper Block - Performance Counters Shadow Registers (RO)     |     |

| 123   | Demapper Block - Alarm Control (RW)                             |     |

| 124   | Demapper Block - Interrupts (RO)                                |     |

| 125   | Demapper Block - Alarms (RO)                                    |     |

| 126   | Demapper Block - Latched Alarms (R/COW-1)                       |     |

| 127   | Demapper Block - Alarm Masks (RW)                               |     |

| 128   | LODMP_Ptr_DefectCorrelations_LP (R/COW-0)                       |     |

| 129   | LODMP_Ptr_DefectCorrelations_PM (RO)                            |     |

| 130   | LODMP_Ptr_DefectCorrelations_FM (RO)                            |     |

| 131   | Demapper Block - POH Byte Monitors (RO)                         |     |

| 132   | LO POH Monitor - Bypass Control (RW)                            |     |

| 133   | LO POH Monitor - J2 Trace Message Handling                      | 309 |

| 134   | LO POH Monitor - POH Byte Monitors (RO)                         | 309 |

| 135   | LO POH Monitor - Accepted Values (RO)                           | 309 |

| 136   | LO POH Monitor - Expected Values (RW)                           | 309 |

| 137   | LO POH Monitor - General Configuration (RW)                     | 310 |

| 138   | LO POH Monitor - Channel Configuration (RW)                     | 311 |

| 139   | LO POH Monitor - Channel Status (RO)                            | 311 |

| 140   | LO POH Monitor - Channel Report (RO)                            | 311 |

| 141   | LO POH Monitor - Channel Defects (RO)                           | 311 |

| 142   | LO POH Monitor - Defect Correlations (RO)                       | 312 |

| 143   | LO POH Monitor - Latched Defects (R/COW-1)                      | 312 |

| 144   | LO POH Monitor - Defect Correlations Latched For PMFM (R/COW-0) | 313 |

| 145   | LO POH Monitor - PM Defect Correlations Monitor (RO)            | 313 |

| 146   | LO POH Monitor - FM Defect Correlations Monitor (RO)            | 313 |

| 147   | LO POH Monitor - Defect Correlations Mask (R/W)                 | 314 |

| 148   | LO POH Monitor - Defect Correlations Configuration (RW)         |     |

| 149   | LO POH Monitor - Defect Correlations Summary (RO)               |     |

| 150   | LO POH Monitor - Defect Correlations Summary Mask (RW)          |     |

| 151   | LO POH Monitor - Defect Correlations Group Summary (RO)         |     |

| 152   | LO POH Monitor - Performance Monitor One Second Latch (RO)      | 315 |

| Tabl | e                                                           | Page |

|------|-------------------------------------------------------------|------|

| 153  | LO POH Monitor - Performance Counters (RW)                  | 315  |

| 154  | LO POH Monitor - Performance Counter Shadow Registers (RO)  | 315  |

| 155  | Tx LO Ring Port - General Configuration (RW)                | 316  |

| 156  | Tx LO Ring Port - Event Latch (COW-1)                       | 316  |

| 157  | Tx LO Ring Port - Performance Counters (RW)                 | 316  |

| 158  | Tx LO Ring Port - Performance Counter Shadow Registers (RO) | 316  |

| 159  | Tx LO Ring Port - Defects                                   |      |

| 160  | Tx LO Ring Port - Interrupt Mask (RW)                       |      |

| 161  | Tx LO Ring Port - Event Interrupt (RO)                      |      |

| 162  | Tx LO Ring Port - Defect Interrupt (RO)                     | 317  |

| 163  | Rx LO Ring Port - Configuration (RW)                        |      |

| 164  | LO Interrupt Controller - Interrupts (RO)                   |      |

| 165  | LO Interrupt Controller - Interrupt Masks (RW)              |      |

| 166  | LO Interrupt Controller - Summary (RO)                      |      |

| 167  | Rx HO Ring Port - Configuration (RW)                        |      |

| 168  | Tx HO Ring Port - Configuration (RW)                        |      |

| 169  | Tx HO Ring Port - Counter Configuration (RW)                |      |

| 170  | Tx HO Ring Port - Event Latch (COW-1)                       |      |

| 171  | Tx HO Ring Port - Performance Counters (RW)                 |      |

| 172  | Tx HO Ring Port - Performance Counter Shadow Registers (RO) |      |

| 173  | Tx HO Ring Port - Defects                                   |      |

| 174  | Tx HO Ring Port - Interrupt Mask (RW)                       |      |

| 175  | Tx HO Ring Port - General Interrupt (RO)                    |      |

| 176  | Tx HO Ring Port - Defect Interrupt (RO)                     |      |

| 177  | HO POH Monitor - Received-64 Byte Trace Message (RO)        |      |

| 178  | HO POH Monitor - Received 16-Byte Trace Message (RO)        |      |

| 179  | HO POH Monitor - Accepted Bytes (RO)                        |      |

| 180  | HO POH Monitor - Expected J1 Bytes (RW)                     |      |

| 181  | HO POH Monitor - Expected C2 Bytes (RW)                     |      |

| 182  | HO POH Monitor - Received POH Bytes (RO)                    |      |

| 183  | HO POH Monitor - Accepted POH Bytes (RO)                    |      |

| 184  | HO POH Monitor - Configuration (RW)                         |      |

| 185  | HO POH Monitor - Loopback Control (RW)                      |      |

| 186  | HO POH Monitor - Channel Configuration (RW)                 |      |

| 187  | HO POH Monitor - Channel Status (RO)                        | 324  |

| 188  | HO POH Monitor - Channel Defects (RO)                       | 324  |

| 189  | HO POH Monitor - J1 Message Status (RO)                     | 324  |

| 190  | HO POH Monitor - Defects (RO)                               |      |

| 191  | HO POH Monitor - Latched Defects (R/COW-1)                  | 325  |

| 192  | HO POH Monitor - Defect Masks (RW)                          | 326  |

| 193  | HO POH Monitor - Defects Latched For PMFM (R/COW-0)         |      |

| 194  | HO POH Monitor - Defects PM (RO)                            | 327  |

| 195  | HO POH Monitor - Defects FM (RO)                            | 327  |

| 196  | HO POH Monitor - Defect Configuration (RW)                  |      |

| 197  | HO POH Monitor - Defect Summary (RO)                        |      |

| 198  | HO POH Monitor - Defect Summary Mask (RW)                   |      |

| 199  | HO POH Monitor - Defect Group Summary (RO)                  |      |

| 200  | HO POH Monitor - APS Event (RO)                             |      |

| 201  | HO POH Monitor - Latched APS Event (R/COW-1)                |      |

| 202  | HO POH Monitor - APS Event Mask (RW)                        |      |

| 203  | HO POH Monitor - APS Interrupt (RO)                         |      |

| Table |                                                                | age |

|-------|----------------------------------------------------------------|-----|

| 204   | HO POH Monitor - Performance Counters (RW)                     | 330 |

| 205   | HO POH Monitor - Performance Counters One Second Latch (RO)    | 330 |

| 206   | HO POH Monitor - Performance Counter Shadow Registers (RO)     | 330 |

| 207   | HO POH Monitor - Performance Counter Configuration (RW)        |     |

| 208   | HO POH Monitor - Counter Reset (WO)                            | 331 |

| 209   | HO POH Monitor - PMFM Configuration (RW)                       |     |

| 210   | TU-3 PTR Tracker - General Configuration (RW)                  |     |

| 211   | TU-3 PTR Tracker - Per Channel Configuration (RW)              |     |

| 212   | TU-3 PTR Tracker - Defects (RO)                                |     |

| 213   | TU-3 PTR Tracker - Defects Latched For Interrupt (R/COW-1)     |     |

| 214   | TU-3 PTR Tracker - Defects Latched For PMFM (R/COW-0)          |     |

| 215   | TU-3 PTR Tracker - Defects PM (RO)                             |     |

| 216   | TU-3 PTR Tracker - Defects FM (RO)                             |     |

| 217   | TU-3 PTR Tracker - Defect Masks (RW)                           |     |

| 218   | TU-3 PTR Tracker - Defect Summary (RO)                         |     |

| 219   | TU-3 PTR Tracker - Defect Summary Mask (RW)                    |     |

| 220   | TU-3 PTR Tracker - Defect Group Summary (RO)                   |     |

| 221   | TU-3 PTR Tracker - Performance Counters (RW)                   |     |

| 222   | TU-3 PTR Tracker - Performance Counter Shadow Registers (RO)   |     |

| 223   | Transmit VC-3/STS-1/TUG-3 Time Slot Interchange (RW)           |     |

| 224   | Receive VC-3/STS-1/TUG-3 Time Slot Interchange (RW)            |     |

| 225   | TU-3 PTR Generator - General Configuration (RW)                |     |

| 226   | TU-3 PTR Generator - Per Channel Configuration (RW)            |     |

| 227   | TU-3 PTR Generator - Defects (RO)                              |     |

| 228   | TU-3 PTR Generator - Defects Latched For Interrupt (R/COW-1)   |     |

| 229   | TU-3 PTR Generator - Defects Latched For PMFM (R/COW-0)        |     |

| 230   | TU-3 PTR Generator - Defects PM (RO)                           |     |

| 231   | TU-3 PTR Generator - Defects FM (RO)                           |     |

| 232   | TU-3 PTR Generator - Defect Mask (RW)                          |     |

| 233   | TU-3 PTR Generator - Defect Summary (RO)                       |     |

| 234   | TU-3 PTR Generator - Defect Summary Mask (RW)                  |     |

| 235   | TU-3 PTR Generator - Defect Group Summary (RO)                 |     |

| 236   | TU-3 PTR Generator - Performance Counters (RW)                 |     |

| 237   | TU-3 PTR Generator - Performance Counter Shadow Registers (RO) |     |

| 238   | HO POH Generator - Channel Control (RW)                        | 337 |

| 239   | HO POH Generator - Configuration (RW)                          | 338 |

| 240   | HO POH Generator - J1 Message Bytes (RW)                       | 338 |

| 241   | HO POH Generator - POH Insertion Values (RW)                   |     |

| 242   | HO POH Generator - POH Port Monitors (RO)                      | 339 |

| 243   | TU-3 Retimer - General Configuration (RW)                      | 339 |

| 244   | TU-3 Retimer - Per Channel Configuration (RW)                  | 339 |

| 245   | TU-3 Retimer - Defects (RO)                                    | 339 |

| 246   | TU-3 Retimer - Defects Latched For Interrupt (R/COW-1)         | 339 |

| 247   | TU-3 Retimer - Defect Masks (RW)                               | 340 |

| 248   | TU-3 Retimer - Defect Group Summary (RO)                       | 340 |

| 249   | TU-3 Retimer - Sequencer Configuration (RW)                    | 340 |

| 250   | TU-3 Retimer - Sequencer Data (RW)                             |     |

| 251   | AU-3/4 Retimer - General Configuration (RW)                    |     |

| 252   | AU-3/4 Retimer - Per Channel Configuration (RW)                |     |

| 253   | AU-3/4 Retimer - Defects (RO)                                  |     |

| 254   | AU-3/4 Retimer - Defects Latched For Interrupt (R/COW-1)       | 341 |

| Tabl | e                                                                         | Page |

|------|---------------------------------------------------------------------------|------|

| 255  | AU-3/4 Retimer - Defect Masks (RW)                                        | 341  |

| 256  | AU-3/4 Retimer - Defect Group Summary (RO)                                | 341  |

| 257  | AU-3/4 Retimer - Ptr Leak Reset Value (RW)                                | 342  |

| 258  | AU-3/4 Retimer - Performance Counters (RO)                                | 342  |

| 259  | HO Interrupt Controller - Interrupts (RO)                                 | 342  |

| 260  | HO Interrupt Controller - Interrupt Masks (RW)                            | 343  |

| 261  | HO Interrupt Controller - Interrupt Group Summary (RO)                    | 343  |

| 262  | Rx Combus Interface - General Configuration (RW)                          | 343  |

| 263  | Rx Combus Interface - Per Channel Configuration (RW)                      | 344  |

| 264  | Rx Combus Interface - Per Channel Status (RO)                             | 344  |

| 265  | Rx Combus Interface - Defects (RO)                                        | 344  |

| 266  | Rx Combus Interface - Defects Latched For Interrupt (R/COW-1)             | 344  |

| 267  | Rx Combus Interface - Defects Latched For PMFM (R/COW-0)                  | 344  |

| 268  | Rx Combus Interface - Defects PM (RO)                                     | 344  |

| 269  | Rx Combus Interface - Defects FM (RO)                                     | 344  |

| 270  | Rx Combus Interface - Defect Masks (RW)                                   | 345  |

| 271  | Rx Combus Interface - Defect Group Summary (RO)                           |      |

| 272  | Rx Combus Interface - Per Channel Defects (RO)                            |      |

| 273  | Rx Combus Interface - Per Channel Defects Latched For Interrupt (R/COW-1) |      |

| 274  | Rx Combus Interface - Per Channel Defects Latched For PMFM (R/COW-0)      | 345  |

| 275  | Rx Combus Interface - Per Channel Defects PM (RO)                         |      |

| 276  | Rx Combus Interface - Per Channel Defects FM (RO)                         |      |

| 277  | Rx Combus Interface - Per Channel Defect Masks (RW)                       |      |

| 278  | Rx Combus Interface - Per Channel Defect Summary (RO)                     |      |

| 279  | Rx Combus Interface - Per Channel Defect Summary Masks (RW)               |      |

| 280  | Rx Combus Interface - Per Channel Defect Group Summary (RO)               |      |

| 281  | Tx Combus Interface - General Configuration (RW)                          |      |

| 282  | Tx Combus Interface - AUG1 Configuration (RW)                             |      |

| 283  | Tx Combus Interface - AU-3 Configuration (RW)                             |      |

| 284  | Tx Combus Interface - TUG-2 Configuration (RW)                            | 348  |

| 285  | Tx Combus Interface - TU-11/TU-12 Configuration (RW)                      |      |

| 286  | Tx Combus Interface - Defects (RO)                                        |      |

| 287  | Tx Combus Interface - Defects Latched For Interrupt (R/COW-1)             | 348  |

| 288  | Tx Combus Interface - Defect Masks (RW)                                   |      |

| 289  | Tx Combus Interface - Defects Latched For PMFM (R/COW-0)                  |      |

| 290  | Tx Combus Interface - Defects PM (RO)                                     | 348  |

| 291  | Tx Combus Interface - Defects FM (RO)                                     | 348  |

| 292  | Tx Combus Interface - Defect Group Summary (RO)                           |      |

| 293  | Tx Combus Interface - Per Channel Defects (RO)                            | 349  |

| 294  | Tx Combus Interface - Per Channel Defects Latched For Interrupt (R/COW-1) | 349  |

| 295  | Tx Combus Interface - Per Channel Defect Masks (RW)                       | 349  |

| 296  | Tx Combus Interface - Per Channel Defects Latched For PMFM (R/COW-0)      |      |

| 297  | Tx Combus Interface - Per Channel Defects PM (RO)                         |      |

| 298  | Tx Combus Interface - Per Channel Defects FM (RO)                         |      |

| 299  | Tx Combus Interface - Per Channel Defect Summary (RO)                     |      |

| 300  | Tx Combus Interface - Per Channel Defect Summary Masks (RW)               |      |

| 301  | Tx Combus Interface - Per Channel Defect Group Summary (RO)               |      |

| 302  | Tx Combus Interface - Defect Configuration (RW)                           |      |

| 303  | Combus Interrupt Controller - Interrupts (RO)                             |      |

| 304  | Combus Interrupt Controller - Interrupt Masks (RW)                        |      |

| 305  | Combus Interrupt Controller - Interrupt Group Summary (RO)                |      |

| Tabl | e                                                          | Page |

|------|------------------------------------------------------------|------|

| 306  | Mapper Interrupt Controller - Interrupts (RO)              | 351  |

| 307  | Mapper Interrupt Controller - Interrupt Masks (RW)         | 351  |

| 308  | Mapper Interrupt Controller - Interrupt Group Summary (RO) | 351  |

| 309  | Reserved Registers                                         | 351  |

| 310  | Latched Alarm Bit (L1Alarm_name) Transition Selection      | 356  |

| 311  | Latched Alarm Bit (L2Alarm name) Transition Selection      | 359  |

#### **FEATURES**

The EtherMap-3 *Plus* supports the following features:

#### **MAPPINGS**

- EtherMap-3 Plus maps Ethernet traffic of up to (8) 10/100 Mb/s SMII ports or (1)1000 Mb/s GMII port onto SONET/SDH

- Performs Virtual Concatenation for SONET/SDH, compensating for up to 48 ms of differential delay

- Implements Link Capacity Adjustment Scheme (LCAS) to allow the size of the virtual concatenation groups to be changed dynamically with hitless switching.

- · Supports both High Order and Low Order Virtual Concatenation

- STS-3c SPE

- STS-3 / STS-1 SPE, STS-1-Xv

- STS-3 / STS-1 / VT1.5 SPE, VT1.5-Xv

- STS-3 / STS-1 / VT2 SPE, VT2-Xv

- STM-1 / AUG-1 / AU-4 / VC-4

- STM-1 / AUG-1 / AU-4 / VC-4 / TUG-3 / TU-3 / VC-3, VC-3-Xv<sup>1</sup>

- STM-1 / AUG-1 / AU-4 / VC-4 / TUG-3 / TUG-2 / TU-12 / VC-12, VC-12-Xv

- STM-1 / AUG-1 / AU-4 / VC-4 / TUG-3 / TUG-2 / TU-11 / VC-11, VC-11-Xv

- STM-1 / AUG-1 / AU-3 / VC-3, VC-3-Xv

- STM-1 / AUG-1 / AU-3 / VC-3 / TUG-2 / TU-12 / VC-12, VC-12-Xv

- STM-1 / AUG-1 / AU-3 / VC-3 / TUG-2 / TU-11 / VC-11, VC-11-Xv

- All supported virtual concatenation mappings can be mixed according to the [G.707] multiplexing structure up to a total payload rate equivalent to one STS-3/STM-1 signal.

- Supports a mix of 100 Mbit/s and 10 Mbit/s traffic (up to 8 ports).

- For 10/100 Mb/s operation (up to 8 ports), can virtually concatenate up to 63 VC-12/VT2 SPEs or 64 VC-11/VT1.5-SPEs.

- For 100 Mb/s operation, a single VC-4 or a single STS-3c SPE can be used, or

- •Can virtually concatenate up to 64 VC-11s or up to 63 VC-12s or up to 3 VC-3s

- •Can virtually concatenate up to 64 VT1.5-SPEs or up to 63 VT2-SPEs or up to 3 STS-1-SPEs

- For 1000 Mb/s

- •Supports either a single VC-4, or can virtually concatenate up to 3 VC-3s

- •Supports either a single STS-3c-SPE, or can virtually concatenate up to 3 STS-1-SPEs

#### **ENCAPSULATION PROTOCOLS**

- EtherMap-3 Plus supports one of four encapsulation protocols per Ethernet MAC:

- LAPS (Link Access Procedure SDH)

- LAPF (Link Access Procedure for Framed Mode service)

- GFP (Generic Framing Procedure)

- PPP (with BCP support)

<sup>1.</sup> Note: in ITU-T SDH a VC-3 can either be high order (AU-3/STS-1) or low order (TU-3). In the remainder of the EtherMap-3 *Plus* data sheet high order and low order refers to the type of path overhead bytes rather than the order of the path in the multiplexing hierarchy. Though both low and high order VC-3 mapping is supported, VC-3 operation will be covered in the high order path sections.

#### **ETHERNET PORTS**

The EtherMap-3 Plus provides the following Ethernet Port features:

- Eight independent SMII (Serial Medial Independent Interfaces) for 10/100 Mbit/s Ethernet

- Global 125 MHz reference clock

- · Global Synchronization signal

- · Lead selects PHY or Switch connection to external client

- Single GMII (Gigabit MII) for 1000 Mbit/s Ethernet

- · Lead shared with the SMII ports

- Selection of GMII or SMII is selected through a lead

- Ethernet Management Interface

- PHY or Switch Selection

### 10/100/1000 MBIT/S ETHERNET MEDIA ACCESS CONTROLLER (MAC) BLOCK

- Compliant to IEEE 802.3, 802.3u, 802.3x, 802.3z, and 802.3ac

- Full Duplex Operation in 10/100/1000 Mbit/s

- Half Duplex Operation in 10/100 Mbit/s

- MAC control sub layer provides support for control frames including PAUSE frames

- Provides support for statistics gathering based on RMON MIB Group 1, RMON MIB Group 2, RMON MIB Group 3, RMON MIB Group 9, RMON MIB 2, and the dot 3 Ethernet MIB

#### **SDRAM INTERFACE**

- Glueless interface to external 64 Mbits, 128 Mbits, or 256 Mbits SDRAM devices

- 32 Data, 13 Address, 1 Chip Select, 1 Clock, 1 Clock Enable, 1 Row Address Strobe, 1 Column Address Strobe, 1 Write Enable Strobe, 1 Data Bus Mask, and 2 Bank Address leads

- · Buffers TX/RX data transfers

- Clock frequency of 100 MHz

- · Programmable Refresh Period

- CAS latency of 3 supported

- Refresh operation is transparent to the user

- Trp timing of the selected SDRAM must be below 30 ns.

#### **TELECOM BUS TIMING**

A single Telecom Bus interface is provided for interfacing to the SONET/SDH line through one of TranSwitch's TOH/POH Terminator devices such as the PHAST<sup>®</sup>-3N or the PHAST-12E/POP-12 chip set. Timing for adding tributaries to the Add bus is derived from either the Drop bus or the Add bus. The EtherMap-3 *Plus* provides the following timing modes for the Add bus: