## QT1M Device Quad T1 Mapper TXC-04251

# DATA SHEET

# **FEATURES**

- Add/drop four 1.544 Mbit/s signals from an STS-1, an STS-3/AU-3, or an STM-1 VC-4

- Independent add and drop bus timing modes

- Selectable AMI or B8ZS positive/negative rail or NRZ T1 interface. Performance counter provided for coding violations

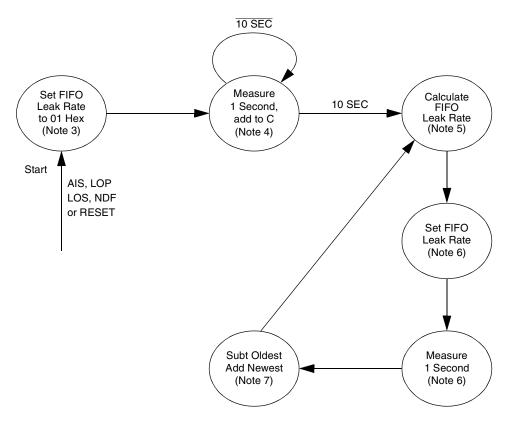

- Digital desynchronizer reduces systemic jitter in the presence of multiple pointer movements. A register is also provided to control the internal FIFO leak rate

- Drop buses are monitored for parity, loss of clock, upstream AIS and H4 multiframe errors

- Performance counters are provided for VT/TU pointer movements, BIP-2 errors and Far End Block Errors (FEBEs)

- VT/TUs are monitored for Loss Of Pointer, New Data Flags (NDFs), AIS, Remote Defect Indication (RDI), and size errors (S-bits)

- V5 Byte Signal Label Mismatch and Unequipped detection

- T1 facility and line loopbacks, generation of BIP-2 and FEBE errors, and send RDI capability

- Multiplexed microprocessor bus interface with interrupt capability

- IEEE 1149.1 standard boundary scan

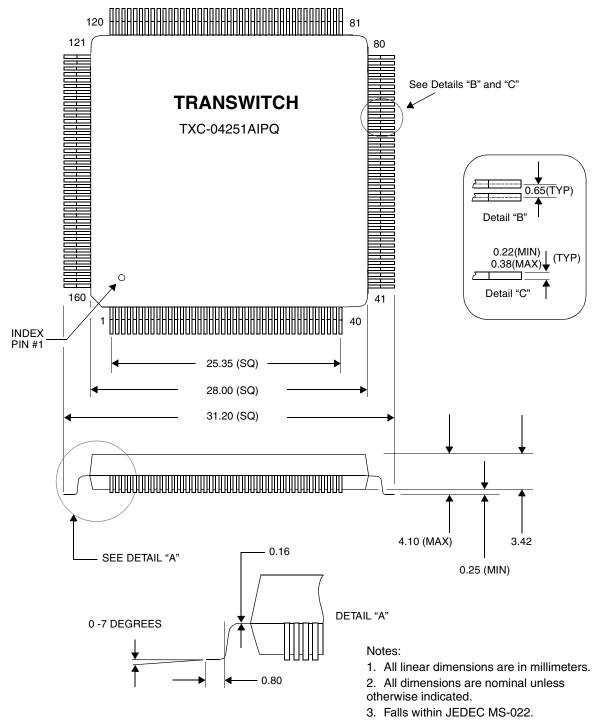

- 160-pin plastic quad flat package

## **DESCRIPTION**

The Quad T1 Mapper device is designed for add/drop multiplexer, terminal multiplexer, and dual and single unidirectional ring applications. Four T1 1.544 Mbit/s signals are mapped to and from asynchronous 1.5 Virtual Tributaries (VT1.5s) or Tributary Unit-11s (TU-11s). The QT1M interfaces to a multiple-segment, byte-parallel SONET/SDH-formatted bus at the 19.44 Mbit/s byte rate for STS-3/STM-1 operation or at the 6.48 Mbit/s byte rate for STS-1 operation. The T1 1.544 Mbit/s signals can be either AMI/B8ZS positive/negative rail- or NRZ-formatted signals. The QT1M provides performance counters, alarm detection, and the ability to generate errors and Alarm Indication Signals (AIS). T1 facility and line loopback capabilities are also provided.

The bus interface can connect to other TranSwitch devices, such as the STM-1/STS-3/STS-3c Overhead Terminator (SOT-3), TXC-03003B, to form an STS-3/STM-1 add/drop or terminal system.

# APPLICATIONS

- STS-1/STS-3/STM-1 to 1.544 Mbit/s add/drop mux/demux

- · Unidirectional or bidirectional ring applications

- STS-1/STS-3/STM-1 termination terminal mode multiplexer

- STS-1/STS-3/STM-1 test equipment

# TABLE OF CONTENTS

| Section                                                | Page  |

|--------------------------------------------------------|-------|

| List of Figures                                        | 3     |

| Block Diagram                                          | 5     |

| Block Diagram Description                              | 5     |

| Pin Diagram                                            | 9     |

| Pin Descriptions                                       | 10    |

| Absolute Maximum Ratings and Environmental Limitations | 17    |

| Thermal Characteristics                                | 17    |

| Power Requirements                                     | 17    |

| Input, Output and Input/Output Parameters              | 18    |

| Timing Characteristics                                 | 20    |

| Operation                                              | 29-60 |

| Bus Interface Modes                                    | 29    |

| Bus Mode Selection                                     | 30    |

| SONET/SDH Add/Drop Multiplexing Format Selections      | 30    |

| Add/Drop VT/TU Selection                               | 31    |

| Unequipped Payload Generation                          | 32    |

| Bus Timing                                             | 33    |

| Drop Bus Multiframe Alignment                          | 33    |

| Add Bus Multiframe Alignment                           | 35    |

| Performance Counters                                   | 36    |

| Alarm Structure                                        | 36    |

| Interrupt Structure                                    | 36    |

| SONET/SDH AIS Detection                                | 39    |

| VT/TU Pointer Tracking                                 | 39    |

| Pointer Leak Rate Calculations                         | 42    |

| Remote Defect Indications (RDI)                        | 43    |

| Overhead Communications Bit Access                     | 45    |

| TUG-3 Null Pointer Indicator                           | 46    |

| T1 Loopback Capability                                 | 47    |

| Resets                                                 | 48    |

| Data Throughput Delay                                  | 48    |

| Boundary Scan                                          | 49    |

| Multiplex Format and Mapping Information               | 55    |

| Memory Map                                             | 61    |

| Memory Map Descriptions                                | 65    |

| Package Information                                    | 86    |

| Ordering Information                                   | 87    |

| Related Products                                       | 87    |

| Standards Documentation Sources                        | 88    |

| List of Data Sheet Changes                             | 90    |

| Documentation Update Registration Form*                | 93    |

\* Please note that TranSwitch provides documentation for all of its products. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

# LIST OF FIGURES

| Figu | re                                                                     | Page |

|------|------------------------------------------------------------------------|------|

| 1.   | QT1M TXC-04251 Block Diagram                                           | 5    |

| 2.   | 1544 kbit/s Mapping                                                    |      |

| 3.   | QT1M TXC-04251 Pin Diagram                                             | 9    |

| 4.   | Ports 1, 2, 3 and 4 DS1 Transmit Timing                                | 20   |

| 5.   | Ports 1, 2, 3 and 4 DS1 Receive Timing                                 | 21   |

| 6.   | STS-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus       |      |

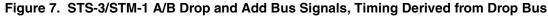

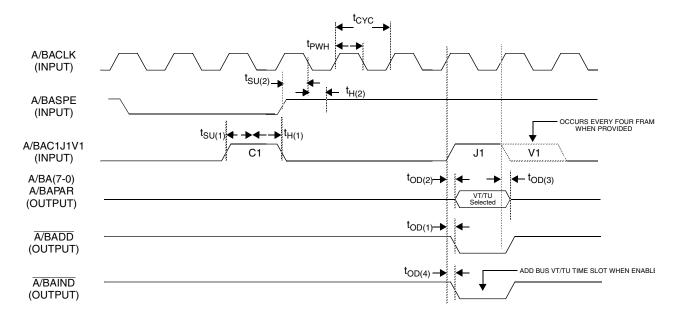

| 7.   | STS-3/STM-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus | 23   |

| 8.   | STS-1 A/B Add Bus Signals, Timing Derived from Add Bus                 | 24   |

| 9.   | STS-3/STM-1 A/B Add Bus Signals, Timing Derived from Add Bus           |      |

| 10.  | Microprocessor Read Cycle Timing                                       |      |

| 11.  | Microprocessor Write Cycle Timing                                      |      |

| 12.  | Boundary Scan Timing                                                   |      |

| 13.  | H4 Byte Floating VT Mode Bit Allocation                                |      |

| 14.  | VT/TU Pointer Tracking State Machine                                   | 41   |

| 15.  | Facility and Line Loopbacks                                            |      |

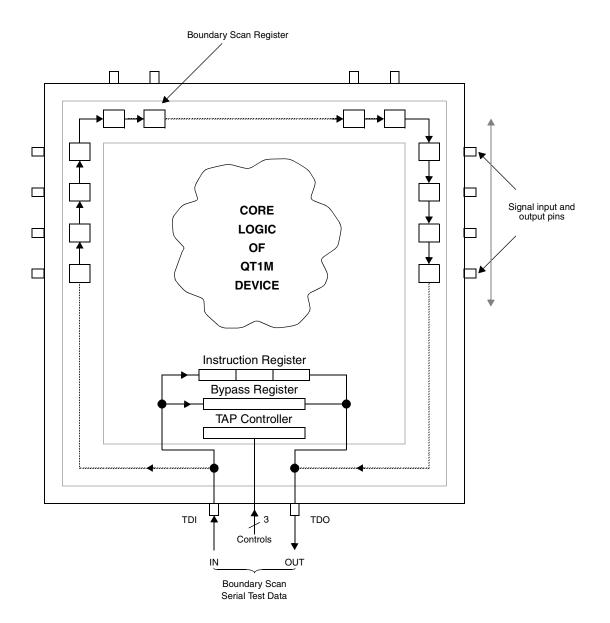

| 16.  | Boundary Scan Schematic                                                | 50   |

| 17.  | QT1M TXC-04251 160-Pin Plastic Quad Flat Package                       |      |

This page has been intentionally left blank.

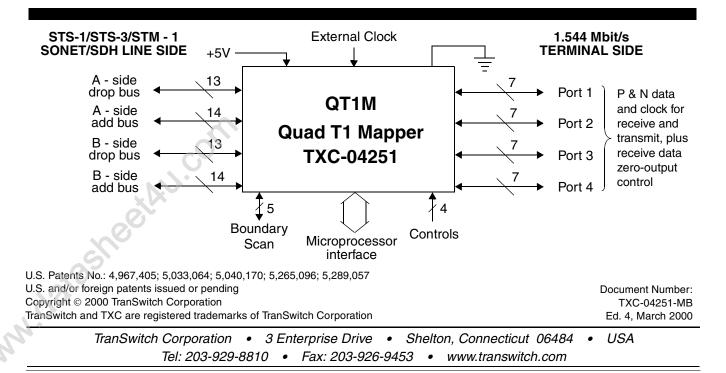

# **BLOCK DIAGRAM**

Figure 1. QT1M TXC-04251 Block Diagram

# **BLOCK DIAGRAM DESCRIPTION**

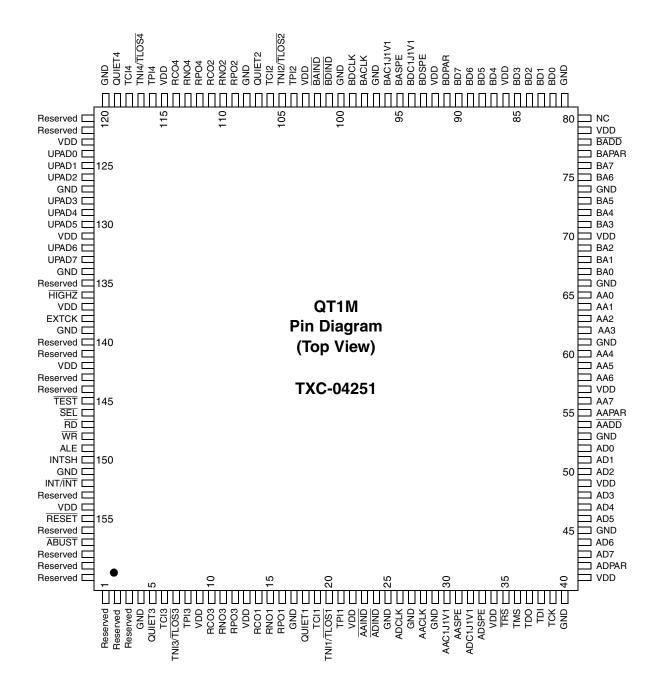

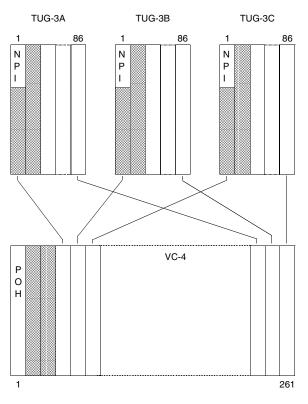

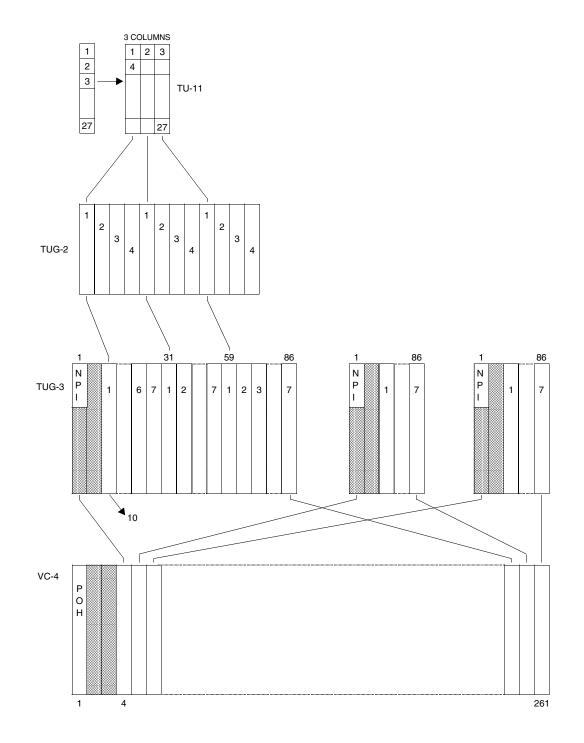

The block diagram for the Quad T1 Mapper is shown in Figure 1. The Quad T1 Mapper interfaces to four buses, designated as A Drop, B Drop, A Add, and B Add. The four buses run at the STS-3/STM-1 rate of 19.44 Mbyte/s, or at the STS-1 rate of 6.48 Mbyte/s. For North American applications, the asynchronous T1 signals are carried in floating Virtual Tributary 1.5s (VT1.5s) in a Synchronous Transport Signal -1 (STS-1), or in STS-1s that are carried in a Synchronous Transport Signal - 3 (STS-3). For ITU applications, the T1 signals are carried in floating mode Tributary Unit -11s (TU-11s) in the STM-1 Virtual Container -4 structure (VC-4) using Tributary Unit Group -3 (TUG-3), or in the STM-1 Virtual Container -3 structure (VC-3) using Tributary Unit Group -2 (TUG-2) mapping schemes. Four T1 signals can be dropped from one bus (A Drop or B Drop), or from both of the drop buses, to the T1 lines. Four asynchronous T1 signals are formatted into VT1.5s or TUs and are added to either of the add buses, or both, depending upon the mode of operation. When the Quad T1 Mapper is configured for drop bus timing, the add buses are, by definition, byte- and multiframe-synchronous with their like-named drop buses, but are delayed by one byte time because of internal processing. For example, if a byte in the STM-1 Virtual Container -4 structure (VC-4) using Tributary Unit Group -3 (TUG-3), VT1.5/TU-11 is to be added to the A Add bus, the time of its placement on the bus is derived from the A Drop

bus timing, and from software instructions specifying which VT/TU number is being dropped/added. When the device is configured for add bus timing, the add bus, parity, and add indicator signals are derived from the add clock, C1J1V1 and SPE signals.

The A Receive block is identical to the B Receive block. The VT/TU Terminate block is repeated 8 times, two for each port (A and B sides). The Destuff, Desync, and AMI/B8ZS Coder Blocks are repeated four times, one for each port. The interface between a drop bus and Receive block consists of 12 input leads (pins), and an optional output lead: a byte clock, byte-wide data, a C1J1 indicator which may be carrying a V1 indication making the signal a C1J1V1 indicator, an SPE indicator, and an odd parity bit for the last-named three signals. Parity is selectable by control bits for even parity and for the data byte only. The output lead is an optional VT/TU select indicator signal. The Drop C1J1V1 signal is used in conjunction with the Drop SPE signal to determine the location of the various pulses. The C1 pulse identifies the location of the C1 byte when the SPE signal is low. A single J1 pulse identifies the starting location of the J1 byte in the VC-4 format, when the SPE signal is high. Three J1 pulses are provided for the STS-3 format, each identifying the starting location of the J1 byte in each of the STS-1 signals.

The Quad T1 Mapper can operate with a V1 pulse in the C1J1V1 signal, or it can use an internal H4 detector for determining the location of the V1 pulse. The V1 pulse location is used to determine the location of the pointer byte V1. For STM-1 VC-4 operation, if the C1J1V1 signal is used, a single V1 pulse must occur three drop bus clock cycles every four frames following the J1 pulse. For STS-3 operation, three V1 pulses must be present every four frames. Each of the three V1 pulses must be present three clock cycles after the corresponding J1 pulse, when the SPE signal is high. For example, in a VC-4 signal, the J1 pulse identifies the J1 byte location (defined as the starting location for the VC-4) in the POH bytes. In the next column (first clock cycle) all the rows are assigned as fixed stuff. Similarly, in the next column (second clock cycle) all the rows are assigned as fixed stuff. The next column (third clock cycle) defines the start of TUG-3 A. This column is where the V1 pulse occurs every four frames. However, the actual V1 byte location is six clock cycles after the V1 pulse.

For STS-1 operation, one V1 must be present if the C1J1V1 signal is used. The V1 pulse must occur on the next clock cycle after J1, and when the SPE signal is high. The J1 pulse identifies the J1 byte location (defined as the starting location for the STS-1) in the POH bytes. In the next column (first clock cycle) the VTs start. Thus, the V1 pulse identifies the starting location of the first V1 byte in the signal. The rest of the V1 bytes for the 21 VT1.5/TU-11s are aligned regarding their starting point with respect to the V1 pulse.

Each bus is monitored for parity errors, loss of clock, H4 multiframe alignment if selected, and an upstream SONET/SDH AIS indication. The Quad T1 Mapper can monitor either the TOH E1 bytes or the H1/H2 bytes for an AIS indication. Which E1 byte and H1/H2 bytes are selected is a function of the VT/TU selected.

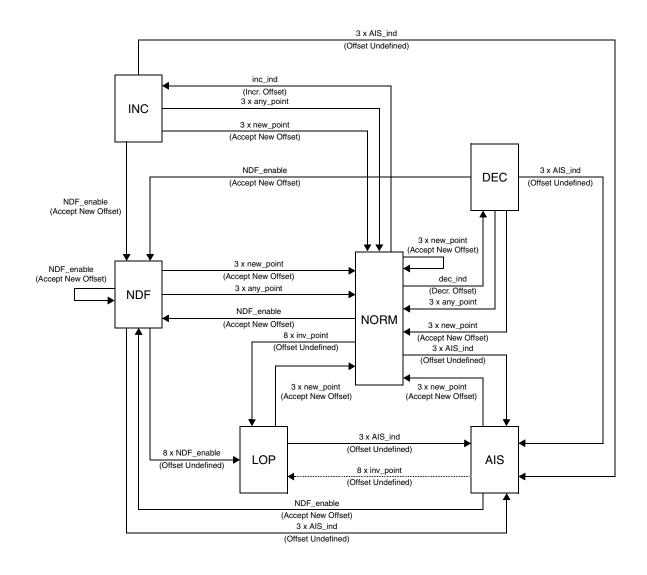

Each VT/TU Terminate block (A and B side) performs pointer processing based on the location of the V1 and V2 bytes. The pointer bytes are monitored for loss of pointer, VT AIS indication, and NDF. The pointer tracking process is based on the latest ETSI standard, which also meets ANSI/Bellcore requirements. Pointer increments and decrements are also counted, and the SS-bits are monitored for the correct value. This block also monitors the various alarms found in the V5 and Z7 bytes, including signal label mismatch detection, unequipped status detection, BIP-2 parity error detection and error counter, FEBE counter, and the RDI indications.

A control bit for each port selects the VT/TU from either the A Drop or B Drop bus. The VT/TU is destuffed in the Destuff block using majority logic rules for the three sets of three justification control bits to determine if the two S-bits are data bits or frequency justification bits.

The Desync block removes the effects on the T1 output of systemic jitter that might occur because of signal mappings and pointer movements in the network. The Desync block contains two parts, a pointer leak buffer, and a T1 loop buffer. The pointer leak buffer can accept up to five consecutive pointer movements, and can adjust the effect over time. The T1 Loop Buffer consists of a digital loop filter, which is designed to track the frequency of the received T1 signal and to remove both transmission and stuffing jitter.

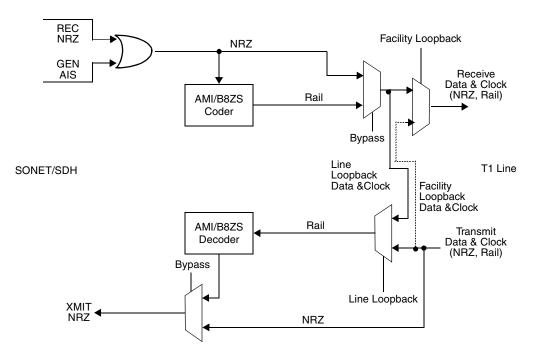

An option for each port provides either NRZ data and clock, or an AMI- or B8ZS-encoded positive and negative rail signal for the T1 interface. Transmit data (towards the T1 line), for all four channels, can be clocked out on either rising or falling edges of the clock. In addition, control bits are provided for forcing the data and clock signals to a high impedance state. A control lead is provided for forcing the output leads to the 0 state.

In the add direction, the Quad T1 Mapper accepts clock and either NRZ data or AMI - or B8ZS-encoded positive and negative rail signals. Data, for all four channels, can be clocked in on either a negative or rising edge of the clock. In the NRZ mode, an external loss of clock indication input signal can be provided. For the rail signal, coding violations are counted, and the signal monitored for loss of signal. A T1AIS detector is also provided.

The data signal is written into a FIFO in one of the eight Stuff/Sync Blocks. Threshold modulation is used for the frequency justification process. Timing information from the drop bus or add bus is used to read the FIFO and perform the VT/TU justification process. This block permits the tracking of the incoming T1 signal having an average frequency offset as high as 120 ppm, and up to 5 UI of peak-to-peak jitter. Since the Quad T1 Mapper supports a ring architecture, two sets of blocks are provided for each port. The VT/TU selection is the same for both blocks. A control bit, and transmit line alarms, can generate a T1AIS.

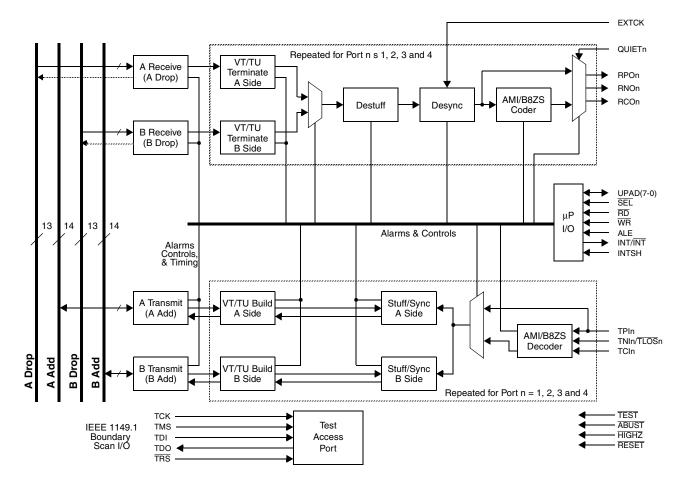

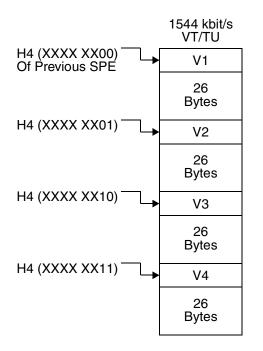

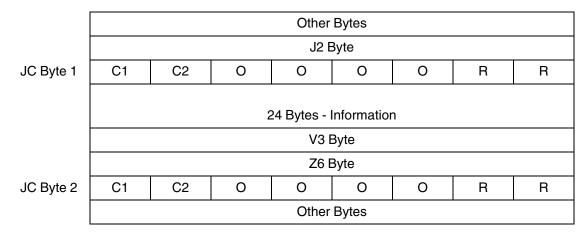

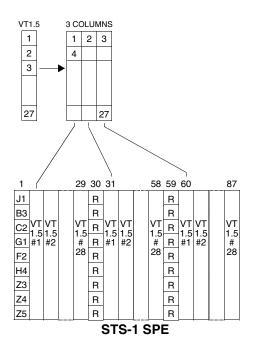

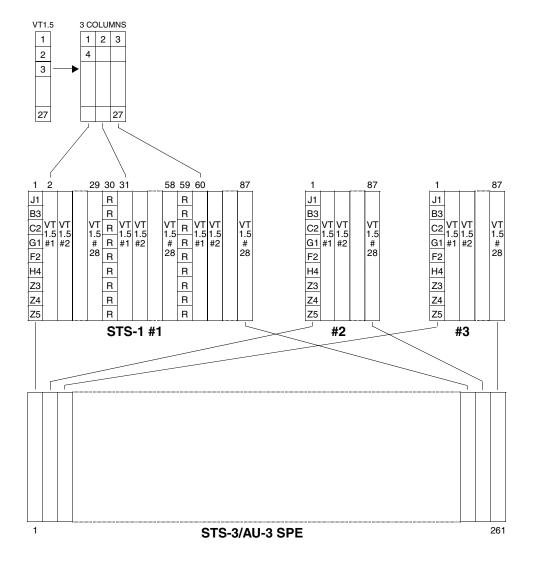

The eight VT/TU Blocks format the VT/TU into a STS-1, STS-3 or STM-1 structure for the asynchronous 1544 kbit/s signals, as shown in Figure 2. The pointer value carried in the V1 and V2 bytes is transmitted with a fixed value of 78. Transmit access is provided for the 8 overhead communications channel bits (O-bits) via the microprocessor. The microprocessor also writes the signal label, and the values of the J2, Z6, and Z7 bytes. The Far End Block Error (FEBE) is inserted from the BIP-2 errors detected on the receive side, and BIP-2 parity is generated. Control bits are provided for generating unequipped status, generating VT/TU AIS, and inserting FEBE and BIP-2 errors. The ability to generate Null Pointer Indicators (NPIs) is also provided for the STM-1 VC-4 format.

The A Transmit block is identical to the B Transmit block. The interface between an add bus and a Transmit block consists of three input pins and eleven output pins, when the add bus timing mode is selected. The input pins are a byte clock, a C1J1V1 indicator, and an SPE indicator. The output pins are byte-wide data, a parity indicator, an add indicator, and an optional VT/TU selection indicator signal. The Add C1J1V1 signal is used in conjunction with the Add SPE signal to determine the location of the various pulses. An option is provided in which the drop side V1 reference pulse, either from the drop bus C1J1V1 indicator or from the H4 multiframe detector, may be used as the add side V1 reference pulse.

When drop bus timing is selected, the output pins are byte-wide data, a parity indicator, an add indicator, and an optional VT/TU selection indicator signal. The add bus clock, SPE and C1J1V1 signals are disabled.

The microprocessor interface consists of a multiplexed address/data bus. Interrupt capability is also provided. The alarms that cause the interrupt can be set on positive, negative, or positive or negative transitions, and on positive levels. Interrupt mask bits are provided for register byte locations, and some defined bits.

Control bits are provided which enable a T1 facility or line loopback. Because of the complexity of the SONET/SDH interface and the two timing modes, SONET/SDH loopback of the VT/TUs is not supported.

The Boundary Scan Interface block provide a five-pin Test Access Port (TAP) that conforms to the IEEE 1149.1 standard. This standard provides external boundary scan functions to read and write the external I/O pins from the TAP for board and component test.

Figure 2. 1544 kbit/s Mapping

DATA SHEET

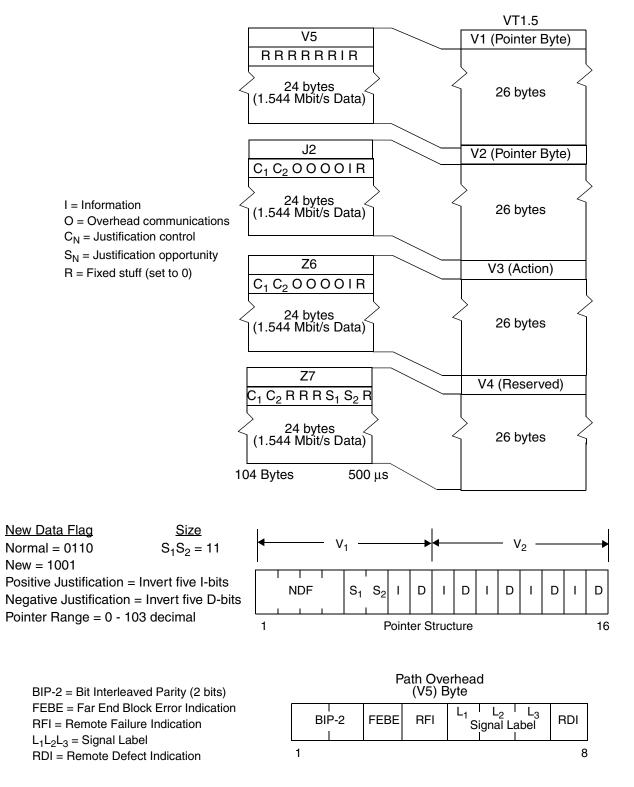

## **PIN DIAGRAM**

Figure 3. QT1M TXC-04251 Pin Diagram

## **PIN DESCRIPTIONS**

#### POWER SUPPLY, GROUND, NO CONNECT AND RESERVED

| Symbol   | Pin No.                                                                                    | I/O/P * | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD      | 9, 13, 22, 34, 41, 49, 57, 70,<br>79, 86, 92, 103, 115, 123,<br>131, 137, 142, 154         | Р       |      | <b>VDD:</b> +5 volt supply voltage, ±5%.                                                                                                                                                                                                                                                                                                                                                                                        |

| GND      | 4, 17, 25, 27, 29, 40, 45, 53,<br>61, 66, 74, 81, 97, 100, 108,<br>120, 127, 134, 139, 151 | Р       |      | Ground: 0 volt reference.                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC       | 80                                                                                         |         |      | <b>No Connect:</b> NC pins are not to be connected, not<br>even to another NC pin, but must be left floating. NC<br>pins may be used for manufacturing test purposes,<br>and/or may be assigned to functions in future<br>versions of the device. Connection of these pins<br>may impair performance or even cause damage to<br>the device, and could prevent the substitution of<br>future device versions in the application. |

| Reserved | 1, 2, 3, 121, 122<br>135, 140, 141<br>143, 144, 153<br>156, 158 - 160                      |         |      | <b>Reserved:</b> Reserved pins permit the connection of leads for input/output signals which are not used/provided by the QT1M device. Such signals may be used/provided by other pin-compatible devices that could be substituted in QT1M applications, particularly future versions of the QT1M device which have additional features requiring the use of these pins.                                                        |

\* I = Input; O = Output; P = Power; T = Tristate

## A DROP AND A ADD BUS I/O

| Symbol | Pin No. | I/O/P | Type * | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|---------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADCLK  | 26      | Ι     | TTLs   | <b>A Drop Bus Clock:</b> This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. A Drop bus byte-wide data (AD7-AD0), the parity bit (ADPAR), SPE indication (ADSPE), and the C1J1V1 indication (ADC1J1) are clocked in on falling edges of this clock. This clock may also be used for timing and deriving the like-named add bus byte-wide data, add and VT/TU indications, and parity bits. The add bus signals are clocked out on rising edges of the clock during the time slots that correspond to the selected VT/TU. |

| ADPAR  | 42      | Ι     | TTL    | A Drop Bus Parity Bit: An odd parity bit input signal representing the parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus. Control bits are provided which enable even parity to be calculated (control bit DPE is 1), and for the data byte only (control bit PDDO is 1).                                                                                                                                                                                                                                                               |

\* See Input, Output and Input/Output Parameters section for Type definitions.

Name/Function

| TRANSWITCH |                                      |       |        |                           |  |  |  |

|------------|--------------------------------------|-------|--------|---------------------------|--|--|--|

|            | <b>`</b>                             |       |        |                           |  |  |  |

| Symbol     | Pin No.                              | I/O/P | Type * |                           |  |  |  |

| AD(7-0)    | 43, 44, 46,<br>47, 48, 50,<br>51, 52 | Ι     | TTL    | A Dr<br>to the<br>first I |  |  |  |

| ADSPE      | 33                                   | Ι     | TTL    | A Dr<br>durir             |  |  |  |

| • • • • • |                                         |      | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------|------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD(7-0)   | 43, 44, 46,<br>47, 48, 50,<br>51, 52    | I    | TTL                                     | <b>A Drop Bus Data Byte:</b> Byte-wide data that corresponds to the STS-3/STM-1/STS-1 signal from the drop bus. The first bit received (dropped) corresponds to bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADSPE     | 33                                      | I    | TTL                                     | <b>A Drop Bus SPE Indicator:</b> A signal that is active high during each byte of the STS-3/STM-1/STS-1 payload, and low during Transport Overhead times.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADC1J1V1  | 32                                      | I    | TTL                                     | A Drop Bus C1J1V1 Indications: An active high timing<br>signal that carries STS-3/STM-1/STS-1 starting frame<br>and SPE information. This signal works in conjunction<br>with the ADSPE signal. The C1 pulse identifies the<br>location of the first C1 byte in the STS-3/STM-1 signal,<br>and the C1 byte in the STS-1 signal, when ADSPE is low.<br>The J1 signal identifies the starting location of the J1<br>signal when ADSPE is high. One or more V1 pulses may<br>be present depending upon the format. The V1 pulses<br>may be used in place of the H4 byte as the multiframe<br>indication. |

| ADIND     | 24                                      | 0    | CMOS<br>4mA                             | A Drop Bus VT/TU Selection Indication: Enabled when<br>control bit ADnEN is written with a 1. An active low signal<br>that is clocked out for the time slots determined by VT/TU<br>selection (VTNn register) for each port.                                                                                                                                                                                                                                                                                                                                                                          |

| AACLK     | 28                                      |      | TTLS                                    | A Add Bus Clock: When the add bus timing mode is selected, this input must be provided for add bus timing. This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication (AASPE), and the C1J1V1 indication (AAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (AA7-AA0), add indicator (AADD), and parity bit (AAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected VT/TU. When drop bus timing is selected, this input is disabled.                |

| AAPAR     | 55                                      | O(T) | CMOS<br>4mA                             | A Add Bus Parity Bit: An odd parity output signal that is calculated over the byte-wide add data. This tristate pin is only active when there is data being added to the add bus. When control bit APE is 1 even parity is calculated.                                                                                                                                                                                                                                                                                                                                                                |

| AA(7-0)   | 56, 58,<br>59, 60,<br>62, 63,<br>64, 65 | O(T) | CMOS<br>4mA                             | A Add Bus Data Byte: Byte-wide data that corresponds to the selected VT/TU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AASPE     | 31                                      | I    | TTL                                     | A Add Bus SPE Indicator: When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STS-3/STM-1/STS-1 payload, and low during Transport Overhead byte times.                                                                                                                                                                                                                                                                                                                                                         |

| Symbol   | Pin No. | I/O/P | Type *      | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AAC1J1V1 | 30      | Ι     | TTL         | <b>A Add Bus C1J1V1 Indications:</b> When the add bus timing mode is selected, this signal must be provided for add bus timing. An active high timing signal that carries STS-3/STM-1/STS-1 starting frame and SPE information. This signal works in conjunction with the AASPE signal. The C1 pulse identifies the location of the first C1 byte in the STS-3/STM-1 signal, and the C1 byte in the STS-1 signal, when AASPE is low. The J1 signal identifies the starting location of the J1 signal when AASPE is high. The J1 signal identifies the location of the J1 byte. One or more V1 pulses may be present depending upon the format. The V1 pulses may be used in place of the H4 byte as the multiframe indication. |

| AAIND    | 23      | 0     | CMOS<br>4mA | A Add Bus VT/TU Selection Indication: Enabled when<br>control bit AAnEN is written with a 1. An active low signal<br>that is clocked out for the time slots determined by VT/TU<br>selection (VTNn register) for each port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AADD     | 54      | 0     | CMOS<br>4mA | A Add Bus Add Data Present Indicator: This normally active low signal is present when output data to the A Add bus is valid. It identifies the location of all of the VT/TU time slots being selected. When control bit ADDI is 1, the indicator is active high instead of low.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## **B DROP AND B ADD BUS I/O**

| Symbol  | Pin No.                                 | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-----------------------------------------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDCLK   | 99                                      | Ι     | TTLs | <b>B Drop Bus Clock:</b> This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. B Drop bus byte-wide data (BD7-BD0), the parity bit (BDPAR), SPE indication (BDSPE), and the C1J1V1 indication (BDC1J1) are clocked in on falling edges of this clock. This clock may also be used for timing and deriving the like-named add bus byte-wide data, add and VT/TU indications, and parity bits. The add bus signals are clocked out on rising edges of the clock during the time slots that correspond to the selected VT/TU. |

| BDPAR   | 91                                      | Ι     | TTL  | <b>B</b> Drop Bus Parity Bit: An odd parity bit input signal representing the parity calculation for each data byte, SPE, and C1J1V1 signal from the drop bus. Control bits are provided which enable even parity to be calculated (control bit DPE is 1), and for the data byte only (control bit PDDO is 1).                                                                                                                                                                                                                                                        |

| BD(7-0) | 90, 89,<br>88, 87,<br>85, 84,<br>83, 82 | Ι     | TTL  | <b>B Drop Bus Data Byte:</b> Byte-wide data that corresponds to the STS-3/STM-1/STS-1 signal from the drop bus. The first bit received (dropped) corresponds to bit 7.                                                                                                                                                                                                                                                                                                                                                                                                |

| Symbol   | Pin No.                                 | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|-----------------------------------------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BDSPE    | 93                                      | Ι     | TTL         | <b>B Drop Bus SPE Indicator:</b> A signal that is active high during each byte of the STS-3/STM-1/STS-1 payload, and low during Transport Overhead times.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BDC1J1V1 | 94                                      | I     | TTL         | <b>B Drop Bus C1J1V1 Indications:</b> An active high timing signal that carries STS-3/STM-1/STS-1 starting frame and SPE information. This signal works in conjunction with the BDSPE signal. The C1 pulse identifies the location of the first C1 byte in the STS-3/STM-1 signal, and the C1 byte in the STS-1 signal, when BDSPE is low. The J1 signal identifies the starting location of the J1 signal when BDSPE is high. One or more V1 pulses may be present depending upon the format. The V1 pulses may be used in place of the H4 byte as the multiframe indication.                |

| BDIND    | 101                                     | 0     | CMOS<br>4mA | <b>B Drop Bus VT/TU Selection Indication:</b> Enabled when control bit BDnEN is written with a 1. An active low signal that is clocked out for the time slots determined by VT/TU selection (VTNn register) for each port.                                                                                                                                                                                                                                                                                                                                                                    |

| BACLK    | 98                                      | Ι     | TTLs        | <b>B</b> Add Bus Clock: When the add bus timing mode is selected, this input must be provided for add bus timing. This clock operates at 19.44 MHz for STS-3/STM-1 operation, and at 6.48 MHz for STS-1 operation. The add bus SPE indication (BASPE), and the C1J1V1 indication (BAC1J1V1) are clocked in on falling edges of this clock. Add bus byte-wide data (BA7-BA0), add indicator (BADD), and parity bit (BAPAR) are clocked out on rising edges of the clock during the time slots that correspond to the selected VT/TU. When drop bus timing is selected, this input is disabled. |

| BAPAR    | 77                                      | O(T)  | CMOS<br>4mA | <b>B Add Bus Parity Bit:</b> An odd parity output signal that is calculated over the byte-wide add data. This tristate pin is only active when there is data being added to the add bus. When control bit APE is 1, even parity is calculated.                                                                                                                                                                                                                                                                                                                                                |

| BA(7-0)  | 76, 75,<br>73, 72,<br>71, 69,<br>68, 67 | O(T)  | CMOS<br>4mA | <b>B Add Bus Data Byte:</b> Byte-wide data that corresponds to the selected VT/TU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BASPE    | 95                                      | Ι     | TTL         | <b>B Add Bus SPE Indicator:</b> When the add bus timing mode is selected, this signal must be provided for add bus timing. This signal must be high during each byte of the STS-3/STM-1/STS-1 payload, and low during Transport Overhead byte times.                                                                                                                                                                                                                                                                                                                                          |

TRANSWITCH

| Symbol   | Pin No. | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|-------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BAC1J1V1 | 96      | Ι     | TTL         | <b>B</b> Add Bus C1J1V1 Indications: When the add bus timing mode is selected, this signal must be provided for add bus timing. An active high timing signal that carries STS-3/STM-1/STS-1 starting frame and SPE information. This signal works in conjunction with the BASPE signal. The C1 pulse identifies the location of the first C1 byte in the STS-3/STM-1 signal, and the C1 byte in the STS-1 signal, when BASPE is low. The J1 signal identifies the starting location of the J1 signal when BASPE is high. The J1 signal identifies the location of the J1 byte. One or more V1 pulses may be present depending upon the format. The V1 pulses may be used in place of the H4 byte as the multiframe indication. |

| BAIND    | 102     | 0     | CMOS<br>4mA | <b>B Add Bus VT/TU Selection Indication:</b> Enabled when control bit BAnEN is written with a 1. An active low signal that is clocked out for the time slots determined by VT/TU selection (VTNn register) for each port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BADD     | 78      | 0     | CMOS<br>4mA | <b>B Add Bus Add Data Present Indicator:</b> This normally active low signal is present when output data to the B Add bus is valid. It identifies the location of all of the VT/TU time slots being selected. When control bit ADDI is 1, the indicator is active high instead of low.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## PORT n LINE INTERFACE (n = 1, 2, 3 or 4)

| Symbol          | Pin No.             | I/O/P | Туре        | Name/Function                                                                                                                                                                                                                                                                                   |

|-----------------|---------------------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCOn<br>(n=1-4) | 14, 111,<br>10, 114 | O(T)  | CMOS<br>4mA | <b>Receive Port n Output Clock:</b> A 1.544 MHz clock<br>output. Data is normally clocked out on rising edges of<br>this clock. When control bit RCKI is 1, data is clocked out<br>on falling edges of this clock. When control bit RnEN is 0,<br>this pin is forced to a high impedance state. |

| RPOn<br>(n=1-4) | 16, 109,<br>12, 112 | O(T)  | CMOS<br>4mA | <b>Receive Port n Data Positive Rail or NRZ:</b> When control bit BYPASn is 0, positive rail data is provided on this lead. When control bit BYPASn is 1, an NRZ signal is provided on this pin. When control bit RnEN is 0, this pin is forced to a high impedance state.                      |

| RNOn<br>(n=1-4) | 15, 110,<br>11, 113 | O(T)  | CMOS<br>4mA | <b>Receive Port n Data Negative Rail:</b> When control bit BYPASn is 0, negative rail data is provided on this pin. When control bit RnEN is 0, or control bit BYPASn is 1, this pin is forced to a high impedance state.                                                                       |

| TCIn<br>(n=1-4) | 19, 106,<br>6, 118  | I     | TTLs        | <b>Transmit Port n Input Clock:</b> A 1.544 MHz clock input.<br>Data is normally clocked in on falling edges of this clock.<br>When control bit TCKI is 1, data is clocked in on the rising<br>edges of this clock.                                                                             |

| TPIn<br>(n=1-4) | 21, 104,<br>8, 116  | I     | TTL         | <b>Transmit Port n Data Positive Rail or NRZ:</b> When control bit BYPASn is 0, positive rail input data is provided on this pin. When control bit BYPASn is 1, an NRZ signal is provided on this pin.                                                                                          |

| Symbol                    | Pin No.            | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                     |

|---------------------------|--------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TNIn/<br>TLOSn<br>(n=1-4) | 20, 105,<br>7, 117 | I     |      | <b>Transmit Port n Data Negative Rail/External Loss Of</b><br><b>Signal:</b> When control bit BYPASn is 0, negative rail input<br>data is provided on this pin. When control bit BYPASn is 1,<br>this pin may be used to input an active low external loss of<br>signal indicator from the line interface device. |

| QUIETn<br>(n=1-4)         | 18, 107,<br>5, 119 | I     |      | Quiet Port n: A high forces the RPOn and RNOn pins to<br>the 0 state for either a rail or NRZ interface, overriding<br>control bit RnEN. A low allows the state of the RPOn and<br>RNOn pins to be controlled by RnEN.                                                                                            |

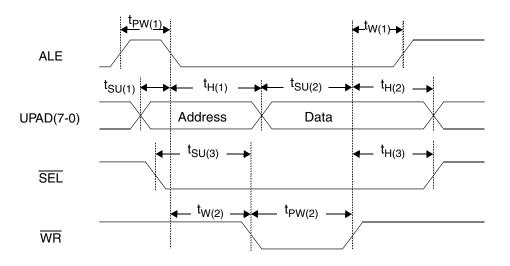

### MICROPROCESSOR BUS INTERFACE

| Symbol    | Pin No.                                         | I/O/P | Туре       | Name/Function                                                                                                                                                                                                                     |

|-----------|-------------------------------------------------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPAD(7-0) | 133, 132,<br>130, 129,<br>128, 126,<br>125, 124 | I/O   | TTL<br>8mA | Address/Data Bus: These pins constitute the time-<br>multiplexed address and data bus for accessing the<br>registers which reside in the memory map of the Quad T1<br>Mapper. UPAD7 is the most significant bit. High is logic 1. |

| SEL       | 146                                             | I     | TTLs       | <b>Select:</b> A low signal generated by the microprocessor for accessing the memory map registers for control, status, and alarm information.                                                                                    |

| RD        | 147                                             | Ι     | TTLs       | <b>Read:</b> A low signal generated by the microprocessor for reading the registers which reside in the memory map. The memory map is selected by placing a low on the select pin.                                                |

| WR        | 148                                             | Ι     | TTLs       | <b>Write:</b> A low signal generated by the microprocessor for writing to the registers which reside in the memory map. The memory map is selected by placing a low on the select pin.                                            |

| ALE       | 149                                             | I     | TTLs       | <b>Address Latch Enable:</b> An active high signal generated by the microprocessor for holding an address stable during a read/write cycle.                                                                                       |

| INT/INT   | 152                                             | O(T)  | TTL<br>8mA | <b>Interrupt:</b> A high or low on this output pin signals an interrupt request to the microprocessor. The polarity of this signal is determined by the state of the INTSH pin.                                                   |

| INTSH     | 150                                             | Ι     | TTL        | <b>Interrupt Sense High Selection:</b> A high on this pin causes the interrupt sense to be high when an interrupt occurs. A low causes the interrupt sense to be low when an interrupt occurs.                                    |

### CONTROLS

| Symbol | Pin No. | I/O/P | Туре | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|---------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST   | 145     | Ι     | TTLs | TranSwitch Test Bit: A high must be placed on this pin.                                                                                                                                                                                                                                                                                                                                                           |

| EXTCK  | 138     | Ι     | CMOS | <b>External Reference Clock:</b> This clock is used for desynchronizer operation and other purposes. The clock frequency must be 48.6360 MHz (+/- 32 ppm over life) and the clock duty cycle must be 50 +/- 10%.                                                                                                                                                                                                  |

| RESET  | 155     | Ι     | TTLs | Hardware Reset: When an active low pulse is applied to<br>this pin for a minimum of 150 nanoseconds after power is<br>applied, this pulse clears all performance counters and<br>alarms, resets the control bits (except those bits that force<br>a high impedance state for the add buses), and initializes<br>the internal FIFOs. The microprocessor must write the<br>control bit states for normal operation. |

| HIGHZ  | 136     | Ι     | TTLs | <b>High Impedance Select:</b> A low forces all output pins to the high impedance state for testing purposes.                                                                                                                                                                                                                                                                                                      |

| ABUST  | 157     | Ι     | TTLs | Add Bus Timing Select: An active low selects the A and<br>B Add bus clock, SPE and C1J1V1 input signals for<br>deriving timing for the A and B Add buses. An active high<br>selects the like-named drop bus for deriving timing (e.g.,<br>A Drop bus for A Add bus). This control pin is disabled<br>when a 1 is written to control bit SBTEN.                                                                    |

## **BOUNDARY SCAN INTERFACE SIGNALS**

| Symbol | Pin No. | I/O/P | Туре       | Name/Function                                                                                                                                                                                                                                                                                             |

|--------|---------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

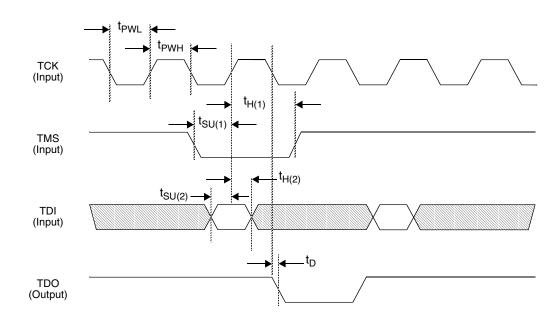

| ТСК    | 39      | I     | TTL        | <b>IEEE 1149.1 Test Port Serial Scan Clock:</b> This signal is used to shift data into TDI on the rising edge, and out of TDO on the falling edge. The maximum clock frequency is 10 MHz.                                                                                                                 |

| TMS    | 36      | I     | TTLp       | <b>IEEE 1149.1 Test Port Mode Select:</b> TMS is sampled on the rising edge of TCLK, and is used to place the Test Access Port controller into various states as defined in IEEE 1149.1. This input has an internal pull-up to VDD.                                                                       |

| TDI    | 38      | I     | TTLp       | <b>IEEE 1149.1 Test Port Serial Scan Data In:</b> Serial test instructions and data are clocked into this pin on the rising edge of TCK. This input has an internal pull-up to VDD.                                                                                                                       |

| TDO    | 37      | 0     | TTL<br>4mA | <b>IEEE 1149.1 Test Port Serial Scan Data Out:</b> Serial test instructions and data are clocked out of this pin on the falling edge of TCLK. When inactive, this 3-state output will be put into its high impedance state.                                                                               |

| TRS    | 35      | I     | TTLp       | <b>IEEE 1149.1 Test Port Reset Pin:</b> This pin will asynchronously reset the Test Access Port (TAP) controller. This lead must be held low, asserted low, or pulsed low (for a minimum duration of 50 ns) to reset the TAP controller upon QT1M power-up.<br>This input has an internal pull-up to VDD. |

# **ABSOLUTE MAXIMUM RATINGS AND ENVIRONMENTAL LIMITATIONS**

| Parameter                         | Symbol          | Min      | Max                   | Unit   | Conditions                     |

|-----------------------------------|-----------------|----------|-----------------------|--------|--------------------------------|

| Supply voltage                    | V <sub>DD</sub> | -0.5     | +6.0                  | V      | Note 1                         |

| DC input voltage                  | V <sub>IN</sub> | -0.5     | V <sub>DD</sub> + 0.5 | V      | Note 1                         |

| Storage temperature range         | Τ <sub>S</sub>  | -55      | 150                   | °C     | Note 1                         |

| Ambient Operating Temperature     | Τ <sub>Α</sub>  | -40      | 85                    | °C     | 0 ft/min linear airflow        |

| Component Temperature x Time      | TI              |          | 270 x 5               | °C x s | Note 1                         |

| Moisture Exposure Level           | ME              | 5        |                       | Level  | per EIA/JEDEC<br>JESD22-A112-A |

| Relative Humidity, non-condensing | RH              |          | 100                   | %      | Note 2                         |

| ESD Classification                | ESD             | absolute | value 2000            | V      | Note 3                         |

Notes:

1. Conditions exceeding the Min or Max values may cause permanent failure. Exposure to conditions near the Min or Max values for extended periods may impair device reliability.

- 2. Pre-assembly storage in non-drypack conditions is not recommended or warranted.

- 3. Test method for ESD per MIL-STD-883D, Method 3015.7.

# THERMAL CHARACTERISTICS

| Parameter                                  | Min | Тур | Max  | Unit | Test Conditions         |

|--------------------------------------------|-----|-----|------|------|-------------------------|

| Thermal resistance:<br>junction to ambient |     |     | 23.0 | °C/W | 0 ft/min linear airflow |

## POWER REQUIREMENTS

| Parameter       | Min  | Тур  | Max  | Unit | Test Conditions    |

|-----------------|------|------|------|------|--------------------|

| V <sub>DD</sub> | 4.75 | 5.0  | 5.25 | V    |                    |

| I <sub>DD</sub> | 160  | 175  | 215  | mA   | STS-1 (see Note 1) |

| P <sub>DD</sub> | 760  | 875  | 1130 | mW   | STS-1 (see Note 1) |

| I <sub>DD</sub> | 212  | 245  | 295  | mA   | STS-3 (see Note 1) |

| P <sub>DD</sub> | 1010 | 1225 | 1550 | mW   | STS-3 (see Note 1) |

| I <sub>DD</sub> | 215  | 250  | 300  | mA   | STM-1 (see Note 1) |

| P <sub>DD</sub> | 1020 | 1250 | 1575 | mW   | STM-1 (see Note 1) |

Note 1: All values assume no more than 15 pF loading.

# **INPUT, OUTPUT AND INPUT/OUTPUT PARAMETERS**

#### INPUT PARAMETERS FOR CMOS

| Parameter             | Min  | Тур | Max  | Unit | Test Conditions              |

|-----------------------|------|-----|------|------|------------------------------|

| V <sub>IH</sub>       | 3.15 |     |      | V    | $4.75 \leq V_{DD} \leq 5.25$ |

| V <sub>IL</sub>       |      |     | 1.65 | V    | $4.75 \le V_{DD} \le 5.25$   |

| Input leakage current |      |     | 10   | μA   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |      | 3.5 |      | pF   |                              |

#### **INPUT PARAMETERS FOR TTL**

| Parameter             | Min | Тур | Max  | Unit | Test Conditions              |

|-----------------------|-----|-----|------|------|------------------------------|

| V <sub>IH</sub>       | 2.0 |     |      | V    | $4.75 \le V_{DD} \le 5.25$   |

| V <sub>IL</sub>       |     |     | 0.8  | V    | $4.75 \leq V_{DD} \leq 5.25$ |

| Input leakage current |     |     | ±1.0 | μA   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |     | 3.5 |      | pF   |                              |

#### **INPUT PARAMETERS FOR TTLs**

| Parameter                                | Min | Тур | Max | Unit | Test Conditions        |

|------------------------------------------|-----|-----|-----|------|------------------------|

| VT- Negative going,<br>threshold voltage |     |     | 0.8 | V    |                        |

| VT+ Positive going,<br>threshold voltage | 2.0 |     |     | V    |                        |

| Input leakage current                    |     |     | 1.0 | μA   | V <sub>DD</sub> = 5.25 |

| Input capacitance                        |     | 3.5 |     | pF   |                        |

| Vhys Hysteresis<br>(VT+ - VT-)           | 0.3 |     | 0.7 | V    |                        |

## INPUT PARAMETERS FOR TTLp, INPUT PADS WITH INTERNAL 25 $\mu\text{A}$ PULL UP \*

| Parameter             | Min | Тур | Max | Unit | Test Conditions              |

|-----------------------|-----|-----|-----|------|------------------------------|

| V <sub>IH</sub>       | 2.0 |     |     | V    | $4.75 \le V_{DD} \le 5.25$   |

| V <sub>IL</sub>       |     |     | 0.8 | V    | $4.75 \leq V_{DD} \leq 5.25$ |

| Input leakage current |     |     | 25  | μA   | V <sub>DD</sub> = 5.25       |

| Input capacitance     |     | 5.1 |     | pF   |                              |

\* Note: TTLp inputs can be disabled for device testing by applying a low to the  $\overline{\text{TEST}}$  pin (pin 145).

### **OUTPUT PARAMETERS FOR CMOS 4mA**

| Parameter                                 | Min                   | Тур | Max   | Unit | Test Conditions                                |

|-------------------------------------------|-----------------------|-----|-------|------|------------------------------------------------|

| V <sub>OH</sub>                           | V <sub>DD</sub> - 0.8 |     |       | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -4.0 |

| V <sub>OL</sub>                           |                       |     | 0.5   | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 4.0  |

| I <sub>OL</sub>                           |                       |     | 4.0   | mA   |                                                |

| I <sub>OH</sub>                           |                       |     | -4.0  | mA   |                                                |

| I <sub>OZ</sub><br>(HIGHZ output current) |                       |     | ±10.0 | μA   |                                                |

### **INPUT/OUTPUT PARAMETERS FOR TTL 8mA**

| Parameter                | Min                   | Тур | Max  | Unit | Test Conditions                                |

|--------------------------|-----------------------|-----|------|------|------------------------------------------------|

| V <sub>IH</sub>          | 2.0                   |     |      | V    | $4.75 \le V_{DD} \le 5.25$                     |

| V <sub>IL</sub>          |                       |     | 0.8  | V    | $4.75 \leq V_{DD} \leq 5.25$                   |

| INPUT LEAKAGE<br>CURRENT |                       |     | ±1.0 | μA   | V <sub>DD</sub> = 5.25                         |

| Input capacitance        |                       | 5.5 |      | pF   |                                                |

| V <sub>OH</sub>          | V <sub>DD</sub> - 0.8 |     |      | V    | V <sub>DD</sub> = 4.75; I <sub>OH</sub> = -8.0 |

| V <sub>OL</sub>          |                       |     | 0.5  | V    | V <sub>DD</sub> = 4.75; I <sub>OL</sub> = 8.0  |

| I <sub>OL</sub>          |                       |     | 8.0  | mA   |                                                |

| I <sub>OH</sub>          |                       |     | -8.0 | mA   |                                                |

## TIMING CHARACTERISTICS

Detailed timing diagrams for the QT1M device are illustrated in Figures 4 through 12, with values of the timing intervals tabulated below each timing diagram. All output times are measured with a maximum 45 pF load capacitance. Timing parameters are measured at voltage levels of  $(V_{IH} + V_{IL})/2$  for input signals or at voltage levels of  $(V_{OH} + V_{OL})/2$  for output signals.

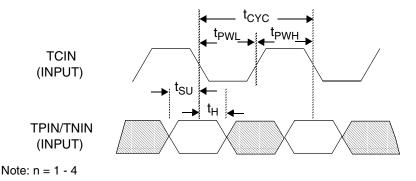

Figure 4. Ports 1, 2, 3 and 4 DS1 Transmit Timing

Note: TCIn is shown for TCLKI = 0, where data are clocked in on falling edges. Data are clocked in on rising edges when TCLKI =1. For NRZ operation, TNIn may be used to input an external loss of signal indication. Otherwise, this pin must be held high.

| Parameter                                           | Symbol           | Min | Тур   | Max | Unit |

|-----------------------------------------------------|------------------|-----|-------|-----|------|

| TCIn Clock period                                   | t <sub>CYC</sub> | 560 | 647.7 |     | ns   |

| TCIn clock low time                                 | t <sub>PWL</sub> | 280 |       |     | ns   |

| TCIn clock high time                                | t <sub>PWH</sub> | 280 |       |     | ns   |

| TPIn/TNIn data set-up time before TCIn $\downarrow$ | t <sub>SU</sub>  | 10  |       |     | ns   |

| TPIn/TNIn data hold time after TCIn $\downarrow$    | t <sub>H</sub>   | 4.0 |       |     | ns   |

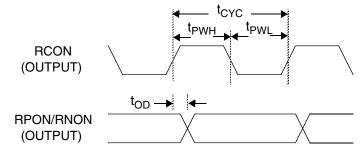

## Figure 5. Ports 1, 2, 3 and 4 DS1 Receive Timing

Note: n = 1 - 4

Note: RCOn is shown for RCLKI=0, where data are clocked out on rising edges. Data are clocked out on falling edges when RCLKI=1.

| Parameter                       | Symbol           | Min | Тур | Max | Unit |

|---------------------------------|------------------|-----|-----|-----|------|

| RCOn clock period               | t <sub>CYC</sub> | 637 |     | 658 | ns   |

| RCOn clock low time             | t <sub>PWL</sub> | 318 |     | 329 | ns   |

| RCOn clock high time            | t <sub>PWH</sub> | 318 |     | 329 | ns   |

| RPOn/RNOn data delay from RCOn↑ | t <sub>OD</sub>  | 0.0 |     | 5.0 | ns   |

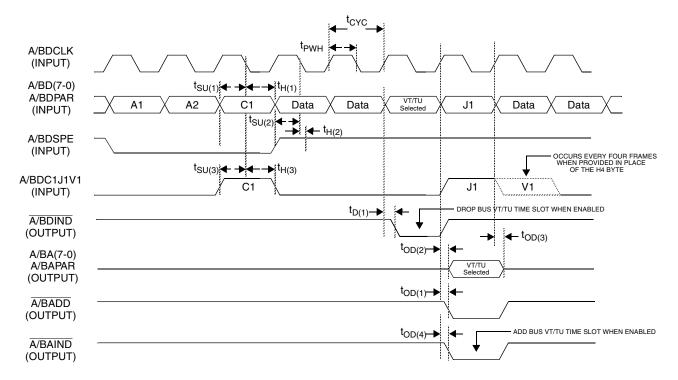

Figure 6. STS-1 A/B Drop and Add Bus Signals, Timing Derived from Drop Bus

Note: For illustration purposes, a single VT/TU (VT number 28) is shown. The V1 pulse may or may not be present. If the V1 pulse is not present, the H4 byte must be provided. The delay of data from D(7-0) to A(7-0) is one byte time. An additional byte time of delay in A(7-0) is provided when control bit ABD is written with a 1.

| Parameter                                                                      | Symbol             | Min | Тур    | Max | Unit |

|--------------------------------------------------------------------------------|--------------------|-----|--------|-----|------|

| DCLK clock period                                                              | t <sub>CYC</sub>   |     | 154.32 |     | ns   |

| DLCK duty cycle t <sub>PWH</sub> /t <sub>CYC</sub>                             |                    | 40  | 50     | 60  | %    |

| D(7-0), DPAR data set up time before DCLK $\downarrow$                         | t <sub>SU(1)</sub> | 4.0 |        |     | ns   |

| D(7-0), DPAR data hold time after DCLK $\downarrow$                            | t <sub>H(1)</sub>  | 5.0 |        |     | ns   |

| DSPE set up time before DCLK $\downarrow$                                      | t <sub>SU(2)</sub> | 4.0 |        |     | ns   |

| DSPE hold time after DCLK $\downarrow$                                         | t <sub>H(2)</sub>  | 5.0 |        |     | ns   |

| DC1J1V1 set up time before DCLK $\downarrow$                                   | t <sub>SU(3)</sub> | 4.0 |        |     | ns   |

| DC1J1V1 hold time after DCLK $\downarrow$                                      | t <sub>H(3)</sub>  | 5.0 |        |     | ns   |

| $\overline{\text{DIND}}$ drop bus indication output delay from DCLK $\uparrow$ | t <sub>D(1)</sub>  | 6.0 |        | 19  | ns   |

| A(7-0), APAR data out (from tristate) delay from DCLK1                         | t <sub>OD(2)</sub> | 6.0 |        | 19  | ns   |

| A(7-0), APAR data to tristate delay from DCLK1                                 | t <sub>OD(3)</sub> | 6.0 |        | 20  | ns   |

| ADD add indicator delayed from DCLK↑                                           | t <sub>OD(1)</sub> | 6.0 |        | 19  | ns   |

| $\overline{AIND}$ add bus indication output delay from $DCLK\uparrow$          | t <sub>OD(4)</sub> | 6.0 |        | 20  | ns   |

<u>Tran</u>Switch<sup>®</sup>

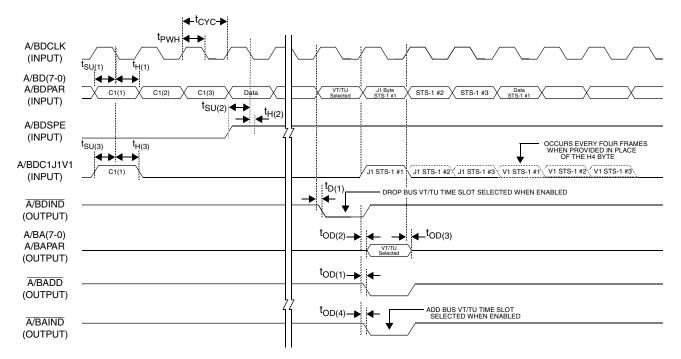

Note: A single VT/TU is shown for illustration purposes. It also shows the VT/TU selection for the drop bus and add bus (number 28 in STS-1 number 3). The format is a AU-3/STS-3. For VC-4 operation, one J1 pulse and one optional V1 pulse are present. The delay of data from D(7-0) to A(7-0) is one byte time. An additional byte time of delay in A(7-0) is provided when control bit ABD is written with a 1.

| Parameter                                                                               | Symbol             | Min | Тур   | Мах | Unit |

|-----------------------------------------------------------------------------------------|--------------------|-----|-------|-----|------|

| DCLK clock period                                                                       | t <sub>CYC</sub>   |     | 51.44 |     | ns   |

| DCLK duty cycle t <sub>PWH</sub> /t <sub>CYC</sub>                                      |                    | 40  | 50    | 60  | %    |

| D(7-0), DPAR data set up time before DCLK $\downarrow$                                  | t <sub>SU(1)</sub> | 10  |       |     | ns   |

| D(7-0), DPAR data hold time after DCLK $\downarrow$                                     | t <sub>H(1)</sub>  | 5.0 |       |     | ns   |

| DSPE set up time before DCLK $\downarrow$                                               | t <sub>SU(2)</sub> | 10  |       |     | ns   |

| DSPE hold time after DCLK $\downarrow$                                                  | t <sub>H(2)</sub>  | 5.0 |       |     | ns   |

| DC1J1V1 set up time before DCLK $\downarrow$                                            | t <sub>SU(3)</sub> | 10  |       |     | ns   |

| DC1J1V1 hold time after DCLK $\downarrow$                                               | t <sub>H(3)</sub>  | 5.0 |       |     | ns   |

| $\overline{	extsf{DIND}}$ drop bus indication output delay from $	extsf{DCLK} \uparrow$ | t <sub>D(1)</sub>  | 6.0 |       | 19  | ns   |

| A(7-0), APAR data out (from tristate) delay from DCLK <sup>↑</sup>                      |                    | 6.0 |       | 20  | ns   |

| A(7-0), APAR data to tristate delay from DCLK $\uparrow$                                | t <sub>OD(3)</sub> | 6.0 |       | 20  | ns   |

| ADD add indicator delayed from DCLK1                                                    | t <sub>OD(1)</sub> | 6.0 |       | 19  | ns   |

| AIND add bus indication output delay from DCLK                                          | t <sub>OD(4)</sub> | 6.0 |       | 20  | ns   |

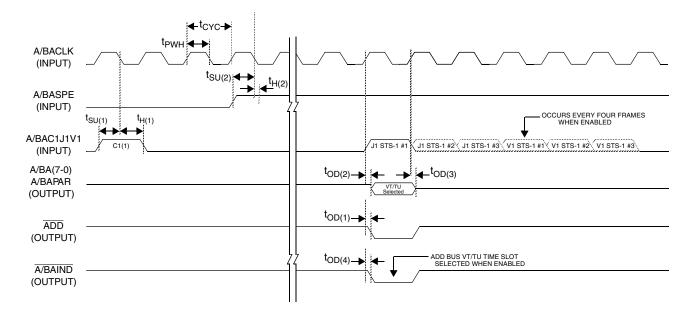

Figure 8. STS-1 A/B Add Bus Signals, Timing Derived from Add Bus

Note: For illustration purposes, a single VT/TU is shown. The location of this VT/TU corresponds to VT/TU number 28. An additional byte time of delay in A(7-0) is provided when control bit ABD is written with a 1.

| Parameter                                                        | Symbol             | Min | Тур    | Max | Unit |

|------------------------------------------------------------------|--------------------|-----|--------|-----|------|

| ACLK clock period                                                | t <sub>CYC</sub>   |     | 154.32 |     | ns   |

| ACLK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub>              |                    | 40  | 50     | 60  | %    |

| AC1J1V1 set up time before ACLK $\downarrow$                     | t <sub>SU(1)</sub> | 10  |        |     | ns   |

| AC1J1V1 hold time after ACLK $\downarrow$                        | t <sub>H(1)</sub>  | 5.0 |        |     | ns   |

| ASPE set up time before ACLK $\downarrow$                        | t <sub>SU(2)</sub> | 10  |        |     | ns   |

| ASPE hold time after ACLK $\downarrow$                           | t <sub>H(2)</sub>  | 5.0 |        |     | ns   |

| A(7-0), APAR data out (from tristate) delay from ACLK $\uparrow$ | t <sub>OD(2)</sub> | 6.0 |        | 19  | ns   |

| A(7-0), APAR data to tristate delay from ACLK $\uparrow$         | t <sub>OD(3)</sub> | 6.0 |        | 20  | ns   |

| $\overline{ADD}$ add indicator delayed from ACLK $\uparrow$      | t <sub>OD(1)</sub> | 6.0 |        | 19  | ns   |

| AIND add bus indication output delay from ACLK                   | t <sub>OD(4)</sub> | 6.0 |        | 20  | ns   |

Figure 9. STS-3/STM-1 A/B Add Bus Signals, Timing Derived from Add Bus

<u>Switch</u>

<u>Trar</u>

Note: A single VT/TU is shown for illustration purposes. It also shows the VT/TU selection for the drop bus and add bus (number 28 in STS-1 number 3). The format is a AU-3/STS-3. For VC-4 operation, one J1 pulse and one optional V1 pulse are present. An additional byte time of delay in A(7-0) is provided when control bit ABD is written with a 1.

| Parameter                                                              | Symbol             | Min | Тур   | Max | Unit |

|------------------------------------------------------------------------|--------------------|-----|-------|-----|------|

| ACLK clock period                                                      | t <sub>CYC</sub>   |     | 51.44 |     | ns   |

| ACLK duty cycle, t <sub>PWH</sub> /t <sub>CYC</sub>                    |                    | 40  | 50    | 60  | %    |

| AC1J1V1 set up time before ACLK $\downarrow$                           | t <sub>SU(1)</sub> | 10  |       |     | ns   |

| AC1J1V1 hold time after ACLK $\downarrow$                              | t <sub>H(1)</sub>  | 5.0 |       |     | ns   |

| ASPE set up time before ACLK $\downarrow$                              | t <sub>SU(2)</sub> | 10  |       |     | ns   |