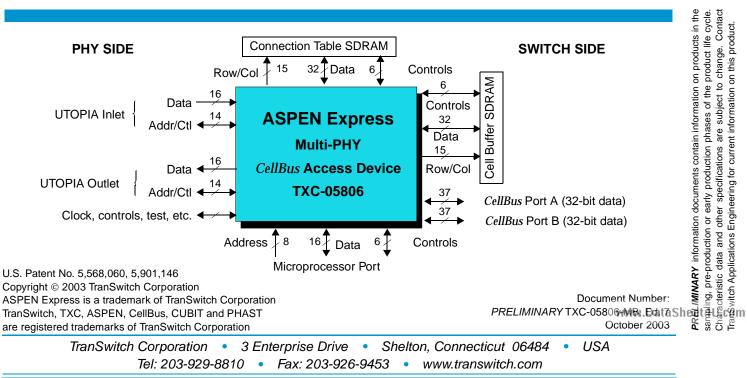

# **ASPEN Express<sup>™</sup> Device** Multi-PHY CellBus<sup>®</sup> Access Device **TXC-05806**

# DATA SHEET

# FEATURES

- 622 Mbit/s bi-directional throughput

- UTOPIA Level 1/2 interface (8/16-bit) with support for 64/124 ports at 50 MHz

- OAM Fault Management per ITU-T I.610

- UPC/NPC policing on ingress compliant with TM4.1

- Early Packet Discard (EPD) and Partial Packet Discard (PPD) in inlet and outlet direction

- Dual CellBus interfaces for load sharing or redundancy

- Inlet-side address translation and routing header insertion

- Header translation for egress cells

- 512k cell shared SDRAM buffer memory

- Support for spatial multicast for 512 sessions with header translation

- Support for over-reservation of GFR, UBR, and **VBR** traffic

- Minimum Cell Rate (MCR) guarantees for egress queues

- CellBus traffic monitor mode including APS support and congestion control

- Cell insertion and extraction via microprocessor interface port

- Microprocessor control port, selectable for Intel, Motorola 360 or Motorola MPC 860 interfaces

- Test Access Port for IEEE 1149.1 boundary scan

- +3.3 V I/O and +1.8 V core power supplies

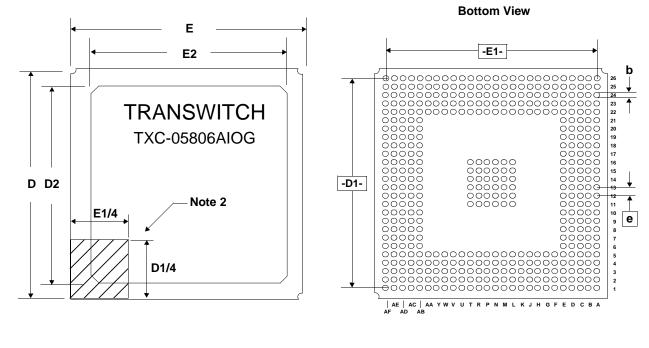

- 456-lead Plastic Ball Grid Array (PBGA) package, 27 mm x 27 mm

# DESCRIPTION

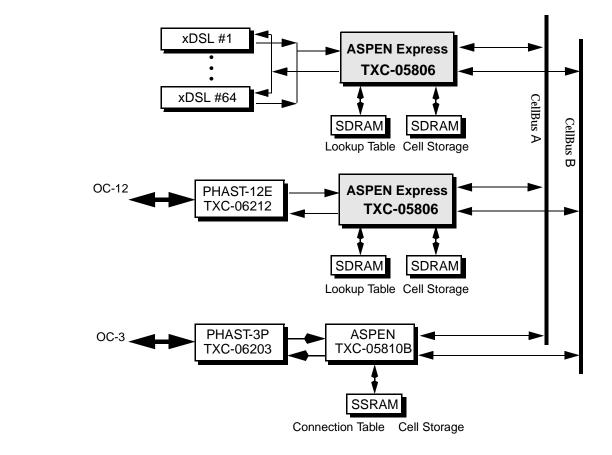

The ASPEN® Express device is a single-chip solution for implementing cost-effective ATM multiplexing and switching systems, based on the CellBus architecture. Such systems are constructed from a number of CUBIT®-3, CUBIT-Pro, CUBIT-622, or ASPEN devices, all interconnected by a 37-line common bus, the CellBus. The ASPEN Express provides state of the art traffic management to the CellBus family of ATM switching devices. ASPEN Express supports unicast and multicast transfers, and has all necessary functions for implementing a switch: cell address translation, cell routing, policing and inlet/outlet cell queuing. The ASPEN Express offers dual CellBus interfaces to support load sharing or redundancy.

The ASPEN Express is designed to interface directly with UTOPIA Level 1/2, 8/16-bit compliant devices, such as the PHAST®-3P (TXC-06203) and the PHAST-12E (TXC-06212) at up to 50 MHz. On the switch side, the ASPEN Express interfaces directly with CellBus devices such as the CUBIT-Pro (TXC-05802B), CUBIT-3 (TXC-05804), CUBIT-622 (TXC-05805) and ASPEN (TXC-05810B).

# APPLICATIONS

- ATM Access Multiplexers

- DSLAM Applications

- Remote Access Equipment

- ATM LAN Switch

- Frame Relay Switch

product

current information on this

Engineering for

itch Applications

ASPEN Express TXC-05806

## **DATA SHEET**

# TABLE OF CONTENTS

| Section P                                              | age |

|--------------------------------------------------------|-----|

| List of Figures                                        | 3   |

| Block Diagram                                          | 4   |

| Block Diagram Description                              | 5   |

| Operation                                              |     |

| Introduction To CellBus Architecture                   | 16  |

| CellBus Operation                                      | 16  |

| CellBus Cell Routing                                   |     |

| CellBus Status Signals and Monitoring                  | 20  |

| The CellBus Interface                                  |     |

| Operation with Internal GTL+ Transceivers              |     |

| Clock Source                                           |     |

| CellBus Bus Arbiter Selection                          | 22  |

| Multicast Session Memory                               |     |

| Loopback Cell Transmit, Receive, and Relay             |     |

| Boundary Scan                                          |     |

| Lead Diagram                                           |     |

| Lead Descriptions                                      |     |

| Absolute Maximum Ratings and Environmental Limitations |     |

| Thermal Characteristics                                |     |

| Power Requirements                                     |     |

| Input, Output and Input/Output Parameters              |     |

| Timing Characteristics                                 |     |

| Memory Map                                             |     |

| Memory Map descriptions                                |     |

| Package Information                                    |     |

| Ordering Information                                   |     |

| Related Products                                       |     |

| Reference Documents                                    |     |

| Application Example                                    |     |

| Standards Documentation Sources                        |     |

| List of Data Sheet Changes                             | 89  |

Please note that TranSwitch provides documentation for all of its products. Current editions of many documents are available from the Products page of the TranSwitch Web site at www.transwitch.com. Customers who are using a TranSwitch Product, or planning to do so, should register with the TranSwitch Marketing Department to receive relevant updated and supplemental documentation as it is issued. They should also contact the Applications Engineering Department to ensure that they are provided with the latest available information about the product, especially before undertaking development of new designs incorporating the product.

DataSheet4U.com

# ASPEN Express TXC-05806

# **LIST OF FIGURES**

#### Page

| Figure |                                                                                        | Page |

|--------|----------------------------------------------------------------------------------------|------|

| 1      | ASPEN Express (TXC-05806) Block Diagram                                                | 4    |

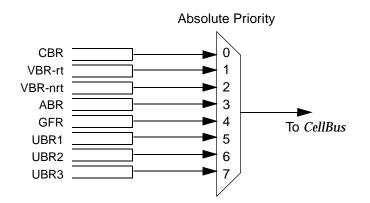

| 2      | ASPEN Express Ingress External Queueing Structure per CellBus                          |      |

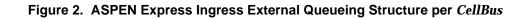

| 3      | ASPEN Express Egress External Queuing Structure                                        |      |

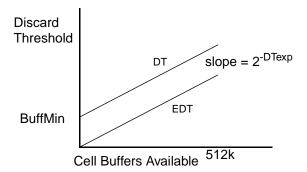

| 4      | Graphic Representation of DT and EDT thresholds vs. Free Cell Buffers Available        |      |

| 5      | Microprocessor Address Connection Example                                              |      |

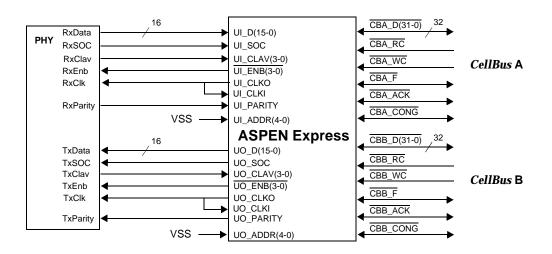

| 6      | ASPEN Express Device in ATM Layer, Single-PHY Mode Configuration                       |      |

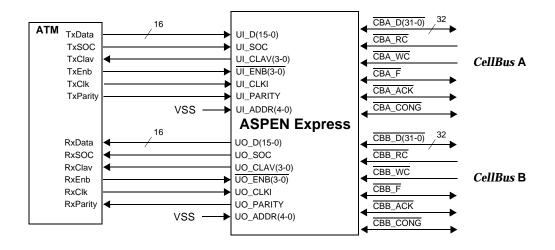

| 7      | ASPEN Express Device in PHY Layer, Single-PHY Mode Configuration                       |      |

| 8      | ASPEN Express Device in ATM Layer, Multi-PHY Mode Configuration                        |      |

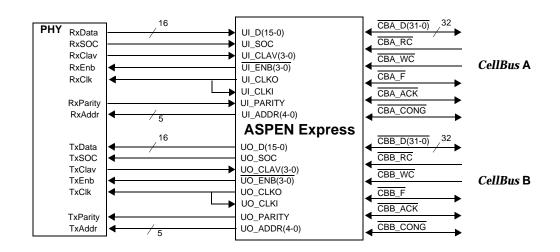

| 9      | ASPEN Express Device in PHY Layer, Multi-PHY Mode Configuration                        | 12   |

| 10     | UTOPIA Clock Control                                                                   | 13   |

| 11     | Data Flow for CellBus Bridging (Note: Data can also flow from CellBus B to CellBus A)  |      |

| 12     | ASPEN Express SDRAM Configuration                                                      |      |

| 13     | CellBus Structure                                                                      | 16   |

| 14     | CellBus Frame Format                                                                   | 17   |

| 15     | CellBus 16/32-User Modes - Frame Formats                                               | 18   |

| 16     | CellBus Routing Header Formats                                                         | 19   |

| 17     | External Circuit Requirements for GTL+ Transceivers                                    |      |

| 18     | Loading the Loopback Registers for ASPEN Express Y                                     | 23   |

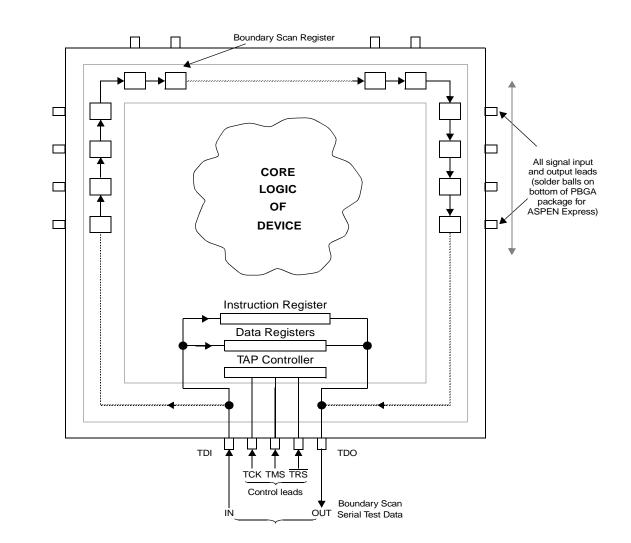

| 19     | Boundary Scan Top-Level Block Diagram                                                  | 26   |

| 20     | ASPEN Express TXC-05806 Lead Diagram                                                   |      |

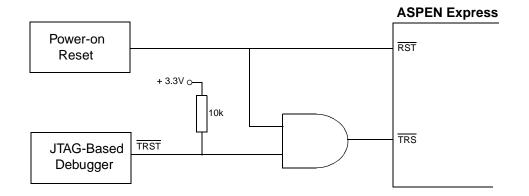

| 21     | Recommended Reset Circuit                                                              |      |

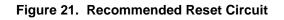

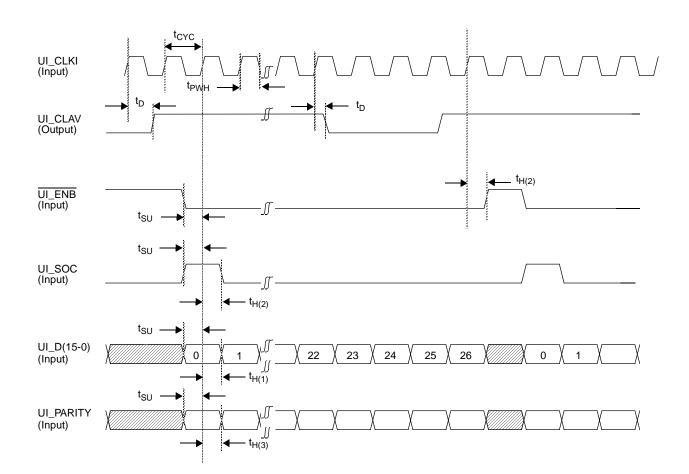

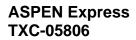

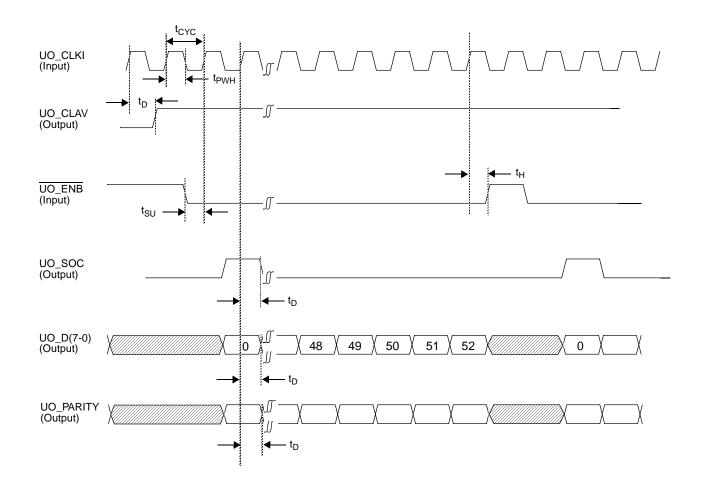

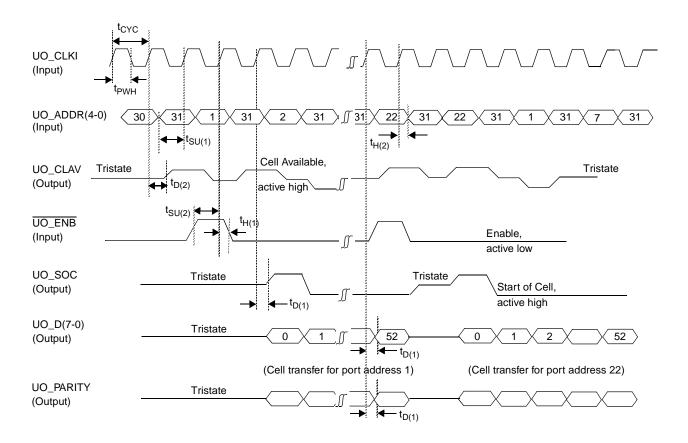

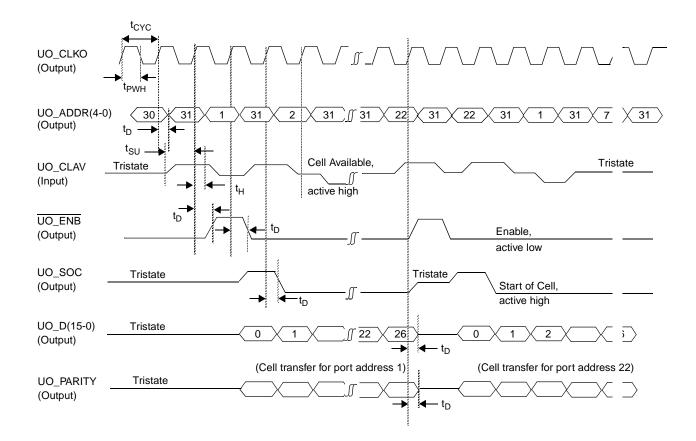

| 22     | Timing of Receive Interface for UTOPIA Mode, Single-PHY (PHY Layer Emulation, 8-bit)   |      |

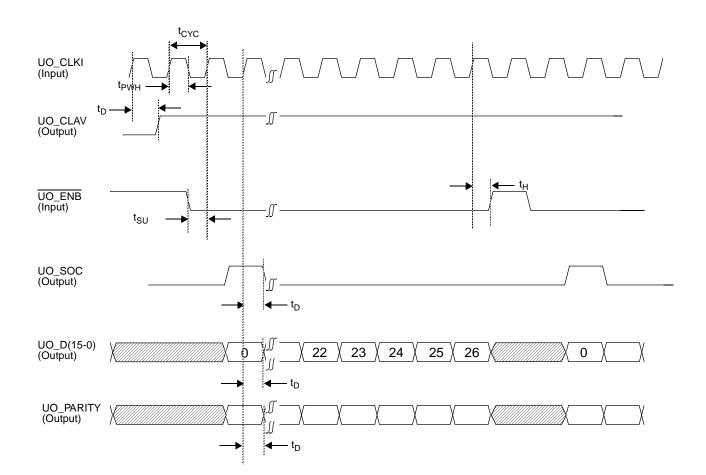

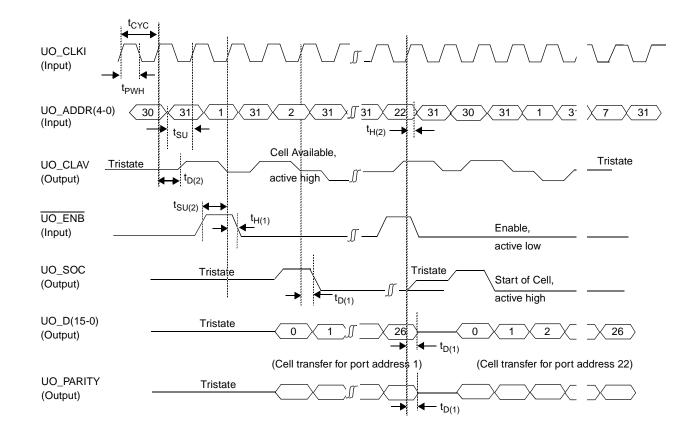

| 23     | Timing of Receive Interface for UTOPIA Mode, Single-PHY (PHY Layer Emulation, 16-bit)  |      |

| 24     | Timing of Receive Interface for UTOPIA Mode, Single-PHY (ATM Layer Emulation, 8-bit)   |      |

| 25     | Timing of Receive Interface for UTOPIA Mode, Single-PHY (ATM Layer Emulation, 16-bit)  |      |

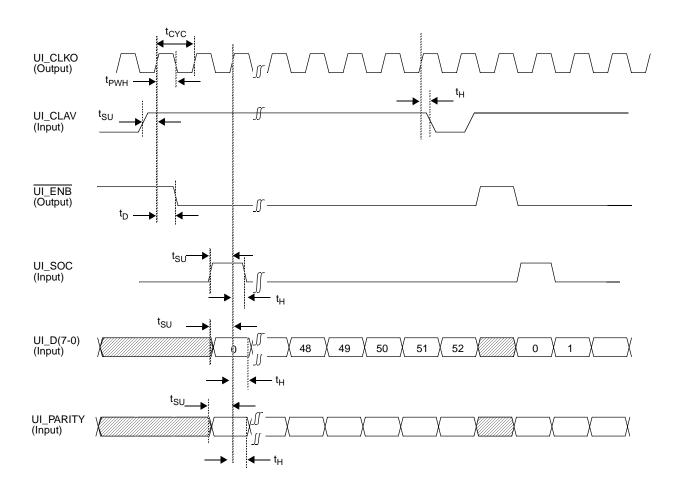

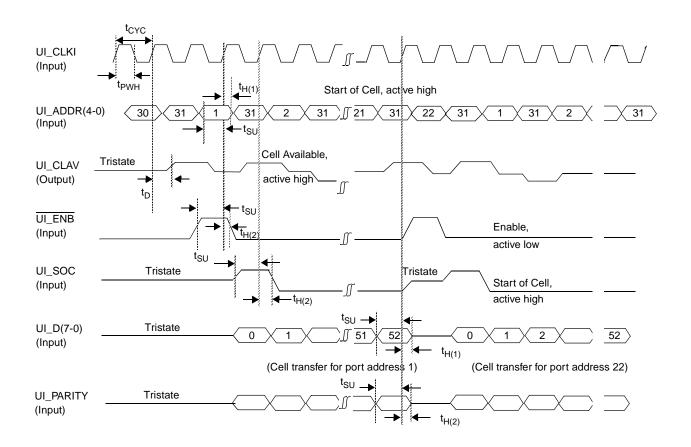

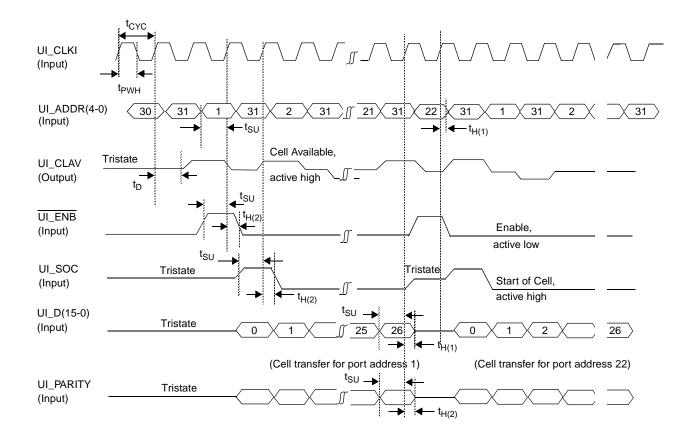

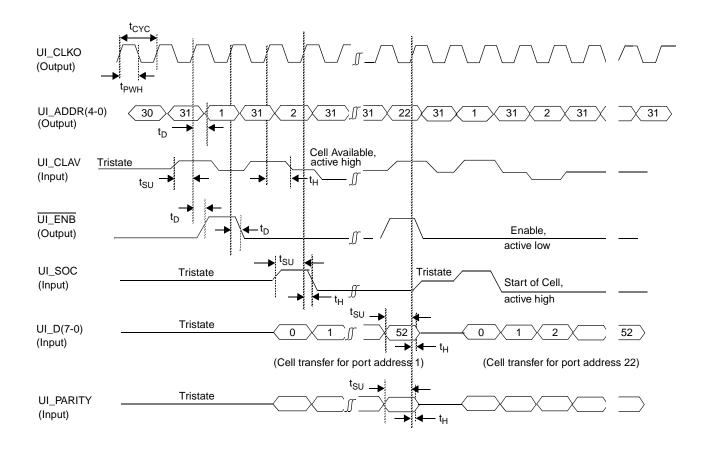

| 26     | Timing of Receive Interface for UTOPIA Mode, Multi-PHY (PHY Layer Emulation, 8-bit)    |      |

| 27     | Timing of Receive Interface for UTOPIA Mode, Multi-PHY (PHY Layer Emulation, 16-bit)   |      |

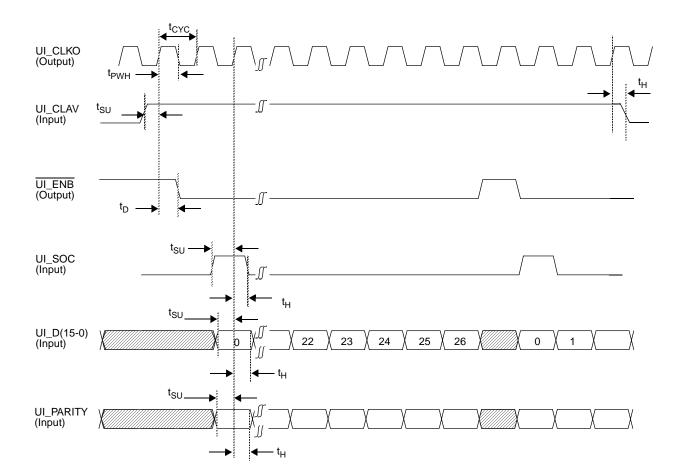

| 28     | Timing of Receive Interface for UTOPIA Mode, Multi-PHY (ATM Laver Emulation, 8-bit)    | 55   |

| 29     | Timing of Receive Interface for UTOPIA Mode, Multi-PHY (ATM Laver Emulation, 16-bit)   | 56   |

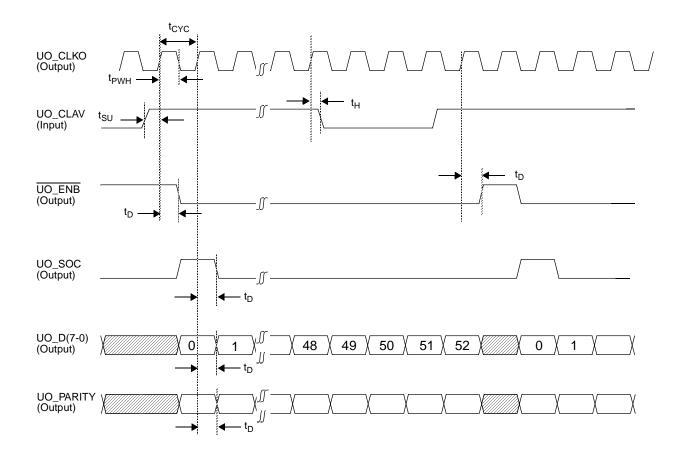

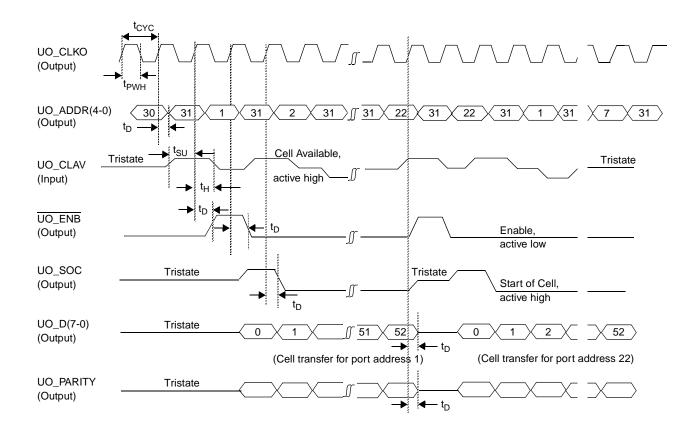

| 30     | Timing of Transmit Interface for UTOPIA Mode, Single-PHY (PHY Layer Emulation, 8-bit)  | 57   |

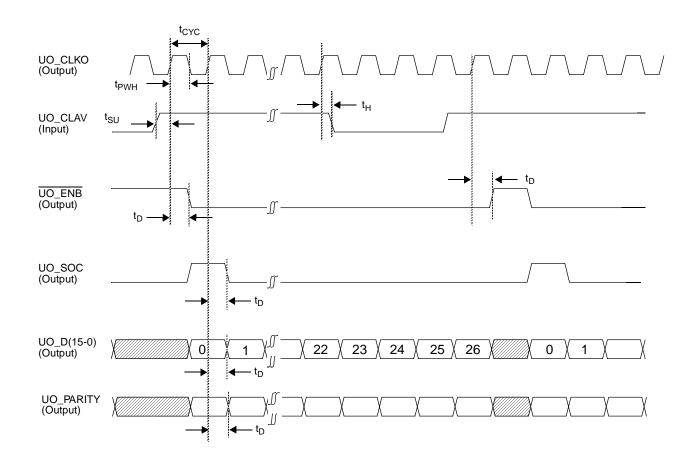

| 31     | Timing of Transmit Interface for UTOPIA Mode, Single-PHY (PHY Layer Emulation, 16-bit) | 58   |

| 32     | Timing of Transmit Interface for UTOPIA Mode, Single-PHY (ATM Layer Emulation, 8-bit)  | 59   |

| 33     | Timing of Transmit Interface for UTOPIA Mode, Single-PHY (ATM Layer Emulation, 16-bit) | 60   |

| 34     | Timing of Transmit Interface for UTOPIA Mode, Multi-PHY (PHY Layer Emulation, 8-bit)   | 61   |

| 35     | Timing of Transmit Interface for UTOPIA Mode, Multi-PHY (PHY Layer Emulation, 16-bit)  | 62   |

| 36     | Timing of Transmit Interface for UTOPIA Mode, Multi-PHY (ATM Layer Emulation, 8-bit)   | 63   |

| 37     | Timing of Transmit Interface for UTOPIA Mode, Multi-PHY (ATM Layer Emulation, 16-bit)  |      |

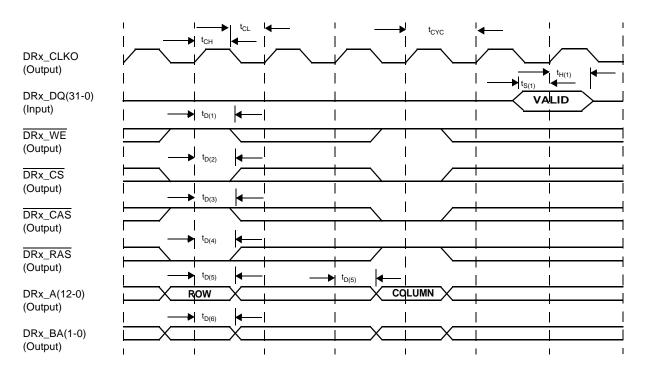

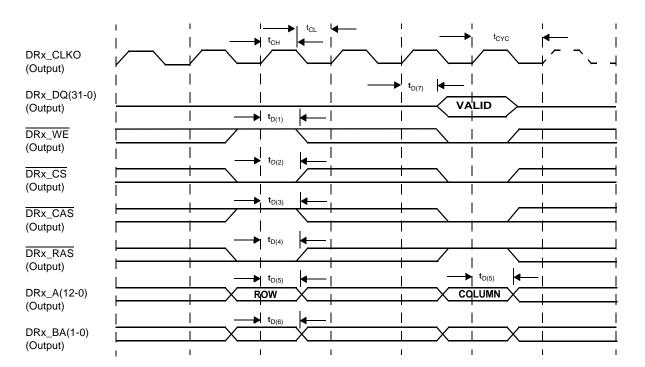

| 38     | SDRAM Read Timing                                                                      |      |

| 39     | SDRAM Write Timing                                                                     | 66   |

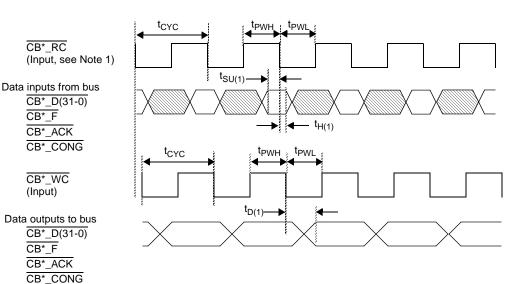

| 40     | Timing of Signals for CellBus Interfaces                                               |      |

| 41     | Timing of CellBus Frame Position                                                       | 68   |

| 42     | MPC860 Single Read Cycle Timing, UPMODE=10                                             | 69   |

| 43     | MPC860 Single Write Cycle Timing, UPMODE=10                                            |      |

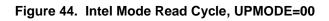

| 44     | Intel Mode Read Cycle, UPMODE=00                                                       | 71   |

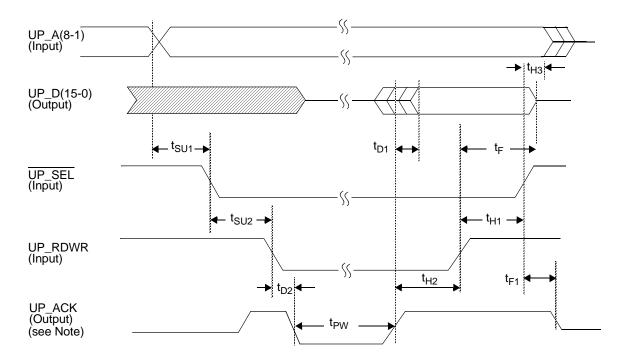

| 45     | Intel Mode Write Cycle, UPMODE=00                                                      | 72   |

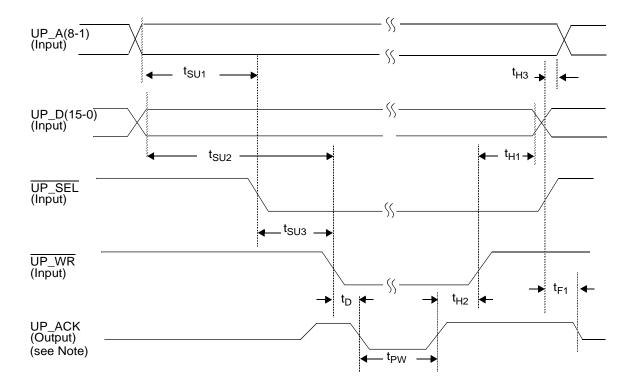

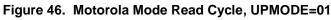

| 46     | Motorola Mode Read Cycle, UPMODE=01                                                    |      |

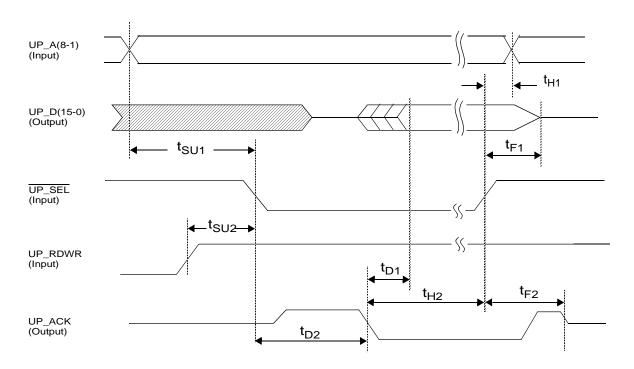

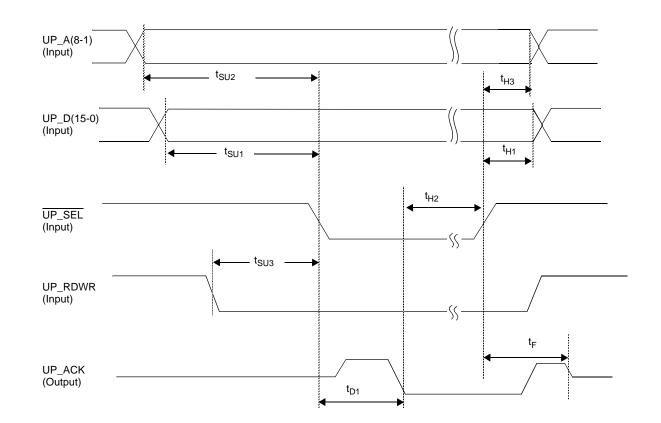

| 47     | Motorola Mode Write Cycle, UPMODE=01                                                   |      |

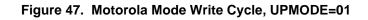

| 48     | Boundary Scan Timing Diagram                                                           |      |

| 49     | ASPEN Express TXC-05806 456-Lead Plastic Ball Grid Array Package                       |      |

| 50     | ASPEN Express TXC-05806 and Related Product Applications                               | 86   |

www.DataSheet4U.com

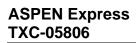

# **BLOCK DIAGRAM**

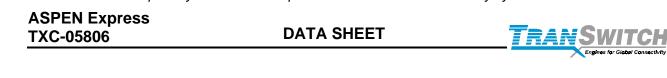

Figure 1. ASPEN Express (TXC-05806) Block Diagram

# **BLOCK DIAGRAM DESCRIPTION**

#### Cell Inlet to CellBus

On the cell inlet side of the ASPEN Express is circuitry associated with accepting cells from the line and passing them to the *CellBus* with an appropriate header. The Cell Inlet Port block is selectable to be compatible with either the ATM Forum UTOPIA (Universal Test and Operations Physical Interface for ATM) Level 1 or 2 interface. Incoming cells may be translated using the ASPEN Express. Translation and routing header tables to support this function are contained in an external SDRAM (up to 64k connections). There is support for VPI, or VPI/VCI address translation. Lookup is supported for up to 600 VPIs within the full 4096 VPI range. Each port can be configured independently for 2 consecutive ranges of VPIs. Different PHYs can use overlapping ranges of VPI. Each VPI is then configured to support 2 ranges of VCI. The total number of VCIs supported cannot exceed 64k. Different VPIs can use overlapping ranges of VCI.

Each VCI can be configured for UPC. Full TM4.1 support for policing is provided utilizing two 32-bit GCRA engines implementing the Virtual Scheduling Algorithm with a 20 ns resolution clock.

Ingress and egress queues share a 512k cell buffer in SDRAM and utilize a decoupling FIFO for each *CellBus*. The ingress queuing consists of 8 priority queues for each *CellBus*. Queue limits are enforced for each queue via dynamic buffer allocation.

A 6-cell FIFO receives all cells from the UTOPIA bus. The ASPEN Express can process a full 622 Mbit/s of ingress traffic while also processing 622 Mbit/s of egress traffic from the *CellBus*. Higher bandwidth can be processed at the ingress if a corresponding lower bandwidth is required from the egress (asymmetric application).

When the ASPEN Express has a cell pending in one of its ingress queues, it makes a *CellBus* access request, and upon receiving a grant will send the cell to the *CellBus* in standard *CellBus* format. In addition to data cells, the ASPEN Express can also send control cells from the local microprocessor to the bus. Diagnostic loopback cells received from the *CellBus* may be looped back to the *CellBus* to a designated *CellBus* device/queue. Both the control cells and the loopback cells have inlet queues consisting of FIFOs with a depth of two cells and one cell, respectively.

Local switching is supported so that cells received from the UTOPIA can be directly queued to egress queues and routed back to another (or the same) UTOPIA address.

A count is kept for total numbers of invalid cells received. An invalid cell is one in which the VPI or VCI is out of range of the configured lookup table. Registers hold Port, VPI and VCI of the last invalid cell received. Misrouted cells are defined as connections whose active bit has not been set; a count is kept for all misrouted cells. Per VC statistics include cell count, non-conforming cells for GCRA1, and non-conforming cells for GCRA2 as well as buffer discard counts for each connection and each queue.

Early Packet Discard (EPD) and Partial Packet Discard (PPD) are ATM cell discard techniques which maximize the transmission of whole packets (goodput) for AAL5 adapted packet traffic. These techniques minimize transmission of partial packets since these represent wasted bandwidth; any cells dropped from a packet require the retransmission of the entire packet by the network. Both EPD and PPD are supported (per VCC) for ingress and egress. The ingress connection table will hold the packet discard state for ingress connections (VCCs). A separate packet discard state machine will keep track of packet discard states for each VCC in the connection table. If a cell is discarded (either due to UPC/NPC or queue full) and packet discard is enabled, the connection drops all remaining cells of the packet. A separate EPD queue threshold triggers EPD for all new packets received while the queue threshold exceeds this level.

Segment or end-end OAM cells for selected VCCs (F5) or VPCs (F4) may be selectively routed to the OAM processor. The OAM processor handles all OAM-FM functions per ITU-T I.610 including AIS, RDI, Continuity Check, and Loopback. All loopback cells can be routed to the host processor. Management flows are identified by assigning them to the host extraction queue; all management cells are extracted to the host.

www.DataSheet4U.com

#### CellBus to Cell Outlet

et4

On the cell outlet side, cells received from the *CellBus* are screened for their *CellBus* address and, if they are identified for this device, are routed into a 64-cell FIFO structure in the Outlet Queue block. The *CellBus* address is set by Unit Address leads UA(4-0) or configured by the host. Cells arriving from the *CellBus* are tagged as unicast or multicast in the *CellBus* Routing Header (CBRH). If tagged as a multicast cell, the Tandem Routing Header (TRH) or *CellBus* Routing Header (CBRH) will contain a multicast session ID. There are up to 511 different multicast sessions and 1 broadcast session shared by all devices on both *CellBuses*. Each ASPEN Express may be programmed to accept cells associated with these multicast sessions in the Multicast Session Table (MST). Each entry in the MST contains a list of destination ports for that device to which a cell will be forwarded (max. all 64 ports). If all entries in the MST for a given session are '0', then all cells for this session are not accepted by the screen. Control cells are routed to a separate queue in external memory and are sent to the host processor. *CellBus* loopback cells arriving from the bus are routed to a 1-cell outlet loopback queue and then looped back to the *CellBus* with a new *CellBus* Routing Header/Tandem Routing Header.

All multicast cells are queued in 1 of 3 priority queues per port - VBR, GFR or UBR. These multicast queues are given higher priority than their unicast equivalents as shown in Figure 3. The multicast engine replicates the buffer pointer to these queues and does not waste buffer space replicating the cell. Each multicast session may be configured to translate each leaf to a unique cell header for spatial multicast.

The ASPEN Express can receive 622 Mbit/s of traffic from the sum of both *CellBuses*, provided the ingress traffic from the UTOPIA is 622 Mbit/s or less. For *CellBus* bridging or asymmetric applications, the bandwidth not used by the UTOPIA interface can be used to handle additional *CellBus* traffic.

If the 64-cell FIFO for either *CellBus* becomes congested, a backpressure mechanism may be engaged across that *CellBus* to alleviate the congestion. There are 3 congestion control mechanisms. The first is that a *CellBus* master can withhold granting the bus on the bus cycle following the congestion of its 64-cell FIFO. The second congestion control mechanism triggers the scheduler to release only high priority traffic (CBR, VBR-rt) for 4 *CellBus* frames. (Note: This will not affect the cells already dequeued by the scheduler to the 1-cell outlet FIFO). This mechanism is triggered by the assertion of CONG on the *CellBus*.

The third mechanism is triggered by the detection of CONG for 2 consecutive *CellBus* frames. This mechanism will also force the arbiter to not grant the next *CellBus* frame following CONG. Each of these mechanisms may be enabled under API control.

All cells are stored in the shared 512k cell buffer SDRAM and queued in one of 8 service categories associated with the destination port. Multicast cells share 3 service class priority queues (VBR, GFR and UBR) per port. Each multicast queue has a higher priority than its corresponding unicast queue. Available buffer space is decreased by 8 cells for each multicast cell stored but it is only stored once, regardless of the number of replications specified. Therefore, appropriate consideration must be given to provisioning unicast and multicast queues.

The ASPEN Express supports queue over-reservation to accommodate traffic burstiness inherent in video and internet traffic. Using this technique, the sum of all queue limits in a service category may exceed the buffer allocation for the entire class. Cells may be discarded if either the individual queue limit is exceeded or the service category buffer limit is exceeded.

At the cell outlet, cells may optionally be translated for either VPC or VCC header translation. Provisions are made for insertion of an Explicit Forward Congestion Indication (EFCI) bit when queues exceed a configurable dynamic threshold. Statistics are kept for discarded cells (per queue, per VC, and per service category) and received cells are counted per VC.

Unicast cells from the *CellBus* are identified by a 16-bit connection ID (CID) contained in the TRH which is unique for each connection. Both VPI and VCI are translated for a VCC. All VCCs within a VPC share a common connection ID. If header translation is configured, only the VPI will be translated (for a VPC) and the VCI passed through. Multicast cells are identified either by the multicast session contained in the TRH or in the CBRH. The device can be configured for either method of multicast identification in order to allow backward compatibility with older *CellBus* devices in existing ASPEN and/or CUBIT systems. All leaves of a multicast session may be uniquely translated for VPI/VCI.

Control cells may be extracted to the host or the OAM processor by assigning the appropriate QID (0x213) for cell extraction to the connection via the connection table.

Cells from any connection may be bridged from one *CellBus* to the other by configuring an Ingress queue for the appropriate *CellBus* destination in the Egress connection table.

Additionally, if enabled the ASPEN Express may be placed in a *CellBus* monitoring mode. In this mode, the ASPEN Express accepts all traffic coming in from the *CellBus* regardless of the *CellBus* ID specified in the CBRH. The cells are enqueued based on *CellBus* ID, *CellBus* IDs 0-15 are enqueued in service class 0 queues for ports 0-15, *CellBus* IDs 16-31 are enqueued in service class 1 queues for ports 0-15. Additionally, all multicast traffic, broadcast traffic and errored cell information are sent to queue 2 ports 16, 17 and 18 respectively.

In support of APS applications, the *CellBus* ID may be configured differently for receive and transmit directions so that 2 devices may have the same *CellBus* receive addresses but different *CellBus* transmit addresses. When this mode is set (UA\_FLIP), the *CellBus* receive ID is set to both UA(4-1), UA(0) and UA(4-1), UA(0). The *CellBus* transmit address remains = UA(4-0). These addresses may be reconfigured by the host processor through an API command.

In support of 32-user mode, the *CellBus* ID may be configured to use 2 IDs for transmit (Dual Tx Mode) so that it can utilize both phases of the 32-user *CellBus* frame and achieve full bandwidth support in 32-user mode. In this case a second *CellBus* transmit address = UA + 16 is used.

#### **Starvation Prevention**

A starvation prevention mechanism exists for VBR-nrt, ABR, GFR and all UBR egress queues including GFR multicast and UBR multicast. The mechanism guarantees that each queue will receive at least as much bandwidth as is specified for that service category. In addition to unicast queues, GFR and UBR multicast each have their own specified MCR rates. Each queue not meeting its specified minimum cell rate is serviced at a constant inter-cell time interval. If all minimum rates specified add up to 100% of the available bandwidth then the effect is a weighted priority scheduling of the queues instead of the default strict priority. The mechanism is work conserving so that if any queue does not utilize its minimum rate, that bandwidth is available to other queues in strict priority.

#### **Dynamic Buffer Allocation**

All (ingress and egress) queues share a common 512k cell buffer. Each service category queue for ingress may specify an Early Discard Threshold (EDT) and a Discard Threshold (DT). The parameter specified for EDT is DTexp which is the square root of the reciprocal of the share of free cell buffers available. For example, if DTexp = 4 then EDT = 1/16 x number of free cell buffers. All cells entering a queue whose EDT threshold is exceeded are subject to discard if they are CLP1 cells and the connection is configured as CLP significant or EPD discard if the connection is configured as AAL5 and the cell represents the beginning of a packet. The Discard Threshold = EDT + BuffMin, where BuffMin is a constant parameter representing a minimum buffer reservation for that queue. Figure 4 shows a graphic representation of the dynamic thresholds as a function of available buffer space. Cells entering the queue when the DT is exceeded are subject to discard unless the connection is configured as AAL5 and the cell represents the end of packet.

Figure 4. Graphic Representation of DT and EDT thresholds vs. Free Cell Buffers Available

Egress queues utilize the same discard thresholds for each service category. The discard thresholds apply to queues for all ports of that service category. Port modifier parameters may be specified to increase or decrease the discard thresholds for all queues of that port relative to their service category discard thresholds. A second set of discard thresholds are also available for the sum of all queues for each service category. This is a constant discard threshold (SCDT) and an early discard threshold (SCEDT). If a cell enters a service category queue while the SCEDT is exceeded then that cell will be subject to CLP1 discard and EPD just as if its own queue EDT was exceeded. Likewise, if a cell enters a service category queue while the SCDT is exceeded for that service category, then the cell will be discarded unless it is the end of packet for an AAL5 designated flow.

| ASPEN         | Express |

|---------------|---------|

| <b>TXC-05</b> | 806     |

#### DATA SHEET

#### **DEVICE INTERFACES**

#### **Microprocessor Interface**

|                |             | ASPEN Express |

|----------------|-------------|---------------|

| Microprocessor |             |               |

| A8             | <b>&gt;</b> | UP_A(8)       |

| A7             | <b>&gt;</b> | UP_A(7)       |

| A6             |             | UP_A(6)       |

| A5             |             | UP_A(5)       |

| A4             | <b>&gt;</b> | UP_A(4)       |

| A3             | <b>&gt;</b> | UP_A(3)       |

| A2             | <b>`</b>    | UP_A(2)       |

| A1             | <b>&gt;</b> | UP_A(1)       |

| A0             | NC          | ( )           |

| -              |             |               |

|                |             |               |

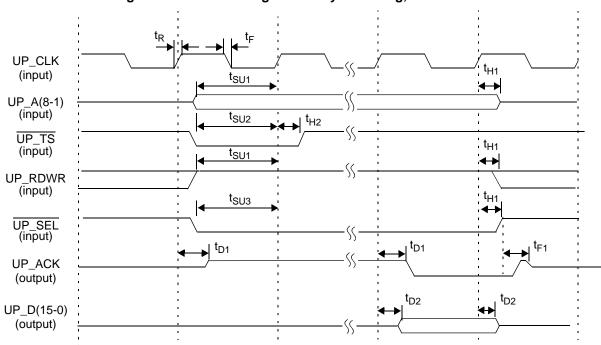

#### Figure 5. Microprocessor Address Connection Example

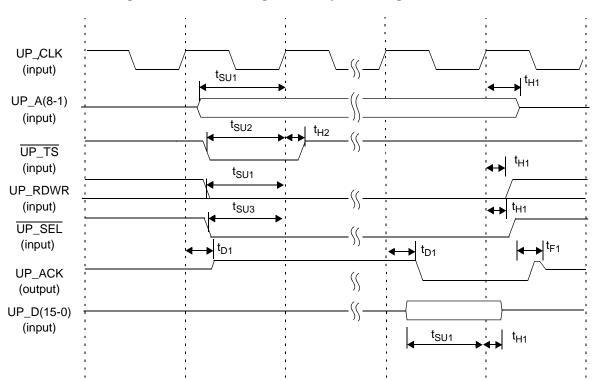

A 16-bit microprocessor data bus supports either Intel or Motorola processor interfaces. All communication to and from the chip is done via an internal mailbox. A gateway processor accesses the mailbox and processes messages from the host. All configuration and management may be done through this interface. A host driver is available providing a high level API to the host to manage the chip.

#### **UTOPIA** Interface

The ASPEN Express' UTOPIA 2 port constitutes the main interface for the cell traffic between the ASPEN Express and other devices. The ATM Forum compatible Level 2 interface can address up to 64 physical devices in ATM layer emulation (master) mode by incorporating 4 CLAV/ENB signals thereby allowing each polling cycle to address 4 devices but only 1 is selected for a given transfer. ASPEN Express supports both master and slave modes of operation.

In UTOPIA level 1 mode, only the cell level handshake is supported. Octet level is not supported.

VCC/VPC cross-connect: Connections may be switched directly from 1 UTOPIA port to another.

The possible UTOPIA configurations in cell mode are shown in Figures 6, 7, 8 and 9.

Note: All physical layer devices must be initialized prior to configuring and enabling the UTOPIA interface on ASPEN, to ensure proper signaling startup.

Figure 6. ASPEN Express Device in ATM Layer, Single-PHY Mode Configuration

www.DataSheet4U.com

DataSheet4U.com

Figure 7. ASPEN Express Device in PHY Layer, Single-PHY Mode Configuration

et4

Figure 8. ASPEN Express Device in ATM Layer, Multi-PHY Mode Configuration

Figure 9. ASPEN Express Device in PHY Layer, Multi-PHY Mode Configuration

Dual Latency 124 port Operation:

For dual latency DSL devices, the ASPEN Express will support 124 ports in a special mode called Dual Latency. In this mode, each pair of dual latency ports shares the lookup space for that port so that VPI/VCI combinations cannot be duplicated for both the low and high latency ports. Likewise, these 2 ports share the 11 egress queues (8 unicast and 3 multicast) so that the low latency channel (real time) uses the CBR, VBR-rt and VBR multicast queues. All other queues are dedicated to the high latency (data) channel. The dual latency channel pairs are mapped as follows:

| UTOPIA<br>Address | CLAV/ENB<br>Pair | Low Latency<br>Ports | High<br>Latency<br>Ports |

|-------------------|------------------|----------------------|--------------------------|

| 0 - 30            | 1                | 0 - 15               | 16 - 30                  |

| 0 - 30            | 2                | 31 - 46              | 47 - 61                  |

| 0 - 30            | 3                | 62 - 77              | 78 - 92                  |

| 0 - 30            | 4                | 93 - 108             | 109 - 123                |

| Table 1. | Dual Latenc | v Channel | Mapping |

|----------|-------------|-----------|---------|

|          | Dual Eatono |           | mapping |

where each Low Latency and High Latency port are paired together respectively (i.e., channel 0 and 16 are paired together in the same DSL subscriber as are 108 and 123).

et4

## **UTOPIA Clock Control**

et4

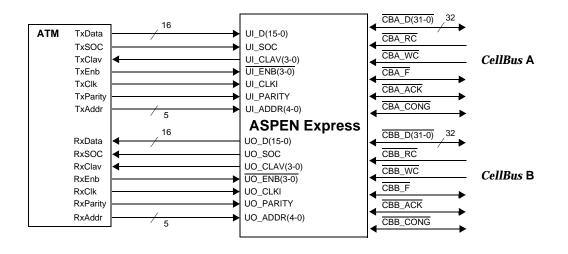

Figure 10. UTOPIA Clock Control

Figure 10 shows the configuration of the UTOPIA Clock output generation logic.

API function TXC\_MASPEN\_SetUtopialfaceCfg() has as one of the arguments, a structure with members utopiaClockDividerSelect and utopiaClockSrcSelect, which act as shown in Figure 10. Thus, the API allows selection of external clock LCLK, or an internally generated 25 MHz or 50 MHz clock as UTOPIA clock outputs UI\_CLKO and UO\_CLKO.

| ASPEN         | Express |

|---------------|---------|

| <b>TXC-05</b> | 806     |

**DATA SHEET**

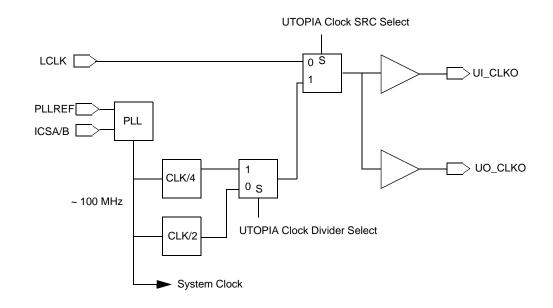

#### Dual CellBus Interface

The *CellBus* is a 37-lead GTLP shared bus with 32 bits of data. It can be implemented either on a single circuit card, or in a backplane configuration among multiple circuit cards. Access to the bus is controlled by a bus controller which resides in each *CellBus* device. Up to 32 *CellBus* devices may be connected on a single bus and 1 of them must be selected as the bus controller by setting its ENARBA or ENARBB lead low. Three different priorities may be requested by each device to the arbiter for access to the bus. The ASPEN Express has two *CellBus* interfaces which may be used for either load sharing or redundancy.

*CellBus* bridging capability is provided which allows traffic to be switched from one *CellBus* to the other on a per connection basis. This allows scalability of port density and bandwidth by using multiple ASPEN Express devices; one *CellBus* of each device is connected together as a local *CellBus* which allows switching between the devices. The other *CellBus* for each device is then used to connect to selected line cards in the system which are only serviced by that *CellBus*.

Figure 11. Data Flow for CellBus Bridging (Note: Data can also flow from CellBus B to CellBus A)

#### **Connection Table Memory Interface**

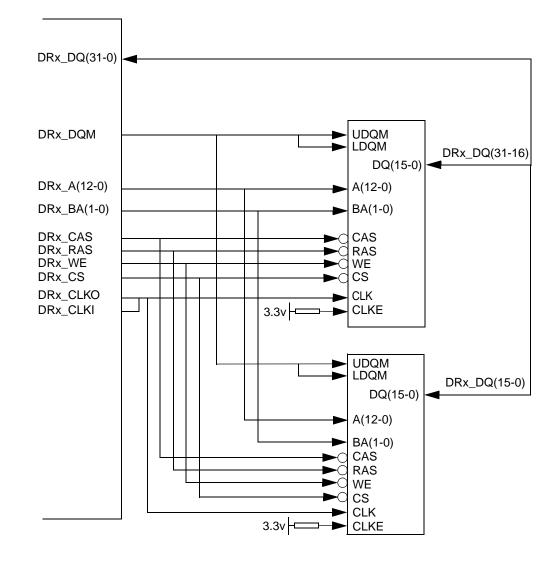

An external local memory is required by the ASPEN Express for policing statistics and address translation. The ASPEN Express integrates a complete memory controller to support this local memory. The on-chip memory controller provides a glueless interface to a 100 MHz SDRAM. No external timing or control logic is required. The connection table SDRAM memory controller directly addresses up to 8 Mbytes (64Mb, 128Mb or 256Mb SDRAMs may be used). The Connection Table memory controller is configured to use either (two) 16-bit memories or (one) 32-bit memory (see Figure 12).

#### **Cell Buffer Memory Interface**

An external local memory is required by the ASPEN Express for cell queuing. The ASPEN Express integrates a complete SDRAM memory controller to support this local memory. The on-chip memory controller provides a glueless interface to a 32-bit 100 MHz SDRAM. No external timing or control logic is required. The Cell Buffer SDRAM memory controller directly addresses up to 32 Mbytes of external memory to enable a maximum shared buffer size of 524,288 cells. The Cell Buffer memory controller is configured to use either (two) 16-bit memories or (one) 32-bit memory (64Mb, 128Mb or 256Mb SDRAMS may be used, see Figure 12).

| _                               |            | ASPEN Express |

|---------------------------------|------------|---------------|

| TRANSWITCH <sup>®</sup>         | DATA SHEET | TXC-05806     |

| Engines far Glabel Connectivity |            |               |

#### **Boundary Scan (Test Access) Port**

The test interface includes a five-lead Test Access Port (TAP) as the boundary scan port that conforms to the IEEE 1149.1 standard. This standard provides external boundary scan functions to read and write the external input/output leads from the TAP for board and component test.

Note: In this figure, DRx\_means DR1\_ or DR2\_

Figure 12. ASPEN Express SDRAM Configuration

et4

ASPEN Express TXC-05806

**DATA SHEET**

# OPERATION

#### **INTRODUCTION TO CellBus ARCHITECTURE**

This section provides an introduction to *CellBus* bus architecture and operation. Additional technical information is provided in Appendix A and B of a TranSwitch Technical Manual, document number TXC-05802-TM1, entitled "*CellBus* Bus Technical Manual and CUBIT-*Pro* Applications", which is available as a CUBIT-*Pro* document from the Products page of the TranSwitch Internet Web site at www.transwitch.com.

#### **CellBus** Operation

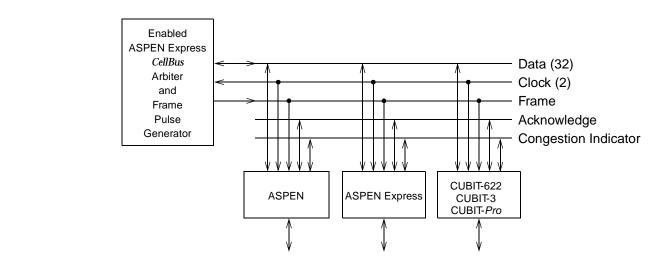

The ASPEN Express is a versatile CMOS device for implementing ATM switching and traffic management functions. Various ATM cell switching or multiplexing structures can be formed by interconnection of a number of ASPEN Express devices (or other TranSwitch *CellBus* compatible devices) over a 37-line parallel bus with 32 data bits, the *CellBus*. Since the interconnect structure is a bus, communication between any of the devices on the bus is possible. Each cell placed onto either *CellBus* by an ASPEN Express device can be routed either to one single *CellBus* device port (unicast addressing), or to multiple *CellBus* device ports (multicast or broadcast addressing). Depending upon the needs of an application, up to 32 *CellBus* devices may be interconnected on either *CellBus*. With a *CellBus* frequency of 40 MHz, the raw bandwidth of each *CellBus* exceeds 1 Gbit/s.

The *CellBus*, shown in Figure 13, is a shared bus, and can be implemented either on a single circuit card, or in a backplane configuration among multiple circuit cards. Since multiple ASPEN Express devices share the same bus, bus access contention must be resolved. This access contention is resolved by use of a central arbitration function. ASPEN Express devices will request bus access, and the central bus Arbiter will grant access back, in response. The circuitry for this bus Arbiter and frame pulse generator is included inside the ASPEN Express device. Any one ASPEN Express on a given bus in a system may be enabled to perform the bus arbitration and frame pulse generation functions for the arbitrated bus.

DataSheet4U.com

| Cycle<br>Number |    |                  |                               |                  |         |      |              |                    |      |

|-----------------|----|------------------|-------------------------------|------------------|---------|------|--------------|--------------------|------|

| <u> </u>        |    |                  |                               |                  |         |      |              |                    |      |

| Request         | 0  | 16161515<br>baba | 14141313<br>baba              | 12121111<br>baba |         |      | 6655<br>baba | 4 4 3 3<br>b a b a |      |

|                 | 1  | Ce               | ellBus Rou                    | iting Head       | ler     | Tar  | idem Rou     | uting Head         |      |

|                 | 2  | GFC              | V                             | PI               |         | VC   |              |                    | PT b |

|                 | 3  | Byt              | e 0                           | Byt              | e 1     | Byte | e 2          | Byt                | e 3  |

|                 | 4  | Byt              | e 4                           | Byt              | e 5     | Byte | e 6          | Byt                | e 7  |

|                 | 5  | Byt              | e 8                           | Byt              | e 9     | Byte | 10           | Byte               | e 11 |

|                 | 6  | Byte 12          |                               | Byte 13          |         | Byte | 14           | Byte 15            |      |

| Cell<br>Body    | 7  | Byte             | Byte 16                       |                  | Byte 17 |      | 18           | Byte 19            |      |

| (14 cycles)     | 8  | Byte             | e 20                          | Byte             | e 21    | Byte | 22           | Byte               | e 23 |

|                 | 9  | Byte             | e 24                          | Byte             | e 25    | Byte | 26           | Byte               | e 27 |

|                 | 10 | Byte             | e 28                          | Byte             | e 29    | Byte | 30           | Byte               | e 31 |

|                 | 11 | Byte             | ə 32                          | Byte             | e 33    | Byte | 34           | Byte               | ə 35 |

|                 | 12 | Byte             | e 36                          | Byte             | e 37    | Byte | 38           | Byte               | ə 39 |

|                 | 13 | Byte             | e 40                          | Byte             | e 41    | Byte | 42           | Byte               | e 43 |

| $\bigvee$       | 14 | Byte             | e 44                          | Byte             | e 45    | Byte | 46           | Byte               | e 47 |

| Grant           |    |                  | Granted<br>Terminal<br>Number |                  |         |      |              |                    |      |

| Figure 14.    | CellBus Fran | ne Format |

|---------------|--------------|-----------|

| i igui e i ti | Cumus i i ui |           |

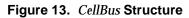

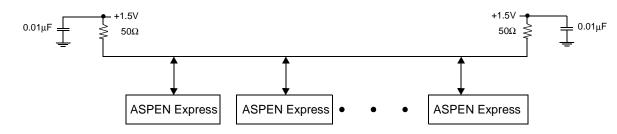

The CellBus has a framed format that is 16 clock cycles long and 32 bits wide, as illustrated in Figure 14. The first cycle of each frame is the Request cycle (Cycle 0), during which those ASPEN Express devices (or other CellBus devices) which have a cell to send to the CellBus each make an access request by asserting one or two assigned bits on the CellBus. The CBA\_F/CBB\_F, CBA\_ACK/CBB\_ACK, and CBA\_CONG/CBB\_CONG signals are asserted during a Request cycle. The CellBus ID assigned to each ASPEN Express by Unit Address leads UA(4-0) uniquely specifies which two bits it may assert during the CellBus Request cycle time. CellBus IDs 0-15 are used for 16-user systems and IDs 0-31 are used for 32-user systems (see Figure 15). For example, when leads UA(4-0) are all high, the CellBus ID is 0 and bits 1a and 1b are selected. By asserting one of its assigned bits, or the other, or both, access requests of three different priorities may be made. A central CellBus Arbiter accepts these access requests, executes an arbitration algorithm (highest priority served first, roundrobin within each priority), and issues a CellBus access grant during the final cycle of the frame, the Grant cycle (Cycle 15). Each grant issued by the CellBus Arbiter is for one CellBus device to send one cell to the CellBus. Whichever CellBus device is issued a grant during a Grant cycle will transmit its cell during the 14 Cell Body clock cycles of the next bus frame, and will also drive an 8-bit cell parity check (BIP-8) during the Grant cycle of that CellBus frame. Each cell sent can be of unicast, multicast, or broadcast type. ASPEN Express devices will accept single-address cells routed to an address defined by its address straps UA(4-0) as well as all broadcast cells, and multicast cells whose multicast session IDs are configured appropriately. Thus, cells may be sent from any one ASPEN Express to any one ASPEN Express (or other CellBus device) or to multiple destinations.

et4

| ASPEN Express |            |            |

|---------------|------------|------------|

| TXC-05806     | DATA SHEET | TRANSWITCH |

|               |            |            |

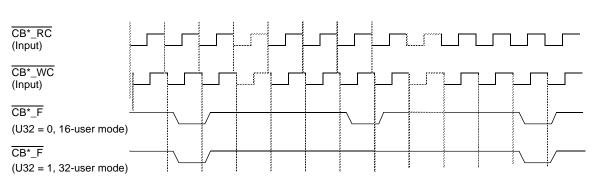

The ASPEN Express can be operated in either 16-user or 32-user mode, selectable via the U32 lead, as shown in Figure 15. For the 16-user mode, all *CellBus* frames have an associated frame pulse CBA\_F/CBB\_F. However, in 32-user mode the frame is duplicated, so that an odd and even frame are provided. The distinction between these two frames is given by the location of the Request cycle relative to the frame pulse. The Request cycle in the even frame ASPEN Express devices with *CellBus* address 0 -15 (lower 16 users) request access to the *CellBus*, and in the odd frame ASPEN Express devices 16-31 (upper 16 users) request access to the *CellBus* bandwidth is available to be shared among all the users on the *CellBus* in either 16 or 32-user mode.

An additional DualTX feature is available in the ASPEN Express. This feature allows the device to assume 2 *CellBus* addresses for transmit - one in the range of 0-15 and the other in the range of 16-31 so that the device can request the *CellBus* in both even and odd frames. This feature allows the ASPEN Express to utilize the entire bandwidth of the *CellBus* in a 32-user configuration. DualTX feature is controlled by ASPEN Express API TXC\_MASPEN\_SetCellbusIfaceCfg.

Figure 15. CellBus 16/32-User Modes - Frame Formats

To detect *CellBus* errors, a BIP-8 (Bit Interleave Parity byte) is calculated over the 54-byte data field that extends from the first Tandem Routing Header byte in Cycle 1 through the final payload data byte, Byte 47 in Cycle 14. The BIP-8 is generated by the transmitting ASPEN Express using the following algorithm: The first byte of the Tandem Routing Header is exclusive-or gated with an all-ones byte, creating a starting seed value. This seed value is then exclusive-or gated with the second byte of the Tandem Routing Header. The result is then exclusive-or gated with the next byte in the cell. This process is repeated with every successive byte in the cell, through Byte 47 of the payload, and the final result is transmitted as the BIP-8 byte in cycle 15. The receiving ASPEN Express performs the same process and compares the generated BIP-8 with the received BIP-8. If no errors are detected the receiving ASPEN Express drives CBA\_ACK/CBB\_ACK low, acknowledging receipt of a cell. The *CellBus* Routing Header has its own CRC-4 field and is not included in the BIP-8 calculation. A cell with a BIP-8 or CRC-4 error is discarded.

The only signals required to operate the *CellBus* which are not sourced by a <u>ASPEN Express</u> device are two transfer clocks per *CellBus*: write clocks CBA\_WC, CBB\_WC and read clocks CBA\_RC, CBB\_RC. These clock signals are of the same frequency, but may be slightly phase-offset to accommodate different backplanes and devices. The frame pulse used to define the bus frame cycle is sent out by one of the ASPEN Express devices, the arbitration function is also performed by the same ASPEN Express device. Each ASPEN Express device contains the circuitry for both the bus Arbiter and the Frame Pulse Generator. Only one ASPEN Express per *CellBus* will have this circuitry enabled, by setting the ENARBA/ENARBB leads on the device to the active low level.

ASPEN Express TXC-05806

## CellBus Cell Routing

The *CellBus* architecture allows several types of cell routing from any one inlet port to the outlet ports of the ASPEN Express devices on the *CellBus*:

- Point-to-Point Routing: In Unicast or Single Address cell routing a cell coming into an inlet port is transferred to a single outlet port of a specific *CellBus* device. The ASPEN Express can also address a cell to itself, effectively implementing both the inlet and outlet ports.

- Point-to-Multipoint (Multicast): In multicast routing the cell arriving at the inlet port is sent to the subset of outlet ports that belong to the specific multicast session in each *CellBus* device on the *CellBus*.

- Point-to-Multipoint (Broadcast): A cell coming into the inlet port is routed to all of the outlet ports of all the *CellBus* devices on the *CellBus*.

For each of the routing methods the cells can be sent to different output queues according to whether the cell is used as a data cell or as control/loopback cell. Furthermore, data cells can be selected to go to one of four different data outlet queues per UTOPIA 2 outlet port: CBR queue, VBR-rt queue, VBR-nrt queue, and UBR/GFR queue.

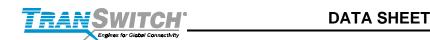

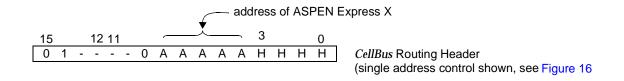

The encoding rules for the two-byte *CellBus* Routing Header in Bits 31-16 of Cycle 1 are summarized in Figure 16.

### Figure 16. CellBus Routing Header Formats

et4

| ASPEN         | Express |

|---------------|---------|

| <b>TXC-05</b> | 806     |

DATA SHEET

#### CellBus Routing Header Format

The CellBus Routing Header contains the following fields, as shown in Figure 16:

- A: ASPEN Express single address field (5 bits, for 32 addresses). A0 is the LSB. For example, A(4-0)=00000 is the address value for the ASPEN Express whose five device identity straps UA(4-0) are all tied high (HHHHH).

- M: Multicast number field (9 bits, for 512 multicast sessions). M0 is the LSB.

- H: CRC-4 field. This 4-bit field H(3-0) provides *CellBus* Routing Header error protection across the *CellBus* in both directions. It is calculated over the 12-bit word (X11-X0) in bits 31-20 of the Routing Header using the following logic, where ⊕ represents logical exclusive-or:

- $H3 = (\overline{X7} \oplus \overline{X9} \oplus \overline{X3} \oplus \overline{X10} \oplus \overline{X8} \oplus \overline{X5} \oplus \overline{X2})$

- $H2 = (X6 \oplus X8 \oplus X2 \oplus X9 \oplus X7 \oplus X4 \oplus X1)$

- $H1 = (\overline{X5} \oplus \overline{X7} \oplus \overline{X1} \oplus \overline{X8} \oplus \overline{X6} \oplus \overline{X3} \oplus \overline{X0})$

- $H0 = (X8 \oplus X10 \oplus X4 \oplus X11 \oplus X9 \oplus X6 \oplus X3 \oplus X0)$

For cells arriving from the *CellBus*, the ASPEN Express automatically calculates the corresponding CRC-4 and compares to the received Routing Header. This may be enabled to cause an interrupt signal to the microprocessor. The CRC-4 is automatically calculated and inserted by the ASPEN Express into cells sent to the *CellBus*.

#### Tandem Routing Header Format

- In ASPEN Express applications, the Tandem Routing Header bits 11-0 (Extended Queue field) are used for queue and priority selection and include cyclical redundancy protection (C3-C0).

- E: Extended Queue field E(15-0). E(15-0) indicate connection ID, and C(3-0) is the CRC-4 for E(11-0). The CRC-4 is inserted by the ASPEN Express.

#### **CellBus** Status Signals and Monitoring

The ASPEN Express provides the capability to monitor the activity on the *CellBus*. The essential signals that determine whether the *CellBus* is active (in the absence of any cell traffic) are the clock signals and the frame pulse.

The *CellBus* clocks (read and write) are generated externally to the ASPEN Express. If either of these clocks fails, the entire *CellBus* will cease operation. The ASPEN Express provides the capability to detect the absence of clock signal for more than the equivalent of 32 processor clock (PCLK) cycles. The failure detection is performed independently for the *CellBus* Read Clocks CBA\_RC, CBB\_RC and the *CellBus* Write Clocks (CBA\_WC, CBB\_WC).

Either event can be used to generate a microprocessor interrupt provided that the corresponding bit in the interrupt enable register is set.

The second monitoring function concerns the detection of loss of frame (CBLOF). The detection mechanism looks for two consecutive missing *CellBus* frame pulses CBA\_F/CBB\_F in 32-user mode (U32 = Low), and four consecutive missing *CellBus* frame pulses in 16-user mode. The *CellBus* Read Clock must be present to detect Loss of Frame Pulse. CBLOF will generate an interrupt to the microprocessor if the corresponding interrupt enable bit is 1.

Apart from the detection of loss of *CellBus* Read and Write clocks, the device has a recovery mechanism that re-synchronizes the device to the *CellBus* frame pulse as soon as the *CellBus* clocks are restored and stabilized to resume normal operation.

## THE CellBus INTERFACE

Thirty-seven lines comprise the *CellBus* interface, as shown in Figures 1 and 13. There are thirty-two data lines, with Frame, Acknowledge, and Congestion Indicator lines, all sourced by a ASPEN Express device, and two Clock lines sourced by external drivers. Additional technical information for implementing a *CellBus* Bus with circuit cards plugged into backplane connectors is provided in a document entitled "TranSwitch *CellBus* Bus Reference Design Guideline for CUBIT-*Pro* Applications", Revision 0.5 dated February 19, 1999, which is available as a CUBIT-*Pro* document from the Products page of the TranSwitch Internet Web site at www.transwitch.com.

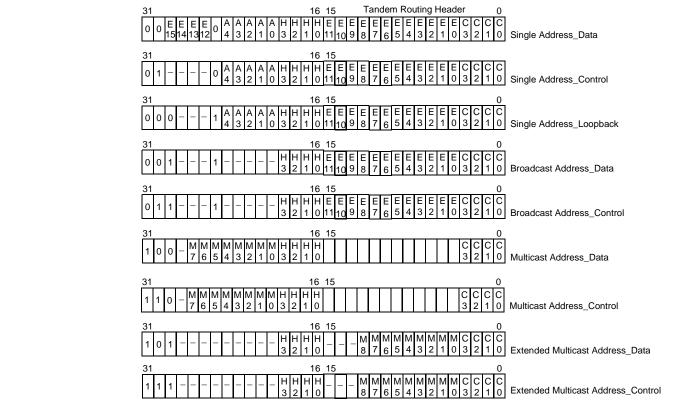

#### **Operation with Internal GTL+ Transceivers**

Gunning Transceiver Logic (GTL+) transceivers for *CellBus* Data, Frame, Acknowledge, and Congestion Indicator lines are contained internally in the ASPEN Express, along with two clock line GTL+ receivers. Each of the drivers has a typical current sink capability of 45 mA and is capable of driving a bus on a card or on a backplane directly. Each of the GTL+ lines is to be pulled up at each of its ends by a 50 ohm ( $\pm$  5%) resistor (metal film or carbon composition) to a +1.5 V low-impedance supply. Each end of each line should have a filtering capacitor connected from the +1.5 V supply to ground, as shown in Figure 17.

Figure 17. External Circuit Requirements for GTL+ Transceivers

In the ASPEN Express lead configuration, all of the leads involved with the *CellBus* interface are aligned along one side of the package (between lead rows AB and W). This side of the package must be aligned toward the board connector, or toward the *CellBus*, with as little board trace length as possible between the leads and the connector or *CellBus*, to maximize operating speed.

### Clock Source

Two GTL+ clock signals must be driven to the *CellBus* from an external source. These are the write clocks, CBA\_WC, CBB\_WC, and the read clocks, CBA\_RC, CBB\_RC. A phase relationship keeping the write clock between 0.5 and 4 nanoseconds behind the read clock is needed to ensure proper synchronous *CellBus* operation. When the clock driver is driven from the center of the backplane (i.e., no greater than half a backplane length from any card) a minimum phase distance of 1.0 ns or more must be maintained. When the driver is at one of the ends, a more conservative 2-4 ns minimum is required. In any *CellBus* implementation, on the backplane and on each card, care must be taken to ensure that these two lines are routed together. The capacitive and inductive loadings of the two lines should be as nearly equal as possible, to maintain performance. At the drive point, a delay line should be used to maintain a stable delay, and the read and write clock drivers must be units of the same integrated circuit package. All of these precautions will ensure the most stable clocks and permit the highest possible operating speed.

| ASPEN  | <b>Express</b> |

|--------|----------------|

| TXC-05 | 806            |

**DATA SHEET**

#### **CellBus Bus Arbiter Selection**

One copy of the *CellBus* Bus Arbiter circuitry is included inside each ASPEN Express device. Enabling of the Arbiter on a particular ASPEN Express is done by connecting the ENARBA, ENARBB leads of that device to ground ( $V_{SS}$ ). Only one Arbiter may be enabled at a time. It is the responsibility of the overall system control to decide which ASPEN Express will have its Arbiter enabled, and to enable it. Failure of an Arbiter can be detected by using the NOGRT indications. If multiple ASPEN Express devices are indicating NOGRT failures, an Arbiter failure is indicated. It is again the responsibility of system control to enable another *CellBus* Arbiter. Upon switching from one Arbiter to another, the receiving devices on the *CellBus* will automatically re-align to the new frame position within one *CellBus* frame.

#### MULTICAST SESSION MEMORY

A multicast address data cell is sent to all ASPEN Express devices, and each ASPEN Express will check the multicast session (max. 512) and lookup in its Multicast Session Table (MST) if this device should participate in the multicast session. Each of the 512 multicast session addresses has a 64-bit list of destination ports to which a cell can be forwarded (max. all 64 ports). For each bit that is set to 1 in the list corresponding to the received multicast address, the cell is forwarded to the port corresponding to that bit. Each ASPEN Express device can be configured to accept any or all of the 512 possible multicast sessions and send them to any or all of the possible 64 destination ports by setting the bit in the corresponding location in the table. The multicast process adopted is a pointer replication process as opposed to a cell duplication process. Pointers to a given multicast cell are added to their appropriate destination queues without replicating the cell. All Broadcast Traffic uses Multicast Session 0.

If any port becomes disabled, the host can reset the multicast session bit corresponding to that port and then disable the UTOPIA port by resetting to zero the corresponding PHYEN bit using ASPEN Express API TXC\_MASPEN\_SetUtopiaPhyCfg. Resetting the active bit will prevent the cell from being replicated to the queue for that port.

Note: In order to update the leaves associated with a particular multicast session, eight consecutive memory addresses must be written, using ASPEN Express API call TXC\_MASPEN\_SetMulticastSession.

Multicast control cells have their own multicast session table for up to 31 sessions. Multicast control cells are only accepted by *CellBus* devices (depending on the state of the control multicast session table) and not replicated to multiple ports. These cells are sent to the Control Receive Queue for extraction to the host processor. The multicast session table memory contains 1 bit for each session.

DATA SHEET

### LOOPBACK CELL TRANSMIT, RECEIVE, AND RELAY

The loopback function is provided for diagnostic purposes. It may be used on-line, or off-line. For example, a loopback path for a cell from ASPEN Express X to ASPEN Express Y and back to ASPEN Express X can be set up, as shown in Figure 18. The host then writes a cell with a single address loopback Routing Header for ASPEN Express Y into the control transmit buffer of ASPEN Express X and causes the cell to be sent. When ASPEN Express Y receives the cell it will use a pre-loaded *CellBus* Routing Header to form a new Routing Header for the cell and send it back to ASPEN Express X. ASPEN Express X will receive the cell and place it in the control receive buffer where it can be accessed by the host. See ASPEN Express API TXC-MASPEN\_SetCellbusIfaceCfg for details.

The above description assumes that the loopback cell originates in the control transmit buffer of ASPEN Express X, but it could also be received from the inlet port. Any of the six Routing Header formats shown in Figure 16 could actually be loaded in the ASPEN Express Y instead of the single address control *CellBus* Routing Header of ASPEN Express X, with a corresponding change in the final destination of the loopback cell.

Note: '-' indicates don't care state

#### Figure 18. Loading the Loopback Registers for ASPEN Express Y

All aspects of system operation are the responsibility of the control system implemented for use of the ASPEN Express devices. Care must be taken to ensure that no more than one ASPEN Express is trying to set up a loopback into the same ASPEN Express, or mis-routing will occur.

www.DataSheet4U.com

| ASPEN  | <b>Express</b> |

|--------|----------------|

| TXC-05 | 806            |

DATA SHEET

#### **BOUNDARY SCAN**

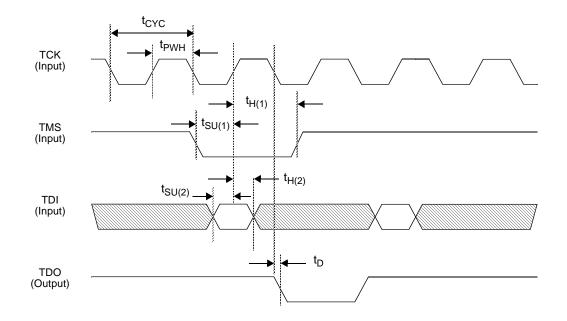

The IEEE 1149.1 Standard defines the requirements of a boundary scan architecture that has been specified by the IEEE Joint Test Action Group (JTAG). Boundary scan is a specialized scan architecture that provides absorbability and controllability for the interface leads of the device. The Test Access Port block, which implements the boundary scan functions, consists of a Test Access Port (TAP) controller, instruction and data registers, and a boundary scan register path bordering the input and output leads, as illustrated in Figure 19. The boundary scan test bus interface consists of four input signals (i.e., the Test Clock (TCK), Test Mode Select (TMS), Test Data Input (TDI) and Test Reset (TRS) input signals) and a Test Data Output (TDO) output signal (see "Reset and Test Leads (Including Test Access Port for Boundary Scan)" on page 40. A brief description of boundary scan operation is provided below; further information is available in the IEEE Standard document.

The TAP controller receives external control information via a Test Clock (TCK) signal, a Test Mode Select (TMS) signal, and a Test Reset (TRS) signal, and it sends control signals to the internal scan paths. The scan path architecture consists of a 16-bit serial instruction register and two or more serial data registers. The instruction and data registers are connected in parallel between the serial Test Data Input (TDI) and Test Data Output (TDO) signals. The Test Data Input (TDI) signal is routed to both the instruction and data registers and is used to transfer serial data into a register during a scan operation. The Test Data Output (TDO) is selected to send data from either register during a scan operation. The timing of the boundary scan signals is shown in Figure 48.

ŧ/

When boundary scan testing is not being performed, the boundary scan register is transparent, allowing the input and output signals at the device leads to pass to and from the device's internal logic. During boundary scan testing, the boundary scan register disables the normal flow of input and output signals to allow the device to be controlled and observed via scan operations. Data is read out from internal test registers LSB first.

#### Boundary Scan Support

The following boundary scan test instructions are supported

- EXTEST

- SAMPLE/PRELOAD

- BYPASS

- IDCODE

- HIGHZ

- CLAMP

#### EXTEST Test Instruction:

One of the required boundary scan tests is the external boundary test (EXTEST) instruction. When this instruction is shifted in, the device is forced into an off-line test mode. While in this test mode, the test bus can shift data through the boundary scan registers to control the external input and output leads.

#### SAMPLE/PRELOAD Test Instruction:

When the SAMPLE/PRELOAD instruction is shifted in, the device remains fully operational. While in this test mode, input data, and data destined for device outputs, can be captured and shifted out for inspection. The data is captured in response to control signals sent to the TAP controller.

#### **BYPASS Test Instruction:**

When the BYPASS instruction is shifted in, the device remains fully operational. While in this test mode, a scan operation will transfer serial data from the TDI input, through an internal scan cell, to the TDO lead. The purpose of this instruction is to abbreviate the scan path through the circuits that are not being tested to only a single clock delay.

**DATA SHEET**

#### **IDCODE** Instruction

When the IDCODE instruction is shifted in, the device remains fully operational. The purpose of this instruction is to output the device ID code register on the TDO lead.

#### **HIGHZ** Instruction

The HIGHZ instruction is used to place all outputs in an inactive drive state (high impedance). In this state, an in-circuit test system may drive signals onto the connections normally driven by a component output without incurring the risk of damage to the component.

#### **CLAMP** Instruction

The CLAMP instruction allows the state of the signals driven from the component leads to be determined from the boundary-scan register while the bypass register is selected as the serial path between TDI and TDO. The signals driven from the component leads will not switch while the CLAMP instruction is selected.

| ASPEN Express |            |      |

|---------------|------------|------|

| TXC-05806     | DATA SHEET | TRAN |

#### **BSDL File**

A Boundary Scan Description Language (BSDL) file for the ASPEN Express device will be made available for download from the Products page of the TranSwitch Internet Web site at www.transwitch.com.

Figure 19. Boundary Scan Top-Level Block Diagram

et4

# ASPEN Express TXC-05806

# LEAD DIAGRAM

|                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |  |                                                                                                                                                       | В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | otto                                                 | om v                                          | view                                          | v of                                                                                                                          | pac                                                  | kag                                         | je |              |                                                                            |                                                                                   |  |  |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|----|--------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

|                                                                                                            | Billelogic         Billelogilogic         Billelogic         Bil                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |  | $\begin{array}{c} A8 \\ \bigcirc DR2_{-} \\ A7 \\ \bigcirc DR2_{-} \\ A6 \\ \bigcirc DR2_{-} \\ A6 \\ \bigcirc DR2_{-} \\ A5 \\ \bigcirc \end{array}$ | $\begin{array}{c} DR2 \\ A11 \\ O2 \\ A0 \\ DR2 \\ A10 \\ DR2 \\ A0 \\ OB2 \\ A0 \\ OB2 \\ A0 \\ OB2 \\ A0 \\ OB2 \\ OB2 \\ A0 \\ OB2 \\ $ |                                                      |                                               |                                               | $\begin{array}{c} DR2\_\\ DQ25 \\ \hline \\ DR2\_\\ DQ22 \\ \hline \\ DR2\_\\ DQ26 \\ \hline \\ VSS \\ \hline \\ \end{array}$ |                                                      | UR2_<br>DQ5<br>VSS<br>VSS<br>VSS<br>VDD18   |    |              | $\bigcirc DR2_DQ30$ $\bigcirc DR2_DQ1$ $\bigcirc DR2_DQ15$ $\bigcirc DQ15$ |                                                                                   |  |  |