# TXC100 300-450MHz RFIC Transmitter

Complies with Directive 2002/95/EC (RoHS)

#### I. Product Overview

TXC100 is a rugged, single chip OOK/ASK/FSK Transmitter IC in the 300-450 MHz frequency range. This chip is highly integrated and has all required RF functions including a complete PLL circuit and power amplifier, thus requiring very few external components. The TXC100 is feature rich and is very small in size with high output power and low current consumption and is ideal for various short range wireless applications in the industrial, automotive and consumer markets.

## **II. Key Features**

Operating Frequency Range: 300-450 MHz

Modulation Types: OOK/ASK/FSK

Operation supply voltage: 2.1V - 3.6V

High Date rate:

ASK: 100 kbps FSK: 20 kbps Low current consumption:

ASK mode: 7 mA typical FSK mode: 10 mA typical

- Low Stand by current: < 1 nA</li>

- Adjustable Output power: -10dBm to +10dBm

- Adjustable FSK Shift

- Programmable Clock Output

- Very Low external component count

- Extended temperature range: -40°C to +125°C.

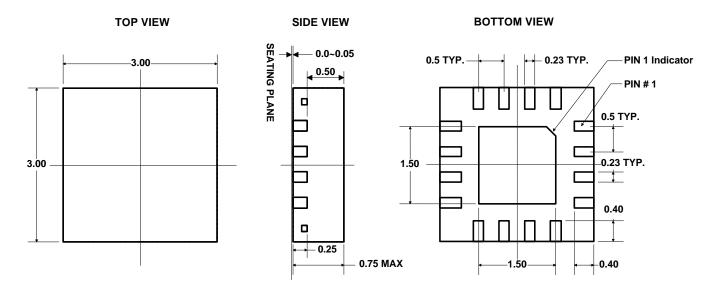

- Small Package: 3X3 mm 16-pin TQFN package

- Standard 13 inch reel, 2500 pieces

## III. Popular applications

- Active RFID tags

- Automated Meter reading

- Wireless sensor nodes

- Home Automation

- Security systems

- Tire pressure monitoring

- Remote keyless entry

- Automobile Immobilizers

- Sports & Performance monitoring

- Wireless Toys

- Medical equipment

- · Command & Control systems

# **Electrical Characteristics**

| Characteristics       | Sym | Min | Typical         | Max  | Units |

|-----------------------|-----|-----|-----------------|------|-------|

| Operating Frequency   | fo  | 300 |                 | 450  | MHz   |

| Modulation Types      |     |     | OOK/ASK/<br>FSK |      |       |

| ASK Data Rate         |     |     |                 | 100  | Kbps  |

| FSK Data Rate         |     |     |                 | 20   | Kbps  |

| Peak RF Output Power  |     |     | 10              |      | dBm   |

| Standby Current       |     |     |                 | 1    | nA    |

| Supply Voltage Range  | Vdd | 2.1 |                 | 3.6  | Vdc   |

| Operating Temperature | Та  | -40 |                 | +125 | °C    |

3x3mm package

#### **Crystal Parameters**

| Characteristics   | Sym | Min | Typical | Max | Units |

|-------------------|-----|-----|---------|-----|-------|

| Crystal Frequency | fc  |     | fo/32   |     | MHz   |

| Load Capacitance  | CI  |     |         | 10  | pF    |

| Tolerance         | Tol |     | 30      |     | ppm   |

# RF Monolithics, Inc.

PIN 4 ENABLE INPUT PIN 16 GND

#### Mode TX Data VDD PA D0 D1 D2 Input Input 2 3 Shape RF Modulation **Mode Select** Control (ASK / FSK) Control **XTAL XTAL1 14** DRV LOGIC REF<sub>EXT</sub>/XTAL2 Mixer PΑ 15 C<sub>3</sub> $\mathbf{C}_{\mathbf{2}}$ Output osc Filter CLK0 • 10 /32 **∮** 5 BIAS CLK

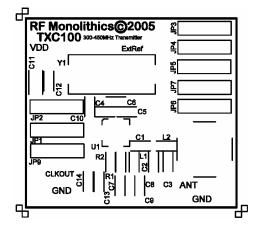

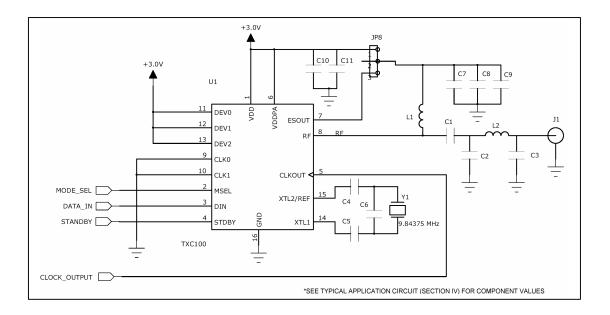

# IV. TXC100 Block Diagram and Typical Application Circuit

Table 1: Component Values for Typical Application Circuit

|                  | 315MHz Band | 433MHz Band |  |  |

|------------------|-------------|-------------|--|--|

| C1               | 100pF       | 100pF       |  |  |

| C2               | 100pF       | 100pF       |  |  |

| C3 <sup>3</sup>  | DNP         | DNP         |  |  |

| C4 <sup>3</sup>  | DNP         | DNP         |  |  |

| C5               | 1uF         | 1uF         |  |  |

| C6               | .01uF       | .01uF       |  |  |

| C7               | 220pF       | 220pF       |  |  |

| C8               | 100pF       | 100pF       |  |  |

| C9               | 680pF       | 680pF       |  |  |

| C10 <sup>1</sup> | 15pF        | 6.8pF       |  |  |

| C11 <sup>1</sup> | 22pF        | 1pF         |  |  |

| C121             | 15pF        | 6.8pF       |  |  |

| C13              | 1uF         | 1uF         |  |  |

| C14              | .01uF       | .01uF       |  |  |

| C15              | 220pF       | 220pF       |  |  |

| C16 <sup>1</sup> | 2.2pF       | 1pF         |  |  |

| L1 <sup>12</sup> | 27nH        | 22nH        |  |  |

| L2 <sup>12</sup> | 22nH        | 18nH        |  |  |

| X1               | 9.84375MHz  | 13.5600MHZ  |  |  |

<sup>1</sup>Matched to 50 Ohms

<sup>2</sup>Use wirewound inductors ONLY

<sup>3</sup>Use for External Reference Input

DNP - Do Not Populate

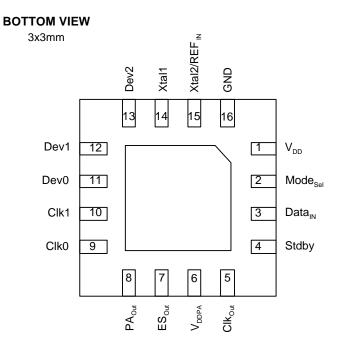

# **V. Pin Configuration**

# **VI. Pin Description**

| Pin | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>DD</sub>    | V <sub>DD</sub> is the supply voltage for the PLL and Logic. Bypass as close as possible to pin with 1μF, .01μF, 220pf.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | $Mode_{Sel}$       | Mode Select enables the chip to be set in ASK or FSK mode Low: ASK mode High: FSK mode  ASK, FSK Mode Selection The Mode Select pin (2) sets the transmit mode of the device. A logic low sets the mode to ASK modulation. A logic high sets the device to FSK modulation.  In ASK mode, data driven onto the Data <sub>IN</sub> pin (3) gates the internal power amplifier. A data "High" turns the power amplifier on and thus drives the RF signal to the antenna. A data "Low" turns off the power amplifier.  In FSK mode, data driven onto the Data <sub>IN</sub> pin shifts the carrier frequency by the amount programmed through the DEV[20] pins (13,12,11). A data "Low" performs no shift. The frequency of a data "Low" in FSK mode is the same frequency of a data "High" in ASK mode. The FSK deviation is achieved by pulling the crystal frequency. See <i>Crystal Reference</i> section (pin 15) for more details. The maximum deviation for the 315MHz band and 433MHz band is approximately 55 kHz and 80 kHz, respectively. |

| 3   | Data <sub>IN</sub> | Data Input enables the turning on and off of the Power Amplifier in ASK mode and selection of high or low frequency in FSK mode.  Low (ASK mode): Power Amplifier off High (ASK mode): Power Amplifier on  Low (FSK mode): Low frequency High (FSK mode): High frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4   | Stdby              | Standby enables selection of low power shutdown/standby mode  Low or if left unconnected: Sets device in Standby mode  High: Sets device in Ready for transmission mode  Note: Lowest current consumption achieved when all config pins at Logic Low.  Standby Mode  The Standby pin (4) sets the device in low power shutdown, pulling only 0.2nA. When the device is brought out of standby with a logic "High", it is ready for operation within 200us. The Standby pin has an internal pull-down resistor so this pin can be pulled low or left unconnected. The 200us turn-on time is due to crystal start-up. An optimally matched crystal will minimize this turn-on time. See Crystal Reference section (pin 15) for details on crystal load matching.                                                                                                                                                                                                                                                                                   |

|            |                         | frequency. In FSK mode, a portion of the 3pF load is removed in response to a data logic "High" applied to the Data <sub>IN</sub> (pin 2) and the programmed frequency deviation pins DEV[02] (13,12,11). For larger frequency deviations use a crystal with larger motional capacitance or reduce PCB parasitic capacitance as much as possible.                                                                                                                                       |

|------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15         | Xtal2/REF <sub>IN</sub> | bypassed with a .01µF capacitor and additional .01µF series capacitance should be added into External Reference input.  Crystal Reference  The crystal drive circuit in the TXC100 is designed to present a 3pF load to GND to the reference crystal. Including PCB parasitic capacitances, this increases to about 4.5pF. In ASK mode, the full 3pF load is applied to the crystal allowing it to oscillate at the desired                                                             |

|            |                         | package capacitance which increases the presented load to about 4.5pF.  External Ref Input enables a custom frequency to be applied to obtain the desired transmit frequency. Unconnected Xtal1 input must be                                                                                                                                                                                                                                                                           |

|            |                         | package capacitance which increases the presented load to about 4.5pF.  External Crystal input 2 presents a capacitance of 3pF to GND in ASK and FSK(Data <sub>IN</sub> =0V) mode. Additional circuit parasitics add to the                                                                                                                                                                                                                                                             |

| 14         | Xtal1                   | External Crystal input 1 presents a capacitance of 3pF to GND in ASK and FSK(Data <sub>IN</sub> =0V) mode. Additional circuit parasitics add to the                                                                                                                                                                                                                                                                                                                                     |

|            |                         | .750 x max                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13, 12, 11 | FreqDev[20]             | .375 x max                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                         | DEV D         DEV 2         DEV 1         DEV 0           .125 x max         0         0         0           .250 x max         0         0         1                                                                                                                                                                                                                                                                                                                                   |

|            |                         | Frequency Deviation configuration pins set the amount of deviation desired between data logic states in FSK mode. Frequency deviation is programmable through pins 13, 12, 11 as below:                                                                                                                                                                                                                                                                                                 |

| 10, 9      | Clk[10]                 | See description for Pin 5                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8          | PA <sub>Out</sub>       | Power Amplifier  The power amp is an open-drain, Class C amplifier with optimal impedance at PA <sub>OUT</sub> (pin 8) of about 250 Ohms. A matching network can optimize the output to drive typical 50 Ohm antennas. An output matching network with component values is shown in the <i>Typical Application Circuit</i> (section IV). Additionally, the matching network aids in suppressing carrier harmonics to aid in compliance testing.                                         |

|            |                         | The envelope-shaping resistor allows for a turn on / turn-off of the Power Amp in ASK mode.  Power-Amplifier Output Requires a DC path to the supply voltage, thru a series inductor which can be part of the output matching network to an antenna                                                                                                                                                                                                                                     |

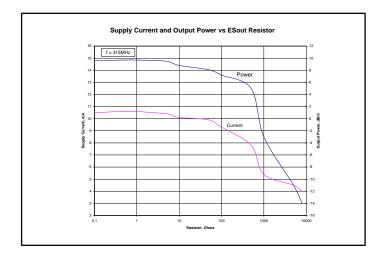

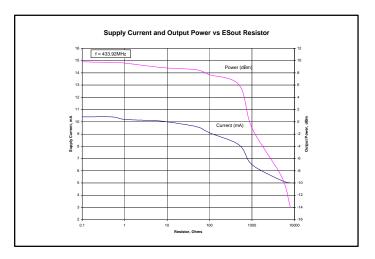

|            |                         | Spectral Shaping/Output Power Adjust The ES <sub>OUT</sub> pin (7) can serve a dual function. Use of the ES <sub>OUT</sub> pin will allow for a softer turn-on/turn-off of the power amplifier resulting in reduced spectral spreading of the ASK signal. Inserting a series resistor between the ES <sub>OUT</sub> pin and the pull-up inductor will allow for adjustment of the carrier output power. Typically a resistance of 5K Ohms or less will allow adjustment down to -10dBm. |

| 7          | ES <sub>Out</sub>       | Note: By using the ES <sub>OUT</sub> pin there is approx a 0.6dB drop in max output power.                                                                                                                                                                                                                                                                                                                                                                                              |

|            |                         | Envelope-Shaping Output controls the on/off ramp time of the power amp in ASK mode. This reduces the spectral width of the output signal when modulated. Placing a small resistor in series with the output, as close as possible to the chip to minimize circuit parasitics, will enable control of output power. A potentiometer may be used to adjust the output power to the desired level. Bypass as close to the pin as possible with a 680pF and 220pF capacitor.                |

| 6          | $V_{DDPA}$              | Supply voltage for the Power amp.  Bypass as close as possible to the pin with a .01µF and 220pf capacitor.                                                                                                                                                                                                                                                                                                                                                                             |

|            |                         | NB: fc = (Crystal Frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5          | Clk <sub>Out</sub>      | 1 0 fc/4<br>0 1 fc/8<br>1 1 fc/16                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| _          |                         | Clk0         Clk1         Clk <sub>Out</sub> 0         0         0                                                                                                                                                                                                                                                                                                                                                                                                                      |

# **VII. Absolute Maximum Ratings**

| Parameter                                                                                                   | Symbol | Limit ' | Unit      |    |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|--------|---------|-----------|----|--|--|--|--|

|                                                                                                             |        | Min     | Max       |    |  |  |  |  |

| Operating Temperature                                                                                       | То     | -40     | +125      | °C |  |  |  |  |

| Junction Temperature                                                                                        | TJ     | -40     | +150      | °C |  |  |  |  |

| Storage Temperature                                                                                         | Ts     | -60     | +150      | °C |  |  |  |  |

| Supply Voltage – Vdd to GND                                                                                 | Vs     | -0.3    | +4        | V  |  |  |  |  |

| All pins to GND                                                                                             |        | -0.3    | Vdd + 0.3 | V  |  |  |  |  |

| Note: Maximum ratings must not be exceeded under any circumstances and can cause permanent damage to the IC |        |         |           |    |  |  |  |  |

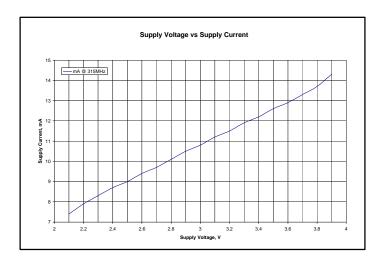

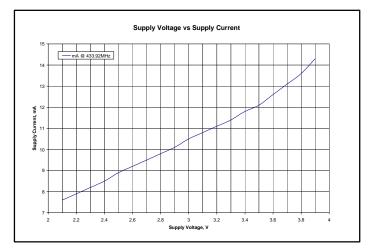

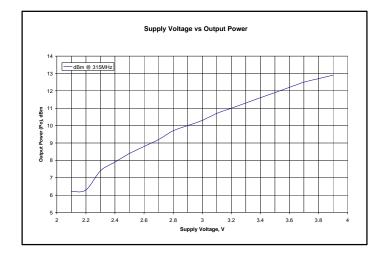

# **VIII. DC Electrical Characteristic**

(Typical values taken at  $V_{DD}$  = +3.0V,  $T_A$  = +25°C, unless otherwise noted)

| Characteristic             | Sym                | Notes | L                     | imit Values | 3    | Unit  | Test Condition                      |              |  |

|----------------------------|--------------------|-------|-----------------------|-------------|------|-------|-------------------------------------|--------------|--|

| Characteristic             | Sylli              | Notes | min                   | typ         | max  | Offic | rest conditions                     |              |  |

| Supply Voltage             | $V_{DD}$           |       | 2.1                   |             | 3.6  | V     |                                     |              |  |

| <b>Current Consumption</b> |                    |       |                       |             |      |       |                                     |              |  |

|                            |                    |       |                       | 0.2         | 1    |       | T <sub>A</sub> = +25 deg 0          | >            |  |

| Standby                    | I <sub>STDBY</sub> |       |                       | 120         | 300  | nA    | T <sub>A</sub> = +85 deg 0          | ;            |  |

|                            |                    |       |                       | 700         | 1600 |       | $T_A = +125 \text{ deg}$            | С            |  |

|                            |                    |       |                       | 2.9         | 4.3  |       | PA off, Data=0V (ASK)               |              |  |

|                            | I <sub>DD</sub>    | 1,4   |                       | 7           | 10.7 |       | 50% duty cycle (ASK)                | 315 Mhz Band |  |

| Supply                     |                    |       |                       | 10.5        | 17.1 | mA    | Data=+V <sub>DD</sub> (FSK and ASK) | 1            |  |

|                            |                    |       |                       | 3.3         | 4.8  |       | PA off, Data=0V (ASK)               |              |  |

|                            |                    |       |                       | 7.3         | 11.4 |       | 50% duty cycle (ASK)                | 433 Mhz Band |  |

|                            |                    |       |                       | 10          | 18.1 |       | Data=+V <sub>DD</sub> (FSK and ASK) |              |  |

| Digital Inputs             |                    |       |                       |             |      |       |                                     |              |  |

| Data Input Low             | V <sub>IL</sub>    |       |                       |             | 0.25 | V     |                                     |              |  |

| Data Input High            | V <sub>IH</sub>    |       | V <sub>DD</sub> -0.25 |             |      | V     |                                     |              |  |

| Max Input Current          | II                 |       |                       | 15.5        | 20   | μа    |                                     |              |  |

| Digital Outputs            |                    |       |                       |             |      |       |                                     |              |  |

| Output Voltage Low         | V <sub>OL</sub>    |       |                       |             | 0.25 | V     | Clkout, Load = 10pF                 |              |  |

| Output Voltage High        | V <sub>OH</sub>    |       | V <sub>DD</sub> -0.25 |             |      | V     | Clkout, Load = 10pF                 |              |  |

# IX. AC Electrical Characteristic

(Typical values taken at  $V_{DD} = +3.0V$ ,  $T_A = +25$ °C, unless otherwise noted)

|                                         |                    |       | Limit Values |                      |      |          |                             |                       |

|-----------------------------------------|--------------------|-------|--------------|----------------------|------|----------|-----------------------------|-----------------------|

| Parameter                               | Sym                | Notes | min          | typ                  | max  | Unit     | Test Condit                 | ions                  |

|                                         |                    |       |              | •                    |      |          |                             |                       |

| PLL Performance                         |                    |       |              |                      |      |          |                             |                       |

| VCO Gain                                | K <sub>VCO</sub>   |       |              | 280                  |      | MHz/V    |                             |                       |

|                                         |                    |       |              | -75                  |      |          | 315 Mhz Band                | Freq Offset =         |

| Phase Noise                             |                    |       |              | -74                  |      | dBc/Hz   | 433 Mhz Band                | 100kHz                |

| Filase Noise                            |                    |       |              | -98                  |      | UDC/11Z  | 315 Mhz Band                | Freq Offset = 1MHz    |

|                                         |                    |       |              | -98                  |      |          | 433 Mhz Band                | ried Oliset = HVII IZ |

| Loop BW                                 | BW                 |       |              | 300                  |      | kHz      |                             |                       |

| Reference Spur                          |                    |       |              | -40                  |      | dBc      |                             |                       |

| 2nd Harmonic                            |                    |       |              | -56                  |      | dBc      | 315 Mhz Band                |                       |

| ZIIG HAIIIIOIIIC                        |                    |       |              | -52                  |      | ubc      | 433 Mhz Band                |                       |

| 3rd Harmonic                            |                    |       |              | -56                  |      | dBc      | 315 Mhz Band                |                       |

| 3rd Harmonic                            |                    |       |              | -65                  |      | UDC      | 433 Mhz Band                |                       |

| Crystal                                 |                    |       |              |                      |      |          |                             |                       |

| Frequency Range                         | f <sub>REF</sub>   |       |              | f <sub>RF</sub> /32  |      | MHz      | fundamental mode, AT        |                       |

| Tolerance                               |                    | 3     |              | 50                   |      | ppm      |                             |                       |

| Internal Load Capacitance               |                    | 2     |              | 3                    |      | pF       |                             |                       |

| Clock Output Frequency                  | CLK <sub>OUT</sub> |       |              | F <sub>XTAL</sub> /N |      | MHz      | Determined by CLK1 and CLK2 |                       |

| System Characteristics                  |                    |       |              |                      |      |          |                             |                       |

| Frequency Range                         |                    |       | 300          |                      | 450  | MHz      |                             |                       |

|                                         |                    | 4     |              | 12.2                 | 16.1 | dBm      | $TA = -40C, V_{DD} = +3.6V$ | into 50Ω matched load |

| Output Power                            |                    |       | 6.1          | 10                   | 12.4 |          | TA = +25C, VDD = +3.0V      |                       |

|                                         |                    |       | 2.7          | 5.3                  |      |          | TA = +125C, VDD = +2.1V     | - IOau                |

| Start-up time                           | t <sub>ON</sub>    | 5     |              | 160                  |      | μs       | STDBY to                    | Tx                    |

| Rise Time                               | tr                 | 5     |              | 300                  |      | ns       |                             |                       |

| Mary Data Data                          |                    | _     |              | 20                   |      | Libraria | FSK (50% Duty               | Cycle)                |

| Max Data Rate                           |                    | 5     |              | 100                  |      | kbps     | ASK (50% Duty               |                       |

| F                                       |                    |       |              | 55                   |      | 1.1.1-   | 315 Mhz Band                | DE///0 01 444         |

| Frequency Deviation (FSK)               |                    |       |              | 80                   |      | kHz      | 433 Mhz Band                | DEV[20]=111           |

|                                         |                    |       |              | 35                   |      |          | 315 Mhz Band                | 014/                  |

| Transmit Efficiency                     |                    |       |              | 31                   |      | 0,       | 433 Mhz Band                | CW                    |

| $h=P_{OUT}/(V_{DD}xI_{DD})$             |                    | 4     |              | 27                   |      | %        | 315 Mhz Band                | 500/ data and         |

|                                         |                    |       |              | 25                   |      | 1        | 433 Mhz Band                | 50% duty cycle        |

| Power ON/OFF Ratio                      |                    |       |              | -77                  |      | dB       | ASK Mod                     | le                    |

| Frequency Stability vs. V <sub>DD</sub> | $\Delta df_{VDD}$  |       |              | 4                    |      | kHz      |                             |                       |

| Frequency Stability vs.<br>Temp         | $\Delta df_TA$     |       |              | TBD                  |      | kHz      | -40°C to +8                 | 5°C                   |

## Notes:

- 1. 10kHz, 50% duty cycle

- 2. Dependent on PCB parasitic trace capacitance and crystal parameters.

- Dependent on crystal parameters.

Transmit Efficiency, RF Output Power, and Supply Current are heavily dependent on proper output matching and PCB layout.

- 5. No Envelope Shaping.

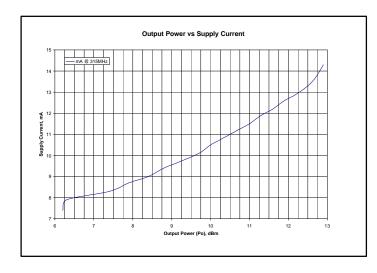

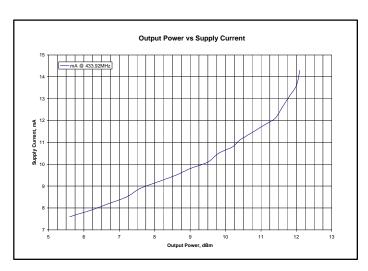

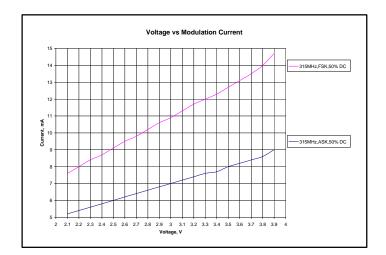

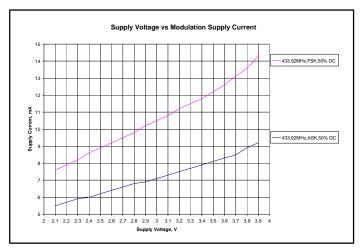

# X. Typical Operating Characteristics

## **XI. Theory of Operation**

#### Introduction

The TXC100 is a crystal-referenced transmitter designed to operate in the 315/433 MHz frequency spectrum. The carrier and crystal reference relation is given by:

$$f_C = f_{XTAL} * 32$$

It is capable of supporting OOK/ ASK and FSK data transmissions at 100kbps and 20kbps, respectively. The output power is adjustable from -10dBm to +10dBm thru a resistor at the ES<sub>OUT</sub> (pin 7). The FSK frequency deviation is programmable with up to eight different deviation values. The IC also provides a buffered clock output of the reference crystal for use by an external processor. The clock output is also programmable.

#### **Frequency Synthesizer**

The frequency synthesizer is simply a Phase Locked Loop circuit with a loop bandwidth of 300 kHz. The PLL contains a phase detector, charge pump, VCO, integrated loop filter, ÷32 clock divider, and crystal oscillator drive circuit. The internal PLL is self contained and requires no external components for filtering or dividing. Only a reference crystal is needed.

#### 50W Output Matching

When properly matched, the TXC100 can output up to  $\pm$ 12 dBm into a 50 $\Omega$  load. The output is an open-drain configuration which requires a pull-up inductor for proper internal biasing. The pull-up inductance serves to provide biasing for the power amplifier and is a high frequency choke to reduce unwanted coupling back into the power supply. Maximum power transfer occurs when the output is closely matched to 250 $\Omega$ . For best performance use wirewound inductors instead of chip inductors. Wirewound inductors provide lower insertion loss as opposed to chip inductors. See *Typical Application Circuit* (section IV) for topology and matching component values.

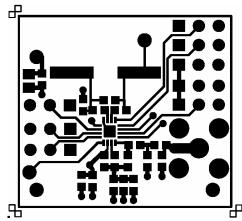

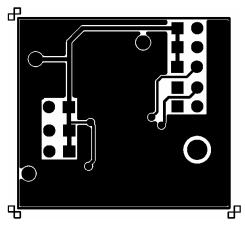

#### **PCB Layout Considerations**

PCB layout is critical to proper and consistent operation. Always use controlled impedance lines from the  $PA_{OUT}$  (pin 8). For a .062" thick FR4 board a  $50\Omega$  impedance line is approximately .110" wide. Component spacing is critical as well. Keep all output matching components as close together as possible to minimize stray inductance and capacitance that can detune the matching network. Keep ground planes at least a board thickness away from the signal output leading to the antenna or RF connector.

#### **Antenna Layout Considerations**

Most compact wireless designs have the need for a small, compact antenna. Typically, loop antennas are the ones of choice since they can be designed into tight spaces. Loop antenna design can become fairly lengthy and detailed discussion is beyond the scope of this datasheet. The object here is to provide a "rule of thumb" approach to achieve an appropriate starting point. Empirical data will provide the best path to take.

The circumference of the antenna should be less than  $\lambda/4$  so that the antenna appears inductive. For this, a series matching capacitor is used to tune out the inductance of the antenna, since the antenna appears inductive. The capacitor may be located at the feed point of the antenna or at the "grounded" end. The capacitor may be a variable type or several fixed values may be attempted until an optimal match is reached. The use of a good network analyzer is essential for proper matching and maximum power transfer. For additional information on antenna design see the <u>Application Notes</u> section of our website: <a href="http://www.rfm.com/corp/apnotes.htm">http://www.rfm.com/corp/apnotes.htm</a>.

# XII. Typical Test Circuit

# Package Dimensions – 3x3mm 16-pin TQFN Package

(all values in mm)

4441 Sigma Road Dallas, Texas 75244 (800) 704-6079 toll-free in U.S. and Canada Email: info@rfm.com

www.rfm.com www.wirelessis.com

© 2005 RF Monolithics, Inc. TXC100 012706