U74CBTLV3125 cmos ic

# LOW-VOLTAGE QUADRUPLE FET BUS SWITCH

#### DESCRIPTION

The **U74CBTLV3125** quadruple FET bus switch features independent line switches. Each switch is disabled when the associated output-enable (  $\overline{\rm OE}$  ) input is high.

The device is fully specified for partial-power-down applications using  $l_{\text{off}}$ . The  $l_{\text{off}}$  feature ensures that damaging current will not backflow through the device when it is powered down. The device has isolation during power off.

To ensure the high-impedance state during power up or power down,  $\overline{\rm OE}$  should be tied to V<sub>CC</sub> through a pullup resistor; the minimum value of the resistor is determined by the current-sinking capability of the driver.

#### ■ FEATURES

- \* 5-Ω Switch Connection Between Two Ports

- \* Standard '125-Type Pinout

- \* Isolation Under Power-Off Conditions

#### ■ ORDERING INFORMATION

| Ordering            | Dealsons            | Dealine  |           |  |

|---------------------|---------------------|----------|-----------|--|

| Lead Free           | Halogen Free        | Package  | Packing   |  |

| U74CBTLV3125L-P14-R | U74CBTLV3125G-P14-R | TSSOP-14 | Tape Reel |  |

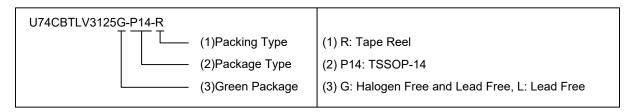

#### MARKING

www.unisonic.com.tw 1 of 6

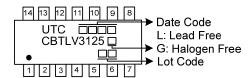

## ■ PIN CONFIGURATION

## ■ FUNCTION TABLE (each bus switch)

| INPUT OE | FUNCTION        |  |

|----------|-----------------|--|

| L        | A port = B port |  |

| Н        | Disconnect      |  |

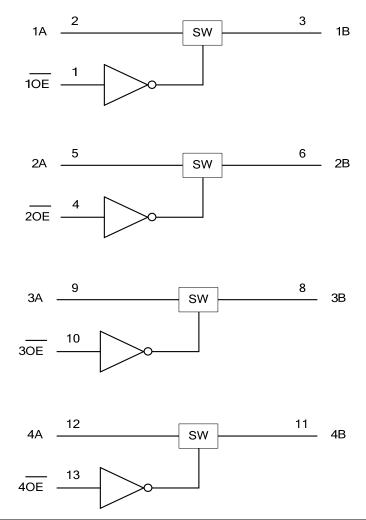

## ■ LOGIC DIAGRAM (positive logic)

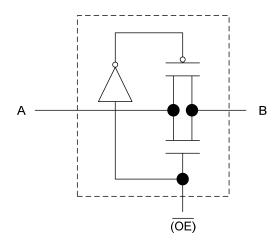

■ SIMPLIFIED SCHEMATIC (each FET switch)

U74CBTLV3125

## ABSOLUTE MAXIMUM RATING (Unless otherwise specified)(Note 1)

| PARAMETER                                | SYMBOL           | RATINGS    | UNIT |

|------------------------------------------|------------------|------------|------|

| Supply Voltage                           | $V_{CC}$         | -0.5~4.6   | V    |

| Input Voltage                            | VI               | -0.5~4.6   | V    |

| Continuous channel current               |                  | 128        | mA   |

| Input Clamp Current(V <sub>I/O</sub> <0) | I <sub>IK</sub>  | -50        | mA   |

| Storage Temperature                      | T <sub>STG</sub> | -65 ~ +150 | °C   |

Notes: 1. The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

## ■ RECOMMENDED OPERATING COMDITIONS (Unless otherwise specified)

| PARAMETER                    | SYMBOL          | TEST CONDITIONS            | MIN | TYP | MAX  | UNIT |

|------------------------------|-----------------|----------------------------|-----|-----|------|------|

| Supply Voltage               | Vcc             |                            | 2.3 |     | 3.6  | V    |

| High control input valte as  | V               | V <sub>CC</sub> =2.3V~2.7V | 1.7 |     |      | V    |

| High-control input voltage   | V <sub>IH</sub> | V <sub>CC</sub> =2.7V~3.6V | 2   |     |      | V    |

| Law control inner traditions | M               | V <sub>CC</sub> =2.3V~2.7V |     |     | 0.7  | V    |

| Low-control input voltage    | V <sub>IL</sub> | V <sub>CC</sub> =2.7V~3.6V |     |     | 8.0  | V    |

| Operating Temperature        | T <sub>A</sub>  |                            | -40 |     | +125 | °C   |

Note: All unused control inputs of the device must be held at V<sub>CC</sub> or GND to ensure proper device operation.

#### ■ THERMAL DATA

| PARAMETER           | SYMBOL        | RATINGS | UNIT |

|---------------------|---------------|---------|------|

| Junction to Ambient | $\theta_{JA}$ | 113     | °C/W |

## ■ STATIC CHARACTERISTICS (Unless otherwise specified)

| PARAMETER                              | SYMBOL               | TEST C                                                                 | ONDITIONS                 |                       | MIN                  | TYP | MAX  | UNIT |   |

|----------------------------------------|----------------------|------------------------------------------------------------------------|---------------------------|-----------------------|----------------------|-----|------|------|---|

| Digital Input Diode Voltage            | $V_{IK}$             | $V_{CC} = 3V$ , $I_I = -18mA$                                          |                           |                       |                      |     | -1.2 | V    |   |

| Input Leakage Current                  | I <sub>I</sub>       | V <sub>CC</sub> =3.6V, V <sub>I</sub> =V <sub>CC</sub> or              | r GND                     |                       |                      |     | ±1   | μΑ   |   |

| Power off Leakage Carrent              | I <sub>off</sub>     | $V_{CC}=0, V_I \text{ or } V_O=0 \text{ to}$                           | 4.5V                      |                       |                      |     | 10   | μΑ   |   |

| Quiosceut Supply Current               | I <sub>CC</sub>      | $V_{CC}$ =3.6V, $V_{I}$ = $V_{CC}$ c                                   | or GND, I <sub>O</sub> =0 |                       |                      |     | 10   | μΑ   |   |

| Additional Quiescent Supply<br>Current |                      | Control Input; V <sub>CC</sub> =3<br>Other inputs at V <sub>CC</sub> ( |                           | out at 3V,            |                      |     | 300  | μA   |   |

| Control input Capacitance              | Cı                   | Control Input; V <sub>O</sub> =3V or 0                                 |                           |                       | 2.5                  |     | рF   |      |   |

| I/O Capacitance (OFF)                  | C <sub>IO(OFF)</sub> | V <sub>O</sub> =3V or 0, OE=GND                                        |                           |                       | 7                    |     | рF   |      |   |

|                                        |                      | \                                                                      | \/_O                      | I <sub>I</sub> =64mA  |                      | 5   | 8    | Ω    |   |

|                                        |                      | V <sub>CC</sub> =2.3V                                                  | V <sub>I</sub> =0         | I <sub>I</sub> =24mA  |                      | 5   | 8    | Ω    |   |

| Desister between two nerts             |                      | Typ. at V <sub>CC</sub> =2.5V                                          | V <sub>I</sub> =1.7V      | I <sub>I</sub> =-15mA |                      | 27  | 40   | Ω    |   |

| Resistor between two ports             | R <sub>ON</sub>      |                                                                        | \/ =0\/                   | I <sub>I</sub> =64mA  |                      | 5   | 7    | Ω    |   |

|                                        |                      | V <sub>CC</sub> =3V                                                    | V <sub>CC</sub> =3V       | V <sub>I</sub> =0V    | I <sub>I</sub> =24mA |     | 5    | 7    | Ω |

|                                        |                      |                                                                        | V <sub>I</sub> =2.4V      | I <sub>I</sub> =-15mA |                      | 10  | 15   | Ω    |   |

Note: All typical values are at  $V_{CC}$ =3.3V,  $T_A$ =25°C, unless otherwise noted.

## ■ DYNAMIC CHARACTERISTICS (Unless otherwise specified)

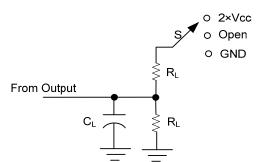

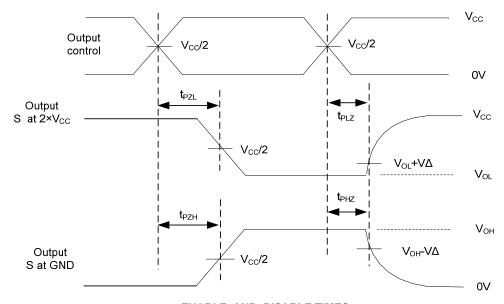

See Fig. 1 and Fig. 2 for test circuit and waveforms.

| PARAMETER                              | SYMBOL                                                 | TEST CONDITIONS            | MIN | TYP | MAX  | UNIT |

|----------------------------------------|--------------------------------------------------------|----------------------------|-----|-----|------|------|

| Francisco (A an D) to sutmit (D an A)  | 4 /4 /4 \                                              | V <sub>CC</sub> =2.5V±0.2V |     |     | 0.35 | ns   |

| From input (A or B) to output (B or A) | t <sub>pd</sub> (t <sub>PLH</sub> /t <sub>PHL)</sub>   | V <sub>CC</sub> =3.3V±0.3V |     |     | 0.25 | ns   |

| [                                      | 1 / 1 / 1                                              | V <sub>CC</sub> =2.5V±0.2V | 2   |     | 4.6  | ns   |

| From input (OE) to output (A or B)     | t <sub>en</sub> (t <sub>PZL</sub> /t <sub>PZH</sub> )  | V <sub>CC</sub> =3.3V±0.3V | 2   |     | 4.4  | ns   |

| [                                      | 4 /4 /4 \                                              | V <sub>CC</sub> =2.5V±0.2V | 1.1 |     | 3.9  | ns   |

| From input (OE) to output (A or B)     | t <sub>dis</sub> (t <sub>PLZ</sub> /t <sub>PHZ</sub> ) | V <sub>CC</sub> =3.3V±0.3V | 1.0 |     | 4.2  | ns   |

<sup>2.</sup> The package thermal impedance is calculated in accordance with JESD 51.

## TEST CIRCUIT AND WAVEFORMS

| V <sub>CC</sub> | $R_L$ | CL   | VΔ    |

|-----------------|-------|------|-------|

| 2.5V±0.2V       | 500   | 30pF | 0.15V |

| 3.3V±0.3V       | 500   | 50pF | 0.3V  |

| TEST                               | S     |

|------------------------------------|-------|

| $t_{PD}$                           | Open  |

| t <sub>PHZ</sub> /t <sub>PZH</sub> | GND   |

| t <sub>PLZ</sub> /t <sub>PZL</sub> | 2×Vcc |

Note: C<sub>L</sub> includes probe and jig capacitance.

$t_{\text{PLZ}}\,\text{and}\,\,t_{\text{PHZ}}\,\text{are}$  the same as  $t_{\text{dis}}.$

$t_{\text{PZL}}$  and  $t_{\text{PZH}}$  are the same as  $t_{\text{en}}.$

$t_{\text{PLH}}\, \text{and}\,\, t_{\text{PHL}}\, \text{are the same as}\,\, t_{\text{PD}}.$

Fig. 1 Load circuitry for switching times.

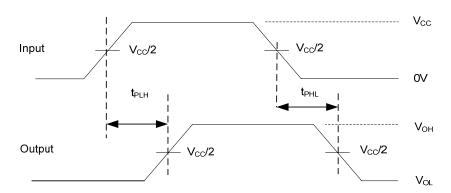

#### **PROPAGATION DELAY TIMES**

**ENABLE AND DISABLE TIMES**

Note: All input pulses are supplied by generators having the following characteristics:  $t_r$ ,  $t_f \le 2ns$ ; PRR  $\le 10MHz$ ; ZO= $50\Omega$ .

Fig. 2 Propagation delay from input(A) to output(B) and Output transition time.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.