UC3883 Preliminary CMOS IC

# HIGH PERFORMANCE CURRENT MODE PWM CONTROLLER WITH PEAK LOAD

#### DESCRIPTION

UTC **UC3883** is a highly integrated current mode PWM control IC optimized for high performance, low standby power and cost effective offline flyback converter applications.

PWM switching frequency at normal operation is internally fixed and is trimmed to tight range. At no load or light load condition, the IC operates in extended 'burst mode' to minimize switching loss. Lower standby power and higher conversion efficiency is thus achieved.

$V_{CC}$  low startup current and low operating current contribute to a reliable power on startup and low standby design with UTC UC3883.

UTC UC3883 offers complete protection coverage with auto-recovery including Cycle-by-Cycle current limiting (OCP), over load protection (OLP), over temperature protection (OTP) and  $V_{\text{CC}}$  under voltage lockout (UVLO). It also provides the over voltage protection (OVP) protections with latched shut down. Excellent EMI performance is achieved with UTC proprietary frequency shuffling technique.

The tone energy at below 20KHZ is minimized in the design and audio noise is eliminated during operation.

#### **■ FEATURES**

- $^{\star}$  Power on Soft Start Reducing MOSFET V<sub>DS</sub> Stress

- \* Frequency shuffling for EMI

- \* Extended Burst Mode Control For Improved Efficiency and Minimum Standby Power Design

- \* Ultra Low Operating Current at Light Load (typical 0.6mA)

- \* Audio Noise Free Operation

- \* Normal 65KHz Switching Frequency

- \* Frequency Triple for peak load (180KHz)

- \* Adjustable Overload Protection (OLP) delay time

- \* Comprehensive Protection Coverage

V<sub>CC</sub> Under Voltage Lockout with Hysteresis (UVLO)

Cycle-by-cycle over current threshold setting for constant output power limiting over universal input voltage range

Overload Protection (OLP) with autorecovery

External (if NTC resistor is connected at CT/RT pin) or internal (if capacitor is connected at CT/RT pin) Over Temperature Protection (OTP) with autorecovery.

V<sub>CC</sub> Over Voltage Protection (OVP) with latch shut down

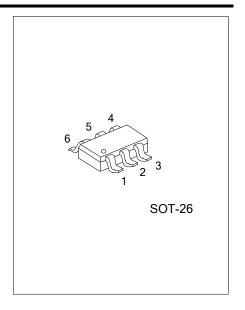

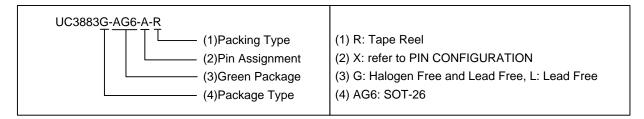

# **■ ORDERING INFORMATION**

| Ordering        | Number                 | Package | Dealing   |  |

|-----------------|------------------------|---------|-----------|--|

| Lead Free       | Lead Free Halogen Free |         | Packing   |  |

| UC3883L-AG6-A-R | UC3883G-AG6-A-R        | SOT-26  | Tape Reel |  |

| UC3883L-AG6-B-R | UC3883G-AG6-B-R        | SOT-26  | Tape Reel |  |

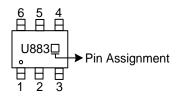

# **■ MARKING**

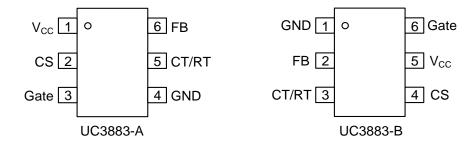

# ■ PIN CONFIGURATION

#### ■ PIN DESCRIPTION

| PIN NO. |         | DININIANE | DECODIDATION                                                                                                                               |  |

|---------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| UC3883A | UC3883B | PIN NAME  | DESCRIPTION                                                                                                                                |  |

| 1       | 5       | Vcc       | Power Supply                                                                                                                               |  |

| 2       | 4       | CS        | Current sense input                                                                                                                        |  |

| 3       | 6       | Gate      | Totem-pole gate driver output for power MOSFET                                                                                             |  |

| 4       | 1       | GND       | Ground                                                                                                                                     |  |

| 5       | 3       | CT/RT     | Dual functions pin. Connecting a NTC resistor to ground for over temperature control. Connecting a capacitor to ground sets OLP delay time |  |

| 6       | 2       | FB        | Feedback input pin. The PWM duty cycle is determined by voltage level into this pin and the current-sense signal at Pin 4.                 |  |

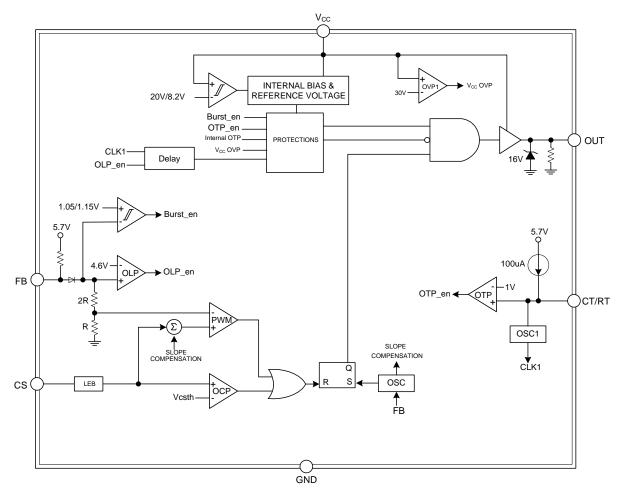

#### **■ BLOCK DIAGRAM**

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER                                 | SYMBOL           | RATINGS                     | UNIT |

|-------------------------------------------|------------------|-----------------------------|------|

| Supply Voltage                            | V <sub>cc</sub>  | -0.3 ~ 36                   | V    |

| Input Voltage to OUT Pin                  | V <sub>OUT</sub> | -0.3 ~ V <sub>CC</sub> +0.3 | V    |

| FB, CS, DEM                               |                  | -0.3 ~ 6                    | V    |

| Power Dissipation @ T <sub>A</sub> =+25°C | $P_D$            | 400                         | mW   |

| Junction Temperature                      | TJ               | +150                        | °C   |

| Operating Ambient Temperature             | T <sub>OPR</sub> | -40 ~ +125                  | °C   |

| Storage Temperature Range                 | T <sub>STG</sub> | -65 ~ <b>+</b> 150          | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# ■ RECOMMENDED OPERATING CONDITIONS

| PARAMETER                 | SYMBOL | RATINGS    | UNIT |

|---------------------------|--------|------------|------|

| Supply Voltage            | Vcc    | 9 ~ 28     | V    |

| Start up Resistor         |        | 0.86 ~ 4.4 | ΜΩ   |

| V <sub>CC</sub> Capacitor |        | 2.2 ~ 4.7  | μF   |

# **■ THERMAL DATA**

| PARAMETER           | SYMBOL        | RATING | UNIT |

|---------------------|---------------|--------|------|

| Junction to Ambient | $\theta_{JA}$ | 250    | °C/W |

# ■ **ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub>=15V, T<sub>A</sub>=25°C, unless otherwise specified)

| PARAMETER                     | SYMBOL                | TEST CONDITIONS                            | MIN  | TYP  | MAX  | UNIT     |  |

|-------------------------------|-----------------------|--------------------------------------------|------|------|------|----------|--|

| SUPPLY VOLTAGE                |                       |                                            |      |      |      |          |  |

| V (ON)                        |                       | For UC3883A                                | 18   | 20   | 22   | V        |  |

| Vcc (ON)                      | V <sub>CC(ON)</sub>   | For UC3883B                                | 13.8 | 15.3 | 16.8 | V        |  |

| V <sub>CC</sub> (OFF)         | V <sub>CC(MIN)</sub>  |                                            | 7.2  | 8.2  | 9.2  | <b>V</b> |  |

| Startup Current               | I <sub>STR</sub>      | V <sub>CC</sub> <v<sub>CC(ON)-0.5V</v<sub> |      | 1.5  | 5    | μΑ       |  |

| Operating Current             |                       | V <sub>FB</sub> =3V                        |      | 0.85 |      | mΑ       |  |

| Operating Current             | I <sub>OP</sub>       | V <sub>FB</sub> =Burst Level               |      | 0.5  |      | mΑ       |  |

| V <sub>CC</sub> OVP Threshold | $V_{CC(OVP)}$         |                                            | 28   | 30   | 32   | V        |  |

| OSCILLATOR & SWITCHING FREQUE | JENCY                 |                                            |      |      |      |          |  |

| Switching Frequency           | F <sub>(SW)</sub>     |                                            | 60   | 65   | 70   | KHz      |  |

| Temperature Stability         | F <sub>DT</sub>       | Guaranteed by Design                       |      |      | 10   | %        |  |

| Voltage Stability             | $F_{DV}$              |                                            |      |      | 10   | %        |  |

| Green Mode Frequency          | F <sub>(SW_GR)</sub>  |                                            | 20   |      |      | KHz      |  |

| Frequency Spreading Range     | Δ OSC                 |                                            | +9   |      | -9   | %        |  |

| Max.Duty Cycle                | DC <sub>MAX</sub>     | V <sub>FB</sub> =3.9V                      | 70   | 77   | 85   | %        |  |

| VOLTAGE FEEDBACK              |                       |                                            |      |      |      |          |  |

| Open Loop Voltage             | $V_{FB\_Open}$        |                                            | 5.00 | 5.40 | 5.80 | V        |  |

| OLP Level                     | $V_{FB\_OLP}$         |                                            |      | 4.60 |      | V        |  |

| OLP De-Bounce Time            | $T_{D\_OLP}$          | V <sub>FB</sub> >5V                        | 60   | 100  | 160  | mS       |  |

| Burst-Mode Enter FB Voltage   | $V_{FB-IN}$           |                                            |      | 1.05 |      | V        |  |

| Burst-Mode Quit FB Voltage    | $V_{FB-OUT}$          |                                            |      | 1.15 |      | V        |  |

| FB Pin Short Current          | I <sub>FB_SHORT</sub> |                                            |      | 130  |      | μA       |  |

# ■ ELECTRICAL CHARACTERISTICS (Cont.)

| PARAMETER                                              | SYMBOL                   | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT  |  |

|--------------------------------------------------------|--------------------------|------------------------------------------------------|------|------|------|-------|--|

| Current Sensing                                        | •                        | •                                                    |      |      |      | •     |  |

| Current Limiting Threshold Voltage                     | $V_{CS\_MAX}$            | Read cs pin in testmode                              |      | 0.88 |      | V     |  |

| Current Limiting Threshold Voltage with 0% Duty        | V <sub>CS_L</sub>        | Read cs pin in testmode                              |      | 0.43 |      | V     |  |

| Lead Edge Blanking Time                                | T <sub>LEB</sub>         | Guaranteed by Design                                 |      | 350  |      | ns    |  |

| SDSP(Secondary Diode Short<br>Protection) CS pin Level | V <sub>SCP</sub>         | Guaranteed by Design                                 |      | 1.32 |      | V     |  |

| CS DCOVP Level                                         | V <sub>CS_DCOVP</sub>    | Guaranteed by Design                                 |      | 0.44 |      | V     |  |

| Soft Start Time                                        |                          | Guaranteed by Design                                 |      | 10   |      | mS    |  |

| GATE DRIVE OUTPUT                                      |                          |                                                      |      |      |      |       |  |

| Output Low Level                                       | $V_{OL}$                 | V <sub>CC</sub> =15V, I <sub>OUT</sub> =-20mA        |      |      | 1    | V     |  |

| Output High Level                                      | V <sub>OH</sub>          | V <sub>CC</sub> =15V, I <sub>OUT</sub> =20mA         | 9    |      |      | V     |  |

| Rising Time                                            | t <sub>R</sub>           | 10% to 90% of V <sub>OUT</sub> , C <sub>L</sub> =1nF |      | 200  |      | nS    |  |

| Falling Time                                           | t <sub>F</sub>           | 90% to 10% of V <sub>OUT</sub> , C <sub>L</sub> =1nF |      | 60   |      | nS    |  |

| Out Clamping                                           | $V_{clamp}$              | V <sub>CC</sub> =20V                                 |      | 15   |      | V     |  |

| CT/RT Detection                                        |                          |                                                      |      |      |      |       |  |

|                                                        | $T_{d\_OLP}$             | C <sub>T</sub> =100nF                                |      | 1    |      |       |  |

| OLP De-bounce time                                     | T <sub>d_OLP_inner</sub> | No capacitor connected to CT/RT                      |      | 12   |      | S     |  |

| OTP Threshold Level                                    | V <sub>OTP</sub>         |                                                      | 0.92 | 0.98 | 1.04 | V     |  |

| Output current of CT/RT pin                            | I <sub>RT</sub>          |                                                      | 94   | 100  | 106  | μA    |  |

| OTP De-Bounce Time                                     | T <sub>OTP</sub>         | Guaranteed by Design                                 |      |      | 7    | Times |  |

| THERMAL SHUT DOWN                                      | THERMAL SHUT DOWN        |                                                      |      |      |      |       |  |

| OTP Threshold                                          |                          |                                                      |      | 150  |      | °C    |  |

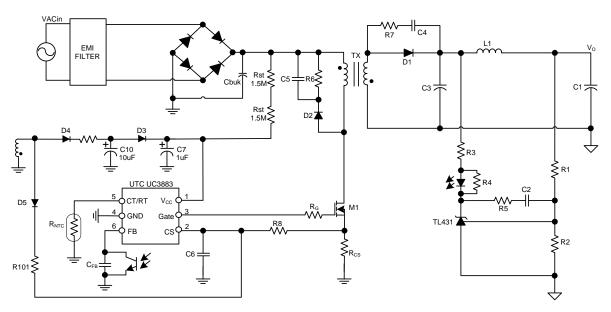

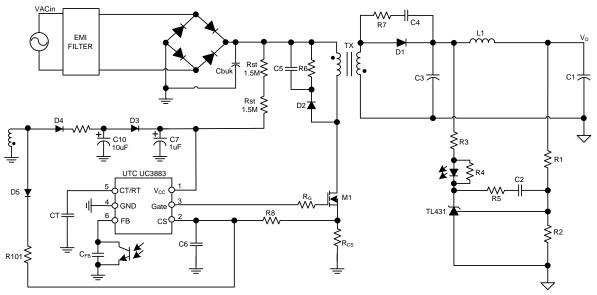

# ■ TYPICAL APPLICATION CIRCUIT

Fig.1 Application Circuit for ADJ-OTP

Fig.2 Application Circuit for ADJ-OLP-Debounce time(0~10s)

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.