UCD90320 SLUSCH8B - AUGUST 2016-REVISED MAY 2019

# UCD90320 32-Rail PMBus™ Power Sequencer and System Manager

#### **Features**

- Sequence, Monitor, and Margin 24 Voltage Rails Plus 8 Digital Rails

- Monitor and Respond to OV, UV, OC, UC, Temperature, Time-Out, and GPI-Triggered Faults

- Flexible Sequence-On and Off Dependencies, Delay Time, Boolean Logic, and GPIO Configuration to Support Complex Sequencing **Applications**

- Four Rail Profiles for Adaptive Voltage Identification (AVID) Voltage Regulator

- High-Accuracy Closed-Loop Margining

- Active Trim Function Improves Rail Output Voltage Accuracy

- Advanced Nonvolatile Event Logging To Assist System Debugging

- Single-Event Fault Log (100 entries)

- Peak Value Log

- Black Box Fault Log to Save Status of All Rails and I/O Pins at the First Fault

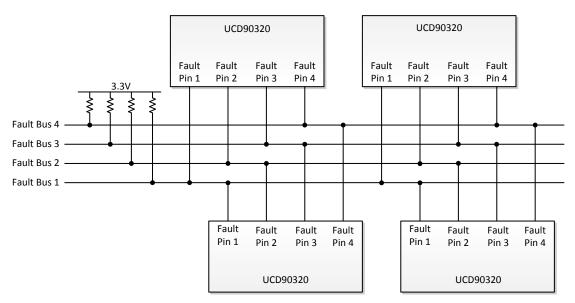

- Easily Cascade Up to 4 Power Sequencers and Take Coordinated Fault Responses

- Programmable Watchdog Timer and System Reset

- Pin-Selected Rail State

- PMBus™ 1.2 Compliant

## **Applications**

- Industrial and ATE

- Telecom and Networking Equipment

- Servers and Storage Systems

- Systems Requiring Sequencing and Monitoring of Multiple Power Rails

### 3 Description

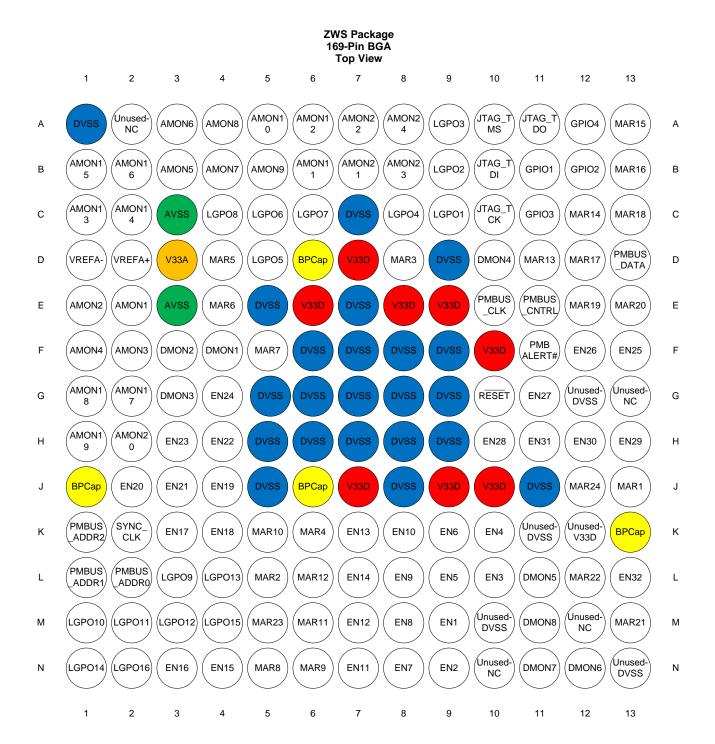

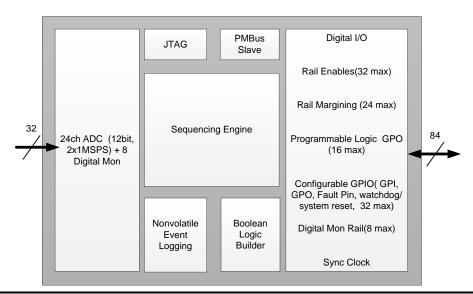

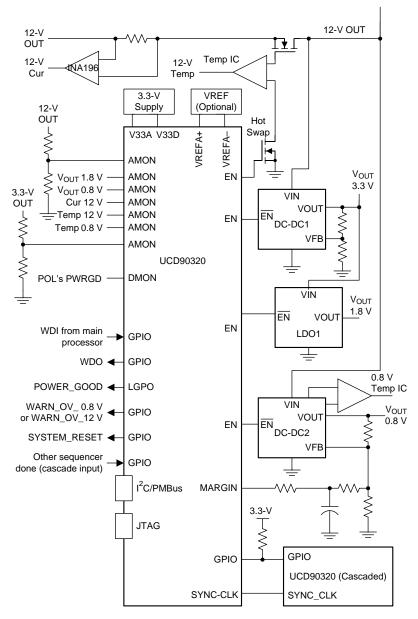

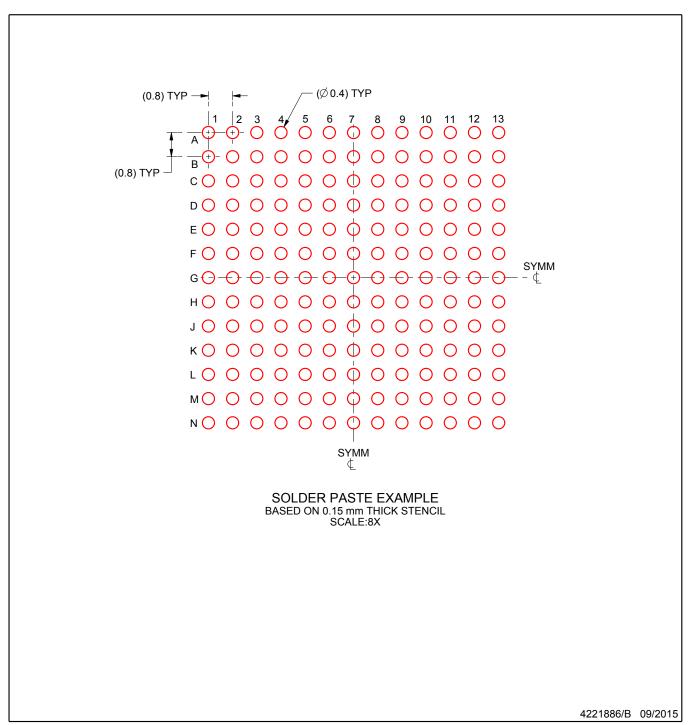

The UCD90320 device is a 32-rail PMBus™ addressable power sequencer and system manager in a compact 0.8-mm pitch BGA package.

The 24 integrated ADC channels (AMONx) monitor the power supply voltage, current, and temperature. Of the 84 GPIO pins, 8 can be used as digital monitors (DMONx), 32 to enable the power supply (ENx), 24 for margining (MARx), 16 for logical GPO, and 32 GPIs for cascading, and system function.

The 32 ENx pins and the 16 LGPOx pins can be configured to be active driven or open drain outputs.

Nonvolatile event logging preserves fault events after power dropout. Black box fault log feature preserves the status for all rails and I/O pins when the first fault occurs. The cascading feature offers convenient ways to manage up to 128 voltage rails through one SYNC\_CLK pin connection.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| UCD90320    | BGA (169) | 12.0 mm × 12.0 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

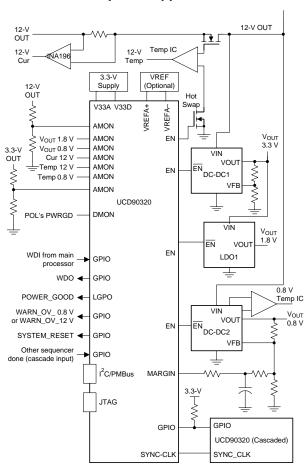

#### Simplified Application

## **Table of Contents**

| 1 | Features 1                                               |    | 8.3 Feature Description                              | . 14 |

|---|----------------------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                           |    | 8.4 Device Functional Modes                          | . 15 |

| 3 | Description 1                                            |    | 8.5 Device Configuration and Programming             | . 40 |

| 4 | Revision History2                                        | 9  | Application and Implementation                       | . 43 |

| 5 | Description Continued 3                                  |    | 9.1 Application Information                          | . 43 |

| 6 | Pin Configuration and Functions                          |    | 9.2 Typical Application                              | . 43 |

| 7 | Specifications8                                          | 10 | Power Supply Recommendations                         | . 46 |

| • | 7.1 Absolute Maximum Ratings 8                           | 11 | Layout                                               | . 46 |

|   | 7.2 ESD Ratings                                          |    | 11.1 Layout Guidelines                               | . 46 |

|   | 7.3 Recommended Operating Conditions                     |    | 11.2 Layout Example                                  | . 47 |

|   | 7.4 Thermal Information                                  | 12 | Device and Documentation Support                     | . 48 |

|   | 7.5 Electrical Characteristics                           |    | 12.1 Community Resources                             | . 48 |

|   | 7.6 Non-Volatile Memory Characteristics                  |    | 12.2 Receiving Notification of Documentation Updates | s 48 |

|   | 7.7 I <sup>2</sup> C/PMBus Interface Timing Requirements |    | 12.3 Trademarks                                      | . 48 |

|   | 7.8 Typical Characteristics                              |    | 12.4 Electrostatic Discharge Caution                 | . 48 |

| 8 | Detailed Description                                     |    | 12.5 Glossary                                        | . 48 |

| • | 8.1 Overview                                             | 13 | Mechanical, Packaging, and Orderable                 | 40   |

|   | 8.2 Functional Block Diagram                             |    | Information                                          | . 40 |

|   |                                                          |    |                                                      |      |

## 4 Revision History

| Changes from Revision A (Septemebr 2016) to Revision B                                                                                                                       | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Changed pin D8 From: MRGN3 To: MAR3 in the pinout image                                                                                                                      | 3    |

| <ul> <li>Added I<sub>REF</sub> specification to ANALOG-TO-DIGITAL CONVERTER (ADC) section of Electrical Characteristics</li> </ul>                                           | 9    |

| <ul> <li>Changed the values of V<sub>RESET</sub> From: MIN = 2.85 , TYP = 3, MAX = 3.15 To: MIN = 2, TYP = 2.3, MAX = 2.6 in t         Electrical Characteristics</li> </ul> |      |

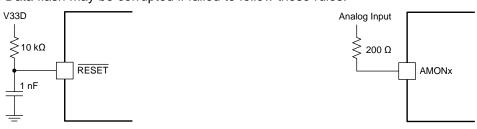

| • Changed 200 kΩ to 200 Ω in Figure 40                                                                                                                                       | 45   |

| Changes from Original (August 2016) to Revision A                                                                                                                            | Page |

| Changed data sheet status from Product Preview to Production Data                                                                                                            | 1    |

Product Folder Links: UCD90320

Submit Documentation Feedback

## 5 Description Continued

The FAULT pin coordinates the cascaded devices to take synchronized fault responses. The pin-selected rail states feature uses up to 3 GPIs to control up to eight user-defined power states. These states can implement system low-power modes as outlined in the *Advanced Configuration and Power Interface* (ACPI) specification.

The TI Fusion Digital Power<sup>™</sup> designer software is an intuitive PC-based graphic user interface (GUI) that can configure, store, and monitor all system operating parameters.

## 6 Pin Configuration and Functions

Copyright © 2016–2019, Texas Instruments Incorporated

Submit Documentation Feedback

### **Pin Functions**

| PIN            | PIN FUNCTIONS |     |                                                           |  |  |

|----------------|---------------|-----|-----------------------------------------------------------|--|--|

| NAME           | NO.           | 1/0 | DESCRIPTION                                               |  |  |

| ANALOG MONITOR |               |     |                                                           |  |  |

| AMON1          | E2            | ı   | Analog input monitor pin                                  |  |  |

|                |               |     |                                                           |  |  |

| AMON2          | E1            | l   | Analog input monitor pin                                  |  |  |

| AMON3          | F2            | l   | Analog input monitor pin                                  |  |  |

| AMON4          | F1            | l   | Analog input monitor pin                                  |  |  |

| AMON5          | B3            | l   | Analog input monitor pin                                  |  |  |

| AMON6          | A3            | l   | Analog input monitor pin                                  |  |  |

| AMON7          | B4            | l   | Analog input monitor pin                                  |  |  |

| AMON8          | A4            | l   | Analog input monitor pin                                  |  |  |

| AMON9          | B5            | l   | Analog input monitor pin                                  |  |  |

| AMON10         | A5            | I   | Analog input monitor pin                                  |  |  |

| AMON11         | B6            | I   | Analog input monitor pin                                  |  |  |

| AMON12         | A6            | I   | Analog input monitor pin                                  |  |  |

| AMON13         | C1            | I   | Analog input monitor pin                                  |  |  |

| AMON14         | C2            | I   | Analog input monitor pin                                  |  |  |

| AMON15         | B1            | I   | Analog input monitor pin                                  |  |  |

| AMON16         | B2            | I   | Analog input monitor pin                                  |  |  |

| AMON17         | G2            | I   | Analog input monitor pin                                  |  |  |

| AMON18         | G1            | I   | Analog input monitor pin                                  |  |  |

| AMON19         | H1            | I   | Analog input monitor pin                                  |  |  |

| AMON20         | H2            | I   | Analog input monitor pin                                  |  |  |

| AMON21         | B7            | I   | Analog input monitor pin                                  |  |  |

| AMON22         | A7            | I   | Analog input monitor pin                                  |  |  |

| AMON23         | B8            | I   | Analog input monitor pin                                  |  |  |

| AMON24         | A8            | I   | Analog input monitor pin                                  |  |  |

| ENABLE PINS    |               |     |                                                           |  |  |

| EN1(GPIO)      | M9            | I/O | Digital output, rail enable signal or GPIO <sup>(2)</sup> |  |  |

| EN2(GPIO)      | N9            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN3(GPIO)      | L10           | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN4(GPIO)      | K10           | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN5(GPIO)      | L9            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN6(GPIO)      | K9            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN7(GPIO)      | N8            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN8(GPIO)      | M8            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN9(GPIO)      | L8            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN10(GPIO)     | K8            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN11(GPIO)     | N7            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN12(GPIO)     | M7            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN13(GPIO)     | K7            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN14(GPIO)     | L7            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN15(GPIO)     | N4            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN16(GPIO)     | N3            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN17(GPIO)     | K3            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN18(GPIO)     | K4            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| EN19(GPIO)     | J4            | I/O | Digital output, rail enable signal or GPIO                |  |  |

| L1413(O110)    | J+            | 1/0 | Digital datpat, fall criable digital of Of 10             |  |  |

Product Folder Links: UCD90320

Submit Documentation Feedback

Copyright © 2016–2019, Texas Instruments Incorporated

<sup>(1)</sup> TI recommends placing a  $200-\Omega$  resistor between analog input and monitor pins. (2) GPIO: GPI, Command GPO, WDI, WDO, system reset (RESET), FAULT pin for multiple chip cascading

## Pin Functions (continued)

| PIN            |           |     |                                               |

|----------------|-----------|-----|-----------------------------------------------|

| NAME           | NO.       | I/O | DESCRIPTION                                   |

| EN20(GPIO)     | J2        | I/O | Digital output, rail enable signal or GPIO    |

| EN21(GPIO)     | J3        | I/O | Digital output, rail enable signal or GPIO    |

| EN22(GPIO)     | H4        | I/O | Digital output, rail enable signal or GPIO    |

| EN23(GPIO)     | H3        | I/O | Digital output, rail enable signal or GPIO    |

| EN24(GPIO)     | G4        | I/O | Digital output, rail enable signal or GPIO    |

| EN25(GPIO)     | F13       | I/O | Digital output, rail enable signal or GPIO    |

| EN26(GPIO)     | F12       | I/O | Digital output, rail enable signal or GPIO    |

| EN27(GPIO)     | G11       | I/O | Digital output, rail enable signal or GPIO    |

| EN28(GPIO)     | H10       | I/O | Digital output, rail enable signal or GPIO    |

| EN29(GPIO)     | H13       | I/O | Digital output, rail enable signal or GPIO    |

| EN30(GPIO)     | H12       | I/O | Digital output, rail enable signal or GPIO    |

| EN31(GPIO)     | H11       | I/O | Digital output, rail enable signal or GPIO    |

| EN32(GPIO)     | L13       | I/O | Digital output, rail enable signal or GPIO    |

| CLOSED-LOOP MA | RGIN PINS |     |                                               |

| MAR1(GPIO)     | J13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR2(GPIO)     | L5        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR3(GPIO)     | D8        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR4(GPIO)     | K6        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR5(GPIO)     | D4        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR6(GPIO)     | E4        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR7(GPIO)     | F5        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR8(GPIO)     | N5        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR9(GPIO)     | N6        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR10(GPIO)    | K5        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR11(GPIO)    | M6        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR12(GPIO)    | L6        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR13(GPIO)    | D11       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR14(GPIO)    | C12       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR15(GPIO)    | A13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR16(GPIO)    | B13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR17(GPIO)    | D12       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR18(GPIO)    | C13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR19(GPIO)    | E12       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR20(GPIO)    | E13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR21(GPIO)    | M13       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR22(GPIO)    | L12       | I/O | Closed-loop margin PWM output or General GPIO |

| MAR23(GPIO)    | M5        | I/O | Closed-loop margin PWM output or General GPIO |

| MAR24(GPIO)    | J12       | I/O | Closed-loop margin PWM output or General GPIO |

| GPIO AND CASCA | DING PINS |     |                                               |

| DMON1(GPIO)    | F4        | I/O | Digital input monitor pin or GPIO             |

| DMON2(GPIO)    | F3        | I/O | Digital input monitor pin or GPIO             |

| DMON3(GPIO)    | G3        | I/O | Digital input monitor pin or GPIO             |

| DMON4(GPIO)    | D10       | I/O | Digital input monitor pin or GPIO             |

| DMON5(GPIO)    | L11       | I/O | Digital input monitor pin or GPIO             |

| DMON6(GPIO)    | N12       | I/O | Digital input monitor pin or GPIO             |

| DMON7(GPIO)    | N11       | I/O | Digital input monitor pin or GPIO             |

## Pin Functions (continued)

| DIN               | PIN FUNCTIONS (CONTINUED)              |          |                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-------------------|----------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME              | NO.                                    | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                   | M11                                    | I/O      | Digital input manitar sin or CDIO                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| DMON8(GPIO)  GPIO | IVIII                                  | 1/0      | Digital input monitor pin or GPIO                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| GPIO1             | B11                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| GPIO2             | B12                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| GPIO3             | C11                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| GPIO4             | A12                                    | I/O      | GPIO                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| SYNC_CLK          | K2                                     | I/O      | Synchronization clock I/O for multiple chip cascading                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| LOGIC GPO PINS    |                                        |          | , ,                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| LGPO1(GPIO)       | C9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO2(GPIO)       | B9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO3(GPIO)       | A9                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO4(GPIO)       | C8                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO5(GPIO)       | D5                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO6(GPIO)       | C5                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO7(GPIO)       | C6                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO8(GPIO)       | C4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO9(GPIO)       | L3                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO10(GPIO)      | M1                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO11(GPIO)      | M2                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO12(GPIO)      | M3                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO13(GPIO)      | L4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO14(GPIO)      | N1                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO15(GPIO)      | M4                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| LGPO16(GPIO)      | N2                                     | I/O      | Logic GPO or GPIO                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PMBus COMM INT    | ERFACE                                 |          | <del>                                     </del>                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PMBUS_CLK         | E10                                    | I        | PMBus clock (must pull up to V33D)                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| PMBUS_DATA        | D13                                    | I/O      | PMBus data (must pull up to V33D)                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PMBALERT          | F11                                    | 0        | PMBus alert, active-low, open-drain output (must pull up to V33D)                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PMBUS_CNTRL       | E11                                    | I        | PMBus control pin                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| PMBUS_ADDR0       | L2                                     | I        | PMBus digital address input. Bit 0                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| PMBUS_ADDR1       | L1                                     | I        | PMBus digital address input. Bit 1                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| PMBUS_ADDR2       | K1                                     | I        | PMBus digital address input. Bit 2                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| JTAG              |                                        |          |                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| JTAG_TMS          | A10                                    | I        | Test mode select with internal pull-up                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| JTAG_TCK          | C10                                    | I        | Test clock with internal pull-up                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| JTAG_TDO          | A11                                    | 0        | Test data out with internal pull-up                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| JTAG_TDI          | B10                                    | I        | Test data in with internal pull-up                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| INPUT POWER, GR   | OUND, AND I                            | EXTERNAL | REFERENCE PINS                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RESET             | G10                                    | I        | Active-low device reset input. Pull up to V33D.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| V33A              | D3                                     | I        | Analog 3.3-V supply. Decouple from V33D to minimize the electrical noise contained on V33D from affecting the analog functions.                                                                                                                                                                                                                               |  |  |  |  |

| V33D              | D7, E6, E8,<br>E9, F10, J7,<br>J9, J10 | I        | Digital 3.3-V supply for I/O and some logic.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| BPCap             | D6, J1, J6,<br>K13                     | I        | Positive supply for most of the logic function, including the processor core and most peripherals. The voltage on this pin is 1.2 V and is supplied by the on-chip LDO. The BPCap pins should only be connected to each other and an external capacitor as specified in On-Chip Low Drop-Out (LDO) Regulator section of the Electrical Characteristics table. |  |  |  |  |

Product Folder Links: UCD90320

Submit Documentation Feedback

Copyright © 2016–2019, Texas Instruments Incorporated

## Pin Functions (continued)

| PIN                         |                                                                                                              | I/O |                                                                                                                                      |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                        | IAME NO.                                                                                                     |     | DESCRIPTION                                                                                                                          |  |  |  |

| AVSS                        | C3, E3                                                                                                       | I   | Analog ground. These are separated from DVSS to minimize the electrical noise contained on V33D from affecting the analog functions. |  |  |  |

| DVSS                        | A1, C7, D9,<br>E5, F9, H5,<br>H9, J5, J8,<br>J11, H6,<br>H7, H8, G5,<br>G6, G7, G8,<br>G9, F6, F7,<br>F8, E7 | I   | Ground reference for logic and I/O pins.                                                                                             |  |  |  |

| VREFA+                      | D2                                                                                                           | I   | (Optional) positive node of external reference voltage                                                                               |  |  |  |

| VREFA-                      | D1                                                                                                           | I   | (Optional) negative node of external reference voltage                                                                               |  |  |  |

| UNUSED PINS                 |                                                                                                              |     |                                                                                                                                      |  |  |  |

| UNUSED-NC A2, G13, M12, N10 |                                                                                                              | _   | Do not connect. Leave floating or isolated.                                                                                          |  |  |  |

| UNUSED-DVSS                 | G12, K11,<br>M10, N13                                                                                        | _   | Tie to DVSS.                                                                                                                         |  |  |  |

| UNUSED-V33D                 | K12                                                                                                          | _   | Tie to V33D.                                                                                                                         |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                       |                                                                                                                       | MIN  | MAX                     | UNIT |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|------|-------------------------|------|

| Cumply voltage        | V33D to DVSS                                                                                                          | 0    | 4                       | V    |

| Supply voltage        | V33A to AVSS                                                                                                          | 0    | 4                       | V    |

| Input voltage         | on all I/O pins except PMBUS_CNTRL, PMBALERT, MARGIN19, and MARGIN20, regardless of whether the device is powered (2) | -0.3 | 5.5                     | V    |

| Input voltage         | PMBUS_CNTRL, PMBALERT, MARGIN19, and MARGIN20                                                                         | -0.3 | V <sub>V33D</sub> + 0.3 | V    |

| Output current        | Maximum current per output pin                                                                                        |      | 25                      | mA   |

| Operating junction te | mperature, T <sub>J</sub>                                                                                             | TBD  | 150                     | °C   |

| Storage temperature   | , T <sub>stg</sub>                                                                                                    | -65  | 150                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those listed in the *Recommended Operating Conditions* table. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                  |                                | MIN  | NOM | MAX  | UNIT     |

|----------------------------------|--------------------------------|------|-----|------|----------|

| $V_{V33D}$                       | Cumply input voltage           | 3.15 | 3.3 | 3.63 | <b>V</b> |

| V <sub>V33A</sub> <sup>(1)</sup> | Supply input voltage           | 2.97 | 3.3 | 3.63 | <b>V</b> |

| T <sub>A</sub>                   | Operating ambient temperature  | -40  |     | 85   | ů        |

| $T_{C}$                          | Operating case temperature     | -40  |     | 90   | ů        |

| $T_J$                            | Operating junction temperature | -40  |     | 93   | °C       |

<sup>(1)</sup> It is recommended to connect the V33A pin and the V33D pin to the same supply. V33A must be powered before V33D if sourced from different supplies. There is no restriction on the ordering sequence for powering off.

<sup>(2)</sup> Applies to static and dynamic signals including overshoot.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                      |                                                           | UCD90320  |      |

|----------------------|-----------------------------------------------------------|-----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                             | ZWS (BGA) | UNIT |

|                      |                                                           | 169 PINS  |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance (2)(3)             | 41.6      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance (2)             | 15.8      | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance (2)(4)(5)            | 18.9      | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter <sup>(6)</sup> | 0.3       | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter (4)          | 20.3      | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance              | n/a       | °C/W |

- (1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

- Junction to ambient thermal resistance ( $\theta_{JA}$ ), junction to board thermal resistance ( $\theta_{JB}$ ), and junction to case thermal resistance ( $\theta_{JC}$ ) numbers are determined by a package simulator.

- (3)  $T_J = T_A + (P \times \theta_{JA})$ (4)  $T_J = T_{PCB} + (P \times \Psi_{JB})$ (5)  $T_J = T_B + (P \times \theta_{JB})^{(1)}$ (6)  $T_J = T_C + (P \times \Psi_{JT})$

#### 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                                                                       | TEST CONDITIONS                       | MIN                | TYP   | MAX                 | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------------|-------|---------------------|------|

| SUPPLY              | CURRENT                                                                                                         |                                       |                    |       |                     |      |

| I <sub>V33</sub>    | Supply Current                                                                                                  | $V_{V33D} = V_{V33A} = 3.3 \text{ V}$ |                    | 31.4  | 54.9                | mA   |

| ON-CHIP             | LOW DROP-OUT (LDO) REGULATOR                                                                                    |                                       |                    |       |                     |      |

| C <sub>LDO</sub>    | External filter capacitor size for internal power supply <sup>(1)</sup>                                         |                                       | 2.5                |       | 4                   | μF   |

| $V_{LDO}$           | LDO output voltage                                                                                              |                                       | 1.08               | 1.2   | 1.32                | V    |

| I <sub>INRUSH</sub> | Inrush current                                                                                                  |                                       | 50                 |       | 250                 | mA   |

| ANALOG              | -TO-DIGITAL CONVERTER (ADC) <sup>(2)(3)</sup>                                                                   | •                                     | •                  |       | ·                   |      |

| V33A                | ADC supply voltage                                                                                              |                                       | 2.97               | 3.3   | 3.63                | V    |

| AVSS                | ADC ground voltage                                                                                              |                                       |                    | 0     |                     | V    |

| C <sub>V33A</sub>   | Voltage reference decoupling capacitance<br>between V33A and AVSS (if using internal<br>reference) (4)          |                                       |                    | 1.01  |                     | μF   |

| $V_{REFA+}$         | Positive external voltage reference on<br>VREFA+ pin                                                            |                                       | 2.4                |       | 3                   | V    |

| $V_{REF-}$          | Negative external voltage reference on<br>VREF– pin                                                             |                                       | V <sub>AVSS</sub>  | AVSS  | 0.3                 | V    |

| I <sub>REF</sub>    | Current on VREF+ pin input                                                                                      | External V <sub>REF+</sub> = 3.3 V    |                    | 330.5 | 440                 | μΑ   |

| C <sub>REF</sub>    | Voltage reference decoupling capacitance between VREFA+ and VREFA- (if using external reference) <sup>(4)</sup> |                                       |                    | 1.01  |                     | μF   |

| \/                  | Analog input range, internal reference (5)                                                                      |                                       | 0                  |       | V33A                | V    |

| V <sub>ADCIN</sub>  | Analog input range, external reference (6)                                                                      |                                       | V <sub>VREFA</sub> |       | V <sub>VREFA+</sub> | V    |

| IL                  | ADC input leakage current                                                                                       |                                       |                    |       | 2                   | μΑ   |

| R <sub>ADC</sub>    | ADC equivalent input resistance                                                                                 |                                       |                    |       | 2.5                 | kΩ   |

| C <sub>ADC</sub>    | ADC equivalent input capacitance                                                                                |                                       |                    |       | 10                  | pF   |

- (1) Connect the capacitor as close as possible to pin D6.

- Total of two ADC channels run independently during normal operation.

- Total unadjusted error is the maximum error at any one code versus the ideal ADC curve. It includes offset error, gain error, and INL at any given ADC code.

- Two capacitors (1.0 µF and 0.01 µF) connected in parallel.

- Internal reference is connected directly between V33A and AVSS.

- External reference noise level must be under 12 bit (-74 dB) of full scale input, over input bandwidth, measured at VREFA+ VREFA+.

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                                                                    | TEST CONDITIONS        | MIN                         | TYP  | MAX                         | UNIT |

|--------------------|------------------------------------------------------------------------------|------------------------|-----------------------------|------|-----------------------------|------|

| F <sub>CONV</sub>  | ADC conversion rate (on each ADC channel) <sup>(1)</sup>                     |                        |                             | 1    |                             | MSPS |

| N                  | ADC resolution                                                               |                        |                             | 12   |                             | bits |

| _                  | Total unadjusted error, over full input rangea when using internal reference |                        |                             | ±10  | ±30                         | LSB  |

| E <sub>T</sub>     | Total unadjusted error, over full input range when using external reference  |                        |                             | ±2.5 | ±4                          | LOD  |

| DIGITAL IN         | IPUTS AND OUTPUTS (GPIO, Logic GPO, E                                        | N, AND MARGIN PINS)    |                             |      |                             |      |

| $V_{IH}$           | I/O high-level input voltage <sup>(7)</sup>                                  |                        | 0.65 ×<br>V <sub>V33D</sub> |      | 5.5                         | V    |

| $V_{IL}$           | I/O low-level input voltage                                                  |                        | 0                           |      | 0.35 ×<br>V <sub>V33D</sub> | V    |

| $V_{HYS}$          | I/O input hysteresis                                                         |                        | 0.2                         |      |                             | V    |

| $V_{OH}$           | I/O high-level output voltage                                                |                        | 2.4                         |      |                             | V    |

| $V_{OL}$           | I/O low-level output voltage                                                 |                        |                             |      | 0.4                         | V    |

| $I_{OH}$           | High-level source current                                                    | $V_{OH} = 2.4 V^{(8)}$ | 4                           |      |                             | mA   |

| $I_{OL}$           | Low-level sink current                                                       | $V_{OL} = 0.4 V^{(8)}$ | 4                           |      |                             | mA   |

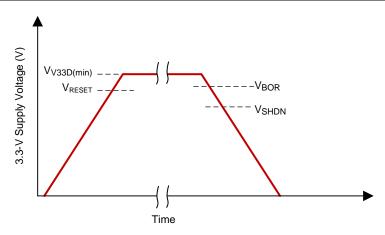

| RESET AN           | D BROWNOUT                                                                   |                        |                             |      |                             |      |

| V33DSlew           | Minimum V33D slew rate between 2.8 V and 3.2 V                               |                        | 0.1                         |      |                             | V/ms |

| $V_{RESET}$        | Supply voltage at which device comes out of reset                            |                        | 2                           | 2.3  | 2.6                         | V    |

| $V_{BOR}$          | Supply voltage at which device enters brownout                               |                        | 2.93                        | 3.02 | 3.11                        | V    |

| V <sub>SHDN</sub>  | Supply voltage at which device shuts down                                    |                        | 2.7                         | 2.78 | 2.87                        | V    |

| t <sub>RESET</sub> | Minimum low-pulse width needed at RESET pin                                  |                        |                             | 250  |                             | ns   |

| t <sub>IRT</sub>   | Internal reset time (9)                                                      |                        |                             | 9    | 11.5                        | ms   |

PMBUS\_CNTRL,  $\overline{\text{PMBALERT}}$ , MARGIN19 and MARGIN20 pins have  $V_{V33D}$  + 0.3 V as maximum input voltage rating.

#### 7.6 Non-Volatile Memory Characteristics

over operating free-air temperature range (unless otherwise noted)

| over operating need an temperature range (amous enterwise noted) |                                                                         |                               |         |         |        |  |  |

|------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------|---------|---------|--------|--|--|

|                                                                  | PARAMETER                                                               | TEST CONDITIONS               | MIN     | TYP MAX | UNIT   |  |  |

| CONFIGU                                                          | RATION FLASH MEMORY                                                     |                               |         |         |        |  |  |

| PE <sub>CYC</sub>                                                | Number of program and erase cycles before failure                       |                               | 100,000 |         | Cycles |  |  |

| T <sub>RET</sub>                                                 | Data retention                                                          | -40°C ≤ T <sub>J</sub> ≤ 85°C | 20      |         | Years  |  |  |

| FAULT AN                                                         | ND EVENT LOGGING EEPROM                                                 |                               |         |         |        |  |  |

| EPE <sub>CYC</sub>                                               | Number of mass program and erase cycles of a single word before failure |                               | 500,000 |         | Cycles |  |  |

| ET <sub>RET</sub>                                                | Data retention                                                          | –40°C ≤ T <sub>J</sub> ≤ 85°C | 20      |         | Years  |  |  |

Io specifications reflect the maximum current where the corresponding output voltage meets the V<sub>OH</sub>/V<sub>OL</sub> thresholds. If power-loss or brown-out event occurs during an EEPROM program or erase operation, and EEPROM needs to be repaired (which is a rare case), the internal reset time may be longer.

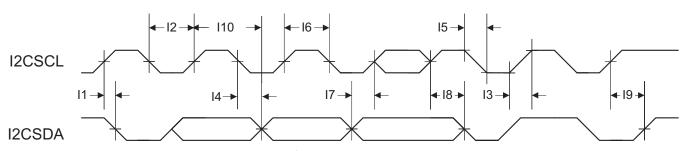

## 7.7 I<sup>2</sup>C/PMBus Interface Timing Requirements

|     |                       |                                                  | MIN | NOM   | MAX                | UNIT |

|-----|-----------------------|--------------------------------------------------|-----|-------|--------------------|------|

| l1  | t <sub>(HD:STA)</sub> | Start condition hold time                        | 450 |       |                    | ns   |

| 12  | t <sub>(LOW)</sub>    | Clock low period <sup>(1)</sup>                  | 450 |       |                    | ns   |

| 13  | t <sub>r</sub>        | Clock rise time and data rise time (2)           |     |       | See <sup>(2)</sup> | ns   |

| 14  | t <sub>(HD:DAT)</sub> | Data hold time                                   |     | 25    |                    | ns   |

| 15  | t <sub>f</sub>        | Clock fall time and data fall time (3)           |     | 112.5 | 125                | ns   |

| 16  | t <sub>(HIGH)</sub>   | Clock high time                                  | 300 |       |                    | ns   |

| 17  | t <sub>(SU:DAT)</sub> | Data setup time                                  | 225 |       |                    | ns   |

| 18  | t <sub>(SU:STA)</sub> | Start condition setup time (repeated start only) | 450 |       |                    | ns   |

| 19  | t <sub>(SU:STO)</sub> | Stop condition setup time                        | 300 |       |                    | ns   |

| l10 | t <sub>(DV)</sub>     | Data valid                                       |     | 25    |                    | ns   |

- (1) PMBus host must support clock stretching per PMBus Power System Management Protocol Specification Part I General Requirements, Transport and Electrical Interface, Revision 1.2, Section 5.2.6.

- (2) Because the I2CSCL signal and the I2CSDA signal operate as open-drain-type signals, which the controller can actively drive only "Low", the time that either signal takes to reach a high level depends on external signal capacitance and pull-up resistor values.

- (3) Specified at a nominal 50-pF load.

Figure 1. I<sup>2</sup>C/PMBus Timing Diagram

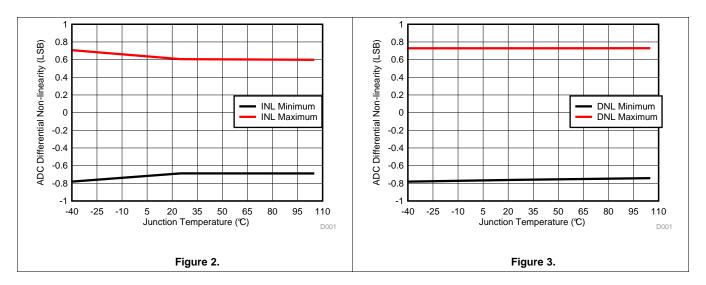

## 7.8 Typical Characteristics

## 8 Detailed Description

#### 8.1 Overview

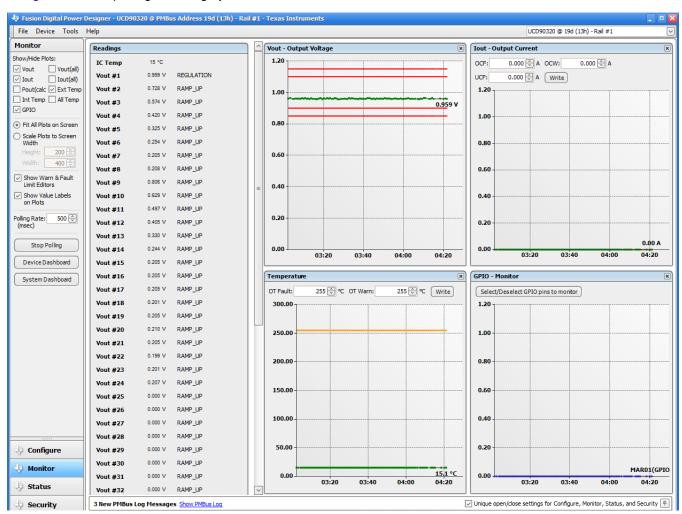

Electronic systems such as CPU, DSP, microcontroller, FPGA, and ASIC can have multiple voltage rails and require certain power-ON and power-OFF sequences in order to function correctly. The UCD90320 device can control up to 32 voltage rails and ensure correct power sequences during normal condition and fault conditions.

In addition to sequencing, the device can continuously monitor rail voltages, currents, temperatures, fault conditions, and report the system health information to upper computers through a PMBus interface, improving long term reliability.

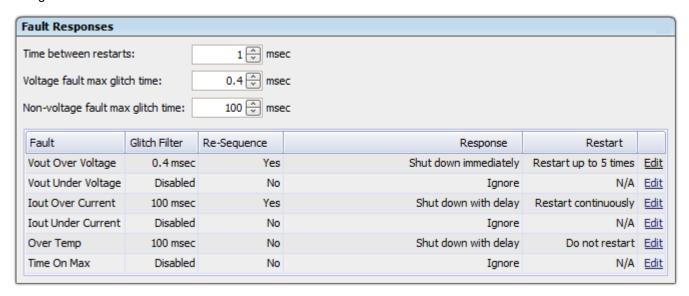

The device can protect electronic systems by responding to power system faults. The fault responses are conveniently configured by users through *Fusion Digital Power Designer* software. Fault events are stored in on-chip nonvolatile flash memory in order to assist failure analysis. A Black Box Fault Log feature stores comprehensive system statuses at the moment when the first fault occurs. With this feature, failure analysis can be more effective.

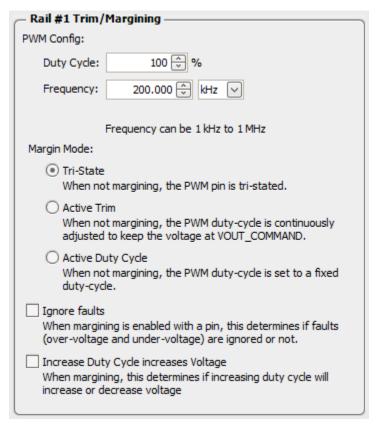

System reliability can be improved through four-corner testing during system verification. During four-corner testing, each voltage rail is required to operate at the minimum and maximum output voltages, commonly known as margining. The device can perform accurate closed-loop margining for up to 24 voltage rails. During normal operation, UCD90320 can also actively trim DC output voltages using the same margining circuitry. This feature allows tuning rail voltages to an optimal level.

The UCD90320 device supports control environments via both PMBus interface and pin-based interface. The device functions as a PMBus slave. It can communicate with upper computers with PMBus commands, and control voltage rails accordingly. In addition to rail enable (EN) pins, up to 32 GPIO pins can be configured as GPOs and directly controlled by PMBus commands. The device can be controlled by up to 32 GPIO configured GPI pins. The GPIs can be used as fault inputs which can shut down rails. The GPIs can be also used as Boolean logic input to control the 16 Logic GPO outputs. Each of the 16 Logic GPO pins has a flexible Boolean logic builder. Input signals of the Boolean logic builder can include GPIs, other GPOs, and selectable system flags such as POWER\_GOOD, faults, warnings, and so forth. A simple state machine is also available for each Logic GPO pin.

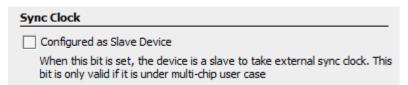

The device provides additional features such as cascading, pin-selected states, system watchdog, system reset, run time clock, peak value log, reset counter, and so forth. Cascading feature offers convenient ways to cascade up to 4 UCD90320 devices and manage up to 128 voltage rails through one SYNC\_CLK pin connection. Pin-selected states feature allows users to define up to 8 rail states. These states can implement system low-power modes as set out in the *Advanced Configuration and Power Interface (ACPI)* specification. The *Feature Description* section of this datasheet describes other device features.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

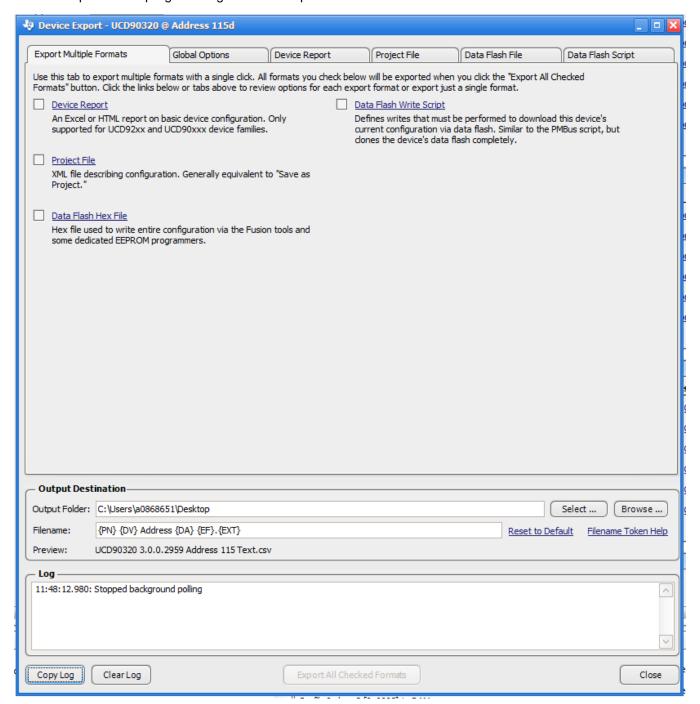

#### 8.3.1 TI Fusion Digital Power Designer software

The Texas Instruments Fusion Digital Power Designer software allows the user to configure the device. This PC-based graphic user interface (GUI) offers an intuitive I<sup>2</sup>C and PMBus interface to the device. The *Fusion Digital Power Designer* software allows the design engineer to configure the system operating parameters for the application without directly using PMBus commands, store the configuration to on-chip nonvolatile memory, and observe system status (voltage, current, temperature, faults, and so forth). This data sheet references the Fusion Digital Power Designer software and many sections include screenshots. Download the *Fusion Digital Power Designer* software from TI here. After configuration, the device can perform all designed functions independently without further need for the Fusion GUI.

#### 8.3.2 PMBUS Interface

PMBus refers to a serial interface specifically designed to support power management. The PMBus interface is based on the SMBus interface that is built on the I²C physical specification. The UCD90320 device supports revision 1.2 of the PMBus standard. Wherever possible, standard PMBus interface commands support the function of the device. Unique features of the device are defined to configure or activate via the MFR\_SPECIFIC commands. These commands are defined in the, *UCD90320 Sequencer and System Health Controller PMBUS Command Reference*. The most current UCD90320 PMBus™ Command Reference can be found within the TI Fusion Digital Power Designer software through the Help Menu (Help, Documentation & Help Center, Sequencers tab, Documentation section).

This data sheet makes frequent mention of the PMBus specification. Specifically, this document is *PMBus Power System Management Protocol Specification Part II – Command Language*, Revision 1.2, dated 6 September 2010. The specification is published by the Power Management Bus Implementers Forum and is available from www.pmbus.org.

The UCD90320 device meets all of the requirements of the *Compliance* section of the PMBus specification. The firmware complies with the SMBus 1.2 specification, including support for the SMBus ALERT function. The hardware supports either 100-kHz or 400-kHz PMBus operation.

#### 8.3.3 Rail Setup

Power rails are defined under the **Pin Assignment** tab, as shown in Figure 4. Click corresponding buttons to add or delete a rail. After a rail is added, AMON, DMON, EN, and MARGIN pins can be assigned to the rail. UCD90320 has 24 AMON pins, 8 DMON pins, 32 EN pins, and 24 MARGIN pins, thus can support up to 32 rails.

| Rails - M | Ionitors & Enable | s             |                                 |                                 |                |                      | 5 of 24 Assigned               |

|-----------|-------------------|---------------|---------------------------------|---------------------------------|----------------|----------------------|--------------------------------|

|           | Rail Name         | Voltage       | Temperature                     | Current                         | Enable         | Trim/Margin PWM      | Actions                        |

| Rail #1   | Rail #1           | Pin E1 MON 01 | <click assign="" to=""></click> | <click assign="" to=""></click> | Pin M9 EN 01   | Pin J13 PWM 01       | <u>Delete</u> <u>Configure</u> |

| Rail #2   | Rail #2           | Pin E2 MON 02 | <click assign="" to=""></click> | <click assign="" to=""></click> | Pin N9 EN 02   | <u>Pin L5 PWM 02</u> | Delete Configure               |

| Rail #3   | Rail #3           | Pin F2 MON 03 | <click assign="" to=""></click> | <click assign="" to=""></click> | Pin L 10 EN 03 | Pin D8 PWM 03        | <u>Delete</u> <u>Configure</u> |

| Rail #4   | Rail #4           | Pin F1 MON 04 | <click assign="" to=""></click> | <click assign="" to=""></click> | Pin K10 EN 04  | Pin K6 PWM 04        | Delete Configure               |

| Rail #5   | Rail #5           | Pin B3 MON 05 | <click assign="" to=""></click> | <click assign="" to=""></click> | Pin L9 EN 05   | Pin D4 PWM 05        | Delete Configure               |

| Add Rai   | <u>il</u>         |               |                                 |                                 |                |                      |                                |

Figure 4. Fusion Digital Power Designer software Rail Setup Window (Configure ▶ Pin Assignment tab)

#### 8.4 Device Functional Modes

#### 8.4.1 Rail Monitoring Configuration

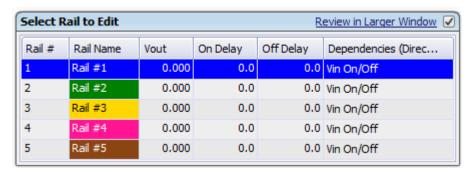

After rails are set up in the **Pin Assignment** tab, they are visible under the **Vout Config** tab, as shown in Figure 5. The initial voltage values are 0.

Figure 5. Rail Selection Window (Rail Configuration)

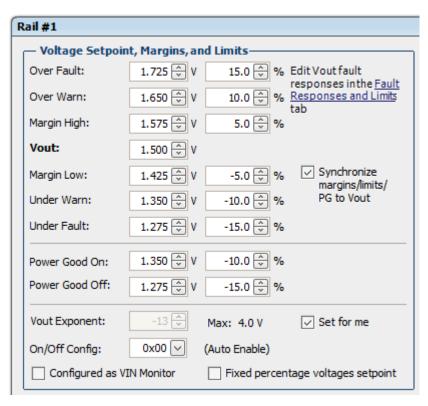

Configure the voltage monitoring parameters of the selected rail under the **Vout Config** tab. Figure 6 shows the configuration window..

Figure 6. Rail Voltage Configuration Window (Rail Configure, Vout Config tab)

When a AMON pin is assigned in Figure 4 to monitor the voltage of a particular a rail, a fault or warn event occurs when the monitored rail voltage exceeds the voltage window defined by the *Over and Under Warn/Fault* thresholds. When a fault is detected, the device responds with user-defined actions. See also the *Fault Responses Configuration* section for more details.

Rail Profile is composed of a group of nine thresholds set by: VOUT\_COMMAND, VOUT\_OV\_FAULT\_LIMIT, VOUT\_OV\_WARNING\_LIMIT, VOUT\_MARGIN\_HIGH, POWER\_GOOD\_ON, VOUT\_MARGIN\_LOW, POWER\_GOOD\_OFF, VOUT\_UV\_WARNING\_LIMIT and VOUT\_UV\_FAULT\_LIMIT.

### **Device Functional Modes (continued)**

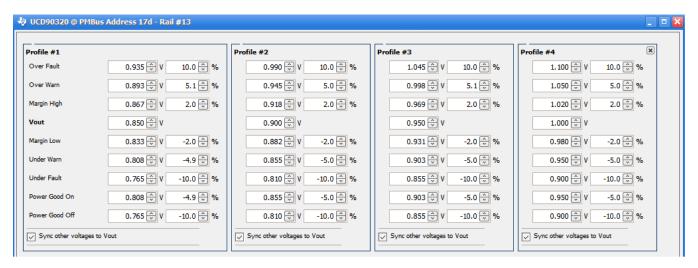

Figure 7. Rail Profile Configurations (Rail Config ▶ Edit Rail Profiles)

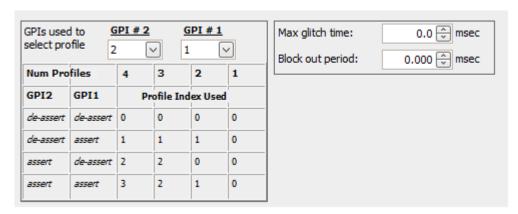

The device offers 50 individual profiles shared among all 24 AMON voltage rails. Each AMON voltage rail can have at least one but no more than 4 profiles. The profiles are controlled by 2 GPIs as shown in Figure 8. A programmable block-out period is used to block all voltage related faults on the given rail when profile is changed.

Figure 8. Rails Profile Selection Through GPIs (Rail Config ▶ Edit Rail Profiles)

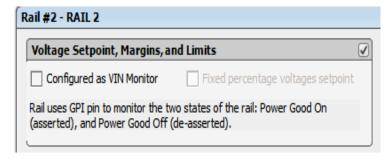

The device supports digital monitor. If a DMON pin is assigned in Figure 7 to monitor POWER\_GOOD of POL. The DMON rail has no rail profile. If the DMON input is logic HIGH, the rail is POWER\_GOOD, otherwise the rails has UV fault or warns and is at POWER\_NOT\_GOOD.

Figure 9. Digital Rail Configuration Window

### **Device Functional Modes (continued)**

Vout Exponent defines the voltage value resolution according to PMBus linear data format. Fusion Digital Power Designer software can automatically select optimal Vout Exponent value to cover the required voltage range with the finest possible resolution. For more information regarding PMBus linear data format, refer to PMBus specification mentioned at the beginning of this section.

On/Off Config defines a rail turn-ON and turn-OFF command:

- None (Auto enable). Rail always seeks to turn-ON as long as UCD90320 is powered.

- CONTROL Pin Only. Rail seeks to turn-ON and turn-OFF according to PMBus CONTROL line (asserted/de-asserted).

- OPERATION Only. Rail seeks to turn-ON and turn-OFF according to PMBus OPERATION command (On/Off).

- Both CONTROL pin and OPERATION. Rail seeks to turn-ON when CONTROL pin is asserted, AND PMBus OPERATION command sets the rail to On. Rail seeks to turn-OFF when OPERATION command sets the rail to OFF, OR when CONTROL line is de-asserted.

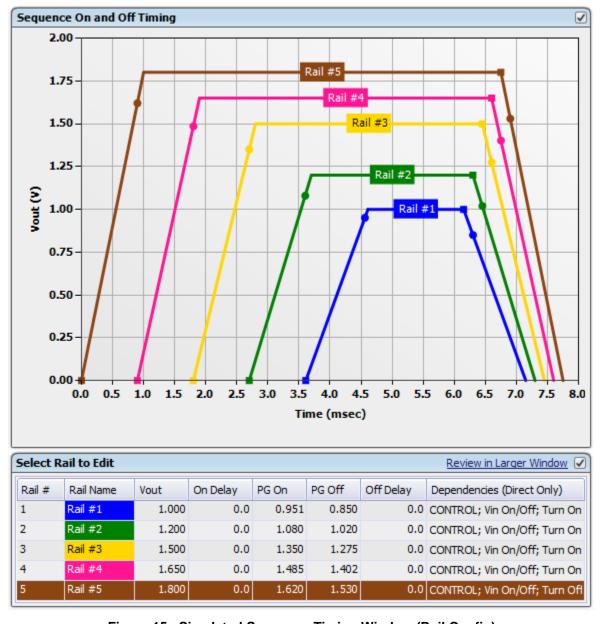

After receiving a turn ON or turn OFF command, a rail examines a series of conditions before asserting or deasserting its EN pin. Conditions include *Rail Sequence On/Off Dependency*, *GPI Sequence On/Off Dependency*, *Turn-On/Off Delay*, as shown in *Rail Sequence Configuration* section.

Fixed percentage voltages setpoint, when checked, configures a rail into adaptive voltage scaling technology (AVS) mode. The *Vout Setpoint* can be dynamically set by PMBus during operation in order to achieve energy saving. The rail warn and fault voltage thresholds maintain fixed ratios with respect to the *Vout Setpoint*. Due to the fact that the power supply and UCD90320 device may not change *Vout Setpoint* simultaneously or with the same slew rate, the device takes the following steps to avoid false-triggering warn and fault. If the new *Vout Setpoint* is higher than the current *Vout Setpoint*, the OV warn and fault thresholds are immediately set to their respective new levels. Other thresholds are initially maintained, and then increase by 20-mV step size in every 400 μs until the new levels are reached. If the new *Vout Setpoint* is lower than the current *Vout Setpoint*, the UV warn and fault and Power Good On and Power Good Off thresholds are immediately set to their respective new levels. Other thresholds are initially maintained, and then decrease by 20-mV step size every 400 μs until the new levels are reached. Table 1 summarizes the thresholds adjustment scheme in AVS mode.. This feature is not available for DMON pin.

Table 1. Thresholds Adjustment Scheme in AVS Mode

| TRANSITION                                 | IMMEDIATE UPDATE                                                 | ADJUSTMENT <sup>(1)</sup>                                                                          |

|--------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| New Vout Setpoint to Current Vout Setpoint | OV fault and warn notification                                   | UV fault and warn notification, Margin High<br>and Margin Low, Power Good On and Power<br>Good Off |

| ·                                          | UV fault and warn notification, Power Good On and Power Good Off | OV fault and warn notification, Margin High and Margin Low,                                        |

(1) Gradual adjustment towards new levels with 2-0mV step size and 400-µs step interval

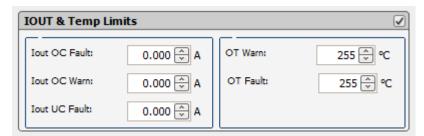

Current and temperature monitoring parameters of the selected rail can be configured under the **Fault Responses and Limits** tab. First select a rail in the top-right corner of the *Fusion Digital Power Designer* software, and then edit the current and temperature monitoring parameters as shown in Figure 10.

Figure 10. Current and Temperature Limits Configuration Window (Rail Config ► IOUT and Temperature Limits)

Each rail has a Power Good status determined by the following rules.

- If rail voltage is monitored by an AMON pin, the *Power Good* status is solely determined by *Power Good On* and *Power Good Off* thresholds as shown in Figure 6. A rail is given *Power Good* status if its rail voltage is above the *Power Good On* threshold. Otherwise, the rail is given *Not Power Good* status if the rail voltage is below the *Power Good Off* threshold. The rail remains in the current status if its voltage is neither above *Power Good On* nor below *Power Good Off* thresholds.

- If rail voltage is not monitored by a AMON or DMON pin, the *Power Good* status is determined by the turn-ON and turn-OFF eligibility of the rail. A rail is immediately given *Power Good* status when the rail meets all the turn-on conditions set by the user, such as *On and Off Config*, dependencies and delays. Similarly, a rail is immediately given *Not Power Good* status when the rail meets all the turn-off conditions set by the user. The behavior is the same regardless whether a physical EN pin is assigned to the rail.

The Power Good status is not affected by any warnings and faults unless the fault response is to turn OFF the rail.

UV fault and warn notification is ignored when a rail is off. UV fault and warn notification is also ignored during start up until the rail enters *Power Good* status for the first time. This mechanism avoids false-triggering UV fault and warn notification when the rail voltage is expected to be below UV thresholds.

A *Graceful Shutdown* feature is enabled by checking the *Configured as VIN Monitor* checkbox. When enabled, the rail is configured to monitor VIN. When VIN drops below *Power Good Off* threshold, the device ignores any UV fault and warn notifications on any other rail.

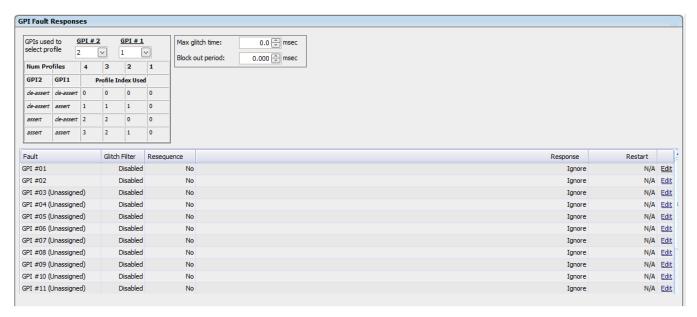

#### 8.4.2 GPI Configuration

Up to 32 of the 84 GPIO pins of the UCD90320 device can be configured as GPI. The GPI configuration window is under the **Pin Assignment** tab. Figure 11 shows an example.

| GPIs - General Pur | pose Inputs    |             |                  | 5 of 24 Assigned               |

|--------------------|----------------|-------------|------------------|--------------------------------|

| GPI Name           | Pin            | Polarity    | Special Behavior | Actions                        |

| GPI #1             | Pin L4 GPIO 01 | Active High |                  | <u>Delete</u> <u>Configure</u> |

| GPI #2             | Pin N1 GPIO 02 | Active High |                  | <u>Delete</u> <u>Configure</u> |

| GPI #3             | Pin M4 GPIO 03 | Active High |                  | <u>Delete</u> <u>Configure</u> |

| GPI #4             | Pin N2 GPIO 04 | Active High |                  | <u>Delete</u> <u>Configure</u> |

| GPI #5             | Pin G3 GPIO 05 | Active High |                  | <u>Delete</u> <u>Configure</u> |

| Add GPI            |                |             |                  |                                |

Figure 11. GPI Configuration Window (Hard Configuration ▶ Monitors and GPIO Pins Assignment)

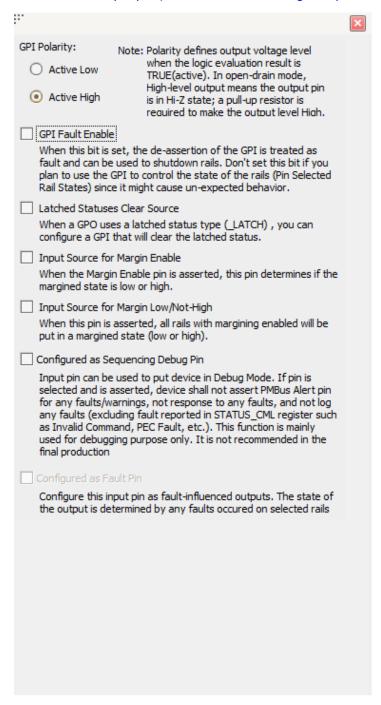

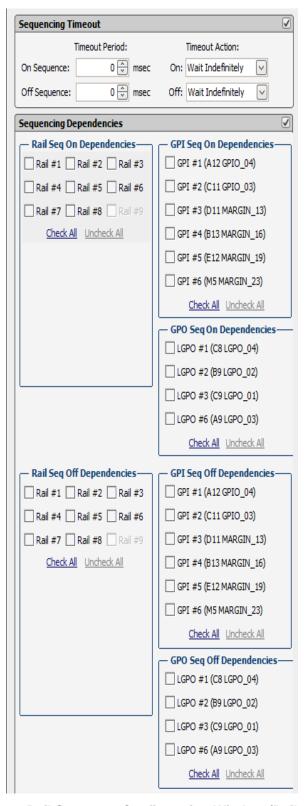

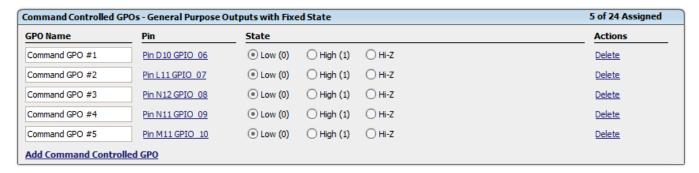

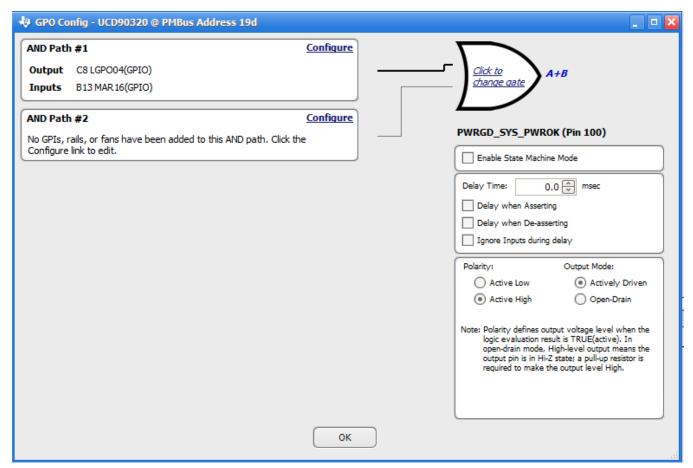

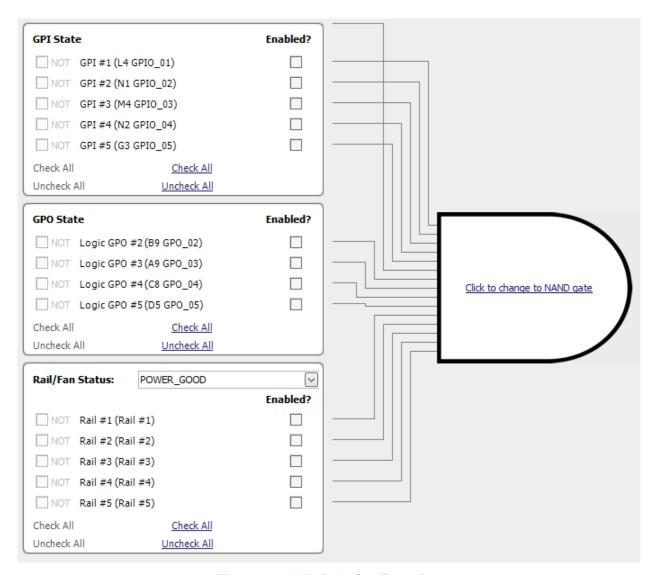

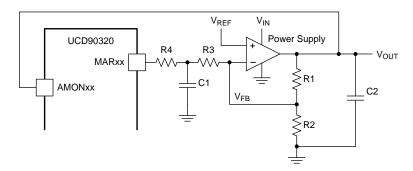

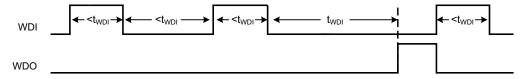

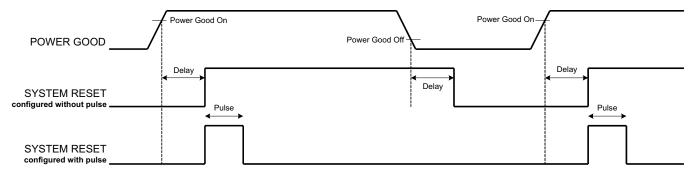

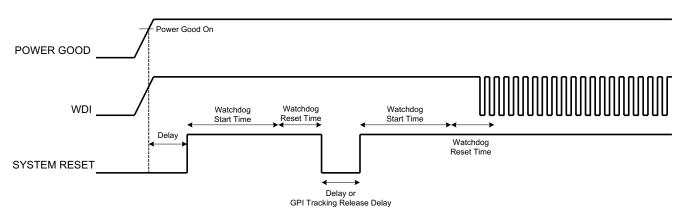

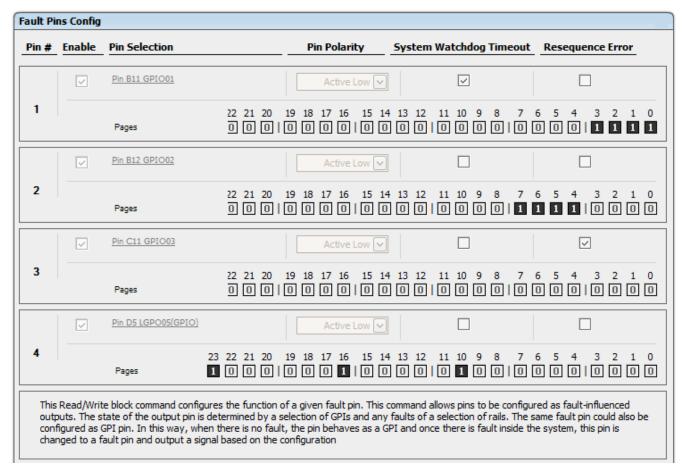

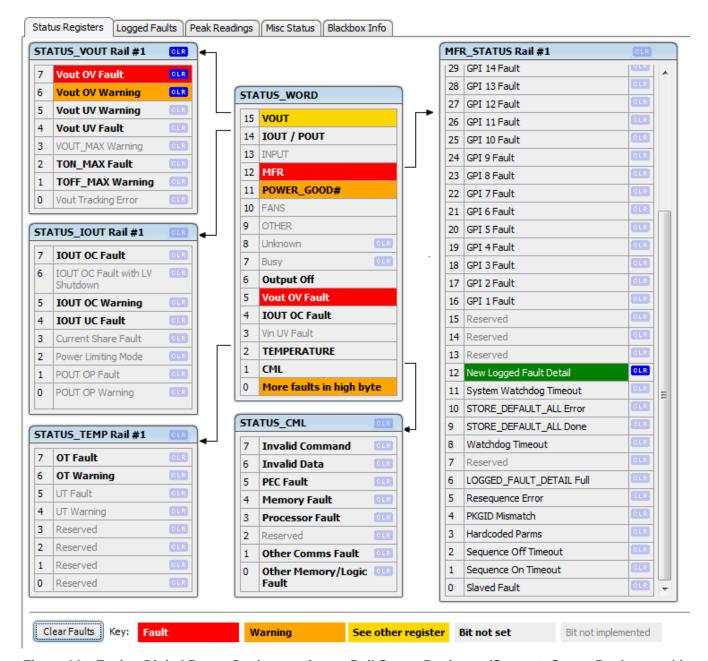

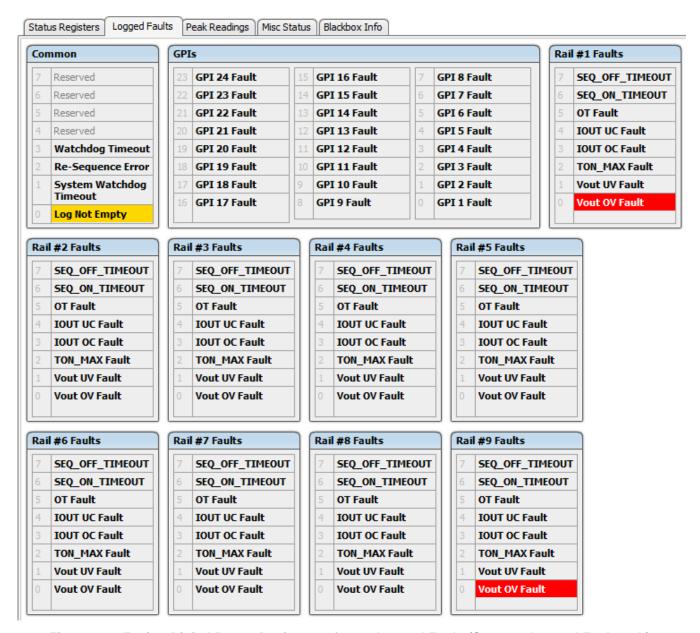

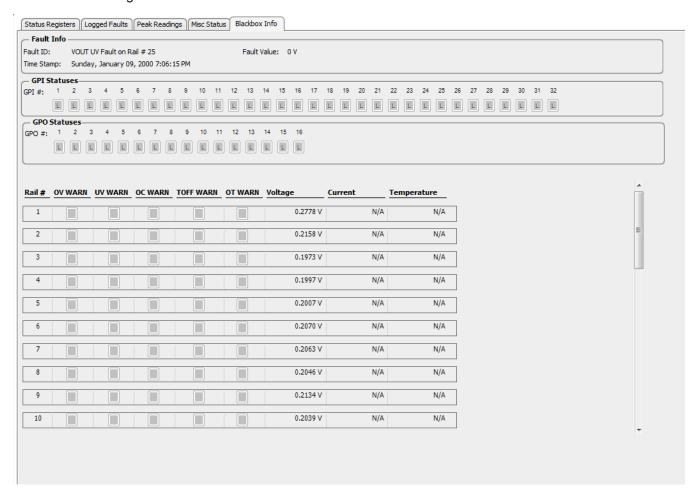

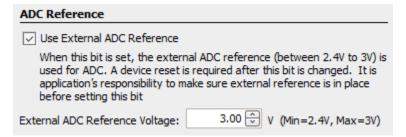

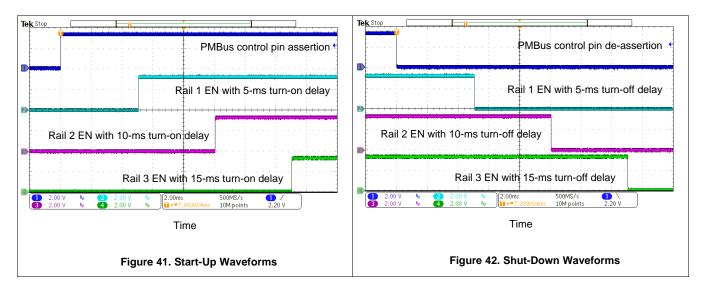

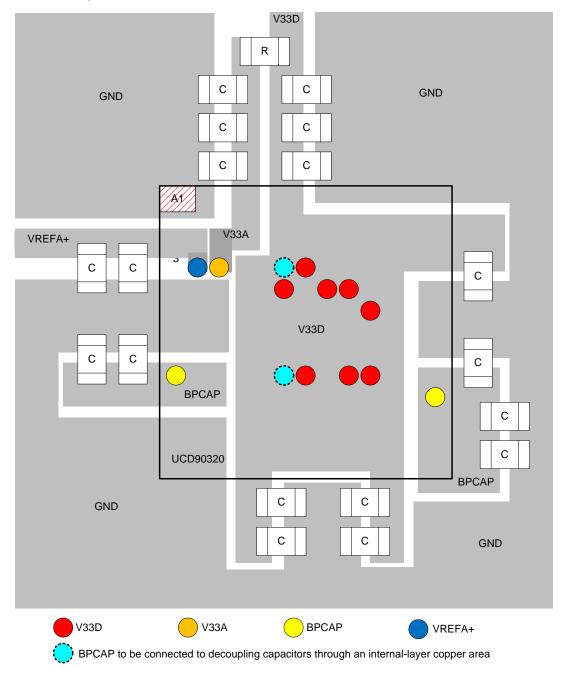

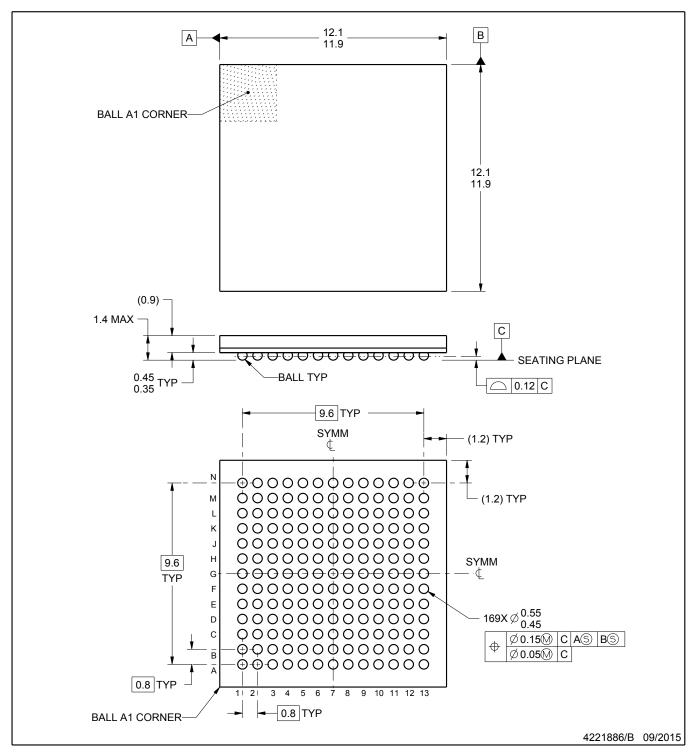

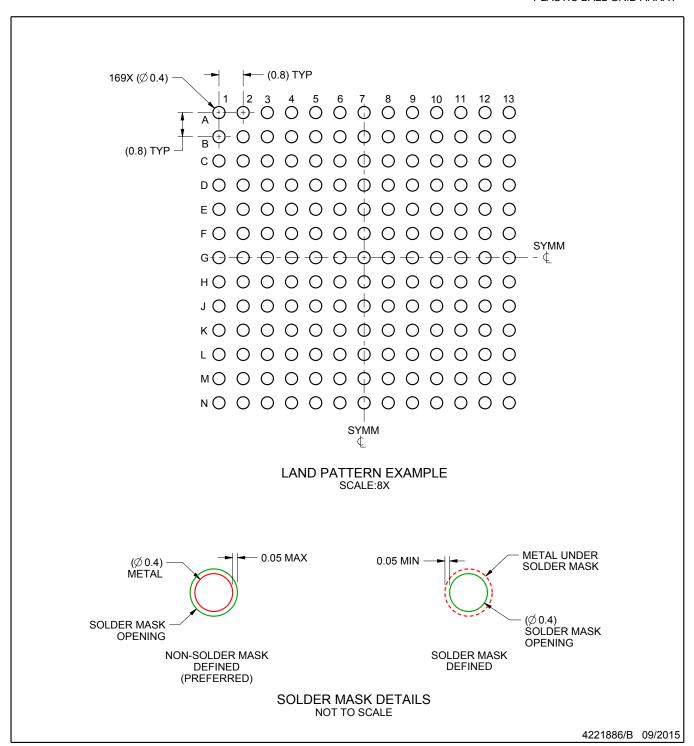

The polarity of GPI pins can be configured to be either active high or active low. Each GPI can be used as a source of sequence dependency. (See also the *Rail Sequence Configuration* section). The GPI pins can be also used for cascading function. (See also the *Cascading Multiple Devices* section). The first defined 3 GPIs regardless of their main purpose are assigned to the pin selected states function. (See also the *Pin Selected Rail States Configuration* section).