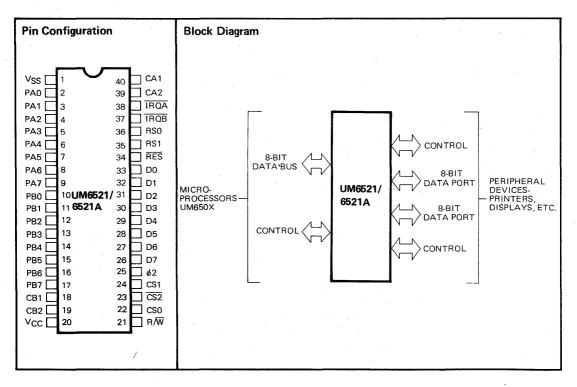

## UM6521/UM6521A

Peripheral Interface Adapter(PIA)

## Features

- Extended performance version of UM6520

- Single +5V power supply

- Two 8-bit bi-directional I/O ports with individual data direction control

- CMOS-compatible peripheral port A lines

- Automatic "handshake" control of data transfers

- Programmable interrupt capability

- Automatic initialization on power up

- 1 and 2 MHz versions

- Direct replacement for Motorola MC6821

### **General Description**

The UM6521/A Peripheral Interface Adapter (PIA) is designed to provide a broad range of peripheral control to microcomputer systems. It is functionally compatible with the UM6520, but with more drive capability and improved performance. Control of peripheral devices

is accomplished through two 8-bit bi-directional I/O ports. Each I/O line may be programmed to be either an input or an output. In addition, four peripheral control lines are provided to perform "handshaking" during data transfers.

## Absolute Maximum Ratings\*

This device contains circuitry to protect the inputs against damage due to high static voltages, however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this circuit.

#### \*Comments

Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **D.C. Characteristics**

(V<sub>CC</sub> =  $5.0V \pm 5\%$ , V<sub>SS</sub> = 0, T<sub>A</sub> = 0°C to 70°C unless otherwise noted)

| Symbol           | Characteristic                                                                                                                                                                                                    | Min. | Max.            | Units          |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|----------------|

| ViH              | Input High Voltage                                                                                                                                                                                                | +2.0 | Vcc             | V              |

| VIL              | Input Low Voltage                                                                                                                                                                                                 | -0.3 | +0.8            | V              |

| IIN              | Input Leakage Current<br>$V_{IN} = 0$ to 5.0V<br>$R/W$ , Reset, RS <sub>0</sub> , RS <sub>1</sub> , CS <sub>0</sub> , CS <sub>1</sub> , $\overline{CS_2}$ , CA <sub>1</sub> , CB <sub>1</sub> , $\phi_2$          |      | ±2.5            | μΑ             |

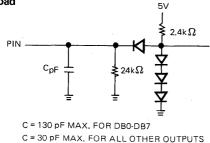

| ITSI             | Three-State (Off State Input Current)<br>( $V_{IN} = 0.4$ to 2.4 V, $V_{CC} = max$ ), $D_0$ - $D_7$ , $PB_0$ - $PB_7$ , $CB_2$                                                                                    | _    | ±10             | μΑ             |

| lін              | Input High Current<br>$(V_{1H} = 2.4 V), PA_0 PA_7, CA_2$                                                                                                                                                         | -200 | _               | μA             |

| lit.             | Input Low Current $(V_{1L} = 0.4 V), PA_0 PA_7, CA_2$                                                                                                                                                             | -    | 2.4             | mA             |

| VOL              | Output Low Voltage<br>(I <sub>L</sub> = 3.2 mA), IRQA, IRQB                                                                                                                                                       | _    | 0.4             | v              |

| V <sub>OH</sub>  | Output High Voltage ( $I_L = 205 \mu$ A), D <sub>0</sub> -D <sub>7</sub>                                                                                                                                          | 2.4  |                 | V              |

| V <sub>OL</sub>  | Output Low Voltage<br>(I <sub>L</sub> = 3.2mA), PA <sub>0</sub> -PA <sub>7</sub> , PB <sub>0</sub> -PB <sub>7</sub> , CA <sub>2</sub> , CB <sub>2</sub>                                                           | _    | 0.4             | v              |

| V <sub>OH</sub>  | Output High Voltage<br>( $I_H = -200 \ \mu A$ ), PA <sub>0</sub> -PA <sub>7</sub> , PB <sub>0</sub> -PB <sub>7</sub> , CA <sub>2</sub> , CB <sub>2</sub>                                                          | 2.4  | _               | v              |

| ЮН               | Output High Current<br>(Direct Transistor Drive Outputs)<br>$(V_{OUT} = 1.5 V), PB_0 - PB_7, CB_2$                                                                                                                | -1.0 | -10.0           | mA             |

| OFF              | Output Leakage Current (Off-State), IRQA, IRQB                                                                                                                                                                    | -    | 10              | μA             |

| PD               | Power Dissipation ( $V_{CC} = 5.25 V$ )                                                                                                                                                                           |      | 500             | mW             |

| CIN              | Input Capacitance<br>$(V_{1N} = 0, T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$<br>$D_0 - D_7, PA_0 - PA_7, PB_0 - PB_7, CA_2, CB_2$<br>$R/W, Reset, RS_0, RS_1, CS_0, CS_1, \overline{CS}_2$<br>$CA_1, CB_1, \phi_2$ |      | 10<br>7.0<br>20 | pF<br>pF<br>pF |

| C <sub>OUT</sub> | Output Capacitance<br>( $V_{1N} = 0, T_A = 25^{\circ}C, f = 1.0 \text{ MHz}$ )                                                                                                                                    | -    | 10              | pF             |

Note: Negative sign indicates outward current flow, positive indicates inward flow.

<sup>2</sup>eripheral IC

## UM6521/UM6521A

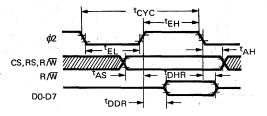

Figure 1. Read Timing Characteristic

Figure 2. Write Timing Characteristics

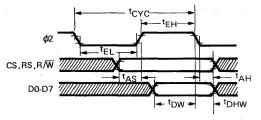

Figure 3. Peripheral Data Setup Time

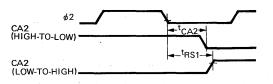

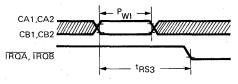

Figure 4. CA<sub>2</sub> Timing

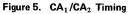

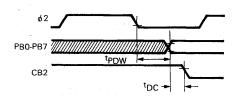

Figure 6. CB<sub>2</sub> Timing

Figure 7. CB<sub>1</sub>/CB<sub>2</sub> Handshake Timing

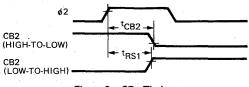

Figure 8. PA Port Delay Time

Figure 9. PB Port Delay Time

Figure 10. Interrupt Timing

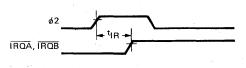

Figure 11. Interrupt Clear Timing

## Processor Interface Timing

(V<sub>CC</sub> = 5V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C unless otherwise noted)

| 0hl          | Paramatan.                   | UN   | 6521     | UM6  | 521A |       |

|--------------|------------------------------|------|----------|------|------|-------|

| Symbol       | Parameter                    | Min. | Max.     | Min. | Max. | Units |

| tCY          | Cycle Time                   | 1000 |          | 500  | _    | ns    |

| tен          | $\phi_2$ Pulse Width         | 440  |          | 200  | -    | ns    |

| tel          | $\phi_2$ Pulse Delay         | 430  | <u> </u> | 210  | -    | ns    |

| tas          | CS, RS, R/W Setup Time       | 160  |          | 70   | _    | ns    |

| tан          | CS, RS, R/W Hold Time        | 10   |          | 10   | -    | ns    |

| tDDR         | Data Delay Time, Read Cycle  | _    | 320      | -    | 180  | ns    |

| t DHR        | Data Hold Time, Read Cycle   | 10   |          | 10   | _    | ns    |

| tDSW         | Data Setup Time, Write Cycle | 195  | _        | 60   | _    | ns    |

| <b>t</b> DHW | Data Hold Time, Write Cycle  | 10   |          | 10   | _    | ns    |

## **Processor Interface Timing**

(V<sub>CC</sub> = 5V  $\pm$  5%, T<sub>A</sub> = 0°C to 70°C unless otherwise noted)

| Sumbol                         | Parameter                                  | UN   | 16521 | UM6  | 521A | Units |

|--------------------------------|--------------------------------------------|------|-------|------|------|-------|

| Symbol                         | Farameter                                  | Min. | Max.  | Min. | Max. |       |

| <b>tPDSU</b>                   | Peripheral Data Setup Time                 | 200  | -     | 100  | -    | ns    |

| tCA2                           | CA <sub>2</sub> Delay Time, High-to-Low    | -    | 1.0   | -    | 0.5  | μs    |

| t <sub>RS1</sub>               | CA <sub>2</sub> Delay Time, Low-to-High    | -    | 1.0   | -    | 0.5  | μs    |

| t <sub>RS2</sub>               | CA <sub>2</sub> Delay Time, Handshake Mode | _    | 2.0   | _    | 1.0  | μs    |

| <sup>t</sup> CB2               | CB <sub>2</sub> Delay Time, High-to-Low    | _    | 1.0   | _    | 0.5  | μs    |

| t <sub>RS1</sub>               | CB <sub>2</sub> Delay Time, Low-to-High    | -    | 1.0   | _    | 0.5  | μs    |

| t <sub>RS2</sub>               | CB <sub>2</sub> Delay Time, Handshake Mode | _    | 2.0   | _ ·  | 1.0  | μs    |

| tPDW                           | Peripheral Port Delay Time                 |      | 1.0   |      | 0.5  | μs    |

| temos                          | Peripheral Port Delay Time (CMOS)          |      | 2.0   | _    | 1.0  | μs    |

| tDC                            | CB <sub>2</sub> Delay Time from Data Valid | 20   | _     | 20   | _    | ns    |

| Pwi                            | Interrupt Input Pulse Width                | 500  | -     | 500  | _    | ns    |

| t <sub>RS3</sub>               | Interrupt Response Time                    | · _  | 1.0   | _    | 1.0  | μs    |

| tir                            | Interrupt Clear Delay                      | _    | 1.6   | _    | 0.85 | μs    |

| t <sub>R</sub> ,t <sub>F</sub> | Rise and Fall Times – CA1, CA2, CB1, CB2   | · —  | 1.0   | _ `  | 1.0  | μs    |

## Test Load

#### OPEN COLLECTOR OUTPUT TEST LOAD

### **Interface Signal Description**

#### **RES** (Reset)

This signal is used to initialize the PIA. A low signal on the RES input causes all internal registers to be cleared.

#### $\phi_2$ (Input Clock)

This input is the system  $\phi_2$  clock and is used to trigger all data transfers between the microprocessor and the PIA.

#### R/W (Read/Write)

This signal is generated by the microprocessor and is used to control the direction of data transfers. A high on the R/W signal permits the processor to read data supplied by the PIA; a low on the R/W signal permits the processor to Write into the PIA.

#### **IRQA**, **IRQB** (Interrupt Requests)

IRQA and IRQB are interrupt lines generated by the PIA for ports A and B respectively. These signals are active low signals and have open-drain outputs, thus allowing multiple IRQ signals from multiple PIA's to be wire-ORed together before connecting to the processor IRO signal input.

#### D<sub>0</sub>-D<sub>7</sub> (Data Bus)

"These eight data bus lines are used to transfer data information between the processor and the PIA. These signals are bi-directional and are normally high mapedance except when selected for a read operation.

#### CS0, CS1, CS2 (Chip Selects)

The PIA is selected when CS0 and CS1 are high and  $\overline{CS2}$  is low. These three chip select lines are normally connected to the processor address lines either directly or through external decoder circuits.

#### RSO, RS1 (Register Selects)

These two signals are used to select the various registers inside the PIA.

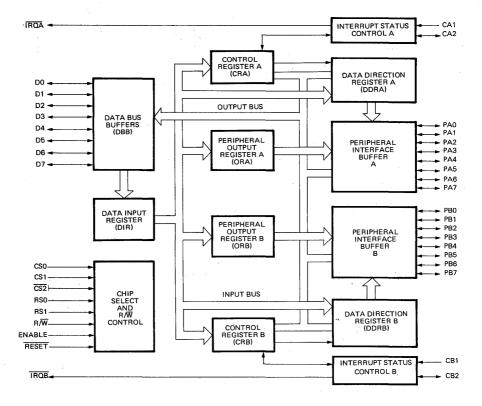

#### Internal Architecture

The UM6520 is organized into two independent sections referred to as the "A Side" and the "B Side." Each section consists of a Control Register (CRA, CRB), Data Direction Register (DDRA, DDRB), Output Register (ORA, ORB), Interrupt Status Control and the buffers necessary to drive the Peripheral Interface buses. Figure 12 is a block diagram of the UM6521.

Figure 12. UM6521 Block Diagram

7--56

|     | 7     | 6     | 5  | 4         | 3 | 2              | 1   | 0       |   |

|-----|-------|-------|----|-----------|---|----------------|-----|---------|---|

| CRA | IRQA1 | IRQA2 | с, | A2 Contro |   | DDRA<br>Access | CA1 | Control | 1 |

|     |       | L     |    |           |   |                |     |         | - |

|     | - 7   | 6     | 5  | 4         | 3 | 2              | 1   | 0       |   |

| CRB | IRQB1 | IRQB2 |    | B2 Contro |   | DDRB<br>Access | CB1 | Control | 1 |

Figure 13. Control Registers

#### **Data Input Register**

When the microprocessor writes data into the Um6521, the data which appears on the data bus during the Phase Two clock pulse is latched into the Data Input Register. It is then transferred into one of six internal registers of the UM6521 after the trailing edge of Phase Two. This assures that the data on the peripheral output lines will make smooth transitions from high to low or from low to high and the voltage will remain stable except when it is going to the opposite polarity.

#### Control Registers (CRA and CRB)

Figure 4 illustrates the bit designation and functions in the Control Registers. The Control Registers allow the microprocessor to control the operation of the Interrupt Control inputs (CA1, CA2, CB1, CB2), and Peripheral Control outputs (CA2, CB2). Bit 2 in each register controls the addressing of the Data Direction Registers (DDRA, DDRB) and the Output Registers (ORA, ORB). In addition, two bits (bit 6 and 7) are provided in each control register to indicate the status of the interrupt input lines (CA1, CA2, CB2). These interrupt status bits (IRQA1, (IRQB1) are normally interrogated by the microprocessor during the interrupt. These are the interrupt lines which drive the interrupt input (IRQ, NMI) of the microprocessor.

#### Data Direction Registers (DDRA, DDRB)

The Data Direction Registers allow the processor to program each line in the 8-bit Peripheral I/O port to be either an input or an output. Each bit in DDRA controls the corresponding line in the Peripheral A port and each bit in DDRB controls the corresponding line in the Peripheral B port. Placing a "O" in a bit position in the Data Direction Register causes the corresponding Peripheral I/O line to act as an input; a "1" causes it to act as an output.

#### Peripheral Output Registers (ORA, ORB)

The Peripheral Output Registers store the output data which appears on the Peripheral I/O port. Writing a "0" into a bit in ORA causes the corresponding line on the Peripheral A port to go low ( $\langle 0.4V \rangle$ ) if that line is programmed to act as an output. A "1" causes the corresponding output to go high. The lines of the Peripheral B port are controlled by ORB in the same manner.

#### **Interrupt Status Control**

The four interrupt/peripheral control lines (CA1, CA2, CB1, CB2) are controlled by the Interrupt Status Control logic (A, B). This logic interprets the contents of the corresponding Control Register, detects active transitions on the interrupt inputs and performs those operations necessary to assure proper operation of these four peripheral interface lines.

# Peripheral Interface Buffers (A, B) and Data Bus Buffers (DBB)

These Buffers provide the necessary current and voltage drive on the peripheral I/O ports and data bus to assure proper system operation and to meet the device specifications.

### **Functional Description**

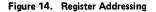

Bit 2 (DDR) in each Control Register (CRA and CRB) controls the accessing to the Data Direction Register or the Peripheral interface. If bit 2 is a "1", a Peripheral Output register (ORA, ORB) is selepted, and if bit 2 is a "0", a Data Direction Register (DDRA, DDRB) is selected. The Data Direction Register Access Control bit, together with the Register Select lines (RSO, SR1) selects the various internal registers as shown in Figure 14.

In order to write data into DDRA, ORA, DDRB, or ORB registers, bit 2 in the proper Control Register must first be set. The desired register may then be accessed with the address determined by the address interconnect technique used.

#### Register Select Lines (RS0), (RS1)

These two register select lines are used to select the various registers inside the UM6521. These input lines are used in conjunction with internal control registers to select a particular register that is to be accessed by the micro-processor. These lines are normally connected to micro-processor address output lines. These lines operate in conjunction with the chip-select inputs to allow the micro-processor to address a single 8-bit register within the microprocessor address space. This register may be an internal register (CRA, ORA, etc.) or it may be a Peripheral I/O port.

The processor may write directly into the Control Registers (CRA, CRB), the Data Direction Registers (DDRA, DDRB) and the Peripheral Output Registers (ORA, ORB). In addition, the processor may directly read the contents of the Control Registers and the Data Direction Registers. Accessing the Peripheral Output Register for the purpose of reading data back into the processor operates differently on the ORA and the ORB registers and therefore are discussed separately below.

#### Reading the Peripheral A I/O Port

The Peripheral A I/O port consists of 8 lines which can be programmed to act as inputs or outputs. When programmed to act as outputs, each line reflects the contents of the corresponding bit in the Peripheral Output Register. When programmed to act as inputs, these lines will go high or low depending on the input data. The Peripheral Output Register (ORA) has no effect on those lines programmed to act as inputs. The eight lines of the Peripheral A I/O port therefore contain either input or output data depending on whether the line is programmed to act as an input or an output. Performing a Read operation with RS1 = 0, RS0 = 0 and the Data Direction Register Access Control bit (CRA-2) = 1, directly transfers the data on the Peripheral A I/O lines into the processor (via the data bus). This will contain both the input and output data. The processor must be programmed to recognize and interpret only those bits which are important to the particular peripheral operation being performed.

Since the processor always reads the Peripheral A I/O port pins instead of the actual Peripheral Output Register (ORA), it is possible for the data read into the processor to differ from the contents of the Peripheral Output Register for an output line. This is true when the I/O pin is not allowed to go to a full +2.4V DC when the Peripheral Output register contains a logic 1. In this case, the processor will read a 0 from the Peripheral A pin, even though the corresponding bit in the Peripheral Output register is a 1.

#### Reading the Peripheral B I/O Port

Reading the Peripheral B I/O port yields a combination of input and output data in a manner similar to the Peripheral A port. However, data is read directly from the Peripheral B Output Register (ORB) for those lines programmed to act as outputs. It is therefore possible to load down the Peripheral B Output lines without causing incorrect data to be transferred back into the processor on a Read operation.

#### Interrupt Request Lines (IRQA, IRQB)

The active low Interrupt Request lines (IRQA and IRQB) act to interrupt the microprocessor either directly or through external interrupt priority circuitry. These lines are "open drain" and are capable of sinking 1.6 milliamps from an external source. This permits all interrupt request lines to be tied together in a "wired-OR" configuration. The "A" and "B" in the titles of these lines correspond to the "A" peripheral port and the "B" peripheral port. Hence each interrupt request line services one peripheral data port.

Each Interrupt Request line has two interrupt flag bits

| Se  | gister<br>Nect<br>Pin | Registe | Direction<br>r Access<br>rol Bit | Register Selected         |

|-----|-----------------------|---------|----------------------------------|---------------------------|

| RS1 | RS0                   | CRA-2   | CRB-2                            |                           |

| 0   | 0                     | 1       | · _                              | Peripheral Interface A    |

| 0   | 0                     | 0       | -                                | Data Direction Register A |

| 0   | • 1                   | ,       | -                                | Control Register A        |

| 1   | 0                     |         | 1                                | Peripheral Interface B    |

| 1   | 0                     | _       | 0                                | Data Direction Register B |

| 1   | 1                     |         |                                  | Control Register B        |

which can cause the Interrupt Request line to go low. These flags are bits 6 and 7 in the two Control Registers. These flags act as the link between the peripheral interrupt signals and the microprocessor interrupt inputs. Each flag has a corresponding interrupt disable bit which allows the processor to enable or disable the interrupt from each of the four interrupt inputs (CA1, CA2, CB1, CB2).

The four interrupt flags are set by active transitions of the signal on the interrupt input (CA1, CA2, CB1, CB2).

### Control of IRQA

Control Register A bit 7 is always set by an active transition of the CA1 interrupt input signal. Interrupting from this flag can be disabled by setting bit 0 in the Control Register A (CRA) to a logic 0. Likewise, Control Register A bit 6 can be set by an active transition of the CA2 interrupt input signal. Interrupting from this flag can be disabled by setting bit 3 in the Control Register to a logic 0.

Both bit 6 and bit 7 in CRA are reset by a "Read Peripheral Output Register A" operation. This is defined as an operation in which the proper chip-select and register-select signals are provided to allow the processor to read the Peripheral A I/O port.

## Control of IRQB

Control of  $\overline{IRQB}$  is performed in exactly the same manner as that described above for  $\overline{IRQA}$ . Bit 7 in CRB is set by an active transition on CB1; interrupting from this flag is controlled by CRB bit 0. Likewise, bit 6 in CRB is set by an active transition on CB2; interrupting from this flag is controlled by CRB bit 3.

Also, both bit 6 and bit 7 are reset by a "Read Peripheral B Output Register" operation.

| SUMMARY:                                                                      |   |

|-------------------------------------------------------------------------------|---|

| IRQA goes low when CRA-7 = 1 and CRA-0 = 1 or<br>when CRA-6 = 1 and CRA-3 = 1 | ٠ |

| IRQB goes low when CRB-7 = 1 and CRB-0 = 1 or<br>when CRB-6 = 1 and CRB-3 = 1 |   |

It should be stressed at this point that the flags act as the link between the peripheral interrupt signals and the processor interrupt inputs. The interrupt disable bits allow the processor to control the interrupt function.

#### Interface Between UM6521 and Peripheral Devices

The UM6521 provides two 8-bit bi-directional ports and 4 interrupt/control lines for interfacing to peripheral devices. These ports and the associated interrupt/control lines are referred to as the "A" side and the "B" side. Each side has its own unique characteristics and will therefore be discussed separately below.

#### Peripheral I/O Ports

The Peripheral A and Peripheral B I/O Ports allow the microprocessor to interface to the input lines on the peripheral device by loading data into the Peripheral Output Register. They also allow the processor to interface with the peripheral device output lines by reading the data on the Peripheral Port input lines directly onto the data bus and into the internal registers of the processor.

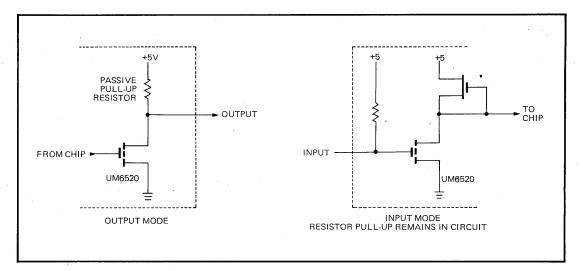

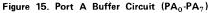

#### Peripheral A I/O Port (PA0-PA7)

Each of the Peripheral I/O lines can be programmed to act as an input or an output. This is accomplished by setting a "1" in the corresponding bit in the Data Direction Register for those lines which are to act as outputs. A "0" in a bit of the Data Direction Register causes the corresponding Peripheral I/O lines to act as an input.

The buffers which drive the Peripheral A I/O lines contain "passive" pull-ups as shown in Figure 15. These pull-up devices are resistive in nature and therefore allow the output voltage to go to  $V_{CC}$  for a logic 1. The switches can sink a full 1.6mA, making these buffers capable of driving one standard TTL load.

In the input mode, the pull-up devices shown in Figure 15 are still connected to the I/O pin and still supply current to this pin. For this reason, these lines represent one standard TTL load in the input mode.

#### Peripheral B I/O Port (PB0-PB7)

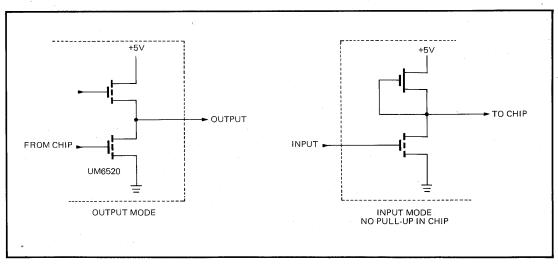

The Peripheral B I/O port duplicates many of the functions of the Peripheral A port. The process of programming these lines to act as an input or an output has been discussed previously. Likewise, the effect of reading or writing this port has been discussed. However, there are several characteristics of the buffers driving these lines which affect their use in peripheral interfacing.

The Peripheral B I/O port buffers are push-pull devices as shown in Figure 16. The pull-up devices are switched "OFF" in the "0" state and "ON" for a logic 1. Since

## UM6521/UM6521A

these pull-ups are active devices, the logic "1" voltage is not guaranteed to go higher than +2.4V. They are TTL compatible but are not CMOS compatible.

However, the active pull-up devices can source up to 1mA at 1.5V. This current drive capability is provided to allow direct connection to Darlington transistor switches. This allows very simple control of relays, lamps, etc.

Because these outputs are designed to drive transistors

directly, the output data is read directly from the Peripheral Output Register for those lines programmed to act as inputs.

The final characteristic which is a function of the Peripheral B push-pull buffers is the high-impedance input state. When the Peripheral B I/O lines are programmed to act as inputs, the output buffer enters the high impedance state.

## Figure 16. Port B Buffer Circuit (PB0-PB7)

7-60

# Interrupt Input/Peripheral Control Lines (CA1, CA2, CB1, CB2)

The four interrupt input/peripheral control lines provide a number of special peripheral control functions. These lines greatly enhance the power of the two general purpose interface ports (PA0-PA7, PB0-PB7). Figure 17 summarizes the operation of these control lines.

# Peripheral A Interrupt Input/Peripheral Control Lines (CA1, CA2)

CA1 is an interrupt input only. An active transition of the signal on this input will set bit 7 of the Control Register A to a logic 1. The active transition can be programmed by setting a "0" in bit 1 of the CRA if the interrupt flag (bit 7 of CRA) is to be set on a negative transition of the CA1 signal or a "1" if it is to be set on a positive transition.

NOTE: A negative transition is defined as a transition from a high to a low, and a positive transition is defined as a transition from a low to a high voltage.

Setting the interrupt flag will interrupt the processor through  $\overline{IRQA}$  if bit 0 of CRA is a 1 as described previously.

CA2 can act as a totally independent interrupt input or as a peripheral control output. As an input (CRA, bit 5 = 0) it acts to set the interrupt flag, bit 6 of CRA, to a logic 1 on the active transition selected by bit 4 of CRA.

These control register bits and interrupt inputs serve the same basic function as that described above for CA1. The input signal sets the interrupt flag which serves as the link between the peripheral device and the processor interrupt structure. The interrupt disable bit allows the processor to exercise control over the system interrupts.

In the Output mode (CRA, bit 5 = 1), CA2 can operate independently to generate a simple pulse each time the microprocessor reads the data on the Peripheral A I/O port. This mode is selected by setting CRA, bit 4 to a "0" and CRA, bit 3 to a "1". This pulse output can be used to control the counters, shift registers, etc. which make sequential data available on the Peripheral input lines.

A second output model allows CA2 to be used in conjunction with CA1 to "handshake" between the processor and the peripheral device. On the A side, this technique allows positive control of data transfers from the peripheral device into the microprocessor. The CA1 input signals the processor that data is available by interrupting the processor. The processor reads the data and set CA2 low. This signals the peripheral device that it can make new data available.

The final output mode can be selected by setting bit 4 of CRA to a 1. In this mode, CA2 is a simple peripheral control output which can be set high or low by setting bit 3 of CRA to a 1 or a 0 respectively.

# Peripheral B Interrupt Input/Peripheral Control Lines (CB1, CB2)

CB1 operates as an interrupt input only in the same manner as CA1. Bit 7 of CRB is set by the active transition selected by bit 0 of CRB. Likewise, the CB2 input mode operates exactly the same as the CA2 input modes. The CB2 output modes, CRB bit 5 = 1, differ somewhat from those of CA2. The pulse output occurs when the processor writes data into the Peripheral B Output Register. Also, the "handshaking" operates on data transfers from the processor into the peripheral device.

| CRA   | (CRB) | Active Transition |                                                                                              |

|-------|-------|-------------------|----------------------------------------------------------------------------------------------|

| Bit 1 | Bit 0 | of Input Signal*  | IRQA (IRQB) Interrupt Outputs                                                                |

| 0     | 0     | Negative          | Disable – remain high                                                                        |

| 0     | 1     | Negative          | Enable – goes low when bit 7 in CRA (CRB) is set by active transition of signal on CA1 (CB1) |

| 1     | 0     | Positive          | Disable — remain high                                                                        |

| 1     | 1     | Positive          | Enable – as explained above                                                                  |

### CA1/CB1 CONTROL

\*Note: Bit 7 of CRA (CRB) will be set to a logic 1 by an active transition of the CA1 (CB1) signal. This is independent of the state of Bit 0 in CRA (CRB).

Peripheral IC

## CA2/CB2 INPUT MODES

|       | CRA (C | RB)   | Active Transition |                                                                                              |

|-------|--------|-------|-------------------|----------------------------------------------------------------------------------------------|

| Bit 5 | Bit 4  | Bit 3 | of Input Signal*  | IRQA (IRQB) Interrupt Outputs                                                                |

| 0     | 0      | 0     | Negative          | Disable — remains high                                                                       |

| 0     | 0      | 1     | Negative          | Enable – goes low when bit 6 in CRA (CRB) is set by active transition of signal on CA2 (CB2) |

| 0     | 1      | 0     | Positive          | Disable — remains high                                                                       |

| 0     | 1      | 1     | Positive          | Enable – as explained above                                                                  |

\*Note: Bit 6 of CRA (CRB) will be set to a logic 1 by an active transition of the CA2 (CB2) signal. This is independent of the state of Bit 3 in CRA (CRB).

## CA2 OUTPUT MODES

|       | CRA   | -     | Mada                   | Descriptions                                                                                                                                                                                                                                 |

|-------|-------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 5 | Bit 4 | Bit 3 | Mode                   | Descriptions                                                                                                                                                                                                                                 |

| 1     | 0     | 0     | "Handshake"<br>on Read | CA2 is set high on an active transition of the CA1 interrupt<br>input signal and set low by a microprocessor "Read A Data"<br>operation. This allows positive control of data transfers from<br>the peripheral device to the microprocessor. |

| 1     | 0     | 1     | Pulse Output           | CA2 goes low for one cycle after a "Read A Data" operation.<br>This pulse can be used to signal the peripheral device that data<br>was taken.                                                                                                |

| 1     | 1     | 0     | Manual Output          | CA2 set low                                                                                                                                                                                                                                  |

| 1     | 1     | 1     | Manual Output          | CA2 set high                                                                                                                                                                                                                                 |

## CB2 OUTPUT MODES

|       | CRB   |       | Mada                      | Descriptions                                                                                                                                                                                                                                   |

|-------|-------|-------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 5 | Bit 4 | Bit 3 | - Mode                    | Descriptions                                                                                                                                                                                                                                   |

| .1    | 0     | 0     | ''Handshake''<br>on Write | CB2 is set low on microprocessor "Write B Data" operation<br>and is set high by an active transition of the CB1 interrupt<br>input signal. This allows positive control of data transfers<br>from the microprocessor to the peripheral device. |

| 1     | 0     | 1     | Pulse Output              | CB2 goes low for one cycle after a microprocessor "Write B<br>Data" operation. This can be used to signal the peripheral<br>device that data is available.                                                                                     |

| 1     | 1     | 0     | Manual Output             | CB2 set low                                                                                                                                                                                                                                    |

| · 1   | 1 .   | 1     | Manual Output             | CB2 set high                                                                                                                                                                                                                                   |

## Figure 17. Summary of Operation of Control Lines

## Ordering Information

| Part Number | Speed | Package |

|-------------|-------|---------|

| UM6521      | 1 MHz | Plastic |

| UM6521A     | 2 MHz | Plastic |