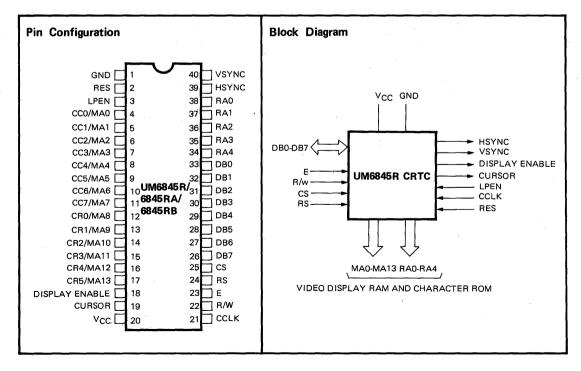

# UM6845R/UM6845RA/UM6845RB

CRT Controller

.

## Features

- Single + 5 volt (±5%) power supply

- Alphanumeric and limited graphics capabilities

- Fully programmable display (rows, columns, blanking, etc.)

- Interlaced or non-interlaced scan

- 50/60 Hz operation

- Fully programmable cursor

- External light pen capability

- Capable of addressing up to 16K character Video Display RAM.

- No DMA required

- Compatible with SY6845R

- Straight-binary addressing for Video Display RAM

## **General Description**

The UM6845R is a CRT Controller intended to provide capability for interfacing any microprocessor family to CRT or TV-type raster scan displays. A unique feature

is the inclusion of several modes of operation, so that the system designer can configure the system with a wide assortment of techniques.

## Absolute Maximum Ratings\*

| Supply Voltage, $V_{CC}$                             |

|------------------------------------------------------|

| Input/Output Voltage, V <sub>IN</sub> 0.3V to + 7.0V |

| Operating Temperature, T <sub>OP</sub> 0°C to 70°C   |

| Storage Temperature, T <sub>STG</sub> 55°C to 150°C  |

| Notice:                                              |

All inputs contain protection circuitry to prevent damage due to high static discharges. Care should be exercised to prevent unnecessary application of voltages in excess of the allowable limits. \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **D.C. Electrical Characteristics**

$(V_{CC} = 5.0V \pm 5\%, T_A = 0 - 70^{\circ}C, unless otherwise noted)$

| Symbol           | Characteristics                                                                                                  | Min.  | Тур. | Max.            | Units    |

|------------------|------------------------------------------------------------------------------------------------------------------|-------|------|-----------------|----------|

| VIH              | Input High Voltage                                                                                               | 2.0   |      | V <sub>CC</sub> | V        |

| VIL              | Input Low Voltage                                                                                                | -0.3  |      | 0.8             | V        |

| IIN              | Input Leakage ( $\phi$ 2, R/ $\overline{w}$ , $\overline{\text{RES}}$ , $\overline{\text{CS}}$ , RS, LPEN, CCLK) | -     |      | 2.5             | μΑ       |

| I <sub>TSI</sub> | Three-State Input Leakage (DB0-DB7)<br>V <sub>IN</sub> = 0.4 to 2.4V                                             | -10.0 |      | +10.0           | μΑ       |

| Voh              | Output High Voltage<br>I <sub>LOAD</sub> = -205 µA (DB0-DB7)<br>I <sub>LOAD</sub> = -100 µA (all others)         | 2.4   |      | _               | V        |

| VOL              | Output Low Voltage<br>I <sub>LOAD</sub> = 1.6mA                                                                  | -     |      | 0.4             | V        |

| P <sub>D</sub>   | Power Dissipation                                                                                                |       | 325  | 650             | mW       |

| C <sub>IN</sub>  | Input Capacitance<br>¢2, R/w, RES, CS, RS, LPEN, CCLK<br>DB0-DB7                                                 | -     |      | 10.0<br>12.5    | pF<br>pF |

| Соит             | Output Capacitance                                                                                               | -     |      | 10.0            | pF       |

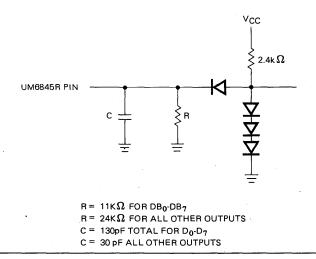

TEST LOAD

## A.C. Electrical Characteristics

MPU BUS INFERFACE CHARACTERISTICS

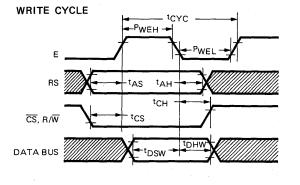

WRITE TIMING CHARACTERISTICS (V<sub>CC</sub> =  $5.0V \pm 5\%$ , T<sub>A</sub> =  $0 - 70^{\circ}$ C, unless otherwise noted)

| Symbol           | Characteristics      | UMe  | 845R | UM68 | 845RA | UM6  | B45RB | 11-14- |

|------------------|----------------------|------|------|------|-------|------|-------|--------|

| Symbol           | Characteristics      | Min. | Max. | Min. | Max.  | Min. | Max.  | Units  |

| tcyc             | Cycle Time           | 1.0  | _    | 0.5  | _     | 0.33 | _     | μs     |

| PWEH             | E Pulse Width, High  | 440  | -    | 200  |       | 150  | -     | ņs     |

| PWEL             | E Pulse Width, Low   | 420  | -    | 190  | _     | 140  | _     | ns     |

| t <sub>AS</sub>  | Address Set-Up Time  | 80   | -    | 40   | -     | 30   | -     | ns     |

| t <sub>AH</sub>  | Address Hold Time    | 0    |      | 0    | -     | 0    |       | ns     |

| tcs              | R/W, CS Set-Up Time  | 80   |      | 40   | _     | 30   | -     | ns     |

| <sup>t</sup> сн  | R/W, CS Hold Time    | 0    | -    | 0    |       | 0    | _     | ns     |

| t <sub>DSW</sub> | Data Bus Set-Up Time | 165  | -    | 60   | _     | 60   | -     | ns     |

| <sup>t</sup> DHW | Data Bus Hold Time   | 10   | _    | 10   | _     | 10   | _     | ns     |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

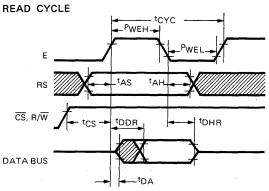

# **READ TIMING CHARACTERISTICS**. (V<sub>CC</sub> = 5.0V $\pm$ 5%, T<sub>A</sub> = 0 - 70°C, unless otherwise noted)

| 0 militat        | Characteristics                     | UMe  | 845R     | UM68 | 345RA | UM6  | 345RB |       |

|------------------|-------------------------------------|------|----------|------|-------|------|-------|-------|

| Symbol           | Characteristics                     | Min. | Max.     | Min. | Max.  | Min. | Max.  | Units |

| <sup>t</sup> CYC | Cycle Time                          | 1.0  |          | 0.5  | -     | 0.33 |       | μs    |

| PWEH             | E Pulse Width, High                 | 440  | <u> </u> | 200  | -     | 150  |       | ns    |

| PWEL             | E Pulse Width, Low                  | 420  | -        | 190  | -     | 140  |       | ns    |

| t <sub>AS</sub>  | Address Set-Up Time                 | 80   | _        | 40   | _     | 30   |       | ns    |

| t <sub>AH</sub>  | Address Hold Time                   | 0    | -        | 0    | _     | 0    | _     | ns    |

| t <sub>CS</sub>  | R/W, CS Set-Up Time                 | 80   | _        | 40   | _     | 30   |       | ns    |

| t <sub>DDR</sub> | Read Access Time (Valid Data)       | -    | 290      | _    | 150   |      | 100   | ns    |

| <sup>t</sup> DHR | Read Hold Time                      | 20   | 60       | 20   | 60    | 20   | 60    | ns    |

| t <sub>DA</sub>  | Data Bus Active Time (Invalid Data) | 40   |          | 40   | _ ·   | 40   | _     | ns    |

$(t_r \text{ and } t_f = 10 \text{ to } 30 \text{ ns})$

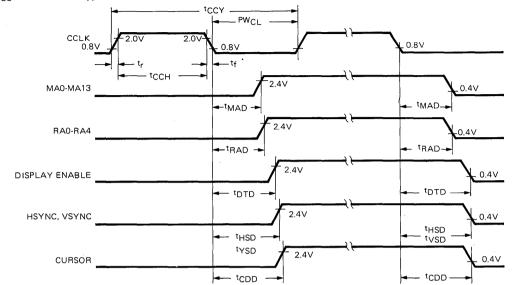

# MEMORY AND VIDEO INTERFACE CHARACTERISTICS

$(V_{CC} = 5.0V \pm 5\%, T_{\Delta} = 0 \text{ to } 70^{\circ}\text{C}, \text{ unless otherwise noted})$

| Symbol              | Parameter                          | Min. | Typ.              | Max. | Units |

|---------------------|------------------------------------|------|-------------------|------|-------|

| тссн                | Minimum Clock Pulse Width, High    | 200  |                   |      | ns    |

| T <sub>CCY</sub>    | Clock Frequency                    |      | ALIAN ALIAN ALIAN | 2.5  | MHz   |

| T <sub>r</sub> , tf | Rise and Fall Time for Clock Input |      |                   | 20   | ns    |

| <sup>t</sup> MAD    | Memory Address Delay Time          |      | 100               | 160  | ns    |

| t <sub>RAD</sub>    | Raster Address Delay Time          |      | 100               | 160  | ns    |

| t <sub>DTD</sub>    | Display Timing Delay Time          |      | 160               | 300  | ns    |

| tHSD                | Horizontal Sync Delay Time         |      | 160               | 300  | ns    |

| t <sub>VSD</sub>    | Vertical Sync Delay Time           |      | 160               | 300  | ns    |

| tCDD                | Cursor Display Timing Delay Time   |      | 160               | 300  | ns    |

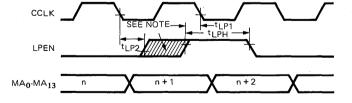

## LIGHT PEN STROBE TIMING

NOTE: "Safe" time position for LPEN positive edge to cause address n+2 to load into Light Pen Register. tLP2 and tLP1 are time positions causing uncertain results.

| Symbol           | Characteristics    | UM6845R |      | UM6  | 845RA | UM68 |      |      |

|------------------|--------------------|---------|------|------|-------|------|------|------|

| Symbol           | Characteristics    | Min.    | Max. | Min. | Max.  | Min. | Max. | Unit |

| tlph             | LPEN Strobe Width  | 100     |      | 100  | -     | 100  |      | ns   |

| t <sub>LP1</sub> | LPEN to CCLK Delay | -       | 120  | -    | 120   | -    | 120  | ns   |

| t <sub>LP2</sub> | CCLK to LPEN Delay |         | 0    |      | 0     | _    | 0    | ns   |

$t_r$  and  $t_f = 20 \text{ ns} (\text{max.})$

# UM6845R / UM6845RA / UM6845RB

**Pin Description**

#### MPU INTERFACE SIGNAL DESCRIPTION

#### E (Enable)

The enable signal is the system input and is used to trigger all data transfers between the system microprocessor and the UM6845R. Since there is no maximum limit to the allowable E cycle time, it is not necessary for it to be a continuous clock. This capability permits the UM6845R to be easily interfaced to non-6500-compatible microprocessors.

## R/W (Read/Write)

The R/W signal is generated by the microprocessor and is used to control the direction of data transfers. A high on the R/W pin allows the processor to read the data supplied by the UM6845R; a low on the R/W pin allows a write to the UM6845R

## CS (Chip Select)

The Chip Select input is normally connected to the processor address bus either directly or through a decoder. The UM6845R is selected when  $\overline{\text{CS}}$  is low.

#### **RS (Register Select)**

The Register Select input is used to access internal registers, A low on this pin permits writes into the Address Register and reads from the Status Register. The contents of the Address Register is the identity of the register accessed when RS is high.

#### DB<sub>0</sub>-DB<sub>7</sub> (Data Bus)

The  $DB_0-DB_7$  pins are the eight data lines used for transfer of data between the processor and the UM6845R. These lines are bi-directional and are normally high-impedance except during read/write cycles when the chip is selected.

## VIDEO INTERFACE SIGNAL DESCRIPTION

#### HSYNC (Horizontal Sync)

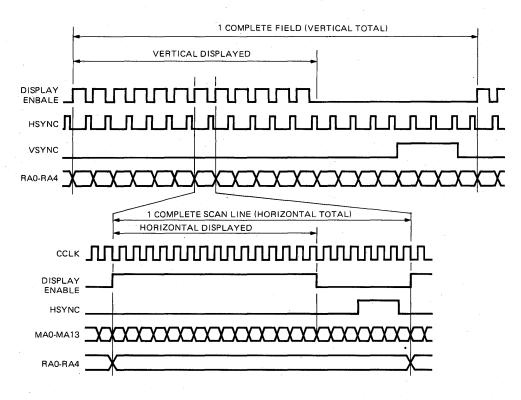

The HSYNC signal is an active-high output used to determine the horizontal position of displayed text. It may drive a CRT monitor directly or may be used for composite video generation. HSYNC time position and width are fully programmable.

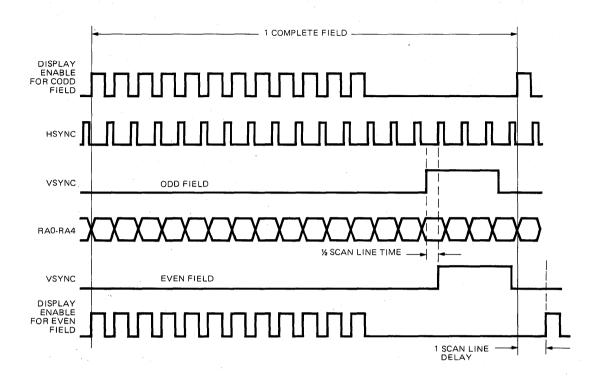

#### VSYNC (Vertical Sync)

The VSYNC signal is an active-high output used to determine the vertical position of displayed text. Like HSYNC, VSYNC may be used to drive a CRT monitor or composite video generation circuits. VSYNC position and width are both fully programmable.

## DISPLAY ENABLE

The DISPLAY ENABLE signal is an active-high output and is used to indicate when the UM6845R is generating active display information. The number of horizontal displayed characters and the number of vertical displayed characters are both fully programmable and together are used to generate the DISPLAY ENABLE signal.

## CURSOR

The CURSOR signal is an active-high output and is used to indicate when the scan coincides with the programmed cursor position. The cursor position may be programmed to be any character in the address field. Furthemore, within the character, the cursor may be programmed to be any block of scan lines, since the start scan line and the end scan line are both programmable.

## LPEN

The LPEN signal is an edge-sensitive input and is used to load the internal Light Pen Register with the contents of the Refresh Scan Counter at the time the active edge occurs. The active edge of LPEN is the low-to-high transition.

#### CCLK

The CCLK signal is the character timing clock input and is used as the time base for all internal count/control functions.

#### RES

The RES signal-is an active-low input used to initialize all internal scan counter circuits. When RES is low, all internal counters are stopped and cleared, all scan and video outputs are low, and control registers are unaffected. RES must stay low for at least one CCLK period. All scan timing is initiated when RES goes high. In this way, RES can be used to synchronize display frame timing with line frequency.

## MEMORY ADDRESS SIGNAL DESCRIPTION

#### MA0-MA13 (Video Display RAM Address Lines)

These signals are active-high outputs and are used to address the Video Display RAM for character storage and display operations. The starting scan address is fully programmable and the ending scan address is determined by the total number of characters displayed, which is also programmable, in terms of characters/line and lines/frame.

## Binary Addressing

Characters are stored in successive memory locations. Thus, the software must be developed so that row and column co-ordinates are translated to sequentially-numbered addresses for video display memory operations.

## **RA0-RA4 (Raster Address Lines)**

These signals are active-high outputs and are used to select each raster scan within an individual character row. The number of raster scan lines is programmable and determines the character height, including spaces between character rows.

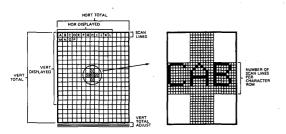

Figure 1. Video Display Format

## **Description of Internal Registers**

Figure 1 illustrates the format of a typical video display and is necessary to understand the functions of the various UM6845R internal registers. Figure 2 illustrates vertical and horizontal timing. Figure 3 summarizes the internal registers and indicates their address selection and read/ write capabilities.

#### Address Register

This is a 5-bit register which is used as a "pointer" to direct UM6845R data transfers to and from the system MPU. Its contents is the number of the desired register (0-31). When RS is low, then this register may be loaded; when RS is high, then the register selected is the one whose identity is stored in this register.

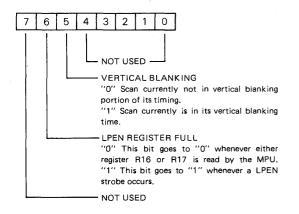

#### **Status Register**

This 2-bit register is used to monitor the status of the CRTC, as follows:

## Horizontal Total (R0)

This 8-bit register contains the total of displayed and non-displayed characters, minus one, per horizontal line. The frequency of HSYNC is thus determined by this register.

#### Horizontal Displayed (R1)

This 8-bit register contains the number of displayed characters per horizontal line.

#### Horizontal Sync Position (R2)

This 8-bit register contains the position of the HSYNC on the horizontal line, in terms of the character location number on the line. The position of the HSYNC determines the left-to-right location of the displayed text on the video screen. In this way, the side margins are adjusted.

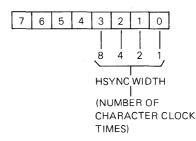

#### Horizontal and Vertical SYNC Widths (R3)

This 4-bit register programs the width of HSYNC.

VSYNC width is set to 16 scan line times.

#### Vertical Total (R4)

The Vertical Total Register is a 7-bit register containing the total number of character rows in a frame, minus one. This register, along with R5, determines the overall frame rate, which should be close to the line frequency to ensure flicker-free appearance. If the frame time is adjusted to be longer than the period of the line frequency, then RES may be used to provide absolute synchronism.

#### Vertical Total Adjust (R5)

The Vertical Total Adjust Register is a 5-bit write only register containing the number of additional scan lines needed to complete an entire frame scan and is intended as a fine adjustment for the video frame time.

#### Vertical Displayed (R6)

This 7-bit register contains the number of displayed character rows in each frame. In this way, the vertical size of the displayed text is determined.

#### Vertical Sync Position (R7)

This 7-bit register is used to select the character row time at which the VSYNC pulse is desired to occur and, thus, is used to position the displayed text in the vertical direction.

Figure 2. Vertical and Horizontal Timing

#### Mode Control (R8)

6 5 4 3

This register is used to select the operating modes of the UM6845R and is outlined as-follows:

#### Scan Line (R9)

This 5-bit register contains the number of scan lines per character row, including spacing minus one.

### Cursor Start (R10) and Cursor End (R11)

These 5-bit registers select the starting and ending scan lines for the cursor. In addition, bits 5 and 6 of R10 are used to select the cursor mode, as follows:

| В   | IT | CURSOR MODE                |

|-----|----|----------------------------|

| 6   | 5  | CORSON MODE                |

| 0   | 0  | No Blinking                |

| 0   | 1  | No Cursor                  |

| . 1 | 0  | Blink at 16 x field period |

| 1   | 1  | Blink at 32 x field period |

|       | Ŀ |                                      |

|-------|---|--------------------------------------|

| BI    | т | OPERATION                            |

| 1.    | 0 | UPENATION                            |

| <br>× | 0 | Non-Interlace                        |

| 0     | 1 | Interlace SYNC Raster Scan           |

| 1     | 1 | Interlace SYNC and Video Raster Scan |

5-32

Note that the ability to program both the start and end scan line for the cursor enables either block cursor or underline to be accommodated. Registers R14 and R15 are used to control the character position of the cursor over the entire 16K address field.

#### Display Start Address High (R12) and Low (R13)

These registers together comprise a 14-bit register whose contents is the memory address of the first character of the displayed scan (the character on the top left of the video display, as in Figure 4. Subsequent memory addresses are generated by the UM6845R as a result of CCLK input pulses. Scrolling of the display is accomplished by changing R12 and R13 to the memory address associated with the first character of the desired line of text to be displayed first. Entire pages of text may be scrolled or changed as well via R12 and R13.

#### Cursor Position High (R14) and Low (R15)

These registers together comprise a 14-bit register whose contents is the memory address of the current cursor position. When the video display scan counter (MA lines) matches the contents of this register, and when the scan line counter (RA lines) falls within the bounds set by R10 and R11, then the CURSOR output becomes active. Bit 5 of the Mode Control Register (R8) may be used to delay the CURSOR output by a full CCLK time to accommodate slow access memories.

#### LPEN High (R16) and Low (R17)

These registers together comprise a 14-bit register whose contents is the light pen strobe position, in terms of the video display address at which the strobe occurred. When the LPEN input changes from low to high, then, on the next negative-going edge of CCLK, the contents of the internal scan counter is stored in registers R16 and R17.

|    |    |   | Ado | lress | Reg. |     | Reg.  |                           | a                               |              |              |   |    | F         | legist    | er Bi                             | t.             |                           |                |

|----|----|---|-----|-------|------|-----|-------|---------------------------|---------------------------------|--------------|--------------|---|----|-----------|-----------|-----------------------------------|----------------|---------------------------|----------------|

| CS | RS | 4 | 3   | 2     | 1    | 0   | No.   | Register Name             | Stored Info.                    | RD           | WR           | 7 | 6  | 5         | 4         | 3                                 | 2              | 1                         | 0              |

| 1  |    | - | -   | -     | -    | -   | -     |                           |                                 |              |              |   |    |           | $\square$ |                                   |                | $\langle \rangle \rangle$ |                |

| 0  | 0  | - | -   | -     | -    | -   | -     | Address Reg.              | Red. No.                        |              | $\checkmark$ |   |    |           | A4        | A <sub>3</sub>                    | A <sub>2</sub> | A <sub>1</sub>            | A <sub>0</sub> |

| 0  | 0  | - | -   | -     | -    | -   | _     | Status Reg.               |                                 | $\checkmark$ |              |   | L  | V         |           | $\langle \rangle \langle \rangle$ | $\square$      | $\langle \rangle \rangle$ |                |

| 0  | 1  | 0 | 0   | 0     | 0    | 0   | RO    | Horiz. Total              | #Charac, -1                     |              | 1            | • | •  | •         | •         | •                                 | ٠              | ٠                         | •              |

| 0  | 1  | 0 | 0   | 0     | 0    | 1.  | R1    | Horiz. Displayed          | #Charac,                        |              | $\checkmark$ | ٠ | ٠  | •         |           | •                                 | •              | ٠                         | •              |

| 0  | 1  | 0 | 0   | 0     | 1    | 0   | R2    | Horiz, Sync<br>Position   | #Charac.                        |              | $\checkmark$ | • | •  | •         | •         | .•                                | •              | •                         | •              |

| 0  | 1  | 0 | 0   | 0     | 1    | 1 - | R3    | VSYNC, HSYNC<br>Widths    | #Scan Lines and<br>#Char, Times |              | $\checkmark$ |   |    |           |           | H <sub>3</sub>                    | H2             | н1                        | но             |

| 0  | 1  | 0 | 0   | 1     | 0    | 0   | R4    | Vert. Total               | #Charac, Rows -1                |              | $\checkmark$ |   | •  | •         | •         | •                                 | ٠              | •                         | •              |

| 0  | 1  | 0 | 0   | 1     | 0    | 1   | R5    | Vert, Total Adjust        | #Scan Lines                     |              | $\checkmark$ |   |    |           | •         | •                                 | .•             | ٠                         | ٠              |

| 0  | 1  | 0 | 0   | 1     | 1    | 0   | R6    | Vert, Displayed           | #Charac Rows                    |              | $\checkmark$ |   | •  | ٠         | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 0 | 0   | 1     | 1    | 1   | R7    | Vert. Sync Position       | #Charac, Rows                   |              | $\checkmark$ |   | •  | •         | •         | ٠                                 | ٠              | •                         | •              |

| 0  | 1  | 0 | 1   | 0     | 0    | 0   | R8    | Mode Control              |                                 |              | $\checkmark$ |   |    | $\square$ |           |                                   |                | 1                         | 10             |

| 0  | 1  | 0 | 1   | 0     | 0    | 1   | R9    | Scan Line                 | #Scan Lines-1                   |              | $\checkmark$ |   |    |           | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 0 | 1   | 0     | 1    | 0   | R10   | Cursor Start              | Scan Line No.                   |              | $\checkmark$ |   | В1 | Bo        | •         | •                                 | ٠              | •                         | •              |

| 0  | 1  | 0 | 1   | 0     | 1    | 1   | R11   | Cursor End                | Scan Line No.                   |              | $\checkmark$ |   |    |           | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 0 | 1   | 1     | 0    | 0   | R12   | Display Start<br>Addr (H) |                                 |              | $\checkmark$ |   |    |           | •         | •                                 | •              | •                         | ٠              |

| 0  | 1  | 0 | 1   | 1     | 0    | 1   | R13   | Display Start<br>Addr (L) |                                 |              |              | • | •  | •         | •         | •                                 | •              | •                         | •              |

| 0  | 1  | 0 | 1   | 1     | 1    | 0   | • R14 | Cursor Position (H)       |                                 | $\checkmark$ | $\checkmark$ |   |    | •         | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 0 | 1   | 1     | 1    | 1   | R15   | Cursor Position (L)       |                                 | $\checkmark$ | $\checkmark$ | ٠ | •  | •         | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 1 | 0   | 0     | 0    | 0   | R16   | Light Pen Reg (H)         |                                 | $\checkmark$ |              |   |    | •         | •         | •                                 | •              | ٠                         | •              |

| 0  | 1  | 1 | 0   | 0     | 0    | 1   | R17   | Light Pen Reg (L)         |                                 | $\checkmark$ |              | ٠ | •  | •         | •         | •                                 | •              |                           | •              |

Designates binary bit

Designates unused bit. Reading this bit is always "0", except for  $\overline{CS} = 1$ , which does not drive the data bus at all.

Figure 3. Internal Register Summary

# UM6845R / UM6845RA / UM6845RB

|          |         |      |      |      |        | V 0   |      | _ = 90 |              |      |      |         |      |

|----------|---------|------|------|------|--------|-------|------|--------|--------------|------|------|---------|------|

| _        |         |      |      | [    | JISPLA | Y = 8 | 0    |        |              |      |      |         |      |

|          |         | 0    | 1    | 2    |        |       | 77   | 78     | 79           | 80   | 81   |         | 89   |

|          |         | 80   | 81   | 82   |        |       | 157  | 158    | 159          | 160  | 161  |         | 169  |

|          | 24      | 160  | 161  | 162  |        |       | 237  | 238    | 239          | 240  | 241  | • • • • | 249  |

|          | u       |      |      |      |        |       |      |        |              |      | ·    |         | 1    |

| 34       | DISPLAY |      |      |      |        |       |      |        | ·  <br> <br> |      |      |         |      |

|          | - DIS   |      |      |      |        |       |      | ·      |              |      |      |         |      |

| TOTAL. = |         | 1760 | 1761 | 1762 |        |       | 1837 | 1838   | 1839         | 1840 | 1841 |         | 1849 |

| Ŭ        |         | 1840 | 1841 | 1842 |        |       | 1917 | 1918   | 1919         | 1920 | 1921 |         | 1929 |

|          |         | 1920 | 1921 | 1922 |        |       | 1997 | 1998   | 1999         | 2000 | 2001 |         | 2009 |

|          |         | 2000 | 2001 | 2002 |        | ,     | 2077 | 2078   | 2079         | 2080 | 2081 |         | 2089 |

|          |         |      |      |      |        |       |      |        |              |      |      |         |      |

|          | -       | 2640 | 2641 | 2642 |        |       | 2717 | 2718   | 2719         | 2720 | 2721 |         | 2729 |

----- TOTAL = 90

STRAIGHT BINARY ADDRESSING SEQUENCE

Figure 4. Display Address Sequences (with Start

Address = 0) for 80 x 24 Example

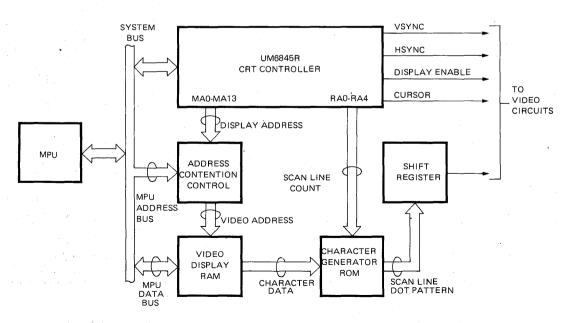

## Memory Contention Schemes for Shared Memory Addressing

From the diagram of Figure 5, it is clear that both the UM6845R and the system MPU must be capable of addressing the video display memory. The UM6845R repetitively fetches character information to generate the video signals in order to keep the screen display active. The MPU occasionally accesses the memory to change the displayed information or to read out current data characters. Three ways of resolving this dual-contention requirement are apparent:

### MPU PRIORITY

In this technique, the address lines to the video display memory are normally driven by the UM6845R unless the MPU needs access, in which case the MPU addresses immediately override those from the UM6845R and the MPU has immediate access.

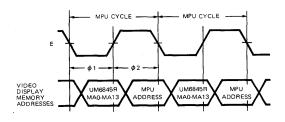

#### φ1/φ2 MEMORY INTERLEAVING

This method permits both the UM6845R and the MPU access to the video display memory by time-sharing via the system  $\phi 1$  and  $\phi 2$  clocks. During the  $\phi 1$  portion of each cycle (the time when E is low), the UM6845R address outputs are gated to the video display memory. In the  $\phi 2$  time, the MPU address lines are switched in. In this way, both the UM6845R and the MPU have unimpeded access to the memory. Figure 6 illustrates the timings.

Figure 6.  $\phi 1/\phi 2$  Interleaving

#### INTERLACE MODES

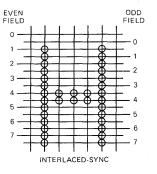

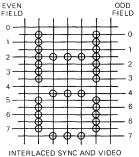

There are three raster-scan display modes (see Figure 7).

a) <u>Non-Interlaced Mode.</u> In this mode each scan line is refreshed at the vertical field rate (50 or 60Hz).

In the interlaced scan modes, even and odd fields alternate to generate frames. The horizontal and vertical timing relationship causes the scan lines in the odd fields to be displaced from those in the even fields. The two additional raster-scan display modes pertain to interlaced scans.

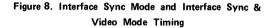

- b) Interlace Sync Mode. This mode is used when the same information is to be displayed in both odd and even fields. Enhanced readability results because the spaces between adjacent rows are filled and a higher quality character is displayed. This is achieved with only a slight alteration in the device operation: in alternate fields, the position of the VSYNC signal is delayed by ½ of a scan line time. This is illustrated in Figure 8 and is the only difference in the UM6845R operation in this mode.

- c) Interlaced Sync and Video Mode. This mode is used to double the character density on the screen by displaying the even lines in even fields and the odd lines in odd fields. As in the Interlace-Sync mode, the VSYNC position is delayed in alternate display fields. In addition, the address generation is altered.

Figure 7. Comparison of Display Modes

٠

# CRTC Register Comparison Table

.

NON-INTERLACE

| Register                         | UM6845R<br>MC6845<br>MC6845*1                                                                                                                                                                  | MC6845R<br>HD6845R                                                                                                                                     | UM6845<br>HD6845S                                                                                              | UM6845E                                                                | SYS6545-1                          |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------|

| R0 Htotal                        | Total-1                                                                                                                                                                                        | Total-1                                                                                                                                                | Total-1                                                                                                        | Total-1                                                                | Total-1                            |

| R1 Hdisp                         | Actual                                                                                                                                                                                         | Actual                                                                                                                                                 | Actual                                                                                                         | Actual                                                                 | Actual                             |

| R2 Hsync                         | Actual                                                                                                                                                                                         | Actual                                                                                                                                                 | Actual                                                                                                         | Actual                                                                 | Actual                             |

| R3 Sync Width                    | Horizontal<br>(& Vertical *1)                                                                                                                                                                  | Horizontal                                                                                                                                             | Horizontal<br>& Vertical                                                                                       | Horizontal<br>& Vertical                                               | Horizontal<br>& Vertical           |

| R4 Vtotal                        | Total-1                                                                                                                                                                                        | Total-1                                                                                                                                                | Total-1                                                                                                        | Total-1                                                                | Total-1                            |

| R5 Vtotal Adjustment             | Any Value                                                                                                                                                                                      | Any Value                                                                                                                                              | Any Value                                                                                                      | Any Value                                                              | Any Value<br>Except R5             |

| R6 Vdisp                         | Any Value<br><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""></r4<></td></r4<></td></r4<></td></r4<></td></r4<> | Any Value<br><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""></r4<></td></r4<></td></r4<></td></r4<> | Any Value<br><r4< td=""><td>Any Value<br/><r4< td=""><td>Any Value<br/><r4< td=""></r4<></td></r4<></td></r4<> | Any Value<br><r4< td=""><td>Any Value<br/><r4< td=""></r4<></td></r4<> | Any Value<br><r4< td=""></r4<>     |

| R7 Vsync                         | Actual-1                                                                                                                                                                                       | Actual-1                                                                                                                                               | Actual-1                                                                                                       | Actual-1                                                               | Actual-1                           |

| R8 B0-1                          | Interlace                                                                                                                                                                                      | Interlace                                                                                                                                              | Interlace                                                                                                      | Interlace                                                              | Interlace                          |

| Mode B2<br>Select                | -                                                                                                                                                                                              | _                                                                                                                                                      |                                                                                                                | Row/Column or<br>Binary Addr.                                          | Row/Column or<br>Binary Addr.      |

| вз                               | -                                                                                                                                                                                              | -                                                                                                                                                      | -                                                                                                              | Shared or<br>Transparent<br>Addr.                                      | Shared or<br>Transparent<br>Addr.  |

| B4                               | (Display Enable<br>Skew *1)                                                                                                                                                                    |                                                                                                                                                        | Display Enable<br>Skew                                                                                         | Display Enable<br>Skew                                                 | Display Enable<br>Skew             |

| B5<br>B6<br>B7                   | (Display Enable<br>Skew *1)<br>(Cursor Skew *1)<br>(Cursor Skew *1)                                                                                                                            |                                                                                                                                                        | Display Enable<br>Skew<br>Cursor Skew<br>Cursor Skew                                                           | Cursor Skew<br>RA4/<br>Transparent                                     | Cursor Skew<br>RA4/<br>Transparent |

| R9 Scan Lines                    | Total-1                                                                                                                                                                                        | Total-1                                                                                                                                                | Total-1                                                                                                        | Total-1                                                                | Total-1                            |

| R10 Cursor Start                 | Actual                                                                                                                                                                                         | Actual                                                                                                                                                 | Actual                                                                                                         | Actual                                                                 | Actual                             |

| R11 Cursor End                   | Actual                                                                                                                                                                                         | Actual                                                                                                                                                 | Actual                                                                                                         | Actual                                                                 | Actual                             |

| R12/R13 Display Addr.            | Write Only<br>Read Write<br>(MC6845 & *1)                                                                                                                                                      | Read/Write                                                                                                                                             | Read/Write                                                                                                     | Write Only                                                             | Write Only                         |

| R14/R15 Cursor Position          | Read/Write                                                                                                                                                                                     | Read/Write                                                                                                                                             | Read/Write                                                                                                     | Read/Write                                                             | Read/Write                         |

| R16/R17 Position                 | Read Only                                                                                                                                                                                      | Read Only                                                                                                                                              | Read Only                                                                                                      | Read Only                                                              | Read Only                          |

| R18/R19 Update<br>Addr. Register | N/A                                                                                                                                                                                            | N/A                                                                                                                                                    | N/A                                                                                                            | Transparent<br>Mode Only                                               | Transparent<br>Mode Only           |

| R31 Dummy Register               | N/A                                                                                                                                                                                            | N/A                                                                                                                                                    | N/A                                                                                                            | Transparent<br>Mode Only                                               | Transparent<br>Mode Only           |

| Status Register                  | Yes (UM6845R)                                                                                                                                                                                  | No                                                                                                                                                     | No                                                                                                             | Yes                                                                    | Yes                                |

# CRTC Register Comparison Table (Continued)

## INTERLACE SYNC

| Register  | UM6845R<br>MC6845<br>MC6845*1 | MC6845 R<br>HD6845 R | UM6845<br>HD6845S | UM6845E                  | SYS6545-1     |

|-----------|-------------------------------|----------------------|-------------------|--------------------------|---------------|

| R0 Htotal | Total-1 = Odd<br>or Even      | Total-1 = Odd        | Total-1 = Odd     | Total-1 = Odd<br>or Even | Total-1 = Odd |

## INTERALACE SYNC AND VIDEO

| R4 Vtotal        | Total-1             | Total-1              | Total-1             | Total-1             | Total/2-1           |

|------------------|---------------------|----------------------|---------------------|---------------------|---------------------|

| R6 Vdisp         | Total               | Total/2              | Total               | Total               | Total/2             |

| R7 Vsync         | Actual-1            | Actual-1             | Actual-1            | Actual-1            | Actual/2            |

| R9 Scan Lines    | Total-1<br>Odd/Even | Total-1<br>Only Even | Total-1<br>Odd/Even | Total-1<br>Odd/Even | Total-1<br>Odd/Even |

| R10 Cursor Start | Odd/Even            | Both Odd or          | Odd/Even            | Odd/Even            | Odd/Even            |

| R11 Cursor End   | Odd/Even            | Both Even            | Odd/Even            | Odd/Even            | Odd/Even            |

| ICCLK            | 2.5 MHz             | 2.5 MHz              | 3.7 MHz             | 3.7 MHz             | 2.5 MHz             |

## **Ordering Information**

| Part Number | CPU Clock Rate | Package |

|-------------|----------------|---------|

| UM6845R     | 1 MHz          | Plastic |

| UM6845RA    | 2 MHz          | Plastic |

| UM6845RB    | 3 MHz          | Plastic |