# **UM82C01**

# Capacitance Keyboard Encoder (CKE)

#### **Features**

- 16x8 matrix, can build up to 128 key capacitance

- Single chip with 16 scan drive outputs and 8 sense

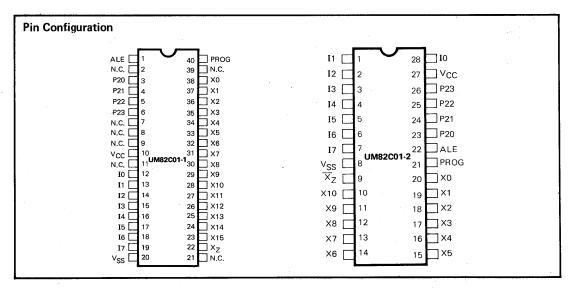

- Two types of package. 28 pin for 88 key KB and 40 pin for 128 key KB

- Keyboard scanning and encoding under complete control of the user's computer, especially UM8048 microcomputer

- Single 5V supply

- High-speed CMOS technology

- Serve as easy interface to UM8048

- New CMOS sense technology, CMOS analog sense circuit is built in

- Byte wide sense, higher performance than serial sense technology

- Wide UM8048 frequency range, 1M to 11 MHz UM8048 can be used

#### General Description

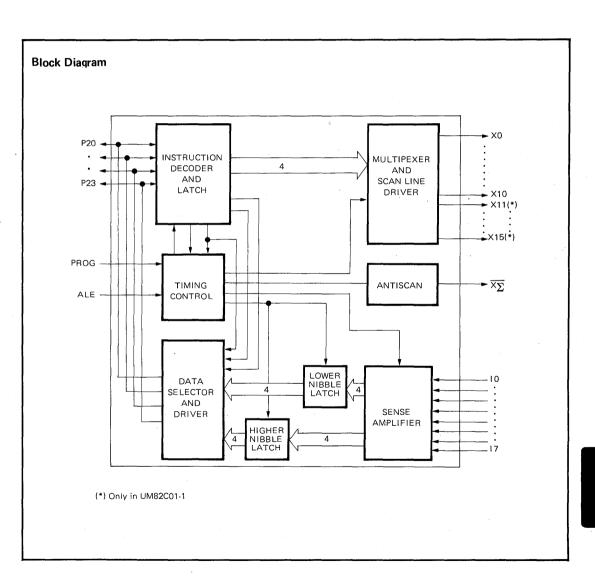

UM82C01 is a CMOS LSI, which offers interface between microcomputer and capacitive keyboard matrix. 40 pin UM82C01-1 is capable of scanning up to 128 lowcost capacitive keys. 28 pin UM82C01-2 serve keyboard applications with less than 88 keys.

The keyboard scan is under complete control of the UM8048 series microcomputer writing to expand I/O port, port 2 data is multiplexed to initiate one of the scan lines. Sense circuit will receive the scan signal through capacitive keys if one key is pressed. Sense circuit includes CMOS analog and digital circuit, which sense action by

following amplifing and latching of analog signal from capacitive switch. These 8 bits data are then divided and latched marcing two nibbles. Two instructions can read these two nibbles from port 2. Then the microcomputer can analyze them and generate the scan code.

Antiscan is used to enhance the simple capacitive switches that are usually used in capacitive keyboard, offering switching threshold in sense input. This provides the keyboard with mechanical hysteresis which builts in the more expensive hall-effect and reed switches.

#### **Absolute Maximum Ratings**

| Operating Temperature 0° to 70°C          |

|-------------------------------------------|

| Storage Temperature                       |

| Power Supply Max. 7V                      |

| Voltage on Any Pin Vss =0.7V to Vsc +0.7V |

#### \*Comments

Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may effect device reliability.

### D.C. Characteristics

(Operating Voltage 5V ± 10%)

| Item    | Parameter                      | Symbol                  | Min.                  | Тур. | Max.            | Units | Conditions                        |

|---------|--------------------------------|-------------------------|-----------------------|------|-----------------|-------|-----------------------------------|

|         | Input Low Voltage              | VIL                     | -0.5                  |      | 0.8             | ٧     |                                   |

|         | Input High Voltage             | V <sub>IH</sub>         | 2.0                   |      | V <sub>CC</sub> | V     |                                   |

| Digital | Output Low Voltage, I/O Port   | VOLP                    |                       |      | 0.45            | ٧     | I <sub>OL</sub> = 5 mA            |

|         | Output High Voltage, I/O Port  | V <sub>CHP</sub>        | V <sub>CC</sub> -0.45 |      | Vcc             | ٧.    | I <sub>OH</sub> = -400 <b>μ</b> Α |

|         | Output Low Voltage, Scan Line  | Vols                    | ,                     |      | 0.45            | ٧     | I <sub>OL</sub> = 5 mA            |

|         | Output High Voltage, Scan Line | V <sub>OHS</sub>        | V <sub>CC</sub> -0.45 | -    | Vcc             | ٧     | I <sub>OH</sub> = -5 mA           |

| Analas  | Input High to Reference        | $\Delta$ V <sub>H</sub> | 0.1                   |      | 1.8             | ٧     | Lying on Voltage                  |

| Analog  | Input Low to Reference         | Δ∨ړ                     | -0.1                  |      | -1.8            | V     | Reference V <sub>REF</sub>        |

| Operati | ng Current                     | lcc                     |                       |      | 15              | m:A   |                                   |

| Stand b | y Power Supply Current         | l <sub>SB</sub>         |                       |      | 200             | μΑ    | No sensing and<br>Scanning        |

# A.C. Characteristics

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, \ V_{CC} = 5V \pm 10\%, \ V_{SS} = 0V)$

| Characteristics            | Symbol           | UM8048/UM82C01 |      |                                         |        |      |      | Units      | Conditions  |

|----------------------------|------------------|----------------|------|-----------------------------------------|--------|------|------|------------|-------------|

| Characteristics            | Symbol           | 4 MHz          |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 11 MHz |      |      | Omits      | Collaitions |

|                            |                  | Min.           | Тур. | Max.                                    | Min.   | Тур. | Max. |            |             |

| Address Latch Width        | tLL              | 700 .          |      |                                         | 150    |      |      | ns         |             |

| Cycle Time                 | t <sub>CY</sub>  | 3.75           |      |                                         | 1.36   |      |      | <b>μ</b> s |             |

| Port Control Setup to PROG | t <sub>CP</sub>  | 420            |      |                                         | 100    |      |      | ns         |             |

| Port Control Hold to PROG  | t <sub>PC</sub>  | 800            |      |                                         | 160    |      |      | ns         |             |

| Port Output Data Setup     | top              | 1350           |      |                                         | 400    |      |      | ns         |             |

| Port Data Hold from PROG   | t <sub>PD</sub>  | 320            |      |                                         | 90     | l    |      | ns         |             |

| PROG Strobe to ALE         | t <sub>CAI</sub> | 210            |      |                                         | 50     |      |      | ns         |             |

| PROG Pulse Width           | tpp              | 2370           |      |                                         | 700    |      |      | ns         |             |

| PROG to Port 2 Input Valid | t <sub>PR</sub>  |                |      | 2130                                    |        |      | 700  | ns         |             |

| Input Data Hold from PROG  | tpF              |                |      | 380                                     |        |      | 140  | ns         |             |

| ALE to SCAN Setup          | t <sub>AS1</sub> |                |      | 200                                     |        |      | 100  | ns         |             |

| ALE to SCAN Ended          | t <sub>AS2</sub> |                |      | 200                                     |        |      | 100  | ns         |             |

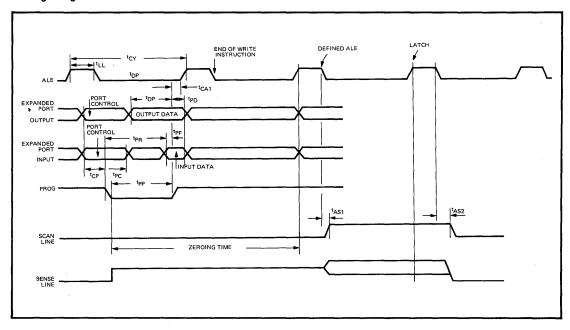

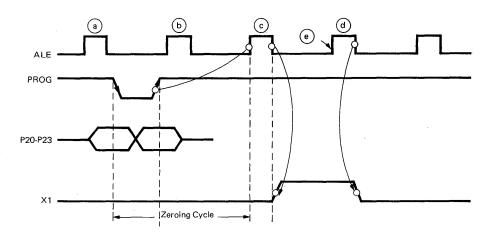

# Timing Diagram

# Pin Description

| ſ       |                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|---------|--------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin     | Names                          | 1/0 | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| P20-P23 | I/O Port                       | 1/0 | This four-bit bidirectional port contains the address and control bits from UM8048 $\mu$ C on a high to low transition of PROG. During a low to high transition of the PROG signal, the port contains the selected scan data for UM82C01 if the last command is a write operation. The sense nibble data from UM82C01 is latched during the low to high transition if the last command is a read operation. There exists a state flow in two continuous read operations which is called "read cycle". Upper nibble coming from sense inputs I4 to I7 are transferred in P20 to P23 from UM82C01 during low to high transition of PROG of MOVD A, P5 instruction, and lower nibble coming from I0 to I3 are transferred in P20 to P23 during low to high transition of PROG of MOVD A, P4 instruction. |  |  |  |  |  |

| ALE     | Address Latch<br>Enable Strobe |     | This pin comes direct from UM8048 ALE. It is used as the time base as well as address latch strobe. Our target is to let UM8048 work between 1MHz to 11MHz, so ALE varies from 66.6KHz to 733.3KHz. General PC key boards use 4 to 5MHz UM8048, hence, ALE is typically a 266.6KHz strobe signal for a 4MHz UM8048. When ALE first goes from low to high in a write cycle, the PROG is activated and goes to low and at this time, Port 2 containing port address and write instruction code is valid and should be latched by UM82C01 to initiate the scan mode.                                                                                                                                                                                                                                     |  |  |  |  |  |

## Pin Description (Continued)

| Pin                | Names                          | I/O | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|--------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALE                | Address Latch<br>Enable Strobe |     | UM82C01 begins Zeroing stage of its sense amplifier at this instant. PROG will go to high before second ALE of this write instruction. The Zeroing stage ends at the next ALE low to high transient. If you see Timing Diagram on P. 11, you will find that this edge triggers the selected scan line to be active. The second ALE, which is next to end write instruction, is used to control scan line to inactive and its active transient is the high to low edge. In read cycle, when first ALE goes from high to low, PROG is activated to go to low, port 2 containing port address and read instruction code is valid and should be latched by UM82C01 to initiate the read mode. |

| PROG               | Control Strobe                 | 1   | An active low strobe comes direct from UM8048 PROG. In the view point of UM8048, PROG is a control strobe to expanded I/O. UM82C01 is designed to locate expanded port 4 and port 5 in UM8048.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                                |     | Every time PROG is activated, UM82C01 is initiated to enter write or read mode. When PROG goes inactive in a write cycle, selected scan data is valid in port 2 and is latched by UM82C01 to encode the scan line. In a read cycle, latched upper nibble and lower nibble are valid circularly in port 2 at every PROG low to high transition.                                                                                                                                                                                                                                                                                                                                            |

| X0-X15             | Scan Line Out                  | 0   | These are the 16 full range drive outputs. One of the lines is activated in a write cycle. Selected scan data is latched and used to decode these sixteen scan lines so the scanning is fully programmable by UM8048. The selected scan line is activated in the defined ALE rising edge and ended in the next ALE falling edge. (Reference to Timing Diagram on P. 11) The defined ALE is the first ALE after the write instruction is finished. There are eleven scan lines for 28 pin UM82C01-2 X11 to X15 and are included in scan line driver for 40 pin UM82C01-1.                                                                                                                  |

| $\overline{X}_{Z}$ | Antiscan Out                   | 0   | This is the antiscan output. This output is activated whenever no scanning occurs, and is deactivated when any one of X0 to X15 is activated. Antiscan is used to reduce the voltage in sense input when there is no scanning that prevents logic error.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10-17              | Sense Line Input               | -   | These eight lines are inputs from capacitance keyboard matrix. The small current pulses caused by the scan lines and pressed keyswitches are detected here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Vcc                | Power Supply                   | ı   | Connected to +5V power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>SS</sub>    | Ground                         |     | Normally connected to +0V ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **Application Description**

#### The Microprocessor

The capacitance keyboard encoder (CKE) UM82C01 is designed to serve as an interface to UM8048 series 8-bit microprocessor. The user can control the keyboard function easily through programming of microprocessor, which includes scanning reading and serve as an interface to host computer.

#### The Keyboard

A keyboard is an array of switches. The array consists of two dimensional matrix. One side of the matrix (X-lines) is used to drive the array with a microprocessor chosen signal, while the other side (1-lines) is connected to sense circuits. In traditional configuration, users make use of mechanical contact switches. With a new sensing mechanism, capacitive switches present a good solution.

#### The Capacitive Switch

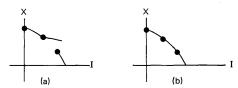

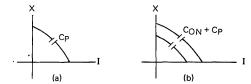

Figure 1. Mechanical Switch (a) Key off (b) Key on

Fig. 1 shows the traditional mechanical switch, (a) The key switch is off, X-line and I-line are open to each other, (b) The key switch is on, X-line and i-line short together. Fig. 2, shows the capacitive switch, (a) The key switch is

Figure 2. Capacitive Switch (a) Key off (b) key on

off; only a small parasitic capacitance exists between X-line and I-line, (b) The key switch is on, a Con + Cp appears between X-line and I-line.

$$V_{D} = \begin{array}{c} C \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_{D} = \begin{array}{c} C \\ \hline \\ \end{array} \\ V_$$

$$\triangle V_{SENSE1} = V_D \cdot \frac{\frac{1}{C_S}}{\frac{1}{C_S} + \frac{1}{C}} = V_D \cdot \frac{C}{C_S + C}$$

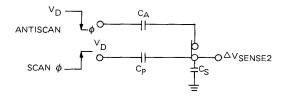

Figure 3a. Equivalent circuit for Capacitive Key

$$O^{\triangle V}_{SENSE2}$$

$\triangle^{V}_{SENSE2} = V_D \frac{C_P}{C_S + C_P + C_A} - V_D \frac{C_A}{C_S + C_P + C_A}$

Figure 3b. Equivalent circuit for Capacitive Key with Antiscan Consideration

In Fig. 3a, an equivalent circuit for capacitive key is shown. The voltage  $\Delta V_{SENSE1}$  is decided by the scanning voltage VD, capacitance C and Cs.

In Fig. 3b, an antiscanning consideration is presented.

The scanning trigger edge is taking place with the inverse voltage "antiscan". After this edge, the voltage  $\Delta V_{SENSE2}$ is decided by the voltage devided by CP minus the voltage divided by CA.

#### Writing

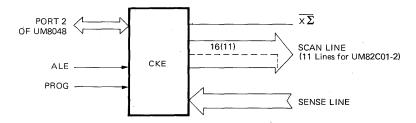

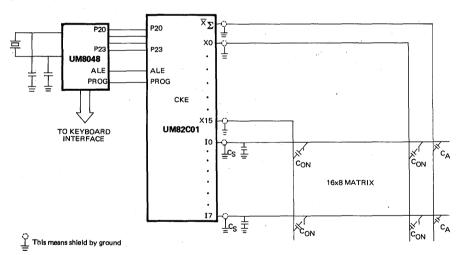

Figure 4. Logic Symbol of the CKE

In system configuration, the CKE is designed to stand in the expanded I/O port of 8048 microcomputer. The CKE uses the PORT 2, ALE and PROG to serve as an interface to the microprocessor. When 8048 writes a scan code to CKE, the CKE must be accessed through the

expanded PORT 4. When UM8048 reads the sensing code from the CKE, the CKE must be accessed through the expanded PORT 4 and 5. The PORT 6 and 7 are reserved for the user.

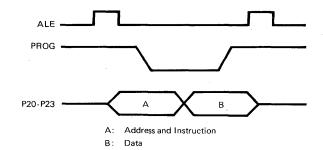

Figure 5. PROG Timing of UM8048 I/O PORT Expansion

| Address     | P21 | P20 | PORT        | Definitions         |

|-------------|-----|-----|-------------|---------------------|

| _           | 0 . | 0   | PORT 4      | Writing Port        |

|             | 0   | 1   | PORT 5      | (Same as PORT 4)    |

|             | 1 - | 0   | PORT 6      |                     |

|             | 1   | 1   | PORT 7      |                     |

| Instruction | P23 | P22 | Instruction | Definitions         |

|             | 0   | 0   | READ        |                     |

|             | 0   | 1   | WRITE       | Writing Instruction |

|             | 1   | 0   | OR          |                     |

|             | • 1 | 1   | AND         |                     |

Figure 6. Expanded Port Definition in Writing Cycle

By using PORT 4 (PORT 5 the same) of UM8048 series microcomputer, the user can write his scanning data to the CKE chip. After the writing, two NOP instructions should be used to permit correct decoding and scanning.

The timing diagram is shown in Fig. 7.

For example, if the user wants to scan  $X_1$ -line, the recommended Assembly is as listed:

| Label  | Command                 | Arguments | Comments                               |

|--------|-------------------------|-----------|----------------------------------------|

| SCAN1: | :<br>MOV                | Α, #φ1Η   | ; #φ1H Can Vary From<br>; #φφΗ Το #φFΗ |

|        | MOVD<br>NOP<br>NOP<br>: | P4, A     | ; Wait Until CKE Starts<br>; Scanning. |

- (a) First ALE of MOVD instruction

- (b) Second ALE of MOVD instruction

- © ALE of first NOP instruction

- d ALE of second NOP instruction

- Edge of latch sense data

Figure 7. Timing Diagram of Writing and Scanning

#### Scanning

The CKE latches port address and instruction at the PROG high to low edge in Fig. 7, then enters the writing mode. At the PROG low to high edge, the CKE latches the data in P20–P23 which is now defined as the expanded PORT 4, and decodes the data to select the programmed scan line. Although the decoding and selection does not take much time, the scan line does not activate immediately.

From the PROG falling edge to the rising edge of the ALE, to the MÖVD instruction in Fig. 7, the Sense Amplifier of CKE is "Zeroing". After the zeroing cycle, all the sense input are balanced at the reference voltage, and the selected scan line is activated at the falling edge of this ALE.

The scanning line  $X_0$  to  $X_{15}$  can each be decoded from the hexadecimal data programmed in the PORT 4 at the writing cycle.

The scanning cycle equals to an ALE cycle, so the scanning closes at the ALE falling edge of second NOP instruction as shown in Fig. 7. Before the end of scanning, Sense Amplifier will latch the sense data; these will be discussed in the Sensing section.

#### Antiscan

Antiscan line  $X_{\Sigma}$  is low whenever any scanning is activated, and is high when all scan line  $X_0$  to  $X_{18}$  are low.

If no key is pressed, the antiscan will generate a  $-\Delta V$  to the reference voltage, so that the Sense Amplifier will sense a voltage lower than reference voltage and latch a denoted low after amplification. If any key is pressed and the key is scanned, the voltage divided by the on capacitance will be a  $+\Delta V$ , so that the Sense Amplifier will sense a voltage higher than reference and latch a logic high after amplification.

The effect on whether antiscanning is larger than scanning depends on whether the key is pressed or not A new CMOS sense technology called "Sense Amplifier" is built in the CKE. In Fig. 8, we show the zeroing and sensing of this technology. In zeroing cycle, the switch between the input and output of the inverter is closed, so the sense input pad equals the reference voltage. After zeroing cycle, the shorting switch at the inverting stage is opened and sensing circuit is activated. In Fig. 7, we can see scanning also starts after zeroing. In fact, sensing is there writing for scanning. During the scanning cycle,

#### Sensing

(b) Sensing

Fig. 8. Zeroing and Sensing

the CKE will latch the sensing input at the edge in Fig. 7.

The CKE uses byte-wide sensing, and has 8-bit latches. After latching, the data is separated into two nibbles, called Higher Nibble and Lower Nibble, and stored.

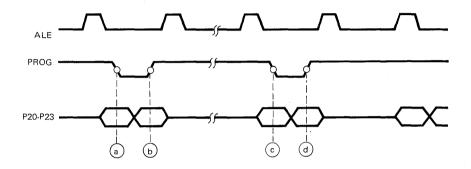

# Reading

Because the CKE serves as an interface to UM8048 microcomputer by expanded PORT, the data must be 4-bit wide. Whenever there is data in the latches, the user can read the sensing data in nibble form. The CKE is designed to stand at the PORT 4 and PORT 5 in reading cycle.

| Address     | P21 | P20 | PORT        | Definitions           |

|-------------|-----|-----|-------------|-----------------------|

|             | 0   | 0   | PORT 4      | Reading Lower Nibble  |

|             | . 0 | 1   | PORT 5      | Reading Higher Nibble |

|             | 1   | 0   | PORT 6      | Not used              |

|             | 1 . | 1   | PORT 7      | Not Used              |

|             |     |     |             |                       |

| Instruction | P23 | P22 | Instruction | Definitions           |

|             | 0   | 0   | Read        | Reading Instruction   |

|             | 0   | 1   | Write       |                       |

|             | 1   | 0   | Or          |                       |

|             | 1   | 1   | And         |                       |

The latched data can be read by UM8048 in two read instructions, these two instructions need not but can be continuous, and higher nibble is defined to be read from PORT 5, lower nibble from PORT 4. Users must pay attention for if no reading is instructed before the next

writing, 82C01 will reject the writing instruction until the reading instruction have been excuited.

The recommended reading Assembly is as listed and the timing diagram is shown in Fig. 10.

| Label       | Command | Arguments                        | Comments                   |

|-------------|---------|----------------------------------|----------------------------|

| *· <u>-</u> | :       | AND THE PERSON NAMED IN COLUMN 1 |                            |

| Read 1:     | MOVD    | A, P5                            | ; Read Higher Nibble       |

|             | SWAP    | A                                | -                          |

|             | MOV     | Rn, A                            |                            |

| Read 2:     | MOVD    | A, P4                            | ; Read Lower Nibble and    |

|             | ORL     | A, Rn                            | ; Combine Nibbles to be By |

|             |         |                                  |                            |

- (a) Port address and instruction of READ 1

- (b) High nibble output from CKE

- C Port address and instruction of READ 2

- d Lower nibble output from CKE

Figure 10. Port Timing of Reading

After the reading cycle, the microcomputer can use the read data to generate scan code or key code easily.

#### **Application Note**

UM82C01 is a new solution for capacitance keyboard.

The application there for differs from the present capacitance Con and P.C. Board parasitic capacitance Cp of general capacitance keyboard and consideration should be given to design take them into. Con and Cp are listed in Table 1.  $C_S$ ,  $C_A$  and  $C_{BS}$  are listed in Table 2. Table 3 (a) and (b) are recommendations of the capacitance selection.

Table 1. Definition of Con and Co

| Name                         | Symbol          | Min. | Тур. | Max. | Unit |

|------------------------------|-----------------|------|------|------|------|

| Key on Capacitance           | C <sub>ON</sub> | 8    | 20   |      | pf   |

| P.C.B. Parasitic Capacitance | СР              |      | 1    | 3    | pf   |

Table 2. Definition of  $C_S$ ,  $C_A$  and  $C_{BS}$

| Name                                                                       | Symbol                                              | Min. | Тур. | Max.          | Unit           |

|----------------------------------------------------------------------------|-----------------------------------------------------|------|------|---------------|----------------|

| Shunt Capacitance<br>Antiscan Capacitance<br>Capacitance between two sense | C <sub>S</sub><br>C <sub>A</sub><br>C <sub>BS</sub> | 4    | 80   | 150<br>8<br>5 | pf<br>pf<br>pf |

Table 3. Recommended Application of  $C_{\mbox{\scriptsize A}}$  for various  $C_{\mbox{\scriptsize ON}}$

| Symbol                                              | Ra           | Unit         |                |  |

|-----------------------------------------------------|--------------|--------------|----------------|--|

|                                                     | Lower        | Upper        |                |  |

| C <sub>ON</sub><br>C <sub>A</sub><br>C <sub>P</sub> | 10<br>4<br>0 | 25<br>8<br>3 | pf<br>pf<br>pf |  |

(a)

| Lower | T     | Unit          |

|-------|-------|---------------|

| LOWEI | Upper |               |

| 25    | 35    | pf            |

| 8     | 15    | pf            |

| 0     | 3     | pf            |

|       |       | 25 35<br>8 15 |

(b)

# **Typical Application**

# **Ordering Information**

| Part Number | Package |

|-------------|---------|

| UM82C01-1   | 40 DIP  |

| UM82C01-2   | 28 DIP  |