# UM8321

CRT Video Attributes Controller(VAC)

6933922 6-0-0-2

#### Features

- On chip attributes logic Reverse video

- Character blank

- Character blink

- Underline

- Full/half intensity

- Four modes of operation Wide graphics Thin graphics

Character mode without underline

- Character mode with underline

- On Chip logic for double height double width characters

Accepts scan line information in parallel or serial format

#### **General Description**

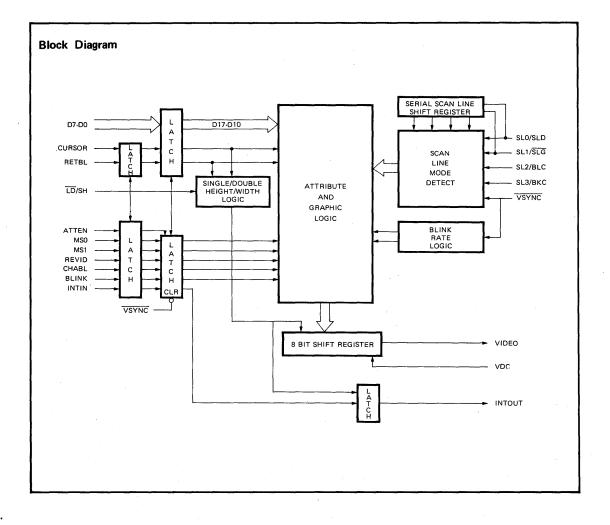

The UM8321 Video Attributes Controller (VAC) is an n-channel MOS/LSI device containing graphics logic, attributes logic, data and attributes latches, cursor control and a high speed video shift register. A character generator ROM and a CRT Video attributes controller UM8321 provide all of the major circuitry for the display portion of a CRT video terminal.

The UM8321 serial video output may be connected directly to 3 CRT monitor's video input.

The UM8321 attributes include: reverse video, underline, character blank, character blink, and full/half intensity selection. In addition. When used in conjunction with the UM9007, the UM8321 will provide double height or double width characters.

Four programmable cursor modes are provided on the UM8321. They are underline, blinking underline, reserve video character block, and blinking reverse video character block. When used in the serial scan line input mode, the cursor mode may be selected via two input pins. When used in the parallel scan line input mode, the cursor mode is a mask program option and is fixed at the time of manufacture.

Two graphics modes are provided. In the wide graphics mode, the UM8321 produces a graphic entity the size of the character block. The graphic entity contains eight parts, each of which is associated with one bit of the input byte, thereby providing 256 unique graphic symbols. The thin graphics mode enables the user to create thin line drawings and forms.

- Four cursor modes dynamically selectable via 2 input pins

- Underline Blinking underline

- Reverse video

- Blinking reverse video

- Programmable character blink rate

- Programmable cursor blink rate

- On chip data and attribute latches

- +5 volt operation

- TTL compatible

- MOS n-Channel silicon gate

- Compatible with UM9007

In both graphics rnodes, continuous horizontal and vertical lines may be drawn. Additional flexibility is provided by allowing the mask programming of the placement and dimensions of the blocks or lines within a character block. In the thin graphics mode, mask programming allows serrated horizontal or vertical lines.

#### Absolute Maximum Ratings\*

| Operating Temperature Range 0°C to +70°C     |

|----------------------------------------------|

| Storage Temperature Range –55°C to +150°C    |

| Lead Temperature (soldering, 10 sec.)        |

| Positive Voltage on any Pin, with respect to |

| ground                                       |

| Negative Voltage on any Pin, with respect    |

| to ground $\ldots \ldots -0.3V$              |

|                                              |

#### \*Comments

Streeses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

Note: When powering this device from laboratory or system power supplies, it is important that the Absolute Maximum Ratings not be exceeded or device failure can result. Some power supplies exhibit voltage spikes or "glitches" on their outputs when the AC power is switched on and off. In addition, voltage transients on the AC power line may appear on the DC output. If this possibility exists it is suggested that a clamp circuit be used.

# **Electrical Characteristics** ( $T_A = 0^{\circ}C$ to $70^{\circ}C$ , $V_{CC} = +5V \pm 5\%$ , unless otherwise noted)

# D.C. CHARACTERISTICS

| Parameter                   | Min. | Тур. | Max. | Units | Conditions                                                    |

|-----------------------------|------|------|------|-------|---------------------------------------------------------------|

| Input Voltage Levels        |      |      |      |       |                                                               |

| Low Level $V_{1L}$          |      | ļ    | 0.8  | V     |                                                               |

| High Level V <sub>IH1</sub> | 2.0  |      |      | V     | All inputs except VDC, LD/SH                                  |

| High Level V <sub>IH2</sub> | 4.3  | 1    | ĺ    | V     | For VDC, LD/SH Input                                          |

| Output Voltage Levels       |      |      |      |       |                                                               |

| Low Level V <sub>OL</sub>   |      |      | 0.4  | V     | l <sub>OL</sub> ≐ 0.4 mA                                      |

| High Level V <sub>OH</sub>  | 2.4  |      |      | V     | I <sub>OH</sub> = 100 <i>µ</i> A                              |

| Input Leakage Current       |      |      |      |       |                                                               |

| Leakage I <sub>L1</sub>     |      |      | 10   | μΑ    | $0 \leq V_{IN} < V_{CC}$ ; excluding VDC, $\overline{LD}$ /SH |

| Leakage I <sub>L2</sub>     |      |      | 50   | μΑ    | $0 \leq V_{IN} < V_{CC}$ , for VDC LD/SH                      |

| Input Capacitance           |      |      |      |       |                                                               |

| C <sub>IN1</sub>            |      | 10   |      | pf    | Excluding VDC, LD/SH                                          |

| C <sub>IN2</sub>            |      | 20   |      | pf    | For LD/SH                                                     |

| C <sub>IN3</sub>            |      | 25   |      | pf    | For VDC                                                       |

| Power Supply Current        |      |      |      |       |                                                               |

| lcc                         |      | 60   | 80   | mA    |                                                               |

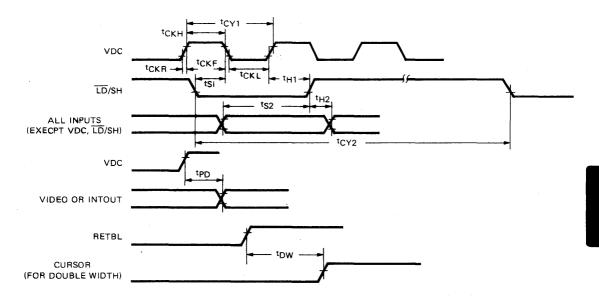

## A.C. CHARACTERISTICS

| Parameter            | Min. | Тур. | Max. | Units | Conditions                      |

|----------------------|------|------|------|-------|---------------------------------|

| VDC                  |      | ,    |      |       |                                 |

| 1/tCY1 VDC Frequency | 1.0  |      | 28.5 | MHz   |                                 |

| tCKL VDC Low         | 10   |      |      | ns    |                                 |

| tCKH VDC High        | 10   |      |      | ns    |                                 |

| tCKR VDC Rise Time   | 10   |      | 10   | ns    | Measured from 10% to 90% points |

| tCKF VDC Fall Time   |      |      | 10   | ns    | Measured from 90% to 10% points |

| LD/SH                |      |      |      |       |                                 |

| tCY2                 | 315  |      |      | ns    |                                 |

| tS1                  | 7    |      |      | ns    |                                 |

| tH1                  | 0    |      |      | ns    |                                 |

| Input Setup and Hold |      |      |      |       |                                 |

| tS2                  | 35   |      |      | ns    |                                 |

| <sup>t</sup> H2      | 0    |      | 1    | ns    |                                 |

| Miscellaneous Timing |      |      |      |       |                                 |

| tPD                  |      |      | 35   | ns    | СL = 15 pf                      |

| tDW                  | tCY2 |      |      |       |                                 |

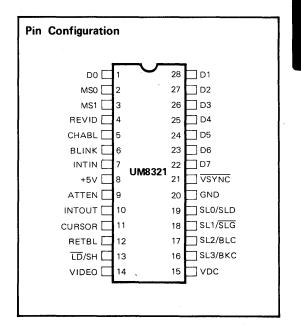

# Pin Description

| Pin No.                             | Name                           | Symbol     | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|--------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

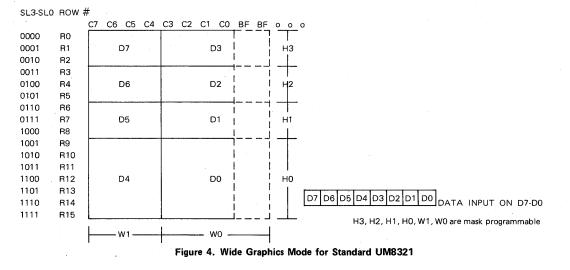

| 1, 28, 27,<br>26, 25, 24,<br>23, 22 | Data                           | D7-D0      | In the character mode, the data on these inputs is passed through the Attributes logic into the 8 bit high speed video shift register. The binary information on D7 will be the first bit output after the LD/SH input goes low. In the thin or wide graphics mode these 8 inputs will individually control the on/off condition of the particular portion of the character block of line drawing. Figure 4 and Figure 5 illustrate the wide and thin graphics modes respectively and their relationships to D7-D0.                                                                                                                                                     |

| 2<br>3                              | Mode Select 0<br>Mode Select 1 | MSO<br>MS1 | These 2 inputs define the four modes of operation of the UM8321 as<br>follows:<br>MS1, MS0 = 00; Wide graphics mode<br>= 10; Thin graphics mode<br>= 01; Character mode without underline<br>= 11; Character mode with underline<br>See section entitled Display Modes for details.                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                                   | Reverse Video                  | REVID      | When this input and Retrace Blank (RETBL) are both low, data from the Attributes and Graphics logic is presented directly to the video shift register. When this input is high and RETBL is low, the Attribute and Graphics logic will invert the data before presenting it to the video shift register.                                                                                                                                                                                                                                                                                                                                                                |

| 5                                   | Character blank                | CHABL      | When this input is high, the parallel inputs to the video shift register are<br>all set low (or high depending on the state of REVID) thus providing a<br>constant video level for the entire length of the character block.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6                                   | Blink                          | BLINK      | When this input is high and both the RETBL and CHABL inputs are low, the character will blink at the programmed character blink rate. Blinking is accomplished by causing the video to go to the background level during the "off" portion of the Character Blink cycle. This video level may be either the white or black level depending on state of REVID. The duty cycle for the character blink is 75/25 (on/off). This input is ignored if it coincides with the CURSOR input and the cursor is formatted to blink.                                                                                                                                               |

| 7                                   | Intensity In                   | INTIN      | The INTIN input along with the INTOUT output provides a user controlled general purpose attribute. Data input to INTIN will appear at INTOUT with the same delay as that from any other attribute input to the serial video output (VIDEO). By using an external mixing circuit, it is possible to raise or lower the voltage level of the video output to produce such attributes as "half intensity" or "intensity".                                                                                                                                                                                                                                                  |

| 8                                   | Supply Voltage                 | +5V        | +5 volt power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9                                   | Attribute<br>Enable            | ATTEN      | When this input is high, the internal attributelatch is updated at the positive going edge of the $\overline{LD}/SH$ input with data appearing on the REVID, CHABL, MS1, MS0, BLINK and INTIN inputs. By selectively bringing this input high, the user will update the attribute only at specific character times; all subsequent characters will carry with them the attributes last updated thus allowing "field" or "embedded" attributes. When using a wide video memory where attribute bits are attached to every character, the internal attribute latch may be updated at each character by tieing this input high (thus allowing for "invisible" attributes). |

| 10                                  | Intensity Out                  | INTOUT     | This output is used in conjunction with the INTIN Input to provide a three character pipeline delay to allow for general purpose attributes (such as intensity) to be implemented. See INTIN (pin 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11                                  | Cursor                         | CURSOR     | When this input is high and RETBL is low, the programmed cursor format will be displayed. When this input is high, and RETBL is high, the UM8321 enters the double width mode. See section entitled cursor formats for details.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

CRT Controller

## Pin Description (Continued)

| Pin No. | Name          | Symbol | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12      | Retrace Blank | RETBL  | When this input is high, the parallel inputs to the video shift register are unconditionally cleared to all zeros and loaded on the next LD/SH pulse. This forces the VIDEO output to a low voltage level, independent of all attributes, for blanking the CRT during horizontal and vertical retrace time.                                                                                                                                                                                                                   |

| 13      | Load/Shift    | LD/SH  | The 8 bit video shift register parallel-in load or serial-out shift operation is established by the state of this input. When high, this input enables the shift register for serial shifting with each video dot clock pulse (VDC input). When low, the video shift register is parallel loaded on the next video dot clock pulse and all data and attributes are moved to the next position in the internal pipeline. In addition, input data and attributes are latched on the positive transition of $\overline{LD}/SH$ . |

| 14      | Video         | VIDEO  | The Video output provides the serial dot stream to the CRT. Video is shifted out on the rising edge of the video dot clock VDC. The timing of $\overline{LD}/SH$ input will determine the number of backfill dots. See Figure 1.                                                                                                                                                                                                                                                                                              |

| PIN No. | Name                        | Symbol  | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|-----------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15      | Video Dot<br>Clock          | VDC     | This input clock controls the rate at which video is shifted out on the VIDEO output.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16      | Scan line<br>3/Block Cursor | SL3/BKC | This input has two separate functions depending on the way scan line<br>information is presented to the UM8321.<br>Parallel scan line mode – This input is the most significant bit of the<br>binary scan line row address.<br>Serial scan line mode – This input controls the cursor's physical dimen-<br>sions. If high the cursor will appear as a reverse video block (the entire<br>character cell will be displayed in reverse video). If low, the cursor will<br>appear as an underline on the scan line(s) programmed. |

# Pin Description (Continued)

| Pin No. | Name                             | Symbol  | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | Scan line<br>2/Blink Cursor      | SL3/BLC | This input has two separate functions depending on the way scan line information is presented to the UM8321.<br>Parallel scan line mode — This input is the second most significant bit of the binary scan line row address.<br>Serial scan line mode — This input if low, will cause the cursor to alternate between normal and reverse video at the programmed cursor blink rate.<br>The duty cycle for the cursor blink is 50/50 (on/off). If this input is high, the cursor will be non-blinking.                                                                |

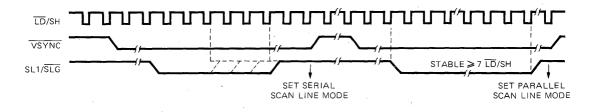

| 18      | Scan Line<br>1/Scan Line<br>Gate | SL1/SLG | This input has two separate functions depending on the way scan line information is presented to the UM8321.<br>Parallel scan line mode – This input is the next to the least significant bit of the binary scan line row address.<br>Serial scan line mode – This input will be low for 5 or 6 LD/SH pulses to allow the scan line information to be serially shifted into the serial scan line shift register. If this signal is low for 7 or more LD/SH pulses, the UM8321 will assume the parallel input scan line row address mode.                             |

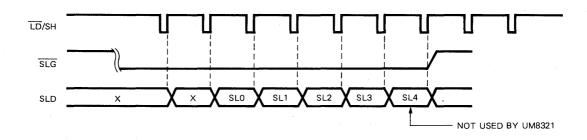

| 19      | Scan line<br>0/Scan Line<br>data | SL0/SLD | This input has two separate functions depending on the way scan line information is presented to the UM8321. Refer to Figure 2. Parallel scan line mode – This input is the least significant bit of the binary scan line row address. Serial scan line mode – This input will present the scan line information in serial form (least significant bit first) to the UM8321 and permits the proper scan line information to enter the serial scan line shift register during the $\overline{\text{LD}}/\text{SH}$ pulses framed by $\overline{\text{SLG}}$ (pin 18). |

| PIN No. | Name          | Symbol | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20      | Ground        | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21      | Vertical Sync | VSYNC  | This input is typically connected to the vertical sync output of the CRT controller and is used as the clock input for the two on-chip mask programmable blink rate dividers. The cursor blink rate (50/50 duty cycle) will always be twice the character blank rate (75/25 duty cycle). In addition, the internal attributes are reset when this input is low. The VSYNC input is also used to determine the scan line mode (parallel or serial) used. See the section "Scan Line Input Modes". |

#### **Attributes Function**

| Retrace Blank   | - | The RETBL input causes the VIDEO<br>to go to the zero (black) level regard-<br>less of the state of all other inputs.                 |

|-----------------|---|---------------------------------------------------------------------------------------------------------------------------------------|

| Reverse Video   | - | The REVID input causes inverted data to be loaded into the video shift register.                                                      |

| Character Blank | - | The CHABL input forces the video<br>to go to the current background<br>level as defined by Reverse Video.                             |

| Underline       | _ | MS1, MS0 = 1, 1 forces the video to<br>go to the inverse of the background<br>level for thescan lines(s) programmed<br>for underline. |

Blink

The BLINK input will cause characters to blink by forcing the video to the background level 25% of the time and allowing the normal video for 75% of the time. When the cursor is programmed to blink (not controlled by the BLINK input), the video alternates from normal to reverse video at 50% duty cycle. The cursor blink rate always overrides the character blink rate when they both appear at the same character position.

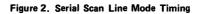

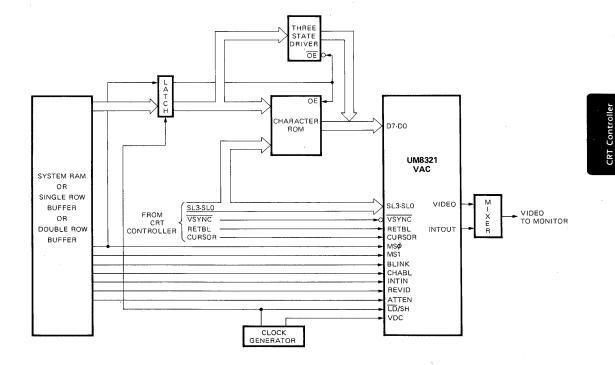

Intensity (Half Intensity) The INTIN input and the INTOUT output allow an intensity (or half intensity) attribute to be carried through the pipeline of the UM8321. An external mixer can be used to combine VICEO and INTOUT to create the desired video level. See Figure 3a and Figure 3b.

#### Figure 3a: UM8321 System Configuration in Parallel Scan Line Mode

.

Figure 3b: UM8321 System Configuration in Serial Scan Line mode

Table 1 illustrates the effect of the REVID, CHABL, UNDLN attributes as a function of the cursor format and the CURSOR and RETBL inputs.

| Cursor Format          |       | UN     | 18321 Inp | uts   |                | Video Shift Register Loaded With                                                |

|------------------------|-------|--------|-----------|-------|----------------|---------------------------------------------------------------------------------|

| Cursor Format          | Retbl | Cursor | Revid     | Chabl | Undin          |                                                                                 |

|                        | 1     | ×      | х ,       | ×     | ×              | All zero's                                                                      |

| · .                    | 0     | 0      | 0         | 0     | 0              | Data                                                                            |

|                        | 0     | 0      | 0         | 0     | 1              | DATA for selected scan line (s); Data for all other scan lines                  |

| <b>x</b>               | 0     | 0      | 0         | 1     | ×              | All zero's                                                                      |

|                        | 0     | 0      | 1         | 0     | 0              | DATA                                                                            |

|                        | 0     | 0      | 1         | 0     | 1              | DATA for selected scan line (s); data for all other scan lines                  |

|                        | 0     | 0      | 1         | 1     | x              | One's for all scan lines                                                        |

|                        | 0     | 1      | 0         | 0     | x <sup>1</sup> | DATA for selected scan line (s) for cursor;<br>data for all other scan lines    |

| Underline <sup>2</sup> | 0     | 1      | 0         | 1     | ×1             | One's for selected scan line(s) for cursor;<br>zero's for all other scan lines  |

| Underline              | 0     | 1      | 1         | 0     | ×1             | DATA for selected scan line (s) for cursor;<br>Data for all other scan lines    |

|                        | 0     | 1      | 1         | 1     | ×1             | Zero's for selected scan line (s) for cursor;<br>one's for all other scan lines |

| Table | 1  | UM8321  | Attribute | Combinations |

|-------|----|---------|-----------|--------------|

| Iavie | •. | 0100321 | Aumute    | Compinations |

#### Table 1. UM8321 Attribute Combinations (Continued)

| 0                                    |       | UN     | /18321 Inp | outs  |       | Video Shift Register Loaded with                                                     |                                                                                      |  |

|--------------------------------------|-------|--------|------------|-------|-------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Cursor Format                        | Retbl | Cursor | Revid      | Chabl | Undin | Video Shift Regis                                                                    | ter Loaded with                                                                      |  |

|                                      | 0     | 1      | 0          | 0     | ×1    | DATA for selected scan line(s) blinking;<br>Data for all other scan lines.           |                                                                                      |  |

| Blinking <sup>3</sup>                | 0     | 1      | 0          | 1     | ×1    | One's for selected scan lir<br>zero's for all other scan li                          |                                                                                      |  |

| Underline <sup>2</sup>               | 0     | 1      | 1          | 0     | ×1    | DATA for selected scan<br>Data for all other scan lin                                | <b>.</b>                                                                             |  |

|                                      | 0     | 1      | 1          | 1     | ×1    | Zero's for selected scan<br>one's for all other scan lir                             | -                                                                                    |  |

|                                      | 0     | 1      | 0          | 0     | 0     | Data for all scan lines.                                                             |                                                                                      |  |

|                                      | 0     | 1      | 0          | 0     | 1     | Data for selected scan line(s) for underline;<br>data for all other scan lines.      |                                                                                      |  |

| Revid Block                          | 0     | 1      | 0          | 1     | ×     | One's for all scan lines.                                                            |                                                                                      |  |

| HEVIG BIOCK                          | 0     | 1      | 1          | 0     | 0     | Data for all scan lines                                                              |                                                                                      |  |

|                                      | 0     | 1      | 1          | 0     | 1     | DATA for selected scan line(s) for underline;<br>data for all other scan lines       |                                                                                      |  |

|                                      | 0     | 1      | 1          | 1     | ×     | Zero's for all scan lines                                                            |                                                                                      |  |

|                                      | 0     | 1      | 0 .        | 0     | 0     | On<br>Data for all scan lines                                                        | Off<br>Data for all scan lines                                                       |  |

|                                      | 0     | 1.     | 0          | . 0   | 1     | Data for selected<br>scan line(s) for<br>underline; Data for<br>all other scan lines | Data for selected<br>scan line(s) for<br>underline; Data for<br>all other scan lines |  |

| Blinking <sup>3</sup><br>Revid Block | 0     | 1      | 0          | 1     | ×     | One's for all scan lines                                                             | Zero's for all scan lines                                                            |  |

|                                      | 0     | 1      | 1          | 0     | 0     | Data for all scan lines                                                              | Data for all scan lines                                                              |  |

|                                      | 0     | 1      | 1          | 0     | 1     | DATA for selected<br>scan line(s); Data<br>for all other scan lines                  | DATA for selected<br>scan line(s); Data<br>for all other scan lines                  |  |

|                                      | 0     | 1      | - 1        | 1     | ×     | Zero's for all scan lines                                                            | One's for all scan lines                                                             |  |

1 - if the programmed scan line(s) for cursor and underline coincide, the cursor takes precedence; otherwise both are displayed.

2 - at programmed scan line(s) for underline

3-at cursor blink rate

Note: cursor blink rate overrides character blink rate.

ø

#### **Display Modes**

Inputs MS1 and MS0 select one of four display modes. All attributes except underline operate independent of the display mode used. Figures 3a and 3b illustrate a typical UM8321 configuration which operates in all display modes for both the parallel and serial scan line modes respectively.

MS1, MS0 = 00 – Wide Graphics Mode. – In this display mode, inputs D7-D0 define a graphics entity as illustrated in figure 4. Note that individual bits in D7-D0 will illuminate particular portion of the character block. Table 2 shows all programming ranges possible when defining the wide graphic boundaries. No underline is possible in this display mode.

#### Table 2. Wide Graphics Mask Programming Options

| Options                   | Choices                   | Standard UM8321                  |  |

|---------------------------|---------------------------|----------------------------------|--|

| Height of graphic block*  |                           |                                  |  |

| D7 and D3                 | any scan line(s)          | R0, R1, R2                       |  |

| D6 and D2                 | any scan line(s)          | R3, R4, R5                       |  |

| -D5 and D1                | any scan line(s)          | R6, R7, R8                       |  |

| D4 and D0                 | any scan line(s)          | R9, R10, R11, R12, R13, R14, R15 |  |

| Width of D7, D6, D5, D4** | any number of dots 0 to 8 | C7, C6, C5, C4                   |  |

| Width of D3, D2, D1, D0** | any number of dots 0 to 8 | C3, C2, C1, C0, BF               |  |

\* Any graphic block pair can be removed by programming for zero scan lines.

\*\* Total number of dots for both must be equal to the total dots per character with no overlap.

MS1, MS0 = 10 – Thin Graphics Mode. In this display mode, inputs D7-D0 define a graphic entity as illustrated in figure 5. Note that individual bits in D7-D0 will illuminate particular horizontal or vertical line segments within the character block. Table 3 shows all programming ranges possible when defining the thin graphics boundaries. No underline is possible in this display mode.

| SL3-SL | 0 ROW      |    |          |    |          |         | но          | RIZONTAL LENGT  | H VERTICAL POSIT  |

|--------|------------|----|----------|----|----------|---------|-------------|-----------------|-------------------|

|        |            | C7 | C6 C5 C4 | C3 | C2 C1 C0 | BF BF o |             |                 |                   |

| 0000   | RO         |    | D4       |    |          | F ]     | D2          | C7-C3           | PROGRAMMABI       |

| 0001   | <b>R</b> 1 |    |          | +  |          | 11      | D3          | C3-BF           | PROGRAMMABL       |

| 0010   | R2         |    |          |    |          | 1       | D4          | C7-BF*          | PROGRAMMABL       |

| 0011   | R3         | D7 |          | DO |          | D6 !    | D5          | C7-BF*          | PROGRAMMABL       |

| 0100   | R4         |    |          |    |          |         | L           |                 |                   |

| 0101   | R5         |    | D2       |    | D3       | 1       |             |                 |                   |

| 0110   | R6         |    |          | -  |          | 1i      | VE          | RTICAL HEIGHT H | ORIZONTAL POSITIC |

| 0111   | R7         |    |          |    |          | 1 1     |             | R0-R5           |                   |

| 1000   | R8         |    |          | D1 |          |         |             |                 | PROGRAMMABI       |

| 1001   | R9         |    |          |    |          |         | D1          | R6-R15          | PROGRAMMABL       |

| 1010   | B10        |    |          |    |          | 1 1     | D6          | R0-R15*         | PROGRAMMABL       |

| 1011   | B11        |    | D5       |    |          | 1       | D7          | R0-R15*         | PROGRAMMABL       |

| 1100   | R12        | -  |          |    |          |         |             |                 |                   |

| 1101   | R13        |    |          |    |          | !       | D7 D6 D5 D4 |                 |                   |

| 1110   | R14        |    |          |    |          |         | D7 D6 D5 D4 | D3 D2 D1 D0     | DATA INPUT ON D7- |

|        | B15        |    |          |    |          |         |             |                 |                   |

#### Table 3. Thin Graphics Mask Programming Options

| Options                                         | Choices                                                                                                   | Standard UM8321                                 |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Backfill                                        | C1 or C0                                                                                                  | CO                                              |

| Horizontal position for                         |                                                                                                           | tannon tanan matangan at da sana tanan ta       |

| D2 and D3<br>D4<br>D5                           | any scan line(s) RO-R15<br>any scan line(s) RO-R15<br>any scan line(s) RO-R15                             | R5<br>R0<br>R11                                 |

| Horizontal length for                           |                                                                                                           |                                                 |

| D2 <sup>2</sup><br>D3 <sup>2</sup>              | any continuous dots C7-C0, BF<br>all dots not covered by D2                                               | C7-C3<br>C3-BF                                  |

| Blanked dots for serrated ho                    | rizontal lines                                                                                            |                                                 |

| D2<br>D3<br>D4 and D5                           | any dot(s) C7-C0, BF<br>any dot(s) C7-C0, BF<br>any dot(s) C7-C0, BF                                      | none<br>none<br>none                            |

| Vertical position for                           |                                                                                                           | <u></u>                                         |

| D0 and D1<br>D6 <sup>1</sup><br>D7 <sup>1</sup> | any dot(s) C7-C0, BF<br>any dot(s) C6-C0, BF<br>any dot(s) C7-C0                                          | C3<br>BF<br>C7                                  |

| Vertical length for                             |                                                                                                           |                                                 |

| D0<br>D1<br>D6<br>D7                            | any scan line(s)<br>all scan lines not used by D0<br>no choice; always R0-R15<br>no choice; always R0-R15 | R0 to R5<br>R6 to R15<br>R0 to R15<br>R0 to R15 |

1 - D7 must always come before D6 With no overlap; otherwise D6 is lost.

2 - D2 and D3 must always over only one dot.

- MS1, MS0 = 01 Character Mode Without Underline. In this display mode, inputs D7-D0 go directly from the input latch to the video shift register via the Attributes and Graphics logic. This mode requires either a bit mapped system RAM (1 bit in RAM equals 1 pixal on the CRT) or an external character generator as shown in figures 3a and 3B.

- MS1, MS0 = 11 Character Mode With Underline. Same operation as MS1, MS0 = 01 with the underline attribute appearing on the scan line(s) mask programmed.

#### BACKFILL

Backfill is a mechanism that allows a character width of greater than 8 dots and provides dot information (usually blanks) for all dot positions beyonds 8. The character width is defined by the period of the  $\overline{\text{LD}/\text{SH}}$

#### Table 4. Cursor Formats

input. For the character modes, backfill is added to the tail end of the character by two methods which are mask programmable.

| Method A | _ | The backfill (BF) dots will be the same as the dot displayed in position C7. |

|----------|---|------------------------------------------------------------------------------|

| Method B | - | The backfill (BF) dots will be the same as the dot displayed in position CO. |

For the wide graphics mode, the backfill dots will always be the same as the dot displayed in position C0 (method B) with no programmable option.

#### CURSOR FORMATS

Four cursor formats are possible with the UM8321. If the parallel scan line input mode is used, one of four cursor formats may be selected as a mask programmed option. If the serial scan line input mode is used, the cursor format is selected via input pins 16 and 17 (SL3/BKC, SL2/ BLC). See Table 4. The four cursor modes are as follows:

| Scan Line Input Mode | Pin 17 | Pin 16 | Cursor Function              |

|----------------------|--------|--------|------------------------------|

|                      | 1      | 0      | Underline                    |

| Serial               | 1      | 1      | Reverse Video Block          |

|                      | 0      | 0      | Blinking Underline           |

|                      | 0      | . 1    | Blinking Reverse Video Block |

| Parallel             | ×      | ×      | Mask programmable Only       |

| Underline                         | The cursor will appear as an under-<br>line. The position and width of<br>the cursor underline is mask pro-<br>grammed.                                                                                     |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blinking Underline—               | The cursor will appear as an under-<br>line. The underline will alternate<br>between normal and reverse video<br>at the mask programmed cursor<br>blink rate.                                               |

| Reverse Video –<br>Block          | The cursor will appear as a reverse<br>Video Block (The entire character<br>cell will be displayed in reverse<br>video).                                                                                    |

| Blinking Reverse —<br>Video Block | The cursor will appear as a reverse<br>video Jlock and the entire block<br>(character plus background) will<br>alternate between normal and reverse<br>video at the masked programmed<br>cursor blink rate. |

#### **Double Width Mode**

In order to display dobuble width characters, video must

be shifted out at half frequency and the video shift register must receive new information (parallel load) every other LD/SH input pulse. In order to divide the video dot clock (VDC) and the LD/SH pulse internally at the proper time, the cursor input should be pulsed during RETBL prior to the scan line to be displayed as double width. The CURSOR input must remain low for a minimum of 1 LD/SH period from the leading edge of RETBL. The CURSOR input can stay high for the entire RETBL time but should not extend into active video. If it does, a cursor will be displayed. It is assumed that the CRT controller knows when a particular scan line should be double width and it should activate the CURSOR in the manner just described. Double height/ double width characters can also be displayed if the scan line count is incremented by the CRT controller every other scan line. With respect to the UM8321, no distinction between double width and double height display is necessary. Figure 6 illustrates timing for both single and double width modes. The UM9007, which supports double height double width characters, will produce the CURSOR signal as required by the UM8321 with no additional hardware.

Attributes include MS0, MS1, BLINK, CHABL, INTENSITY, REVID

#### Scan Line Input Modes

Scan line information can be introduced into the UM8321 in parallel format or serial format. Table 5 illustrates the pin definition as a function of the scan line input mode. The UM8321 will automatically recognize the proper scan line mode by observing the activity on pin 18. In parallel mode, this input will be stable for at least 1 scan line and in serial mode this input will remain low for about 5 or 6  $\overline{\text{LD}}/\text{SH}$  periods. If pin 18 goes active low for less than seven but more than two con-

tinuous  $\overline{LD}/SH$  periods during the last scan line that has an active low on the  $\overline{VSYNC}$  input, the serial mode will be locked in for the next field. The parallel scan line input mode will be selected for the next field if the following two condition occur during  $\overline{VSYNC}$  low time. First, at least one positive transition must occur on pin 18 and second, pin 18 must be low for seven or more  $\overline{LD}/SH$  periods. Refer to Figure 7 for timing details.

| Table 5. Pin Definition for Parallel and Serial Scan Line N | Viodes |

|-------------------------------------------------------------|--------|

|-------------------------------------------------------------|--------|

| Scan Line Input Mode | UM8321 Pin Number |     |     |     |

|----------------------|-------------------|-----|-----|-----|

| Scan Line input wode | 19                | 18  | 17  | 16  |

| Serial               | SLD               | SLG | BLC | вкс |

| Parallel             | SL0               | SL1 | SL2 | SL3 |

Figure 7. Serial/Parallel Scan Line Mode Selection Timing

#### **Program Otpions**

The UM8321 has a variety of mask programmed options. Tables 2 and 3 illustrate the range of these options for the wide and thin graphics modes respectively. Table 6 illustrates the range of the miscellaneous mask programmed options. In addition, Table 2, 3 and 6 show the mask programmed options for the standard UM8321.

#### Table 6. Miscellaneous Mask Programming Options

| Options                                            | Choices                                                                                | Standard UM8321               |  |

|----------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------|--|

| Backfill in character mode                         | C7 or C0                                                                               | C7                            |  |

| Character blink rate (division of VSYNC frequency) | 8 to 60; divisible by 4<br>(7.5 Hz to 1 Hz) <sup>1</sup>                               | 32<br>(1.875 Hz) <sup>1</sup> |  |

| Cursor blink rate <sup>2</sup>                     | Twice the character<br>blink rate                                                      | 16<br>(3.75 Hz) <sup>1</sup>  |  |

| Character underline position                       | any scan line(s) R0-R15                                                                | R11                           |  |

| Cursor underline <sup>3</sup>                      | any scan line(s) R0-R15                                                                | not applicable                |  |

| Cursor format <sup>4</sup>                         | Underline<br>Blinking underline<br>Reverse video block<br>Blinking reverse video block | Blinking reverse video block  |  |

$1 - Assumes \overline{VSYNC}$  input frequency of 60 Hz.

2 - Valid only if the cursor is formatted to blink.

3 - Valid only if the cursor is formatted for underline.

4 - Valid for the parallel scan line mode only.

#### **Ordering Information**

| Part No. | Operation Option | Package Type |

|----------|------------------|--------------|

| 8321A    | 30 MHz           | Plastic      |

| 8321B    | 28.5 MHz         | Plastic      |