# LINEAR INTEGRATED CIRCUIT

# 5.0A, STEP-UP/DOWN/ INVERTING SWITCHING REGULATORS

### DESCRIPTION

The UTC **UMC33167** series are high performance fixed frequency power switching regulators that contain the primary functions required for dc-to-dc converters. This series was specifically designed to be incorporated in step-down and voltage-inverting configurations with a minimum number of external components and can also be used cost effectively in step-up applications.

These devices consist of an internal temperature compensated reference, fixed frequency oscillator with on-chip timing components, latching pulse width modulator for single pulse metering, high gain error amplifier, and a high current output switch.

Protective features consist of cycle-by-cycle current limiting, undervoltage lockout, and thermal shutdown. Also included is a low power standby mode that reduces power supply current to  $36\mu$ A.

## FEATURES

- \* Output Switch Current in Excess of 5.0A

- \* Fixed Frequency Oscillator (72kHz) with On-Chip Timing

- \* Provides 5.05V Output without External Resistor Divider

- \* Precision 2% Reference

- \* 0% ~ 95% Output Duty Cycle

- \* Cycle-by-Cycle Current Limiting

- \* Undervoltage Lockout with Hysteresis

- \* Internal Thermal Shutdown

- \* Operation from 7.5V ~ 40V

- \* Standby Mode Reduces Power Supply Current to 36µA

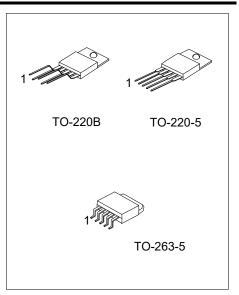

### ORDERING INFORMATION

| Ordering Number |                                 | Deelvere | Deaking   |  |

|-----------------|---------------------------------|----------|-----------|--|

| Lead Free       | Halogen Free                    | Package  | Packing   |  |

| UMC33167L-TA5-T | UMC33167L-TA5-T UMC33167G-TA5-T |          | Tube      |  |

| UMC33167L-TB5-T | UMC33167G-TB5-T                 | TO-220B  | Tube      |  |

| UMC33167L-TQ5-T | UMC33167G-TQ5-T                 | TO-263-5 | Tube      |  |

| UMC33167L-TQ5-T | UMC33167G-TQ5-T                 | TO-263-5 | Tape Reel |  |

| UMC33167G-TA5-T   |                                                 |

|-------------------|-------------------------------------------------|

| (1) Packing Type  | (1) T: Tube, R: Tape Reel                       |

| (2) Package Type  | (2) TA5: TO-220-5, TB5: TO-220B, TQ5: TO-263-5  |

| (3) Green Package | (3) G: Halogen Free and Lead Free, L: Lead Free |

## MARKING

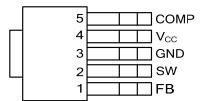

## PIN CONFIGURATION

### PIN DESCRIPTION

| PIN NO. | PIN NAME | FUNCTION                        |

|---------|----------|---------------------------------|

| 1       | FB       | Output voltage feedback control |

| 2       | SW       | Switch Output                   |

| 3       | GND      | Ground pin                      |

| 4       | Vcc      | IC power supply pin             |

| 5       | COMP     | Compensation pin                |

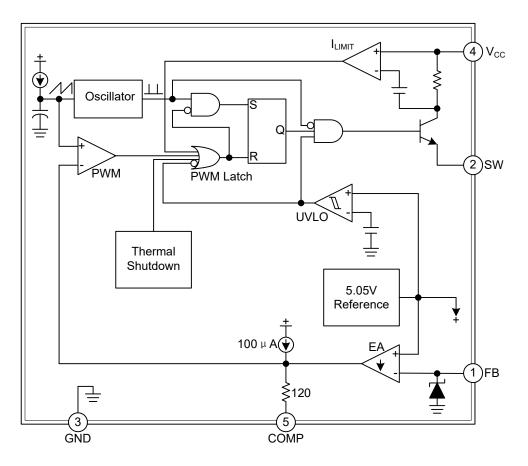

## BLOCK DIAGRAM

Figure 1 Simplified Block Diagram (Step Down Application)

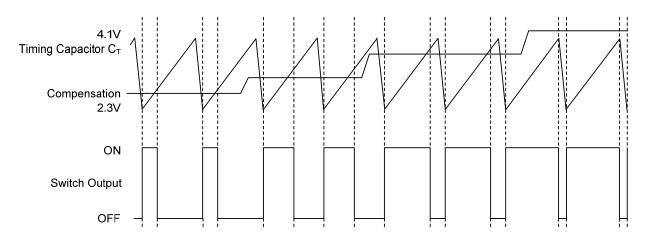

Figure 2. Timing Diagram

## ABSOLUTE MAXIMUM RATING (Note 2)

| PARAMETER                                                | SYMBOL                 | RATINGS                 | UNIT |

|----------------------------------------------------------|------------------------|-------------------------|------|

| Power Supply Input Voltage                               | Vcc                    | 40                      | V    |

| Switch Output Voltage Range                              | V <sub>O(switch)</sub> | -2.0 ~ +V <sub>IN</sub> | V    |

| Voltage Feedback and Compensation Input<br>Voltage Range | $V_{FB}, V_{COMP}$     | -1.0 ~ +7.0             | V    |

| Power Dissipation (T <sub>A</sub> =25°C)                 | PD                     | Internally Limited      | W    |

| Operating Junction Temperature                           | TJ                     | +150                    | °C   |

| Operating Ambient Temperature                            | T <sub>A</sub>         | -40 ~ +85               | °C   |

| Storage Temperature                                      | T <sub>STG</sub>       | -65 ~ 150               | °C   |

Notes: 1. Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

2. Maximum package power dissipation limits must be observed to prevent thermal shutdown activation.

This device series contains ESD protection and exceeds the following tests: Human Body Model 2000V per MIL-STD-883, Method 3015. Machine Model Method 200V.

#### THERMAL DATA

| PARAMETER           | SYMBOL | RATINGS | UNIT |

|---------------------|--------|---------|------|

| Junction to Ambient | θյΑ    | 65      | °C/W |

| Junction to Case    | θις    | 5.0     | °C/W |

## ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub>=12V, for typical values  $T_A$ =25°C, for min/max values  $T_A$  is the operating ambient temperature range that applies (Notes 4), unless otherwise noted.)

| 1                                       | olitei wise noteu.) |                      |                                                                              |      |         |         |          |

|-----------------------------------------|---------------------|----------------------|------------------------------------------------------------------------------|------|---------|---------|----------|

| PARAMETER                               |                     | SYMBOL               | TEST CONDITIONS                                                              | MIN  | TYP     | MAX     | UNIT     |

| OSCILLATOR                              |                     |                      |                                                                              |      |         |         |          |

| Frequency (V <sub>CC</sub> =7.5V ~ 40V) |                     | fosc                 | T <sub>A</sub> =25°C                                                         | 65   | 72      | 79      | KHz      |

|                                         |                     |                      | TJ=TLOW ~THIGH                                                               | 62   |         | 81      | KHz      |

| ERROR AMPLIFI                           | ER                  |                      |                                                                              |      |         |         |          |

| Voltage Feedback Input Threshold        |                     | V <sub>FB(th)</sub>  | T <sub>A</sub> =25°C                                                         | 4.95 | 5.05    | 5.15    | V        |

|                                         |                     |                      | TJ=TLOW ~THIGH                                                               | 4.85 |         | 5.20    | V        |

| Line Regulation                         |                     | RegLINE              | V <sub>CC</sub> =7.5V~ 40V, T <sub>A</sub> =25°C                             |      | 0.03    | 0.078   | %/V      |

| Input Bias Current                      |                     | I <sub>IB</sub>      | V <sub>FB</sub> =V <sub>FB(th)</sub> +0.15V                                  |      | 0.15    | 1.0     | μA       |

| Power Supply Rejection Ratio            |                     | PSRR                 | V <sub>CC</sub> =7.5V~ 40V, f=120H <sub>Z</sub>                              | 60   | 80      |         | dB       |

| Output Voltage                          | High State          | Vон                  | I <sub>SOURCE</sub> =75µA, V <sub>FB</sub> =4.5V                             | 4.2  | 4.9     |         | V        |

| Swing                                   | Low State           | Vol                  | I <sub>SINK</sub> =0.4mA, V <sub>FB</sub> =5.5V                              |      | 1.6     | 1.9     | V        |

| PWM COMPARA                             | TOR                 |                      |                                                                              |      |         |         |          |

|                                         |                     | DC <sub>(max)</sub>  | Maximum (V <sub>FB</sub> =0V)                                                | 92   | 95      | 100     | %        |

| Duty Cycle (V <sub>cc</sub> =           | 20V)                | DC(min)              | Minimum (V <sub>COMP</sub> =1.9V)                                            | 0    | 0       | 0       | %        |

| SWITCH OUTPU                            | Т                   |                      |                                                                              |      |         |         |          |

| Output Voltage So                       | ource Saturation    | VSAT                 | Vcc=7.5V, Isource=5.0A                                                       |      | Vcc-1.5 | Vcc-1.8 | V        |

| Off-State Leakage                       | e<br>e              | I <sub>SW(off)</sub> | $V_{CC}$ =40V, Pin 2 = GND                                                   |      | 0       | 100     | μA       |

| Current Limit Thre                      | eshold              | PK(switch)           | V <sub>CC</sub> =7.5V                                                        | 5.5  | 6.5     | 8.0     | Α        |

|                                         | Output Voltage Rise |                      | V <sub>CC</sub> =40V,I <sub>РК</sub> =5.0А, L=225µН,<br>Т <sub>А</sub> =25°С |      | 100     | 200     | -        |

| Switching Times                         | Time                |                      |                                                                              |      | 100     | 200     | ns       |

| Switching Times                         | Output Voltage Fall |                      |                                                                              |      | 50      | 100     | no       |

|                                         | Time                | ŀ                    |                                                                              |      | 50      | 100     | ns       |

| UNDERVOLTAG                             | E LOCKOUT           |                      |                                                                              |      |         |         |          |

| Startup Threshold                       |                     | Vth(UVLO)            | V <sub>CC</sub> Increasing, T <sub>A</sub> =25°C                             | 5.5  | 5.9     | 6.3     | V        |

| Hysteresis                              |                     | V <sub>H(UVLO)</sub> | (V <sub>CC</sub> Decreasing, T <sub>A</sub> =25°C                            | 0.6  | 0.9     | 1.2     | V        |

| TOTAL DEVICE                            |                     |                      |                                                                              |      |         |         | <u> </u> |

| Power Supply                            | Standby             |                      | V <sub>CC</sub> =12V, V <sub>Comp</sub> <0.15V                               |      | 36      | 100     | μA       |

| Current<br>(T <sub>A</sub> =25°C)       | Operating           | Icc                  | V <sub>CC</sub> =40V, Pin 1=GND for<br>maximum duty cycle                    |      | 40      | 60      | mA       |

Note 4: Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

#### VIN 12V I<sub>LIMI</sub>- $\boldsymbol{C}_{\text{IN}}$ 330µF Oscillator 1 C R 2 PWM PWM Latch D1 1N5825 Π UVLO Thermal L Shutdown ₹190uH 5.50V Reference ♦ 100µA 🕀 ΕA R<sub>2</sub> FΒ V<sub>0</sub> 5.05V/5.0A 1 6.8K ₹120 Ŀ<u>L</u> C<sub>o</sub> \_\_4700uF 5 3 COMP CF GND $R_{F}$ Ŵ ╢╤ 68K 0.1uF ŞR₁

## **TYPICAL APPLICATION CURRENT**

Figure 3. Step-Down Converter

The Step-Down Converter application is shown in Figure 3. The output switch transistor  $Q_1$  interrupts the input voltage, generating a squarewave at the LC<sub>O</sub> filter input. The filter averages the squarewaves, producing a dc output voltage that can be set to any level between  $V_{IN}$  and  $V_{REF}$  by controlling the percent conduction time of  $Q_1$  to that of the total oscillator cycle time. If the converter design requires an output voltage greater than 5.05V, resistor  $R_1$  must be added to form a divider network at the feedback input.

### APPLICATION INFORMATION

The UTC **UMC33167** series are monolithic power switching regulators that are optimized for dc-to-dc converter applications. These devices operate as fixed frequency, voltage mode regulators containing all the active functions required to directly implement step-down and voltage-inverting converters with a minimum number of external components. They can also be used cost effectively in step-up converter applications. Potential markets include automotive, computer, industrial, and cost sensitive consumer products. A description of each section of the device is given below with the representative block diagram shown in Figure 1.

#### Oscillator

The oscillator frequency is internally programmed to 72kHz by capacitor  $C_T$  and a trimmed current source. The charge to discharge ratio is controlled to yield a 95% maximum duty cycle at the Switch Output. During the discharge of  $C_T$ , the oscillator generates an internal blanking pulse that holds the inverting input of the AND gate high, disabling the output switch transistor. The nominal oscillator peak and valley thresholds are 4.1V and 2.3V respectively.

#### Pulse Width Modulator

The Pulse Width Modulator consists of a comparator with the oscillator ramp voltage applied to the noninverting input, while the error amplifier output is applied into the inverting input. Output switch conduction is initiated when  $C_T$  is discharged to the oscillator valley voltage. As  $C_T$  charges to a voltage that exceeds the error amplifier output, the latch resets, terminating output transistor conduction for the duration of the oscillator ramp-up period. This PWM/Latch combination prevents multiple output pulses during a given oscillator clock cycle. Figures 2 illustrate the switch output duty cycle versus the compensation voltage.

#### Error Amplifier and Reference

A high gain Error Amplifier is provided with access to the inverting input and output. This amplifier features a typical dc voltage gain of 80dB, and a unity gain bandwidth of 600kHz with 70 degrees of phase margin. The noninverting input is biased to the internal 5.05V reference and is not pinned out. The reference has an accuracy of  $\pm 2.0\%$  at room temperature. To provide 5.0V at the load, the reference is programmed 50mV above 5.0V to compensate for a 1.0% voltage drop in the cable and connector from the converter output. If the converter design requires an output voltage greater than 5.05V, resistor R1 must be added to form a divider network at the feedback input as shown in Figures 1 and 3. The equation for determining the output voltage with the divider network is:  $V_{OUT}=5.05(R_2/R_1+1)$

External loop compensation is required for converter stability. A simple low-pass filter is formed by connecting a resistor ( $R_2$ ) from the regulated output to the inverting input, and a series resistor-capacitor ( $R_F$ ,  $C_F$ ) between Pins 1 and 5. The compensation network component values shown in each of the applications circuits were selected to provide stability over the tested operating conditions. The step-down converter (Figure 3) is the easiest to compensate for stability. The simplest way to optimize the compensation network is to observe the response of the output voltage to a step load change, while adjusting RF and  $C_F$  for critical damping. The final circuit should be verified for stability under four boundary conditions. These conditions are minimum and maximum input voltages, with minimum and maximum loads.

By clamping the voltage on the error amplifier output (Pin 5) to less than 150mV, the internal circuitry will be placed into a low power standby mode, reducing the power supply current to 36A with a 12V supply voltage.

The Error Amplifier output has a 100 A current source pull-up that can be used to implement soft-start.

#### Switch Output

The output transistor is designed to switch a maximum of 40V, with a minimum peak collector current of 5.5A. When configured for step-down or voltage-inverting applications, as in Figures 3, the inductor will forward bias the output rectifier when the switch turns off. Rectifiers with a high forward voltage drop or long turn on delay time should not be used. If the emitter is allowed to go sufficiently negative, collector current will flow, causing additional device heating and reduced conversion efficiency. shows that by clamping the emitter to 0.5V, the collector current will be in the range of 100A over temperature. A 1N5825 or equivalent Schottky barrier rectifier is recommended to fulfill these requirements.

## APPLICATION INFORMATION (Cont.)

#### Undervoltage Lockout

An Undervoltage Lockout comparator has been incorporated to guarantee that the integrated circuit is fully functional before the output stage is enabled. The internal reference voltage is monitored by the comparator which enables the output stage when  $V_{CC}$  exceeds 5.9V. To prevent erratic output switching as the threshold is crossed, 0.9V of hysteresis is provided.

#### **Thermal Protection**

Internal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 170°C, the latch is forced into a 'reset' state, disabling the output switch. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking. The UTC **UMC33167** is contained in a 5-lead TO-220 type package. The tab of the package is common with the center pin (Pin 3) and is normally connected to ground.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.