# S3C49F9X User's Manual (Compact Flash Controller)

Samsung Electronics Co.,LTD Semiconductor LSI System Division

1

# **PRODUCT OVERVIEW**

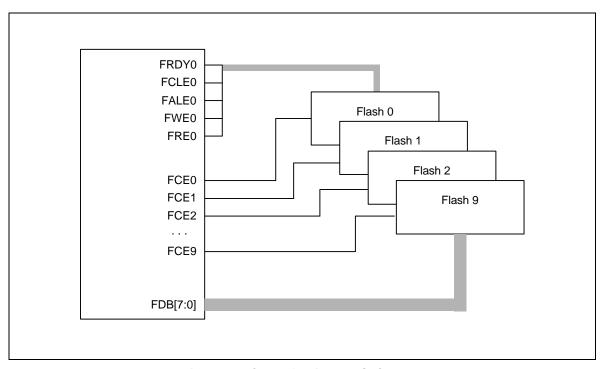

Samsung's S3C49F9X is NAND flash memory controller which can control flash memories as solid state disk. It provides PC Card ATA/IDE interface, host and flash transfer rates up to 20.0MB/S. S3C49F9X can control flash memory maximum 10 pieces if use the 32M,64M,128M,512Mbit and can control flash memory maximum 8 pieces if use the 1Gbit. The device is designed using 0.35-um CMOS process, housed in a 100-TQFP package. It supports operation in both 5.0V and 3.3V.

An outstanding feature of the S3C49F9X flash disk controller is its CPU core: the ARM7TDMI 16/32-bit RISC processor, designed by Advanced RISC Machine (ARM), Ltd. The ARM core is a low-power, general purpose, microprocessor macro-cell that was developed for use in application-specific and customer-specific intergrated circuit. It is simple, elegant, and fully static design is particularly suitable for cost and power sensitive application

### 1.1 Features

- PC Card-ATA/True IDE/CompactFlash compatible host interface

- Automatic sensing of PC Card ATA and 68-pin IDE

- Included 256-byte CIS RAM

- Five PC Card ATA addressing modes

- Host data transfer rate: 20MB/S

Flash data transfer rate: 10MB/S

Host Interface: 8/16-bit Access

Flash Interface: 8-bit Access

- Support 3 power save mode : stop/idle/active

- Support up to 10 flash memories

- Support 32/64/128/256/512Mbit,1Gbit NAND flash memory made by Samsung

| NAND Flash Density              | Min. / Max. Capacity (number of flash) |

|---------------------------------|----------------------------------------|

| 32Mb, 64Mb, 128Mb, 256Mb, 512Mb | 4MB / 512MB (Up to 10ea)               |

| 1Gb                             | 128MB/1GB (Up to 8ea)                  |

- Auto power down function

- ECC function

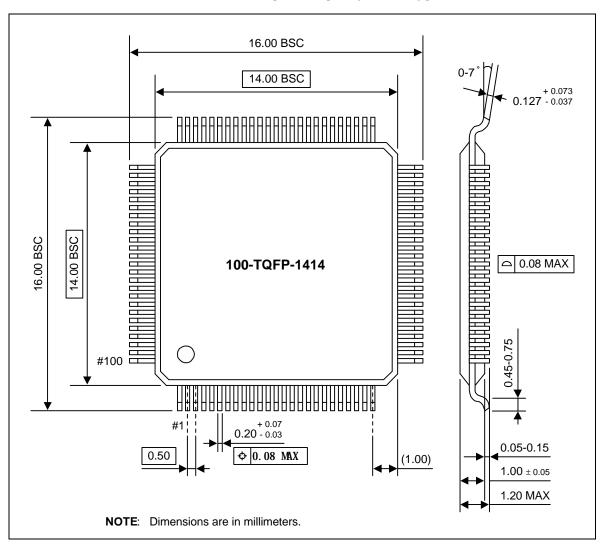

- Available 100-pin TQFP

- Operating Voltage: 3.3V to 5.0V

### **Microprocessor Architecture**

- 16/32-bit RISC architecture

- Efficient and powerful ARM7TDMI CPU core

- Cost-effective JTAG based debug solution

# Interrupts

- 8 interrupt sources

- Normal or fast interrupt modes (IRQ, FIQ)

### **System Manager**

- 512-Kbyte virtually addressable memory space

- Support 8/16-bit external bus for SRAM/ROM

- Programmable external memory access time

- Included 32-Kbytes internal ROM

- Included 8-Kbytes internal SRAM

### **PC-Card/ATA Interface**

- Include 256-Bytes SRAM for CIS

- Support memory and I/O addressing mode

- Support True IDE mode

- 1-bit ECC

# **DMA Controller**

- Two-channel, general-purpose DMA controller

- Memory to memory, PCMCIA to/from memory data transfers without CPU Intervention

- Support for 8/16-bit data transfers

- Increment or decrement of source or destination address

# **Operating Voltage Range**

- 3.3 to 5.0 volts

# **Programmable Timer**

- 1-channel 16-bit programmable timer

# **Operating Frequency**

- Up to 20MHz

### **Package Type**

- 100-TQFP

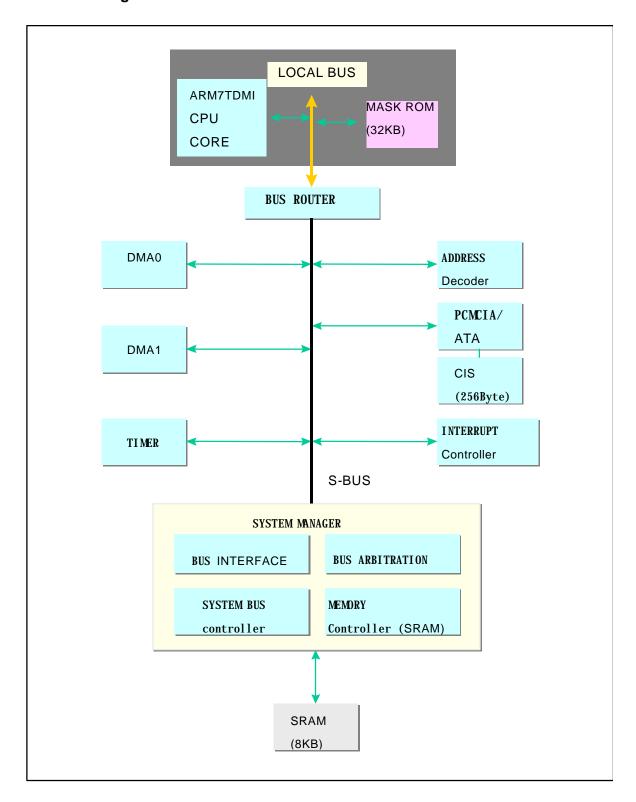

# 1.2 Block Diagram

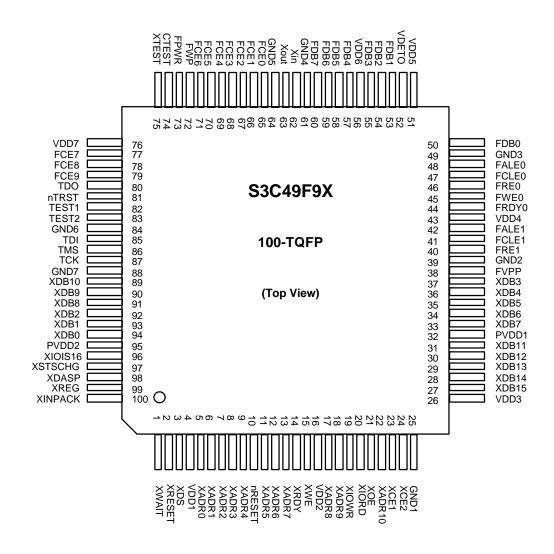

# 2.1 Controller Package Drawing

Figure 2-1 S3C49F9X Pin Assignment

# 2.2 Controller Pin Assignments and Pin type

Table 2-1 Controller Pin Assignments

| Pin    | Signal Name | Pin Type | I/O Type  | Function                                       |

|--------|-------------|----------|-----------|------------------------------------------------|

| Number |             | _        |           |                                                |

| 1      | XWAIT       | 0        | 01        | Wait of PCMCIA                                 |

| 2      | XRESET      | l        | l1        | Write protect of flash chips for flash bus 0,1 |

| 3      | XDS         | l        | 15        | Device select for IDE                          |

| 4      | VDD1        | -        | -         | System power                                   |

| 5      | XADR0       | I        | <u>I1</u> | Address bus of PCMCIA                          |

| 6      | XADR1       | I        | l1        | Address bus of PCMCIA                          |

| 7      | XADR2       | l        | l1        | Address bus of PCMCIA                          |

| 8      | XADR3       | I        | l1        | Address bus of PCMCIA                          |

| 9      | XADR4       | I        | l1        | Address bus of PCMCIA                          |

| 10     | nRESET      | I        | 13        | System power reset                             |

| 11     | XADR5       | I        | l1        | Address bus of PCMCIA                          |

| 12     | XADR6       | I        | l1        | Address bus of PCMCIA                          |

| 13     | XADR7       | I        | l1        | Address bus of PCMCIA                          |

| 14     | XRDY        | 0        | 01        | Ready(IREQ) of PCMCIA                          |

| 15     | XWE         | I        | 12        | Write enable of PCMCIA                         |

| 16     | VDD2        | -        | -         | System power                                   |

| 17     | XADR8       | I        | I1        | Address bus of PCMCIA                          |

| 18     | XADR9       | I        | I1        | Address bus of PCMCIA                          |

| 19     | XIOWR       | I        | 12        | IOWR of PCMCIA                                 |

| 20     | XIORD       | I        | 12        | IORD of PCMCIA                                 |

| 21     | XOE         | I        | 12        | Output enable of PCMCIA                        |

| 22     | XADR10      | I        | I1        | Address bus of PCMCIA                          |

| 23     | XCE1        | l        | 12        | Card enable1 of PCMCIA                         |

| 24     | XCE2        | l        | 12        | Card enable2 of PCMCIA                         |

| 25     | GND1        | -        | -         | Ground                                         |

| 26     | VDD3        | -        | -         | System power                                   |

| 27     | XDB15       | I/O      | B1        | Data bus of PCMCIA                             |

| 28     | XDB14       | I/O      | B1        | Data bus of PCMCIA                             |

| 29     | XDB13       | I/O      | B1        | Data bus of PCMCIA                             |

| 30     | XDB12       | I/O      | B1        | Data bus of PCMCIA                             |

| 31     | XDB11       | I/O      | B1        | Data bus of PCMCIA                             |

| 32     | PVDD1       | -        | -         | PCMCIA power                                   |

| 33     | XDB7        | I/O      | B1        | Data bus of PCMCIA                             |

| 34     | XDB6        | I/O      | B1        | Data bus of PCMCIA                             |

| 35     | XDB5        | I/O      | B1        | Data bus of PCMCIA                             |

| 36     | XDB4        | I/O      | B1        | Data bus of PCMCIA                             |

| 37     | XDB3        | I/O      | B1        | Data bus of PCMCIA                             |

# S3C49F9X SOLID DISK CONTROLLER

| 38 | FVPP | - | - | High voltage power for OTP |

|----|------|---|---|----------------------------|

Table 2-1 Controller Pin Assignments (Cont.)

| Pin<br>Number | Signal Name | Pin Type | I/O Type | Function                                          |

|---------------|-------------|----------|----------|---------------------------------------------------|

| 39            | GND2        | -        | -        | Ground                                            |

| 40            | FRE1        | I/O      | B9       | Read enable flash chips of flash bus1             |

| 41            | FCLE1       | I/O      | B5       | Command latch enable of flash chips of flash bus1 |

| 42            | FALE1       | I/O      | B5       | Address latch enable of flash chips of flash bus1 |

| 43            | VDD4        | -        | -        | System power                                      |

| 44            | FRDY0       | I/O      | B5       | Ready signal of flash chips of flash bus0         |

| 45            | FWE0        | I/O      | В9       | Write enable of flash chips of flash bus0         |

| 46            | FRE0        | I/O      | В9       | Read enable flash chips of flash bus0             |

| 47            | FCLE0       | I/O      | B5       | Command latch enable of flash chips of flash bus1 |

| 48            | FALE0       | I/O      | B5       | Address latch enable of flash chips of flash bus1 |

| 49            | GND3        | -        | -        | Ground                                            |

| 50            | FDB0        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 51            | VDD5        | -        | -        | System power                                      |

| 52            | VDETO       | 0        | O2       | Voltage detect output                             |

| 53            | FDB1        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 54            | FDB2        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 55            | FDB3        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 56            | VDD6        | -        | -        | System power                                      |

| 57            | FDB4        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 58            | FDB5        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 59            | FDB6        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 60            | FDB7        | I/O      | B7       | I/O of flash chips of flash bus0,1                |

| 61            | GND4        | -        | -        | Ground                                            |

| 62            | ΧI          | -        | OSC      | Input clock                                       |

| 63            | хо          | -        | OSC      | Output clock                                      |

| 64            | GND5        | -        | -        | Ground                                            |

| 65            | FCE0        | I/O      | В3       | Chip enable 0 of flash chips of flash bus0,1      |

| 66            | FCE1        | I/O      | В3       | Chip enable 1 of flash chips of flash bus0,1      |

| 67            | FCE2        | I/O      | В3       | Chip enable 2 of flash chips of flash bus0,1      |

| 68            | FCE3        | I/O      | В3       | Chip enable 3 of flash chips of flash bus0,1      |

| 69            | FCE4        | I/O      | В3       | Chip enable 4 of flash chips of flash bus0,1      |

| 70            | FCE5        | I/O      | В3       | Chip enable 5 of flash chips of flash bus0,1      |

| 71            | FCE6        | I/O      | В3       | Chip enable 6 of flash chips of flash bus0,1      |

| 72            | FWP         | I/O      | B5       | Write protect of flash chips of flash bus 0, 1    |

| 73            | FPWR        | 0        | O2       | Power control signal for flash memory             |

| 74            | CTEST       | I        | 14       | Core test mode select signal                      |

| 75 | XTEST | ı | 14 | Test input for test mode  |

|----|-------|---|----|---------------------------|

| 10 | AILOI |   | 17 | 1 Cot input for test mode |

Table 2-1 Controller Pin Assignments (Cont.)

| Pin    | Signal Name | Pin Type | I/O Type | Function                                     |

|--------|-------------|----------|----------|----------------------------------------------|

| Number |             |          |          |                                              |

| 76     | VDD7        | -        | -        | System power                                 |

| 77     | FCE7        | I/O      | В3       | Chip enable 7 of flash chips of flash bus0,1 |

| 78     | FCE8        | I/O      | В3       | Chip enable 8 of flash chips of flash bus0,1 |

| 79     | FCE9        | I/O      | В3       | Chip enable 9 of flash chips of flash bus0,1 |

| 80     | TDO         | 0        | O2       | Test data output for JTAG                    |

| 81     | nTRST       | I        | 14       | Test reset for JTAG                          |

| 82     | TEST1       | I        | 14       | OTP mode select signal 1                     |

| 83     | TEST2       | I        | 14       | OTP mode select signal 2                     |

| 84     | GND6        | -        | -        | Ground                                       |

| 85     | TDI         | I        | 14       | Test data input for JTAG                     |

| 86     | TMS         | I        | 14       | Test mode select for JTAG                    |

| 87     | TCK         | I        | 14       | Test clock for JTAG                          |

| 88     | GND7        | -        | -        | Ground                                       |

| 89     | XDB10       | I/O      | B1       | Data bus of PCMCIA                           |

| 90     | XDB9        | I/O      | B1       | Data bus of PCMCIA                           |

| 91     | XDB8        | I/O      | B1       | Data bus of PCMCIA                           |

| 92     | XDB2        | I/O      | B1       | Data bus of PCMCIA                           |

| 93     | XDB1        | I/O      | B1       | Data bus of PCMCIA                           |

| 94     | XDB0        | I/O      | B1       | Data bus of PCMCIA                           |

| 95     | PVDD2       | -        | -        | PCMCIA power                                 |

| 96     | XIOIS16     | I/O      | B1       | IOIS16 of PCMCIA                             |

| 97     | XSTSCHG     | I/O      | B1       | STSCHG of PCMCIA                             |

| 98     | XDASP       | I/O      | B4       | DASP for IDE                                 |

| 99     | XREG        | I        | 12       | REG of PCMCIA                                |

| 100    | XINPACK     | 0        | 01       | INPACK of PCMCIA                             |

Table 2-2 I/O Type Description

| I/O       | Pad Type | Description                                                                        |

|-----------|----------|------------------------------------------------------------------------------------|

| Туре      | D) (II 0 | O OV TTL and only this country of POMOIA LINE country (for                         |

| <u>I1</u> | PVIL3    | 3.3V TTL schmitt trigger level PCMCIA LIN input buffer                             |

| 12        | PVILU3   | 3.3V TTL schmitt trigger level PCMCIA LIN input buffer with pull-up register       |

| 13        | PIS      | CMOS schmitt trigger level input buffer                                            |

| 14        | PIC      | CMOS level input buffer                                                            |

| 15        | PICU     | CMOS level input buffer with pull-up register                                      |

| 16        | PICD     | CMOS level input buffer with pull-down register                                    |

| 17        | PVILD3   | 3.3V TTL schmitt trigger level PCMCIA LIN input buffer with pull-down register     |

| 01        | PVOB43   | 3.3V 4mA PCMCIA output buffer without SRC                                          |

| O2        | POD4     | 4mA open drain output buffer                                                       |

| O3        | POB4     | 4mA Normal output buffer                                                           |

| 04        | POB4SM   | 4mA Normal output buffer with medium slew-rate control                             |

| O5        | POB16SM  | 16mA Normal output buffer with medium slew-rate control                            |

| 06        | POB12    | 12mA Normal output buffer                                                          |

| B1        | PVBTT43  | 3.3V 4mA PCMCIA LIN bi-directional buffer without SRC                              |

| B2        | PBCT4    | CMOS level input buffer and 4mA tri-state output buffer                            |

| В3        | PBCT4SM  | CMOS level input buffer and 4mA tri-state output buffer with medium slew-rate      |

|           |          | control                                                                            |

| B4        | PBCUT4SM | CMOS level input buffer with pull-up register and 4mA tri-state output buffer with |

|           |          | medium slew-rate control                                                           |

| B5        | PBCT8SM  | CMOS level input buffer and 8mA tri-state output buffer with medium slew-rate      |

|           |          | control                                                                            |

| B6        | PBCUT8SM | CMOS level input buffer with pull-up register and 8mA tri-state output buffer with |

|           |          | medium slew-rate control                                                           |

| B7        | PBCDT8   | CMOS level input buffer with pull-down register and 8mA tri-state output buffer    |

| B8        | PBSDT4SM | CMOS schmitt trigger level input buffer with pull-down register and 4mA tri-state  |

|           |          | output buffer with medium slew-rate control                                        |

| B9        | PBCT16SM | CMOS level input buffer and 16mA tri-state output buffer with medium slew-rate     |

|           |          | control                                                                            |

| B10       | PVBTD43  | 3.3V 4mA PCMCIA LIN bi-directional buffer without SRC with pull-down register      |

| OSC       | PSOSCM26 | Oscillator cell with enable and register                                           |

# 2.3 Pin description for host interface

Table 2-3 Pin description for host interface

| Signal | 100-Pin | I/O | Description                                                                          |

|--------|---------|-----|--------------------------------------------------------------------------------------|

| Name   | Number  | 1/0 | Description                                                                          |

| XARD0  | 5       |     | ADDRESS BUS[10:0]: These address lines along with the –REG signal are used           |

| XARD1  | 6       |     | to select the following: The I/O port address registers within the PC Storage Card,  |

| XARD2  | 7       |     | the memory mapped port address registers within the PC Storage Card, a byte in       |

| XARD3  | 8       |     | the Card's information structure and its configuration control and status registers. |

| XARD4  | 9       |     | <b>3</b>                                                                             |

| XARD5  | 11      | ı   | This signal is the same as the PC Card Memory Mode signal in PC Card I/O             |

| XARD6  | 12      |     | mode.                                                                                |

| XARD7  | 13      |     |                                                                                      |

| XARD8  | 17      |     | In True IDE Mode only A[2:0] are used to select the one of eight registers in the    |

| XARD9  | 18      |     | Task File, the remaining address lines should be grounded by the host.               |

| XARD10 | 22      |     |                                                                                      |

| XDB0   | 94      |     | DATA BUS[15:0]: These lines carry the Data, Commands and Status information          |

| XDB1   | 93      |     | between the host and the controller. XDB0 is the LSB of the even byte of the word.   |

| XDB2   | 92      |     | XDB8 is the LSB of the odd byte of the word.                                         |

| XDB3   | 37      |     |                                                                                      |

| XDB4   | 36      |     | This signal is the same as the PC Card memory mode signal in PC Card I/O             |

| XDB5   | 35      |     | mode.                                                                                |

| XDB6   | 34      |     |                                                                                      |

| XDB7   | 33      | I/O | In True IDE mode, all Task File operations occur in byte mode on the low order       |

| XDB8   | 91      |     | bus XDB0-XDB7 while all data transfers are 16 bit using XDB0-XDB15.                  |

| XDB9   | 90      |     |                                                                                      |

| XDB10  | 89      |     |                                                                                      |

| XDB11  | 31      |     |                                                                                      |

| XDB12  | 30      |     |                                                                                      |

| XDB13  | 29      |     |                                                                                      |

| XDB14  | 28      |     |                                                                                      |

| XDB15  | 27      |     |                                                                                      |

| XREG   | 99      |     | ATTRIBUTE MEMORY AREA SELECTION : This signal is used during memory                  |

|        |         |     | cycles to distinguish between common memory and register (Attribute) memory          |

|        |         |     | accesses. High for Common memory, low for attribute memory.                          |

|        |         |     |                                                                                      |

|        |         |     | The signal must also be active (low) during I/O cycles when the I/O address is on    |

|        |         | ļ   | the Bus.                                                                             |

|        |         |     | In True IDE mode, this input signal is not used and should be connected to VCC.      |

|        |         |     | In True IDE mode, this input signal is not used and should be connected to VCC       |

|        |         |     | by the host.                                                                         |

Table 2-3 Pin description for host interface(Cont.)

| Signal<br>Name | 100-Pin<br>Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XCE1           | 23                | 1   | CARD ENABLE: These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed.  -CE2 always accesses the odd byte of the wordCE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2. A multi-plexing scheme based on A0, -CE1, -CE2 allows 8 bit hosts to access all data on XDB0-XDB7. See tables 3-7,3-8,4-3 and 4-4.  This signal is the same as the PC card memory mode signal in PC Card I/O mode. |

|                |                   |     | In the True IDE mode, CS0 is the chip select for the task file registers while CS1 is used to select the alternate status register and the device control register.                                                                                                                                                                                                                                                                                                                                    |

| XCE2           | 24                | ı   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XOE            | 21                | 1   | OUTPUT ENABLE: This is an output enable strobe generated by the host interface. It is used to read data from the PC Card in memory mode and to read the CIS and configuration registers.  In PC Card I/O mode, this signal is used to read the CIS and configuration registers.  To enable True IDE mode this input should be grounded by the host.                                                                                                                                                    |

| XWE            | 15                | _   | WRITE ENABLE: This is a signal driven by the host and used for strobing memory write data to the registers of the PC Card when the card is configured in the memory interface mode. It is also used for writing the configuration registers.  In PC Card I/O mode, this signal is used for writing the configuration registers.  In True IDE mode, this input signal is not used and should be connected to VCC by the host.                                                                           |

| XWAIT          | 1                 | 0   | WAIT: The -WAIT signal is driven low by the PC Card to signal the host to delay completion of a memory or I/O cycle that is in progress.  IORDY: In True IDE mode, this output signal may be used as IORDY.                                                                                                                                                                                                                                                                                            |

Table 2-3 Pin description for host interface(Cont.)

| Signal<br>Name | 100-Pin<br>Number | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIOIS16        | 96                | I/O | I/O PORT IS 16 BITS: Memory mode - The PC Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.  I/O operation - When the PC Card is configured for I/O operation pin 24 is used for the -I/O selected is 16-Bit Port (-IOIS16) function. A low signal indicates that a 16 bit or odd byte only operation can be performed at the addressed port.  In True IDE mode, this output signal is asserted low when this device is                                                                                                                                                                                                                                                                                                                                            |

| XINPACK        | 100               | 0   | expecting a word data transfer cycle.  INPUT PORT ACKNOWLEDGE: This signal is not used in memory mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |                   |     | The Input acknowledge signal is asserted by the PC Card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enable of any input data buffers between the PC Card and the CPU.  In True IDE mode, this output signal is not used and should be connected at the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XRDY/          | 14                | O   | READY/BUSY: In memory mode, this signal is set high when the PC Card is ready to accept a new data transfer operation and held low when the card is busy. The host memory card socket must provide a pull-up resistor. At power up and at reset, the RDY/-BSY signal is held low (busy) until the PC Card has completed its power up or reset function. No access of any type should be made to the PC Card during this time. The RDY/-BSY signal is held high (disabled from being busy) whenever the following condition is true: The PC Card has been powered up with +RESET continuously disconnected or asserted.  I/O operation - After the PC Card has been configured for I/O operation, this signal is used as Interrupt request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt. |

|                |                   |     | In True IDE mode, this signal is the active high Interrupt request to the host.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2-3 Pin description for host interface(Cont.)

| Signal  | 100-Pin | I/O | Description                                                                                                                                           |

|---------|---------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Number  |     |                                                                                                                                                       |

| XIORD   | 20      | I   | I/O READ : This signal is not used in memory mode.                                                                                                    |

|         |         |     | This is an I/O read strobe generated by the host. This signal gates I/O data onto the bus from the PC Card when the card is configured to use the I/O |

|         |         |     | interface.                                                                                                                                            |

|         |         |     |                                                                                                                                                       |

|         |         |     | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                           |

| XIOWR   | 19      | 1   | I/O WRITE: This signal is not used in memory mode.                                                                                                    |

|         |         |     | The I/O write strobe pulse is used to clock I/O data on the card data bus into                                                                        |

|         |         |     | the PC Card controller registers when the PC Card is configured to use the                                                                            |

|         |         |     | I/O interface. The clocking will occur on the negative to positive edge of the                                                                        |

|         |         |     | signal (trailing edge).                                                                                                                               |

|         |         |     | In True IDE mode, this signal has the same function as in PC Card I/O Mode.                                                                           |

| XSTSCHG | 97      | I/O | STATUS CHANGED : This signal is asserted high as the BVD1 signal since a                                                                              |

|         |         |     | battery is not used with this product.                                                                                                                |

|         |         |     | This signal is asserted low to alert the host to changes in the RDY/-BSY and                                                                          |

|         |         |     | write protect states, while the I/O interface is configured. Its use is controlled                                                                    |

|         |         |     | by the Card config and status                                                                                                                         |

|         |         |     | In the True IDE mode, this input / output is the pass diagnostic signal in the                                                                        |

|         |         |     | Master / Slave handshake protocol.                                                                                                                    |

| XDS     | 3       | I   | CARD SELECT : In True IDE mode, this signal is used for configure this                                                                                |

|         |         |     | device as a master or slave. When it is grounded , the device is configured as                                                                        |

|         |         |     | a master. When this signal is open, the device is configured as a slave.                                                                              |

|         |         |     | In I/O and memory mode, this signal is not used.                                                                                                      |

| XRESET  | 2       | I   | RESET: When the pin is high, this signal resets the PC Card. The PC Card                                                                              |

|         |         |     | is reset only at Power up if this pin is left high or open from power-up. The PC                                                                      |

|         |         |     | Card is also reset when the soft reset bit in the Card Configuration Option                                                                           |

|         |         |     | Register is set.                                                                                                                                      |

|         |         |     | In the True IDE mode, this input pin is the active low hardware reset from the                                                                        |

|         |         |     | host.                                                                                                                                                 |

Table 2-3 Pin description for host interface(Cont.)

| Signal | 100-Pin | I/O | Description                                                                                                             |

|--------|---------|-----|-------------------------------------------------------------------------------------------------------------------------|

| Name   | Number  |     |                                                                                                                         |

| XDASP  | 98      | I/O | This output line is always driven to a high state in memory mode since a battery is not required for this product.      |

|        |         |     | This output line is always driven to a high state in I/O mode since this product does not support the audio function.   |

|        |         |     | In the True IDE mode, this input/output is the disk active/slave present signal in the Master/Slave handshake protocol. |

| XP55   | -       | 1   | Input for inverter                                                                                                      |

| XP56   | -       | 0   | Output for inverter                                                                                                     |

| VDEOT  | 52      | 0   | Voltage detect output                                                                                                   |

| XTEST  | 75      | 1   | Test input for test mode                                                                                                |

# 2.4 Pin Assignment for Flash Memory Interface

Table 2-4 Pin description for Flash memory interface

| Signal | 100-Pin | I/O | Description                                                               |

|--------|---------|-----|---------------------------------------------------------------------------|

| Name   | Number  |     |                                                                           |

| FDB0   | 50      |     | FLASH DATA BUS[15:0]: These lines are 16-bit data lines to/from the       |

| FDB1   | 53      |     | flash memory chip.                                                        |

| FDB2   | 54      |     |                                                                           |

| FDB3   | 55      |     |                                                                           |

| FDB4   | 57      |     |                                                                           |

| FDB5   | 58      |     |                                                                           |

| FDB6   | 59      |     |                                                                           |

| FDB7   | 60      |     |                                                                           |

| FDB8   | -       | I/O |                                                                           |

| FDB9   | -       |     |                                                                           |

| FDB10  | -       |     |                                                                           |

| FDB11  | -       |     |                                                                           |

| FDB12  | -       |     |                                                                           |

| FDB13  | -       |     |                                                                           |

| FDB14  | -       |     |                                                                           |

| FDB15  | -       |     |                                                                           |

| FRDY0  | 44      | I/O | FLASH READY 0/1: The signal is used for indicate to the controller, which |

| FRDY1  | -       | - 1 | flash memory is ready to accept a command. FDB0 ~ FDB7 are controlled     |

|        |         |     | by FRDY0 signal, FDB8 ~ FDB15 are controlled by FRDY1.                    |

| FALE0  | 48      | I/O | FLASH ADDRESS LATCH ENABLE 0/1 : When this signal is asserted the         |

| FALE1  | 42      | I/O | controller can send an address to the flash memory by asserting of FWE    |

|        |         |     | pin. FDB0 ~ FDB7 are controlled by FALE0 signal, FDB8 ~ FDB15 are         |

|        |         |     | controlled by FALE1.                                                      |

| FCLE0  | 47      | I/O | FLASH COMMAND LATCH ENABLE 0/1 : When this signal is asserted, a          |

| FCLE1  | 41      | I/O | command can be to the flash memory. FDB0 ~ FDB7 are controlled by         |

|        |         |     | FCLE0 signal, FDB8 ~ FDB15 are controlled by FCLE1.                       |

| FRE0   | 46      | I/O | FLASH READ ENABLE 0/1 : This signal is asserted to enable the reading     |

| FRE1   | 40      | I/O | of data from the flash memory. FDB0 ~ FDB7 are controlled by FRE0         |

|        |         |     | signal, FDB8 ~ FDB15 are controlled by FRE1.                              |

| FWE0   | 45      | I/O | FALSH WRITE ENABLE 0/1: When this signal is asserted, the controller      |

| FWE1   | -       | 0   | can write data to the flash memory. FDB0 ~ FDB7 are controlled by FWE0    |

|        |         |     | signal, FDB8 ~ FDB15 are controlled by FWE1.                              |

Table 2-4 Pin description for Flash memory interface(Cont.)

| Signal | 100-Pin | I/O | Description                                                          |

|--------|---------|-----|----------------------------------------------------------------------|

| Name   | Number  |     |                                                                      |

| FCE0   | 65      |     | FLASH CHIP ENABLE [9:0]: These lines are flash memory enable signal. |

| FCE1   | 66      |     |                                                                      |

| FCE2   | 67      |     |                                                                      |

| FCE3   | 68      |     |                                                                      |

| FCE4   | 69      | I/O |                                                                      |

| FCE5   | 70      |     |                                                                      |

| FCE6   | 71      |     |                                                                      |

| FCE7   | 77      |     |                                                                      |

| FCE8   | 78      |     |                                                                      |

| FCE9   | 79      |     |                                                                      |

| FWP    | 72      | I/O | Write protect of flash chips of flash bus 0, 1                       |

| FPWR   | 73      | 0   | Power control signal for flash memory                                |

# 2.5 Pin Assignment for external memory control

Table 2-5 Pin description for external memory interface

| Signal | 100-Pin | I/O | Description                                                               |

|--------|---------|-----|---------------------------------------------------------------------------|

| Name   | Number  |     |                                                                           |

| ADDR0  | -       |     | EXTERNAL MEMORY ADDRESS BUS [16:0]: These signals are address             |

| ADDR1  | -       |     | bus to access external memory device as SRAM or ROM.                      |

| ADDR2  | -       |     |                                                                           |

| ADDR3  | -       |     |                                                                           |

| ADDR4  | -       |     |                                                                           |

| ADDR5  | -       |     |                                                                           |

| ADDR6  | -       |     |                                                                           |

| ADDR7  | -       |     |                                                                           |

| ADDR8  | -       | 0   |                                                                           |

| ADDR9  | -       |     |                                                                           |

| ADDR10 | -       |     |                                                                           |

| ADDR11 | -       |     |                                                                           |

| ADDR12 | -       |     |                                                                           |

| ADDR13 | -       |     |                                                                           |

| ADDR14 | -       |     |                                                                           |

| ADDR15 | -       |     |                                                                           |

| ADDR16 | -       |     |                                                                           |

| DATA0  | -       |     | EXTERNAL MEMORY DATA BUS [7:0] : These signals are data bus to            |

| DATA1  | -       |     | access external memory device as SRAM or ROM.                             |

| DATA2  | -       |     |                                                                           |

| DATA3  | -       |     |                                                                           |

| DATA4  | -       | I/O |                                                                           |

| DATA5  | -       |     |                                                                           |

| DATA6  | -       |     |                                                                           |

| DATA7  | -       |     |                                                                           |

| nRCS   | -       | 0   | EXTERNAL ROM CHIP SELECT : When this signal is asserted(low active) ,     |

|        |         |     | the controller can access the external ROM device.                        |

| nSCS   | -       | 0   | EXTERNAL SRAM CHIP SELECT : When this signal is asserted(low active) ,    |

|        |         |     | the controller can access the external SRAM device.                       |

| nOE    | -       | 0   | OUTPUT ENABLE: This signal is data output enable signal. When an          |

|        |         |     | external memory access for ROM/SRAM occurs, this signal controls the      |

|        |         |     | output enable port of the specific device.                                |

| nWE    | -       | 0   | WRITE ENABLE : When an external memory device access for SRAM/ROM         |

|        |         |     | occurs, this signal control the write enable port of the specific device. |

Table 2-5 Pin description for external memory interface(Cont.)

| Signal | 100-Pin      | I/O | Description                                                                                                                                                                                                                                                                                                         |

|--------|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCK    | Number<br>87 | I   | TEST CLOCK: The KS32P49F9X contains internally in-circuit emulation block for debugger mode which use standard JTAG protocol. When the controller go into debugger mode, this signal is provided from external debugger tool.                                                                                       |

| TMS    | 86           | I   | TEST MODE SELECT: In the debugger mode, this signal select test mode. This pin should be held to "1', when do not use the JTAG block.                                                                                                                                                                               |

| TDI    | 85           | I   | TEST DATA INPUT: In the debugger mode, this signal is used for carry data. from external debugger tool to the controller.                                                                                                                                                                                           |

| nTRST  | 81           | I   | TEST RESET: This signal should be sustained LOW first at the begging of normal operation.                                                                                                                                                                                                                           |

| TDO    | 80           | I/O | TEST DATA OUTPUT: In the debugger mode, this signal is used for carry data. from the controller to external debugger tool.                                                                                                                                                                                          |

| XI     | 62           | ОС  | INPUT CLOCK : This signal is system clock.                                                                                                                                                                                                                                                                          |

| ХО     | 63           | ОС  | OUTPUT CLOCK :                                                                                                                                                                                                                                                                                                      |

| nRESET | -            | I   | RESET: This pin is system power on reset. A low input will stop all operation within the controller.                                                                                                                                                                                                                |

| SW1    | -            | I   | ROM SELECTION: This pin is used for select ROM. When this signal set "1", the controller access external ROM. When this pin is "0", the controller access internal ROM.                                                                                                                                             |

| SW0    | -            | I   | FLASH NUMBER OF SELECTION: Basically flash memory can be connected up to 20. But if use the external buffer on pc card, flash memory can be connected up to 32. This signal is used for select number of flash. When this signal is high, can be connected up to 20. In the case of low, can be connected up to 32. |

| CTEST  | 74           | I   | CORE TEST: This signal is used for test CPU(ARM7TDMI) core. When this signal is low(0), the controller operate normal mode. When it is high(1), operate CPU test mode.                                                                                                                                              |

| CMODE  | -            | I   | INTERRUPT ENABLE: This signal is used for control interrupt signal of CPU, when the signal is set(1), interrupt signal of CPU can be enabled. When this signal is cleared(0), interrupt signal can be disabled.                                                                                                     |

| TEST1  | 82           | I   | OTP MODE SELECT : These signals are used for select OTP mode. When                                                                                                                                                                                                                                                  |

| TEST2  | 83           | I   | OTPMS1 and OTPMS2 are low, the controller operate normal mode. To operate the OTP mode, OTPMS1 and OTPMS2 signal should be set to low and high. The others setting mode are reserved for chip maker.                                                                                                                |

# 2.6 Power Pin Assignment

Table 2-6 Pin description for power signal

| Signal | 100-Pin Number       | I/O | Description                                |

|--------|----------------------|-----|--------------------------------------------|

| Name   |                      |     |                                            |

| VDD    | 4,16,26,43,51,56,76  | -   | System power supply voltage                |

| PVDD   | 32,95                | -   | PCMCIA power supply voltage                |

| FVPP   | 38                   | -   | High voltage power for internal OTP(12.5V) |

| GND    | 25,39,49,61,64,84,88 | _   | Ground                                     |

3

# INTERFACE BUS TIMMING

There are two types of bus cycles and timing sequences that occur in the PCMCIA type interface, a direct mapped I/O transfer and a memory access. The two timing sequences are explained in detail in the PCMCIA PC Card Standard. The PC Card conforms to the timing in that reference document.

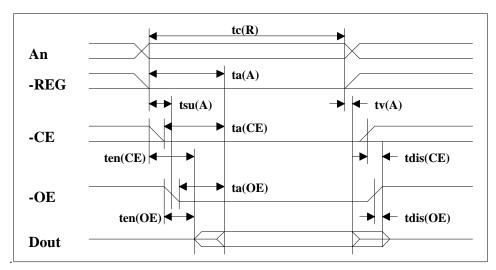

# 3.1 Attribute Memory Read Timing Specification

The attribute memory read time is defined as 300ns. Detailed timing specifications are shown in Table 3-1.

Table 3-1 Attribute Memory Read Timing

| Parameter                      | Symbol   | IEEE Symbol | 300 ns  |         |  |

|--------------------------------|----------|-------------|---------|---------|--|

|                                |          |             | Min ns. | Max ns. |  |

| Read Cycle Time                | tcR      | TAVAV       | 300     |         |  |

| Address Access Time            | ta(A)    | TAVQV       |         | 300     |  |

| Card Enable Access Time        | ta(CE)   | TELQV       |         | 300     |  |

| Output Enable Access Time      | ta(OE)   | TGLQV       |         | 150     |  |

| Output Disable Time from CE    | tdis(CE) | TEHQZ       |         | 100     |  |

| Output Disable Time from OE    | tdis(OE) | TGHQZ       |         | 100     |  |

| Address Setup Time             | tsu(A)   | TAVWL       | 30      |         |  |

| Output Enable Time from CE     | ten(CE)  | TELQNZ      | 5       |         |  |

| Output Enable Time from OE     | ten(OE)  | TGLQNZ      | 5       |         |  |

| Data Valid from Address Change | tv(A)    | TAXQX       | 0       |         |  |

Note. All times are in nanosecond. Dout signifies data provided by the PC Card to the system. The –CE signal or both the –OE signal & the -WE signal must be de-asserted between consecutive cycle operation.

Figure 3-1 Attribute Memory Read Timing Diagram

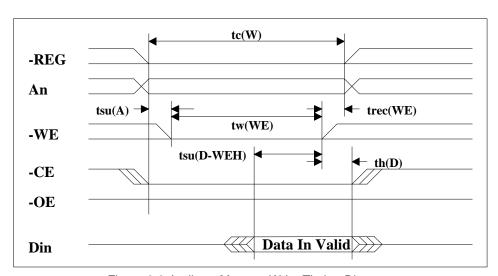

# 3.2 Attribute Memory Write Timing Specification

The attribute memory access time is defined as 250 ns. Detailed timing specifications are shown in table 3-2.

Note. A host cannot write to CIS. This timing is specified only for the write to Configuration Register.

Table 3-2 Attribute Memory Write Timing

| Parameter              | Symbol     | IEEE Symbol | 250 ns  |         |

|------------------------|------------|-------------|---------|---------|

|                        |            |             | Min ns. | Max ns. |

| Write Cycle Time       | tcW        | tAVAV       | 250     |         |

| Write Pulse Width      | tw(WE)     | tWLWH       | 150     |         |

| Address Setup Time     | tsu(A)     | tAVWL       | 30      |         |

| Write Recovery Time    | trec(WE)   | tWMAX       | 30      |         |

| Data Setup Time for WE | tsu(D-WEH) | tDVWH       | 80      |         |

| Data Hold Time         | th(D)      | tWMDX       | 30      |         |

Note. All times are in nanosecond. Din signifies data provided by the system to the PC Card.

Figure 3-2 Attribute Memory Write Timing Diagram

# 3.3 Common Memory Read Timing Specification

Table 3-3 Common Memory Read Timing

| Parameter                   | Symbol    | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------|-----------|-------------|---------|---------|

|                             |           |             |         |         |

| Output Enable Access Time   | ta(OE)    | tGLQV       |         | 125     |

| Output Disable Time from OE | tdis(OE)  | tGHQZ       |         | 100     |

| Address Setup Time          | tsu(A)    | tAVGL       | 30      |         |

| Address Hold Time           | th(A)     | tGHAX       | 20      |         |

| CE Setup before OE          | tsu(CE)   | tELGL       | 0       |         |

| CE Hold following OE        | th(CE)    | tGHEH       | 20      |         |

| Wait Delay Falling from OE  | tv(WT-OE) | tGLWTV      |         | 35      |

| Data Setup for Wait Release | tv(WT)    | tQVWTH      |         | 0       |

| Wait Width Time             | tw(WT)    | tWTLWTH     |         | 350     |

Note. The maximum load on -WAIT is 1 LSTTL with 50pF total load. All times are in nanoseconds. Dout signifies data provided by the PC Card to the system. The -WAIT signal may be ignored if the -OE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined from the Card Information Structure. The Wait Width time meets the PCMCIA specification of 12s but is intentionally less in this specification.

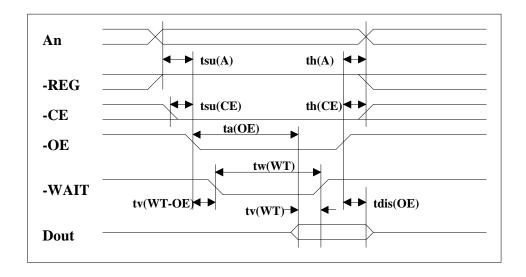

Figure 3-3 Common Memory Read Timing Diagram

# 3.4 Common Memory Write Timing Specification

Table 3-4 Common Memory Write Timing

| Parameter                  | Symbol     | IEEE Symbol | Min ns. | Max ns. |

|----------------------------|------------|-------------|---------|---------|

| Data Setup before WE       | tsu(D-WEH) | tDVWH       | 80      |         |

| Data Hold following WE     | th(D)      | tIWMDX      | 30      |         |

| WE Pulse Width             | tw(WE)     | tWLWH       | 150     |         |

| Address Setup Time         | tsu(A)     | tAVWL       | 30      |         |

| CE Setup before WE         | tsu(CE)    | tELWL       | 0       |         |

| Write recovery Time        | trec(WE)   | tWMAX       | 30      |         |

| Address Hold Time          | th(A)      | tGHAX       | 20      |         |

| CE Hold following WE       | th(CE)     | tGHEH       | 20      |         |

| Wait Delay Falling from WE | tv(WT-WE)  | tWLWTV      |         | 35      |

| WE High from Wait Release  | tv(WT)     | tWTHWH      | 0       |         |

| Wait Width Time            | tw(WT)     | tWTLWTH     |         | 350     |

Note. The maximum load on -WAIT is 1 LSTTL with 50pF total load. All times are in nanoseconds. Din signifies data provided by the system to the PC Card. The -WAIT signal may be ignored if the -WE cycle to cycle time is greater than the Wait Width time. The Max Wait Width time can be determined from the Card Information Structure. The Wait Width time meets the PCMCIA specification of 12s but is intentionally less in this specification.

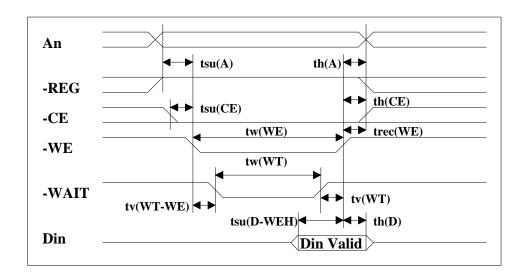

Figure 3-4 Common Memory Write Timing Diagram

# 3.5 I/O Input (Read) Timing Specification

Table 3-5 I/O Read Timing

| Parameter                         | Symbol          | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|-----------------|-------------|---------|---------|

| Data Delay after IORD             | td(IORD)        | tlGLQV      |         | 100     |

| Data Hold following IORD          | th(IORD)        | tIGHQX      | 0       |         |

| IORD Width Time                   | tw(IORD)        | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA(IORD)      | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA(IORD)       | tIGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE(IORD)     | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE(IORD)      | tIGHEH      | 20      |         |

| REG Setup before IORD             | tsuREG(IORD)    | tRGLIGL     | 5       |         |

| REG Hold following IORD           | thREG(IORD)     | tIGHRGH     | 0       |         |

| INPACK Delay Falling from IORD    | tdfINPACK(IORD) | tIGLIAL     | 0       | 45      |

| INPACK Delay Rising from IORD     | tdrINPACK(IORD) | tIGHIAH     |         | 45      |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR)  | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR)  | tAVISH      |         | 35      |

| Wait Delay Falling from IORD      | tdWT(IORD)      | tIGLWTL     |         | 35      |

| Data Delay from Wait Rising       | td(WT)          | tWTHQV      |         | 0       |

| Wait Width Time                   | tw(WT)          | tWTLWTH     |         | 350     |

Note. The maximum load on -WAIT, -INPACK and -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from -WAIT high to -IORD high is 0nsec, but minimum -IORD width must still be met. Dout signifies data provided by the PC Card to the system. The Wait Width time meets the PCMCIA specification of 12s but is intentionally less in this specification.

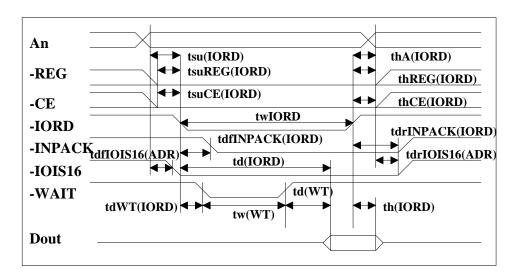

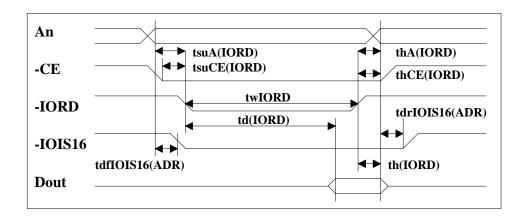

Figure 3-5 I/O Read Timing Diagram

# 3.6 I/O Output (Write) Timing Specification

Table 3-6 I/O Write Timing

| Parameter                         | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60      |         |

| Data Hold following IOWR          | th(IOWR)       | tIWHDX      | 30      |         |

| IOWR Width Time                   | twIOWR         | tIWLIWH     | 165     |         |

| Address Setup before IOWR         | tsuA(IOWR)     | tAVIWL      | 70      |         |

| Address Hold following IOWR       | thA(IOWR)      | tIWHAX      | 20      |         |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5       |         |

| CE Hold following IOWR            | thCE(IOWR)     | tIWHEH      | 20      |         |

| REG Setup before IOWR             | tsuREG(IOWR)   | tRGLIWL     | 5       |         |

| REG Hold following IOWR           | thREG(IOWR)    | tIWHRGH     | 0       |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOIS16(ADR) | tAVISH      |         | 35      |

| Wait Delay Falling from IOWR      | tdWT(IOWR)     | tIWLWTL     |         | 35      |

| IOWR high from Wait high          | tdrIOWR(WT)    | tWTJIWH     | 0       |         |

| Wait Width Time                   | tw(WT)         | tWTLWTH     |         | 350     |

Note. The maximum load on -WAIT, -INPACK, and -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from -WAIT high to -IOWR high is 0nsec, but minimum -IOWR width must still be met. Din signifies data provided by the system to the PC Card. The Wait Width time meets the PCMCIA specification of 12s but is intentionally less in this specification.

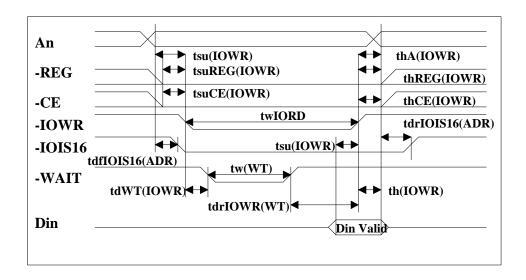

Figure 3-6 I/O Write Timing Diagram

# 3.7 IDE Mode I/O Input(Read) Timing Specification

Table 3-7 IDE Mode I/O Read Timing

| Parameter                         | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

|                                   |                |             |         |         |

| Data Delay after IORD             | td(IORD)       | tlGLQV      |         | 100     |

| Data Hold following IORD          | th(IORD)       | tIGHQX      | 0       |         |

| IORD Width Time                   | tw(IORD)       | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA(IORD)     | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA(IORD)      | tIGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE(IORD)    | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE(IORD)     | tIGHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdflOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR) | tAVISH      |         | 35      |

Note. The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from -WAIT high to -IORD high is 0nsec, but minimum -IORD width must still be met. Dout signifies data provided by the PC Card to the system.

Figure 3-7 IDE Mode I/O Read Timing Diagram

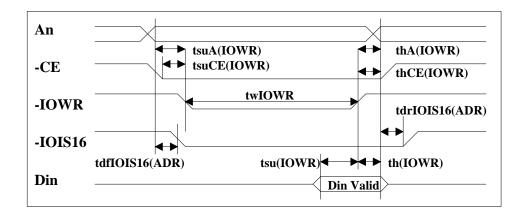

# 3.8 IDE Mode I/O Output(Write) Timing Specification

Table 3-8 IDE Mode I/O Write Timing

| Parameter                         | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

|                                   |                |             |         |         |

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60      |         |

| Data Hold following IOWR          | th(IOWR)       | tIWHDX      | 30      |         |

| IOWR Width Time                   | twIOWR         | tIWLIWH     | 165     |         |

| Address Setup before IOWR         | tsuA(IOWR)     | tAVIWL      | 70      |         |

| Address Hold following IOWR       | thA(IOWR)      | tIWHAX      | 20      |         |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5       |         |

| CE Hold following IOWR            | thCE(IOWR)     | tIWHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOIS16(ADR) | tAVISH      |         | 35      |

Note. The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds. Minimum time from -WAIT high to -IOWR high is 0nsec, but minimum -IOWR width must still be met. Din signifies data provided by the system to the PC Card.

Figure 3-8 I/O Write Timing Diagram

# **CARD CONFIGURATION**

The PC Cards are identified by appropriate information in the Card Information Structure (CIS). The following configuration registers are used to coordinate the I/O spaces and the Interrupt level of cards that are located in the system. In addition, these registers provide a method for accessing status information about the PC Card that may be used to arbitrate between multiple interrupt sources on the same interrupt level or to replace status information that appears on dedicated pins in memory cards that have alternate use in I/O cards.

Table 4-1 Registers and Memory Space Decoding

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | А3 | A2 | A1 | A0 | SELECTED SPACE                       |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|--------------------------------------|

| 1    | 1    | ×    | ×   | ×   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Standby                              |

| ×    | 0    | 0    | 0   | 1   | ×   | 1  | ××    | ×  | ×  | ×  | 0  | Configuration Registers Read         |

| 1    | 0    | 1    | 0   | 1   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Common Memory Read(8bit D7-D0)       |

| 0    | 1    | 1    | 0   | 1   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Common Memory Read(8bit D15-D8)      |

| 0    | 0    | 1    | 0   | 1   | ×   | ×  | ××    | ×  | ×  | ×  | 0  | Common Memory Read(16bit D15-D0)     |

| ×    | 0    | 0    | 1   | 0   | ×   | 1  | ××    | ×  | ×  | ×  | 0  | Configuration Registers Write        |

| 1    | 0    | 1    | 1   | 0   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Common Memory Write(8bit D7-D0)      |

| 0    | 1    | 1    | 1   | 0   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Common Memory Write(8bit D15-D8)     |

| 0    | 0    | 1    | 1   | 0   | ×   | ×  | ××    | ×  | ×  | ×  | 0  | Common Memory Write(16bit D15-D0)    |

| ×    | 0    | 0    | 0   | 1   | 0   | 0  | ××    | ×  | ×  | ×  | 0  | Card Information Structure Read      |

| 1    | 0    | 0    | 1   | 0   | 0   | 0  | ××    | ×  | ×  | ×  | 0  | Invalid Access (CIS Write)           |

| 1    | 0    | 0    | 0   | 1   | ×   | ×  | ××    | ×  | ×  | ×  | 1  | Invalid Access (Odd Attribute Read)  |

| 1    | 0    | 0    | 1   | 0   | ×   | ×  | ××    | ×  | ×  | ×  | 1  | Invalid Access (Odd Attribute Write) |

| 0    | 1    | 0    | 0   | 1   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Invalid Access (Odd Attribute Read)  |

| 0    | 1    | 0    | 1   | 0   | ×   | ×  | ××    | ×  | ×  | ×  | ×  | Invalid Access (Odd Attribute Write) |

Table 4-2 Configuration Registers Decoding

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | А3 | A2 | A1 | A0 | SELECTED SPACE                 |  |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|--------------------------------|--|

| ×    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Read  |  |

| ×    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Write |  |

| ×    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status Register Read      |  |

| ×    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status Register Write     |  |

| ×    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement Register Read  |  |

| ×    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement Register Write |  |

| ×    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy Register Read  |  |

| ×    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy Register Write |  |

Note. The location of the card configuration registers should always be read from the CIS since these locations may vary in future products. No writes should be performed to the PC Card attribute memory except to the card configuration register addresses. All other attribute memory locations are reserved.

# 4.1 Attribute Memory Function

Attribute memory is a space where PC Card identification and configuration information are stored, and is limited to 8-bit wide accesses only at even addresses. The card configuration registers are also located here. For the attribute memory read function, signals -REG and -OE must be active and -WE inactive during the cycle. As in the main memory read functions, the signals -CE1 and -CE2 control the even-byte and odd-byte address, but only the even-byte data is valid during the attribute memory access. Refer to table 4-3 below for signal states and bus validity for the attribute memory function.

Table 4-3 Attribute Memory Function

| Function Mode                             | -REG | -CE2 | -CE1 | A9 | A0 | -OE | -WE | D15-D8     | D7-D0     |

|-------------------------------------------|------|------|------|----|----|-----|-----|------------|-----------|

| Standby Mode                              | ×    | Н    | Н    | ×  | ×  | ×   | ×   | High Z     | High Z    |

| Read Byte Access<br>CIS (8 bits)          | L    | Н    | L    | L  | L  | L   | Н   | High Z     | Even Byte |

| Write Byte Access CIS (8 bits) (invalid)  | L    | Н    | L    | L  | L  | Н   | L   | Don't Care | Even Byte |

| Read Byte Access Configuration (8 bits)   | L    | Н    | Г    | Н  | L  | L   | Ξ   | High Z     | Even Byte |

| Write Byte Access Configuration (8 bits)  | L    | Н    | L    | Н  | L  | Н   | L   | Don't Care | Even Byte |

| Read Word Access<br>CIS (16 bits)         | L    | L    | L    | L  | ×  | L   | Н   | Not Valid  | Even Byte |

| Write Word Access CIS (16 bits) (invalid) | L    | L    | L    | L  | ×  | Н   | L   | Don't Care | Even Byte |

| Read Word Access Configuration (16 bits)  | L    | L    | L    | Н  | ×  | L   | Ħ   | Not Valid  | Even Byte |

| Write Word Access Configuration (16 bits) | L    | L    | L    | Н  | ×  | Н   | L   | Don't Care | Even Byte |

Note The -CE signal or both the -OE signal and the -WE signal must be de-asserted between consecutive cycle operations.

# 4.2 Configuration Option Register (Address 200h in attribute memory)

The Configuration Option Register is used to configure the cards interface, address decoding and interrupt and to issue a soft reset to the PC Card.

| Operation | D7     | D6      | D5    | D4    | D3    | D2    | D1    | D0    |

|-----------|--------|---------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET | LevIREQ | Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 |

SRESET Soft Reset - Setting this bit to one (1), waiting the minimum reset width time and returning to zero (0) places the PC Card in the reset state. Setting this bit to one (1) is equivalent to assertion of the +RESET signal except that the SRESET bit is not cleared. Returning this bit to zero (0) leaves the PC Card in the same un-configured, Reset state as following power-up and hardware reset. This bit is set to zero (0) by power-up and hardware reset. Using the PCMCIA Soft Reset is considered a hardware reset by the ATA commands. Contrast with software reset in the Device Control Register.

**LevIREQ** This bit is set to one (1) when Level Mode Interrupt is selected, and zero (0) when pulse mode is selected. Set to zero (0) by reset.

**Conf5 - Conf0** Configuration Index. Set to zero (0) by reset. It's used to select operation mode of the PC Card as shown below.

Note: Conf5 and Conf4 are reserved and must be written as zero (0)

**Table 4-4 Card Configurations**

| Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 | Disk Card Mode                                 |

|-------|-------|-------|-------|-------|-------|------------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | Memory Mapped                                  |

| 0     | 0     | 0     | 0     | 0     | 1     | I/O Mapped, Any 16byte system decoded boundary |

| 0     | 0     | 0     | 0     | 1     | 0     | I/O Mapped, 1F0-1F7/3F6-3F7                    |

| 0     | 0     | 0     | 0     | 1     | 1     | I/O Mapped, 170-177/376-377                    |

# 4.3 Card Configuration and Status Register (Address 202h in attribute memory)