# **NEC** Microcomputers, Inc.

# CLOCK GENERATOR AND DRIVER FOR 8080A PROCESSORS

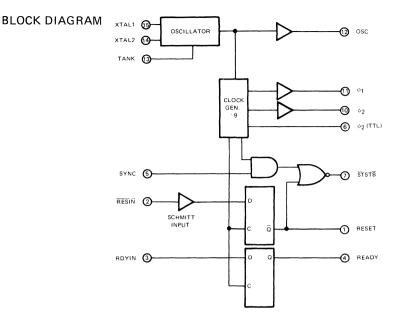

DESCRIPTION The µPB8224 is a single chip clock generator and driver for 8080A processors. The clock frequency is determined by a user specified crystal and is capable of meeting the timing requirements of the entire 8080A family of processors. MOS and TTL level clock outputs are generated.

Additional logic circuitry of the  $\mu$ PB8224 provides signals for power-up reset, an advance status strobe and properly synchronizes the ready signal to the processor. This greatly reduces the number of chips needed for 8080A systems.

The  $\mu$ PB8224 is fabricated using NEC's Schottky bipolar process.

#### FEATURES • Crystal Controlled Clocks

- Oscillator Output for External Timing

- MOS Level Clocks for 8080A Processor

- TTL Level Clock for DMA Activities

- Power-up Reset for 8080A Processor

- Ready Synchronization

- Advanced Status Strobe

- Reduces System Package Count

- Available in 16-pin Cerdip and Plastic Packages

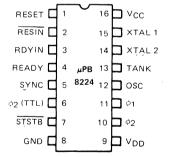

#### PIN CONFIGURATION

|           | -                    |  |  |

|-----------|----------------------|--|--|

| RESIN     | Reset Input          |  |  |

| RESET     | Reset Output         |  |  |

| RDYIN     | Ready Input          |  |  |

| READY     | Ready Output         |  |  |

| SYNC      | Sync Input           |  |  |

| STSTB     | Status STB<br>Output |  |  |

| Ø1        | Processor            |  |  |

| ¢2        | ∫ Clocks             |  |  |

| XTAL 1    | Crystal              |  |  |

| XTAL 2    | ∮ Connections        |  |  |

|           | Used With            |  |  |

| TANK      | Overtone             |  |  |

|           | Crystal              |  |  |

|           | Oscillator           |  |  |

| OSC       | Output               |  |  |

|           | φ <sub>2</sub> CLK   |  |  |

| \$2 (TTL) | (TTL Level)          |  |  |

| Vcc       | +5V                  |  |  |

| VDD       | +12V                 |  |  |

| GND       | 0V                   |  |  |

|           |                      |  |  |

**PIN NAMES**

9

#### Clock Generator

The clock generator circuitry consists of a crystal controlled oscillator and a divide-by-nine counter. The crystal frequency is a function of the 8080A processor speed and is basically nine times the processor frequency, i.e.:

Crystal frequency =  $\frac{9}{tCY}$

where  $t_{CY}$  is the 8080A processor clock period.

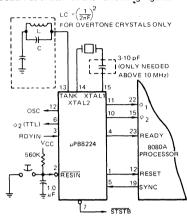

A series resonant fundamental mode crystal is normally used and is connected across input pins XTAL1 and XTAL2. If an overtone mode crystal is used, an additional LC network, AC coupled to ground, must be connected to the TANK input of the  $\mu$ PB8224 as shown in the following figure.

The formula for the LC network is:

LC =

$$\left(\frac{1}{2\pi F}\right)^2$$

where F is the desired frequency of oscillation.

The output of the oscillator is input to the divide-by-nine counter. It is also buffered and brought out on the OSC pin, allowing this stable, crystal controlled source to be used for derivation of other system timing signals. The divide-by-nine counter generates the two non-overlapping processor clocks,  $\phi_1$  and  $\phi_2$ , which are buffered and at MOS levels, a TTL level  $\phi_2$  and internal timing signals.

The  $\phi_1$  and  $\phi_2$  high level outputs are generated in a 2-5-2 digital pattern, with  $\phi_1$  being high for two oscillator periods,  $\phi_2$  being high for five oscillator periods, and then neither being high for two oscillator periods. The TTL level  $\phi_2, \phi_2$  (TTL), is normally used for DMA activities by gating the external device onto the 8080A bus once a Hold Acknowledge (HLDA) has been issued.

#### Additional Logic

In addition to the clock generator circuitry, the  $\mu$ PB8224 contains additional logic to aid the system designer in the proper timing of several interface signals.

The STSTB signal indicates, at the earliest possible moment, when the status signals output from the 8080A processor are stable on the data bus. STSTB is designed to connect directly to the  $\mu$ PB8228 System Controller and automatically resets the  $\mu$ PB8228 during power-on Reset.

The RESIN input to the µPB8224 is used to automatically generate a RESET signal to the 8080A during power initialization. The slow rise of the power supply voltage in an external RC network is sensed by an internal Schmitt Trigger. The output of the Schmitt Trigger is gated to generate an 8080A compatible RESET. An active low manual switch may also be attached to the RC circuit for manual system reset.

The RDYIN input to the  $\mu$ PB8224 accepts an asynchronous "wait request" and generates a READY output to the 8080A that is fully synchronized to meet the 8080A timing requirements. 566

#### ABSOLUTE MAXIMUM RATINGS\*

| Operating Temperature          |

|--------------------------------|

| Storage Temperature            |

| All Output Voltages (TTL)      |

| All Output Voltages (MOS)      |

| All Input Voltages             |

| Supply Voltage V <sub>CC</sub> |

| Supply Voltage VDD             |

| Output Currents                |

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*T<sub>a</sub> ≈ 25°C

#### DC CHARACTERISTICS

$T_a = 0^{\circ}C$  to +70°C;  $V_{CC} = +5V \pm 5\%$ ,  $V_{DD} = +12V \pm 5\%$

| PARAMETER                      | SYMBOL LIMITS     |      | UNIT | TEST CONDITIONS |    |                                                         |  |

|--------------------------------|-------------------|------|------|-----------------|----|---------------------------------------------------------|--|

|                                |                   | MIN  | TYP  | MAX             |    |                                                         |  |

| Input Current Loading          | ١F                |      |      | -0.25           | mA | VF = 0.45V                                              |  |

| Input Leakage Current          | İR                |      |      | 10              | μA | V <sub>R</sub> = 5 25V                                  |  |

| Input Forward Clamp Voltage    | vc                |      |      | -1.0            | V  | I <sub>C</sub> = -5 mA                                  |  |

| Input "Low" Voltage            | VIL               |      |      | 0.8             | v  | V <sub>CC</sub> = 5.0V                                  |  |

| Input "High" Voltage           | VIH               | 2.6  |      |                 | V  | Reset Input                                             |  |

|                                |                   | 2.0  |      |                 |    | All Other Inputs                                        |  |

| RESIN Input Hysteresis         | VIH-VIL           | 0.25 |      |                 | v  | V <sub>CC</sub> = 5.0V                                  |  |

| Output "Low" Voltage           | VOL               |      |      | 0.45            | v  | (φ <sub>1</sub> , φ <sub>2</sub> ), Ready, Reset, STSTB |  |

|                                |                   |      |      |                 |    | IOL = 25 mA                                             |  |

|                                |                   |      |      | 0.45            | v  | All Other Inputs                                        |  |

|                                |                   |      |      |                 |    | IOL = 15 mA                                             |  |

| Output "High" Voltage          | V <sub>OH</sub>   |      |      |                 |    |                                                         |  |

| ¢1, ¢2                         |                   | 9.4  |      |                 | v  | 1 <sub>OH</sub> = -100 µA                               |  |

| READY, RESET                   |                   | 3.6  |      |                 | v  | I <sub>OH</sub> = -100 μA                               |  |

| All Other Outputs              |                   | 2.4  |      |                 | v  | IOH = -1 mA                                             |  |

| Output Short Circuit Current   | ∣ <sub>SC</sub> Φ | -10  |      | -60             | mA | V <sub>O</sub> = 0V                                     |  |

| (All Low Voltage Outputs Only) |                   |      |      |                 |    | V <sub>CC</sub> = 5.0V                                  |  |

| Power Supply Current           | 'cc               |      |      | 115             | mA |                                                         |  |

| Power Supply Current           | <sup>1</sup> DD   |      |      | 15              | mA |                                                         |  |

Note: 1) Caution,  $\phi_1$  and  $\phi_2$  output drivers do not have short circuit protection

CIN

Input Capacitance

CAPACITANCE ()

| $T_a = 25^{\circ}$ C; f = 1 MHz; V <sub>CC</sub> = 5V; V <sub>DD</sub> = 12V; V <sub>BIAS</sub> = 2.5V |        |        |     |     |      |                 |

|--------------------------------------------------------------------------------------------------------|--------|--------|-----|-----|------|-----------------|

| PARAMETER                                                                                              | SYMBOL | LIMITS |     |     | UNIT | TEST CONDITIONS |

|                                                                                                        |        | MIN    | TYP | MAX |      |                 |

8

рF

$T_a = 0^{\circ}C$  to +70°C;  $V_{CC} = +5V \pm 5\%$ ;  $V_{DD} = +12V \pm 5\%$

#### AC CHARACTERISTICS

| PARAMETER                           | SYMBOL           | LIMITS ①                            |          |                            | UNIT | TEST CONDITIONS                            |

|-------------------------------------|------------------|-------------------------------------|----------|----------------------------|------|--------------------------------------------|

|                                     |                  | MIN                                 | TYP      | MAX                        |      |                                            |

| $\phi_1$ Pulse Width                | <sup>t</sup> ø1  | $\frac{2t_{CY}}{9}$ -20 ns          |          |                            |      |                                            |

| $\phi_2$ Pulse Width                | <sup>t</sup> ø2  | 5tCY<br>9 −35 ns                    |          |                            |      |                                            |

| $\phi_1$ to $\phi_2$ Delay          | tD1              | 0                                   |          |                            | ns   |                                            |

| $\phi_2$ to $\phi_1$ Delay          | tD2              | $\frac{2t_{CY}}{9}$ -14 ns          |          |                            |      | C <sub>L</sub> = 20 pF to 50 pF            |

| $\phi_1$ to $\phi_2$ Delay          | tD3              | $\frac{2t_{CY}}{9}$                 |          | $\frac{2t_{CY}}{9}$ +20 ns |      |                                            |

| $\phi_1$ and $\phi_2$ Rise Time     | tR               |                                     |          | 20                         |      |                                            |

| $\phi_1$ and $\phi_2$ Fall Time     | tF               |                                     |          | 20                         |      |                                            |

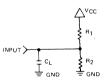

| $\phi_2$ to $\phi_2$ (TTL) Delay    | <sup>t</sup> Dø2 | -5                                  |          | +15                        | ns   | $\phi_2$ TTL, CL = 30 pF                   |

|                                     |                  |                                     |          |                            |      | R <sub>1</sub> = 300Ω                      |

|                                     |                  |                                     |          |                            |      | R <sub>2</sub> = 600Ω                      |

| d2 to STSTB Delay                   | 1D3S             | 6t <u>C</u> Y<br>9 −30 ns           |          | 6tCY<br>9                  | ns   |                                            |

| STSTB Pulse Width                   | tPW              | t <u>CY</u> −15 ns                  |          |                            |      | STSTB, CL = 15 pF                          |

| RDYIN Setup Time<br>to STSTB        | <sup>t</sup> DRS | $50 \text{ ns} - \frac{4t_{CY}}{9}$ |          |                            | ns   | R <sub>1</sub> = 2K<br>R <sub>2</sub> = 4K |

| RDYIN Hold Time<br>After STSB       | <sup>t</sup> DRH | $\frac{4t_{CY}}{9}$                 |          |                            |      |                                            |

| READY or RESET<br>to $\phi_2$ Delay | <sup>t</sup> DR  | $\frac{4t_{CY}}{9} - 25 \text{ ns}$ |          |                            | ns   | Ready and Reset<br>CL = 10 pF              |

|                                     |                  |                                     |          |                            |      | R <sub>1</sub> ≈ 2K<br>R <sub>2</sub> = 4K |

| Crystal Frequency                   | fclk             |                                     | 9<br>tCY |                            | MHz  | ·                                          |

| Maximum Oscillating<br>Frequency    | fMAX             |                                     |          | 27                         | MHz  |                                            |

Note: (1)  $t_{CY}$  represents the processor clock period

568

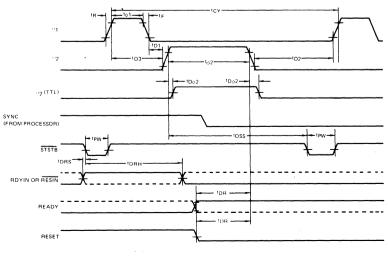

TIMING WAVEFORMS

#### CRYSTAL REQUIREMENTS

| Tolerance               |

|-------------------------|

| Resonance               |

| Load Capacitance        |

| Equivalent Resistance   |

| Power Dissipation (Min) |

Note: (1) With tank circuit use 3rd overtone mode.

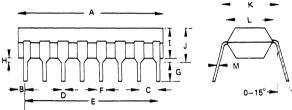

#### PACKAGE OUTLINE μPB8224C

| (PLASTIC) |                        |          |  |  |  |

|-----------|------------------------|----------|--|--|--|

| ITEM      | MILLIMETERS            | INCHES   |  |  |  |

| A         | 19 4 MAX               | 076 MAX  |  |  |  |

| 8         | 0.81                   | 0 0 3    |  |  |  |

| С         | 2 54                   | 0.10     |  |  |  |

| D         | 05                     | 0 02     |  |  |  |

| E         | 17 78                  | 0 70     |  |  |  |

| F         | 13                     | 0 051    |  |  |  |

| G         | 2 54 MIN               | 0.10 MIN |  |  |  |

| н         | 0.5 MIN                | 0.02 MIN |  |  |  |

| 1         | 4 05 MAX               | 0 16 MAX |  |  |  |

| J         | 4 55 MAX               | 0 18 MAX |  |  |  |

| к         | 7 62                   | 0 30     |  |  |  |

| L         | 64                     | 0 25     |  |  |  |

| 11        | 0 25 0 10<br>0 25 0 05 | 0.01     |  |  |  |

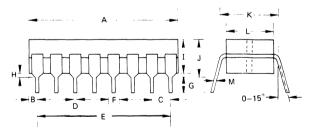

μPB8224D

| (CERDIF | ?) |

|---------|----|

|---------|----|

|      | (CERDIP)    |                 |

|------|-------------|-----------------|

| ITEM | MILLIMETERS | INCHES          |

| A    | 19 9 MAX    | 0 784 MAX       |

| В    | 1 06        | 0 042           |

| С    | 2 54        | 0 10            |

| D    | 046 · 010   | 0 0 18 · 0 004  |

| E    | 17 78       | 0 70            |

| F    | 15          | 0 059           |

| G    | 2.54 MIN    | 0.10 MIN        |

| н    | 0 5 MIN     | 0.019 MIN       |

| 1    | 4.58 MAX    | 0.181 MAX       |

| J    | 5.08 MAX    | 0.20 MAX        |

| к    | 7.62        | 0.30            |

| L    | 6.8         | 0.27            |

| м    | 0.25 + 0 10 | 0.0098 + 0.0039 |

9