# $\mu$ PC3250T7L

SiGe CMOS/BiCMOS Integrated Circuit

IF Down-converter MMIC for Ku-band LNB Converter

R09DS0052EJ0100 Rev.1.00 Oct 23, 2012

### **DESCRIPTION**

The  $\mu$ PC3250T7L is a CMOS/BiCMOS MMIC for Ku-band LNB converter.

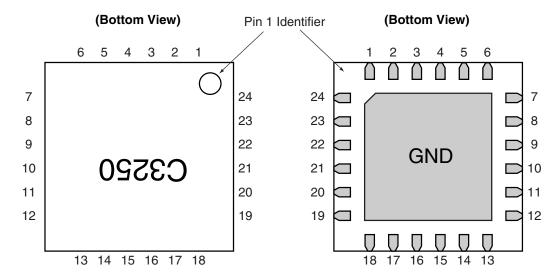

This device is housed in a 24-pin plastic QFN (Quad Flat Non-Leaded) (T7L) package.

### **FEATURES**

• Low power consumption : 3.3 V/63 mA, 208 mW

• Switched LO frequency : 9.75 G Hz, 10.6 GHz, 10.75 GHz

2 step Gain selected function : 41 dB/36 dB

Low noise figure : 7.5 dB

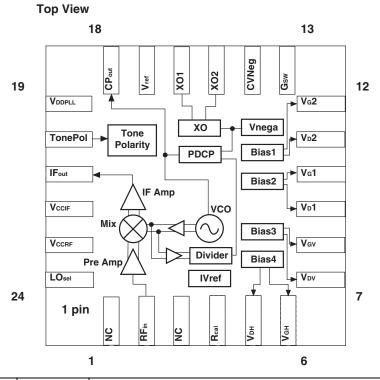

• Fully integrated Mixer/Oscillator/PLL synthesizer/IF Amplifier/4-channel FET bias supply circuit/ Polarity control voltage detector/Tone control signal detector

Integrated power save detector

• 24-pin plastic QFN (T7L) package  $(4.0 \times 4.0 \times 0.6 \text{ mm})$

### **APPLICATIONS**

• Ku-band Low Noise Block (LNB) converters for satellite receiver (DVB-S, ABS-S application)

### ORDERING INFORMATION

| Part Number   | Order Number    | Package            | Marking | Supplying Form                                    |

|---------------|-----------------|--------------------|---------|---------------------------------------------------|

| μPC3250T7L-E1 | μPC3250T7L-E1-A | 24-pin plastic QFN | C3250   | Embossed tape 12 mm wide                          |

|               |                 | (0.5 mm pitch)     |         | Pin 7 to 12 face the perforation side of the tape |

|               |                 | (Pb-Free)          |         | Qty 5 kpcs/reel                                   |

|               |                 |                    |         | Dry packing specification (MSL 3 Equivalent)      |

Remark To order evaluation samples, please contact your nearby sales office.

Part number for sample order: µPC3250T7L

### **CAUTION**

Observe precautions when handling because these devices are sensitive to electrostatic discharge.

### PIN CONNECTIONS

| Pin No. | Pin Name         | Pin No. | Pin Name         | Pin No. | Pin Name          | Pin No. | Pin Name          |

|---------|------------------|---------|------------------|---------|-------------------|---------|-------------------|

| 1       | NC               | 7       | $V_{DV}$         | 13      | Gsw               | 19      | $V_{DDPLL}$       |

| 2       | RF <sub>in</sub> | 8       | $V_{GV}$         | 14      | CVNeg             | 20      | TonePol           |

| 3       | NC               | 9       | V <sub>D</sub> 1 | 15      | XO2               | 21      | IF <sub>out</sub> |

| 4       | R <sub>cal</sub> | 10      | V <sub>G</sub> 1 | 16      | XO1               | 22      | V <sub>CCIF</sub> |

| 5       | $V_{DH}$         | 11      | V <sub>D</sub> 2 | 17      | $V_{ref}$         | 23      | V <sub>CCRF</sub> |

| 6       | $V_{GH}$         | 12      | V <sub>G</sub> 2 | 18      | CP <sub>out</sub> | 24      | LO <sub>sel</sub> |

**Remark** NC means no connection pin.

Heat sink of bottom side of this device is connected to GND.

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                       | Symbol                                                     | Ratings     | Unit |

|-------------------------------------------------|------------------------------------------------------------|-------------|------|

| Supply Voltage                                  | V <sub>CCRF</sub> , V <sub>CCIF</sub> , V <sub>DDPLL</sub> | +4.0        | V    |

| Control Voltage                                 | V <sub>POLA</sub> , V <sub>LOsel</sub> , G <sub>SW</sub>   | +4.0        | V    |

| (TonePol, LO <sub>sel</sub> , G <sub>SW</sub> ) |                                                            |             |      |

| Power dissipation Note                          | $P_{tot}$                                                  | 1.53        | mW   |

| Storage Temperature                             | $T_{stg}$                                                  | -55 to +125 | °C   |

| Operating Ambient Temperature                   | T <sub>A</sub>                                             | -40 to +85  | °C   |

| Input Power                                     | P <sub>in</sub>                                            | 0           | dBm  |

Note: Mounted on double-sided copper-clad  $50 \times 50 \times 0.51$  mm laminated PWB,  $T_A = +85^{\circ}C$

## **BLOCK DIAGRAM**

| Pin No. | Name              | Description                                              |

|---------|-------------------|----------------------------------------------------------|

| 1       | NC                | No Connection                                            |

| 2       | RFin              | Ku band RF signal input, AC coupling required.           |

| 3       | NC                | No Connection                                            |

| 4       | R <sub>cal</sub>  | LNFET drain current adjust by resister                   |

| 5       | $V_{DH}$          | Horizontal LNFET drain voltage supply                    |

| 6       | $V_{GH}$          | Horizontal LNFET gate bias voltage                       |

| 7       | $V_{DV}$          | Vertical LNFET drain voltage supply                      |

| 8       | $V_{GV}$          | Vertical LNFET gate bias voltage                         |

| 9       | V <sub>D</sub> 1  | Common LNFET drain voltage supply 1                      |

| 10      | V <sub>G</sub> 1  | Common LNFET gate bias voltage 1                         |

| 11      | V <sub>D</sub> 2  | Common LNFET drain voltage supply 2                      |

| 12      | V <sub>G</sub> 2  | Common LNFET gate bias voltage 2                         |

| 13      | G <sub>SW</sub>   | Gain control input terminal                              |

| 14      | CVNeg             | Negative voltage line decoupling                         |

| 15      | XO2               | Crystal oscillator connection terminal 2                 |

| 16      | XO1               | Crystal oscillator connection terminal 1                 |

| 17      | $V_{ref}$         | Reference voltage line decoupling                        |

| 18      | CP <sub>out</sub> | Charge pump output, connect capacitor for loop filter    |

| 19      | $V_{DDPLL}$       | PLL Power supply terminal. Decoupling capacitor required |

| 20      | TonePol           | Tone and Polarity control signal input terminal          |

| 21      | IF <sub>out</sub> | L band IF signal output, AC coupling required            |

| 22      | V <sub>CCIF</sub> | IF Power supply terminal. Decoupling capacitor required  |

| 23      | V <sub>CCRF</sub> | RF Power supply terminal. Decoupling capacitor required  |

| 24      | LO <sub>sel</sub> | Local Oscillator frequency control input terminal        |

Remark NC means no connection pin.

Heat sink of bottom side of this device is connected to GND.

### RECOMMENDED OPERATING RANGE ( $T_A = +25$ °C, unless otherwise specified)

| Parameter                                                            | Symbol                                                           | MIN.                  | TYP.  | MAX.                   | Unit |

|----------------------------------------------------------------------|------------------------------------------------------------------|-----------------------|-------|------------------------|------|

| Supply Voltage                                                       | V <sub>CCRF</sub> ,<br>V <sub>CCIF</sub> ,<br>V <sub>DDPLL</sub> | +3.0                  | +3.3  | +3.6                   | V    |

| High level of Control Voltage (LO <sub>sel</sub> , G <sub>SW</sub> ) | V_High                                                           | V <sub>DD</sub> – 0.5 | -     | V <sub>DD</sub> Note 1 | V    |

| Low level of Control Voltage (LO <sub>sel</sub> , G <sub>SW</sub> )  | V_Low                                                            | 0                     | 1     | 0.5                    | V    |

| Operating Ambient Temperature                                        | T <sub>A</sub>                                                   | -40                   | +25   | +85                    | °C   |

| RF Input frequency                                                   | $f_{RF}$                                                         | 10.7                  | _     | 12.75                  | GHz  |

| IF Output frequency                                                  | f <sub>IF</sub>                                                  | 950                   | _     | 2 150                  | GHz  |

| LO frequency                                                         | f <sub>LO</sub>                                                  | _                     | 9.75  | -                      | GHz  |

|                                                                      |                                                                  | _                     | 10.6  | -                      |      |

|                                                                      |                                                                  | _                     | 10.75 | -                      |      |

| TONE control signal frequency                                        | f <sub>TONE</sub>                                                | 18                    | 22    | 26                     | kHz  |

| TONE control signal voltage                                          | $V_{TONE}$                                                       | 0.4                   | 0.6   | 0.8                    | Vp-p |

| Polarity control voltage <sup>Note 2</sup>                           | $V_{POLA}$                                                       | 13                    | -     | 18                     | V    |

| Input Voltage of pin 20 (TonePol)                                    | $V_{TP}$                                                         | 0                     | _     | V <sub>DD</sub>        | V    |

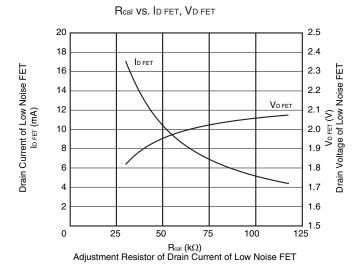

| Adjustment supply current for each FET                               | I <sub>D</sub>                                                   | 5                     | 10    | 18                     | mA   |

Notes: 1  $V_{DD}$ : Supply Voltage =  $V_{CCRF} = V_{CCIF} = V_{DDPLL}$

2 See the evaluation (application) circuit.

The detail connection of pin 20 (TonePol) is shown in the evaluation circuit.

This pin cannot be directly connected to 13 V/18 V polarity control voltage.

The polarity control voltage must be divided to a low voltage by the external resistors.

### **ELECTRICAL CHARACTERISTICS**

# (T<sub>A</sub> = +25°C, V<sub>CCRF</sub> = V<sub>CCIF</sub> = V<sub>DDPLL</sub> = +3.3 V, Z<sub>S</sub> = Z<sub>L</sub> = 50 $\Omega$ , f<sub>xtal</sub> = 25 MHz, unless otherwise specified)

| Parameter                                                     | Symbol            | Test Conditions                           | MIN. | TYP. | MAX. | Unit |

|---------------------------------------------------------------|-------------------|-------------------------------------------|------|------|------|------|

| Total Supply Current 1 Note                                   | I <sub>CC</sub> 1 | V <sub>POLA</sub> > 7.0 V , Non-RF input, | 50   | 63   | 80   | mA   |

| (Vccrf, Vccif, Vddpll)                                        |                   | $G_{SW} = +3.3 \text{ V}$                 |      |      |      |      |

| Normal mode                                                   |                   | (without FETs bias supply current)        |      |      |      |      |

| (High Gain selected)                                          |                   |                                           |      |      |      |      |

| Total Supply Current 2 <sup>Note</sup>                        | I <sub>CC</sub> 2 | V <sub>POLA</sub> > 7.0 V , Non-RF input, | 48.5 | 61.5 | 78.5 | mA   |

| (VCCRF, VCCIF, VDDPLL)                                        |                   | Gsw = 0 V                                 |      |      |      |      |

| Normal mode                                                   |                   | (without FETs bias supply current)        |      |      |      |      |

| (Low Gain selected)                                           |                   | , , , , , , , , , , , , , , , , , , , ,   |      |      |      |      |

| Total Supply Current 3 <sup>Note</sup>                        | I <sub>cc</sub> 3 | V <sub>POLA</sub> = 0 V ( < 3.6V)         | _    | 5    | 10   | mA   |

| (V <sub>CCRF</sub> , V <sub>CCIF</sub> , V <sub>DDPLL</sub> ) |                   | Non-RF input                              |      |      |      |      |

| Power Save mode                                               |                   | (without FETs bias supply current)        |      |      |      |      |

Note: See the evaluation (application) circuit.

The detail connection of pin 20 (TonePol) is shown in the evaluation circuit.

This pin cannot be directly connected to 13 V/18 V polarity control voltage.

The polarity control voltage must be divided to a low voltage by the external resistors.

### **ELECTRICAL CHARACTERISTICS**

# (T<sub>A</sub> = +25°C, V<sub>CCRF</sub> = V<sub>CCIF</sub> = V<sub>DDPLL</sub> = +3.3 V, G<sub>SW</sub> = +3.3 V, Z<sub>S</sub> = Z<sub>L</sub> = 50 $\Omega$ , f<sub>xtal</sub> = 25 MHz, unless otherwise specified)

| Parameter                                                                         | Symbol                 | Test Conditions                                                                                                     | MIN. | TYP. | MAX. | Unit             |

|-----------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------------------|

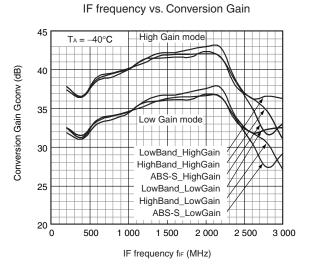

| Conversion Gain 1 <sup>Note 1</sup>                                               | G <sub>conv</sub> 1    | $f_{LO} = 9.75 \text{ GHz}, f_{IF} = 1.5 \text{ GHz},$ $P_{in} = -50 \text{ dBm}$                                   | 37   | 41   | 45   | dB               |

| Conversion Gain 2 <sup>Note 1</sup>                                               | G <sub>conv</sub> 2    | $f_{LO} = 10.6 \text{ GHz}, f_{IF} = 1.5 \text{ GHz},$ $P_{in} = -50 \text{ dBm}$                                   | 37   | 41   | 45   | dB               |

| Conversion Gain 3 <sup>Note 1</sup>                                               | G <sub>conv</sub> 3    | $\begin{split} f_{LO} &= 10.75 \text{ GHz},  f_{IF} = 1.5 \text{ GHz}, \\ P_{in} &= -50 \text{ dBm} \end{split}$    | 37   | 41   | 45   | dB               |

| POLA control Threshold<br>Voltage 1 <sup>Note 1</sup>                             | V <sub>th_POLA</sub> 1 | Power Save mode to Normal mode Dividing resistor : 8.2 k $\Omega$ /51 k $\Omega$                                    | 3.6  | _    | 7.0  | V                |

| POLA control Threshold<br>Voltage 2 <sup>Note 1</sup><br>(Channel selection)      | V <sub>th_POLA</sub> 2 | Vertical mode to Horizontal mode Dividing resistor : 8.2 k $\Omega$ /51 k $\Omega$                                  | 15.2 | 15.7 | 16.2 | V                |

| TONE control signal Threshold<br>Voltage <sup>Note 1</sup><br>(Channel selection) | V <sub>th_TONE</sub>   | Low band to High band $f_{TONE} = 22$ kHz, Duty Cycle = 50%, Pulse wave Divider capacitor : 0.1 $\mu$ F/0.1 $\mu$ F | 0.1  | 0.15 | 0.35 | V <sub>p-p</sub> |

| Drain Voltage H <sup>Note 1, 2</sup>                                              | V <sub>DH</sub>        | $V_{POLA}$ = 18 V, $I_D$ = 10 mA, $R_{cal}$ = 22 k $\Omega$                                                         | 1.8  | 2.0  | 2.2  | V                |

| Drain Voltage V <sup>Note 1, 2</sup>                                              | $V_{DV}$               | $V_{POLA}$ = 13 V, $I_D$ = 10 mA, $R_{cal}$ = 22 k $\Omega$                                                         | 1.8  | 2.0  | 2.2  | V                |

| Drain Voltage 1 Note 1, 2                                                         | V <sub>D</sub> 1       | $I_D$ = 10 mA, $R_{cal}$ = 22 k $\Omega$                                                                            | 1.8  | 2.0  | 2.2  | V                |

| Drain Voltage 2 <sup>Note 1, 2</sup>                                              | V <sub>D</sub> 2       | $I_D = 10 \text{ mA}, R_{cal} = 22 \text{ k}\Omega$                                                                 | 1.8  | 2.0  | 2.2  | V                |

| Drain Current HNote 1, 2                                                          | I <sub>DH</sub>        | $V_{POLA}$ = 18 V, $R_{cal}$ = 22 k $\Omega$                                                                        | 8.5  | 10   | 11.5 | mA               |

| Drain Current VNote 1, 2                                                          | I <sub>DV</sub>        | $V_{POLA}$ = 13 V, $R_{cal}$ = 22 k $\Omega$                                                                        | 8.5  | 10   | 11.5 | mA               |

| Drain Current 1 Note 1, 2                                                         | I <sub>D</sub> 1       | $R_{cal} = 22 \text{ k}\Omega$                                                                                      | 8.5  | 10   | 11.5 | mA               |

| Drain Current 2Note 1, 2                                                          | I <sub>D</sub> 2       | $R_{cal} = 22 \text{ k}\Omega$                                                                                      | 8.5  | 10   | 11.5 | mA               |

| Gate Voltage H <sup>Note 1, 2</sup> of FET OFF mode                               | V <sub>GH</sub>        | V <sub>POLA</sub> = 13 V                                                                                            | -2.0 | -2.5 | -3.0 | V                |

| Gate Voltage V <sup>Note 1, 2</sup> of FET OFF mode                               | V <sub>GV</sub>        | V <sub>POLA</sub> = 18 V                                                                                            | -2.0 | -2.5 | -3.0 | V                |

Notes: 1 See the evaluation (application) circuit.

The detail connection of pin 20 (TonePol) is shown in the evaluation circuit.

This pin cannot be directly connected to 13 V/18 V polarity control voltage.

The polarity control voltage must be divided to a low voltage by the external resistors.

2 See the graph of " $R_{cal}$  vs.  $I_{DFET}$ ,  $V_{DFET}$ ." FET's drain current can be adjusted by the external resisters ( $R_{cal}$ ).

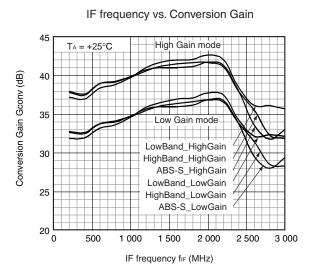

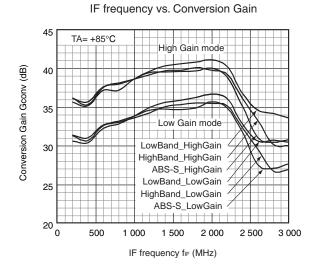

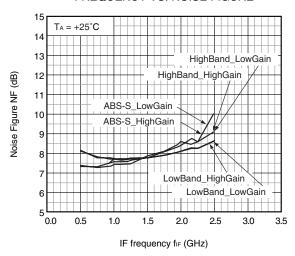

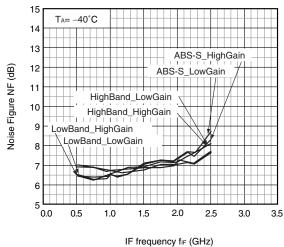

### STANDARD CHARACTERISTICS FOR REFERENCE

(T<sub>A</sub> = +25°C, V<sub>CCRF</sub> = V<sub>CCIF</sub> = V<sub>DDPLL</sub> = +3.3 V, G<sub>SW</sub> = +3.3 V, Z<sub>S</sub> = Z<sub>L</sub> = 50  $\Omega$ , f<sub>xtal</sub> = 25 MHz, unless otherwise specified)

| Parameter                                    | Symbol                   | Test Conditions                                                                                          | Reference<br>Value | Unit   |

|----------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------|--------------------|--------|

| Conversion Gain Flatness 1                   | $\Delta G_{conv}$ 1      | $f_{LO} = 9.75 \text{ GHz}, f_{IF} = 0.95 \text{ G to } 1.95 \text{ GHz},$<br>$P_{in} = -50 \text{ dBm}$ | 2.5                | dB     |

| Conversion Gain Flatness 2                   | $\Delta G_{conv}2$       | $f_{LO}$ = 10.6 GHz, $f_{IF}$ = 1.1 G to 2.15 GHz, $P_{in}$ = -50 dBm                                    | 2.0                | dB     |

| Conversion Gain Flatness 3                   | $\Delta G_{conv}3$       | $f_{LO} = 10.75 \text{ GHz}, f_{IF} = 0.95 \text{ G to } 2.0 \text{ GHz},$<br>$P_{in} = -50 \text{ dBm}$ | 2.0                | dB     |

| Noise Figure 1                               | NF1                      | f <sub>LO</sub> = 9.75 GHz, f <sub>IF</sub> = 1.5 GHz                                                    | 7.5                | dB     |

| Noise Figure 2                               | NF2                      | f <sub>LO</sub> = 10.6 GHz, f <sub>IF</sub> = 1.5 GHz                                                    | 7.5                | dB     |

| Noise Figure 3                               | NF3                      | f <sub>LO</sub> = 10.75 GHz, f <sub>IF</sub> = 1.5 GHz                                                   | 7.5                | dB     |

| Gain 1 dB Compression Output Power 1         | P <sub>O(1 dB)</sub> 1   | f <sub>LO</sub> = 9.75 GHz, f <sub>IF</sub> = 1.5 GHz                                                    | 5                  | dBm    |

| Gain 1 dB Compression Output Power 2         | P <sub>O (1 dB)</sub> 2  | f <sub>LO</sub> = 10.6 GHz, f <sub>IF</sub> = 1.5 GHz                                                    | 5                  | dBm    |

| Gain 1 dB Compression Output Power 3         | P <sub>O(1 dB)</sub> 3   | $f_{LO} = 10.75 \text{ GHz}, f_{IF} = 1.5 \text{ GHz}$                                                   | 5                  | dBm    |

| Output 3rd Order Intercept Point 1           | OIP <sub>3</sub> 1       | $f_{LO} = 9.75 \text{ GHz},$<br>$f_{IF}1 = 1500 \text{ MHz}, f_{IF}2 = 1501 \text{ MHz}$                 | 16                 | dBm    |

| Output 3rd Order Intercept Point 2           | OIP <sub>3</sub> 2       | $f_{LO} = 10.6 \text{ GHz},$<br>$f_{IF}1 = 1500 \text{ MHz}, f_{IF}2 = 1501 \text{ MHz}$                 | 16                 | dBm    |

| Output 3rd Order Intercept Point 3           | OIP <sub>3</sub> 3       | $f_{LO} = 10.75 \text{ GHz},$<br>$f_{IF}1 = 1500 \text{ MHz}, f_{IF}2 = 1501 \text{ MHz}$                | 16                 | dBm    |

| RF Input Return Loss                         | $RL_{RF}$                | f <sub>RF</sub> = 10.7 G to 12.75 GHz                                                                    | 10                 | dB     |

| IF Output Return Loss                        | RL <sub>IF</sub>         | f <sub>RF</sub> = 950 M to 2 150 MHz                                                                     | 10                 | dB     |

| Phase Noise 1                                | PN1                      | 1 kHz offset                                                                                             | -78                | dBc/Hz |

| Phase Noise 2                                | PN2                      | 10 kHz offset                                                                                            | -80                | dBc/Hz |

| Phase Noise 3                                | PN3                      | 100 kHz offset                                                                                           | -88                | dBc/Hz |

| Phase Noise 4                                | PN4                      | 1 MHz offset                                                                                             | -108               | dBc/Hz |

| Integrated phase noise density               | Φnλ (itg)                | Integrated offset frequency 10 k to 15 MHz                                                               | 1.7                | °RMS   |

| Local signal Leakage 1                       | L <sub>o_Leakage</sub> 1 | f <sub>LO</sub> = 9.75 GHz, Local to RF <sub>in</sub>                                                    | -58                | dBm    |

| Local signal Leakage 2                       | L <sub>o_Leakage</sub> 2 | f <sub>LO</sub> = 10.6 GHz, Local to RF <sub>in</sub>                                                    | -58                | dBm    |

| Local signal Leakage 3                       | L <sub>o_Leakage</sub> 3 | $f_{LO} = 10.75$ GHz, Local to RF <sub>in</sub>                                                          | -57                | dBm    |

| Total Circuit current 1 (Reference status 1) | I <sub>CC</sub> 1        | 2ch FET bias supplied V <sub>POLA</sub> > 7.0 V, Non-RF                                                  | 83                 | mA     |

| Total Circuit current 2 (Reference status 2) | I <sub>CC</sub> 2        | 3ch FET bias supplied<br>V <sub>POLA</sub> > 7.0 V, Non-RF                                               | 93                 | mA     |

Note: See the evaluation (application) circuit.

## STANDARD CHARACTERISTICS FOR REFERENCE

(T<sub>A</sub> = +25°C, V<sub>CCRF</sub> = V<sub>CCIF</sub> = V<sub>DDPL</sub>L = +3.3 V, G<sub>SW</sub> = 0 V, Z<sub>S</sub> = Z<sub>L</sub> = 50  $\Omega$ , f<sub>xtal</sub> = 25 MHz, unless otherwise specified)

| Parameter                               | Symbol                 | Test Conditions                                                                                        | Reference<br>Value | Unit |

|-----------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|--------------------|------|

| Conversion Gain 1                       | G <sub>conv</sub> 1    | $f_{LO} = 9.75 \text{ GHz}, f_{IF} = 1.5 \text{ GHz}, \\ P_{in} = -50 \text{ dBm}$                     | 36                 | dB   |

| Conversion Gain 2                       | G <sub>conv</sub> 2    | $f_{LO} = 10.6 \text{ GHz}, f_{IF} = 1.5 \text{ GHz},$<br>$P_{in} = -50 \text{ dBm}$                   | 36                 | dB   |

| Conversion Gain 3                       | G <sub>conv</sub> 3    | $f_{LO} = 10.75 GHz, f_{IF} = 1.5 GHz,$<br>$P_{in} = -50 dBm$                                          | 36                 | dB   |

| Conversion Gain Flatness 1              | $\Delta G_{conv}$ 1    | $f_{LO} = 9.75 \text{ GHz}, f_{IF} = 0.95 \text{ G to } 1.95 \text{ GHz}, \\ P_{in} = -50 \text{ dBm}$ | 2.5                | dB   |

| Conversion Gain Flatness 2              | $\Delta G_{conv}2$     | $f_{LO} = 10.6 \text{ GHz}, f_{IF} = 1.1 \text{ G to } 2.15 \text{ GHz}, \\ P_{in} = -50 \text{ dBm}$  | 2.0                | dB   |

| Conversion Gain Flatness 3              | $\Delta G_{conv}3$     | $f_{LO} = 10.75 \text{ GHz}, f_{IF} = 0.95 \text{ G to } 2.0 \text{ GHz}, \\ P_{in} = -50 \text{ dBm}$ | 2.0                | dB   |

| Noise Figure 1                          | NF1                    | f <sub>LO</sub> = 9.75 GHz, f <sub>IF</sub> = 1.5 GHz                                                  | 7.5                | dB   |

| Noise Figure 2                          | NF2                    | f <sub>LO</sub> = 10.6 GHz, f <sub>IF</sub> = 1.5 GHz                                                  | 7.5                | dB   |

| Noise Figure 3                          | NF3                    | f <sub>LO</sub> = 10.75 GHz, f <sub>IF</sub> = 1.5 GHz                                                 | 7.5                | dB   |

| Gain 1 dB Compression Output<br>Power 1 | P <sub>O(1 dB)</sub> 1 | $f_{LO} = 9.75 \text{ GHz}, f_{IF} = 1.5 \text{ GHz}$                                                  | 2                  | dBm  |

| Gain 1 dB Compression Output<br>Power 2 | P <sub>O(1 dB)</sub> 2 | f <sub>LO</sub> = 10.6 GHz, f <sub>IF</sub> = 1.5 GHz                                                  | 2                  | dBm  |

| Gain 1 dB Compression Output<br>Power 3 | P <sub>O(1 dB)</sub> 3 | $f_{LO} = 10.75 \text{ GHz}, f_{IF} = 1.5 \text{ GHz}$                                                 | 2                  | dBm  |

| Output 3rd Order Intercept Point 1      | OIP <sub>3</sub> 1     | $f_{LO} = 9.75 \text{ GHz}, f_{IF}1 = 1500 \text{ MHz}, \\ f_{IF}2 = 1501 \text{ MHz}$                 | 12                 | dBm  |

| Output 3rd Order Intercept Point 2      | OIP <sub>3</sub> 2     | $f_{LO} = 10.6 \text{ GHz}, f_{IF}1 = 1500 \text{ MHz}, \\ f_{IF}2 = 1501 \text{ MHz}$                 | 12                 | dBm  |

| Output 3rd Order Intercept Point 3      | OIP <sub>3</sub> 3     | $f_{LO} = 10.75 \text{ GHz}, f_{IF}1 = 1500 \text{ MHz}, \\ f_{IF}2 = 1501 \text{ MHz}$                | 12                 | dBm  |

| RF Input Return Loss                    | $RL_{RF}$              | f <sub>RF</sub> = 10.7 G to 12.75 GHz                                                                  | 10                 | dB   |

| IF Output Return Loss                   | RL <sub>IF</sub>       | f <sub>RF</sub> = 950 M to 2 150 MHz                                                                   | 10                 | dB   |

Note: See the evaluation (application) circuit.

### TRUTH TABLE

### Local Oscillator frequency select pin function description (pin 24 (LO<sub>sel</sub>))

| LO <sub>sel</sub>          | LO <sub>sel</sub><br>(DVB-S | LO <sub>sel</sub> = High<br>(ABS-S mode) |           |

|----------------------------|-----------------------------|------------------------------------------|-----------|

|                            | Tone signal = 0 kHz         | Tone signal = 22 kHz                     | -         |

| Local Oscillator frequency | 9.75 GHz                    | 10.6 GHz                                 | 10.75 GHz |

Note: The relationships between the LO<sub>sel</sub> state and the pin connection are as follows.

By connecting this pin to GND line (0 V DC), LO<sub>sel</sub> becomes "Low" state.

By connecting this pin to  $V_{DD}$  line ( $V_{DD}$  DC),  $LO_{sel}$  becomes "High" state.

The  $V_{DD}$  described above means the power supply voltage. Its value is 3.3 V the same as  $V_{CCRF}$ ,  $V_{CCIF}$ , and  $V_{DDPLL}$ .

### FET's DC bias control pin function description (pin 20 (TonePol), polarity control voltage)

|                   | FETs              | Horizontal FET   |            | Vertical FET     |                 | Common FET 1     |                  | Common FET 2     |                  |

|-------------------|-------------------|------------------|------------|------------------|-----------------|------------------|------------------|------------------|------------------|

| V <sub>POLA</sub> |                   | $V_{GH}$         | $V_{DH}$   | V <sub>GV</sub>  | V <sub>DV</sub> | V <sub>G</sub> 1 | V <sub>D</sub> 1 | V <sub>G</sub> 2 | V <sub>D</sub> 2 |

| Normal            | V <sub>POLA</sub> | Controlled       | Controlled | Disable          | Disable         | Controlled       | Controlled       | Controlled       | Controlled       |

| mode              | > 16.2 V<br>Note  | (-2.5 V to +1 V) | (≈ 2 V)    | (-2.5V)          | (0 V)           | (-2.5 V to +1 V) | (≈ 2 V)          | (-2.5 V to +1 V) | (≈ 2 V)          |

|                   | V <sub>POLA</sub> | Disable          | Disable    | Controlled       | Controlled      | Controlled       | Controlled       | Controlled       | Controlled       |

|                   | < 15.2 V<br>Note  | (-2.5 V)         | (0 V)      | (-2.5 V to +1 V) | (≈ 2 V)         | (-2.5 V to +1 V) | (≈ 2 V)          | (-2.5 V to +1 V) | (≈ 2 V)          |

| Power             | V <sub>POLA</sub> | Disable          | Disable    | Controlled       | Controlled      | Controlled       | Controlled       | Controlled       | Controlled       |

| Save<br>mode      | < 3.6 V<br>Note   | (-2.5 V)         | (0 V)      | (-2.5 V to +1 V) | (≈ 2 V)         | (-2.5 V to +1 V) | (≈ 2 V)          | (-2.5 V to +1 V) | (≈ 2 V)          |

Note: Dividing Resistor: 8.2 k $\Omega$ /51 k $\Omega$

See the evaluation (application) circuit.

The detail connection of pin 20 (TonePol) is shown in the evaluation circuit.

This pin cannot be directly connected to 13 V/18 V polarity control voltage.

The polarity control voltage must be divided to a low voltage.

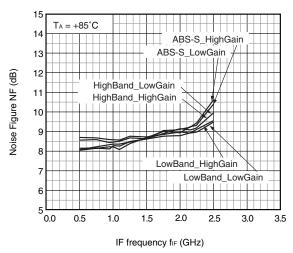

# TYPICAL CHARACTERISTICS $(T_A = +25^{\circ}C, \text{ unless otherwise specified})$

**Remark** The graphs indicate nominal characteristics.

#### FREQUENCY VS. NOISE FIGURE

# FREQUENCY VS. NOISE FIGURE

### FREQUENCY VS. NOISE FIGURE

Remark The graphs indicate nominal characteristics.

For example,  $R_{cal}$  = 22 k $\Omega,$   $I_D$  = 10 mA is set.

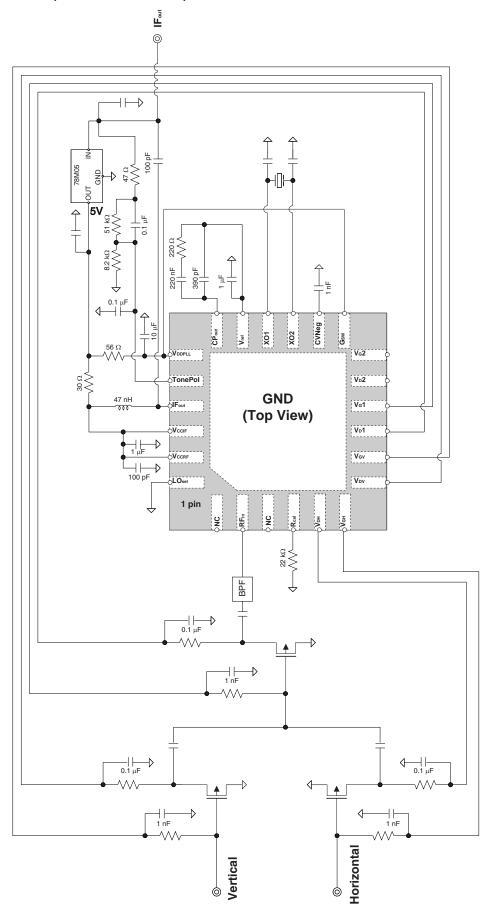

## **EVALUATION CIRCUIT**

**LO**sel

24

Vev

0.1 µF

. Vertical FET

pin

NC

RFin

NC

6

Horizontal FET

RFin ⊚

€ 22 kΩ

For example, Polarity control voltage is V<sub>POLA</sub> = +13 V and +18 V, V<sub>TP</sub> is divided to a low voltage, +1.8 V and +2.5 V, respectively, by the resistors (8.2 k $\Omega$ , 51 k $\Omega$ ). Vcc (3.3 V) **IF**out **Tone** 8.2 kΩ 51 kΩ 100 pF 100 F 0.1 μF 10 μF VDDPLL (3.3 V) 19 VCCIF 220 nF  $220 \Omega$ 18 -| |<sub>390 p</sub>F√√√ CPout Vref **GND** XO1 (Top View) AT-41CD2 (fxtal = 25 MHz) XO2 CVNeg Gsw Gsw 13 <u>^</u> <u>د</u> **V**<sub>D</sub>2 V<sub>6</sub>2 <u>L</u> 12

Remark NC means Non-Connection. Heat sink (bottom side of the device) is connected to GND. Board material is RO4003C (Rogers, t = 0.508 mm).

Common FET1

0.1 µF

0.1

Common FET2

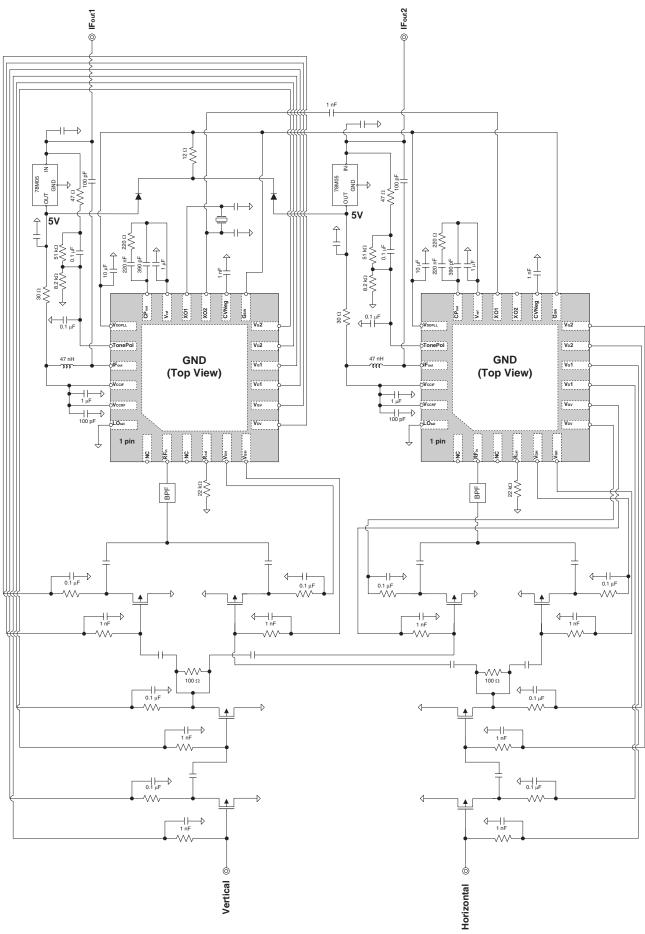

# APPLICATION CIRCUIT

# FOR SINGLE LNB (REFERENCE ONLY)

# FOR TWIN LNB (DOUBLE SINGLE LNB) (REFERENCE ONLY)

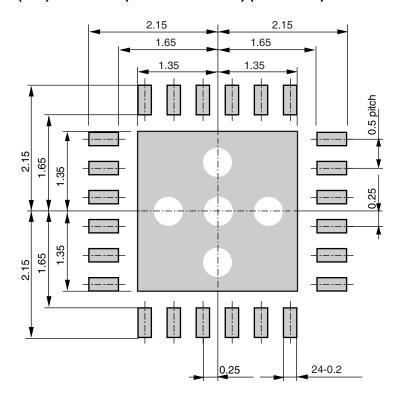

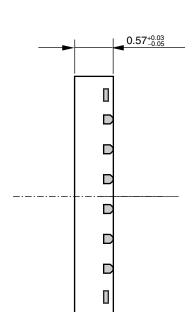

## MOUNTING PAD LAYOUT DIMENSIONS

24-PIN PLASTIC QFN (T7L) PACKAGE (4.0  $\times$  4.0  $\times$  0.6 mm) (UNIT : mm)

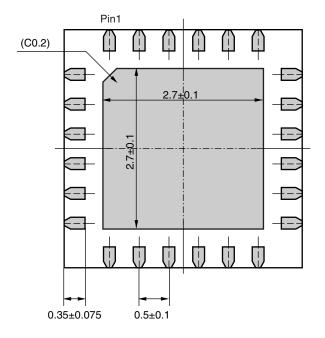

## **PACKAGE DIMENSIONS**

# 24-PIN PLASTIC QFN (T7L) PACKAGE ( $4.0 \times 4.0 \times 0.6$ mm) (UNIT : mm)

(Top View)

4.0±0.1

(Side View)

# (Bottom View)

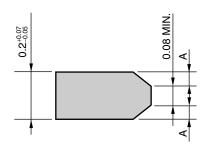

### (Dimensions of Each Pin Part)

Remark A > 0

### RECOMMENDED SOLDERING CONDITIONS

This product should be soldered and mounted under the following recommended conditions. For soldering methods and conditions other than those recommended below, contact your nearby sales office.

| Soldering Method | Soldering Conditions                                                                                                                                                              |                                                                               | Condition Symbol |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------|

| Infrared Reflow  | Peak temperature (package surface temperature) Time at peak temperature Time at temperature of 220°C or higher Preheating time at 120 to 180°C Maximum number of reflow processes | : 10 seconds or less<br>: 60 seconds or less<br>: 120±30 seconds<br>: 3 times | IR260            |

| D (111) (1       | Maximum chlorine content of rosin flux (% mass)                                                                                                                                   | . ,                                                                           | 110050           |

| Partial Heating  | Peak temperature (package surface temperature) Soldering time (per side of device) Maximum chlorine content of rosin flux (% mass)                                                | : 3 seconds or less                                                           | HS350            |

| C | Α | U | Τ | 10 | ١ |

|---|---|---|---|----|---|

|   |   |   |   |    |   |

Do not use different soldering methods together (except for partial heating).

**Revision History**

# $\mu$ PC3250T7L Data Sheet

|      |              | Description |                      |  |

|------|--------------|-------------|----------------------|--|

| Rev. | Date         | Page        | Summary              |  |

| 1.00 | Oct 23, 2012 | _           | First edition issued |  |

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information,

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries,

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics

#### **SALES OFFICES**

Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

California Eastern Laboratories, Inc. 4590 Patrick Henry Drive, Santa Clara, California 95054, U.S.A. Tel: +1-408-919-2500, Fax: +1-408-988-0279

Renesas Electronics Europe Limited

Dukes Meadow, Milliboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +44-1628-651-700, Fax: +44-1628-651-804 Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, Germar Tel: +49-211-65030, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

7th Floor, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100083, P.R.China

Tel: +86-10-9235-1155, Fax: +86-10-8235-7679 Renesas Electronics (Shanghai) Co., Ltd. Unit 204, 205, AZIA Center, No.1233 Lujiazui Ring Rd., Pudong District, Shanghai 200120, China Tel: +86-21-5877-1818, Fax: +86-21-6887-7858 / -7898

Renesas Electronics Hong Kong Limited

Unit 1601-1613, 16/F., Tower 2, Grand Century Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

Tel: +852-2868-9318, Fax: +852-2886-9022/9044

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei, Tai Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Ini Tel: +65-6213-0200, Fax: +65-6213-0300 Innovation Centre Singapore 339949

Renesas Electronics Malaysia Sdn.Bhd.

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tei: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics Korea Co., Ltd. 11F., Samik Lavied' or Bidg., 720-2 Yeoksam-Dong, Kangnam-Ku, Seoul 135-080, Korea Tel: 482-2-558-3737, Fax: +82-2-558-5141

© 2012 Renesas Electronics Corporation, All rights reserved.