## DATA SHEET

# MOS INTEGRATED CIRCUIT μ**PD17005**

## DIGITAL TUNING SYSTEM HARDWARE BUILT-IN 4-BIT SINGLE-CHIP MICROCONTROLLER

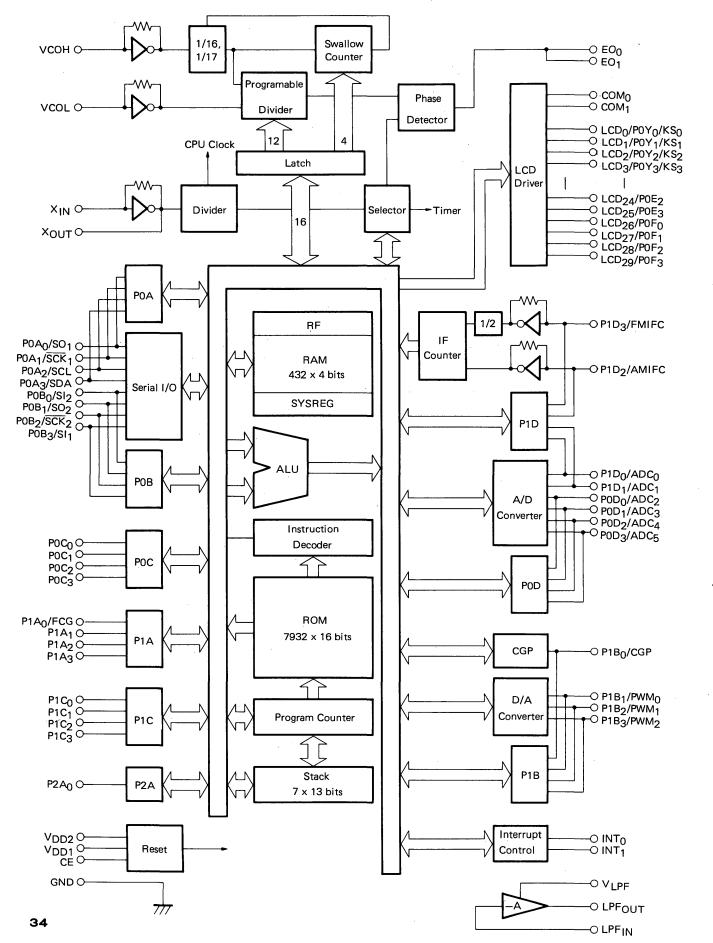

$\mu$ PD17005 is a 4-bit single-chip CMOS micro controller which contains digital tuning system hardware.

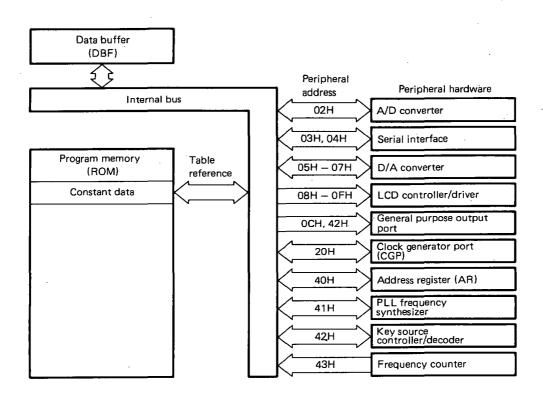

17K architecture is used for CPU, data and memory manipulations and various types of operations, and peripheral hardware control can be performed directly by one instruction.

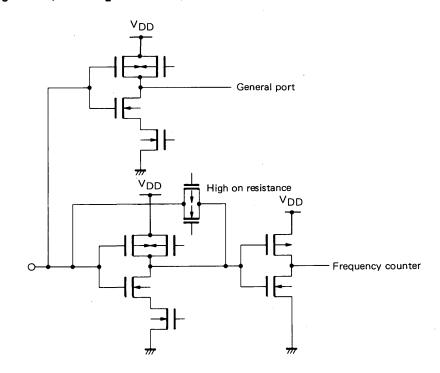

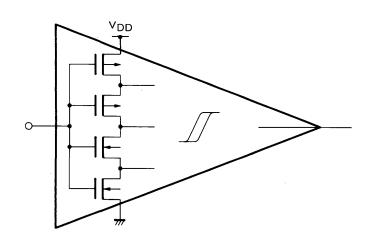

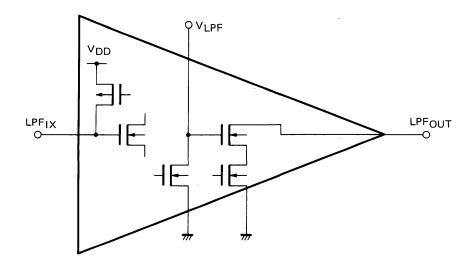

Peripheral hardware devices include a prescaler which operates up to 150 MHz, PLL frequency synthesizer, LPF (Low Pass Filter) amplifier, and frequency counter for digital tuning in addition to various types of input/output ports, LCD controller/driver, A/D converter, D/A converter (PWM output), and clock generator ports.

Consequently, a high performance digital tuning system with a variety of functions can be constructed using only one chip.  $\mu$ PD17005 is pin-compatible with  $\mu$ PD17003A and its memory size (ROM) is reduced. One-time PROM version  $\mu$ PD17P005 is available as  $\mu$ PD17005, and  $\mu$ PD17P005 can be used for program evaluation of  $\mu$ PD17005 at small volume production.

### FEATURES

- Using 17K architecture

- Program memory (ROM)

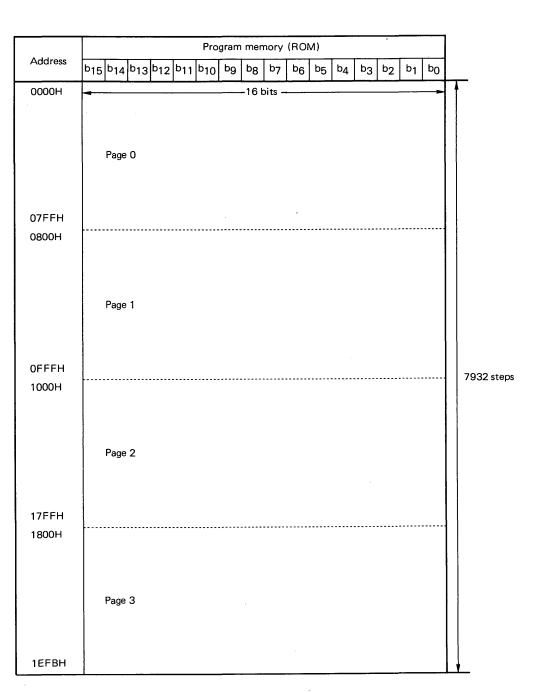

16K bytes (7932 steps x 16 bits)

- General purpose data memory (RAM)

432 nibble (432 words x 4 bits)

- Instruction execution time

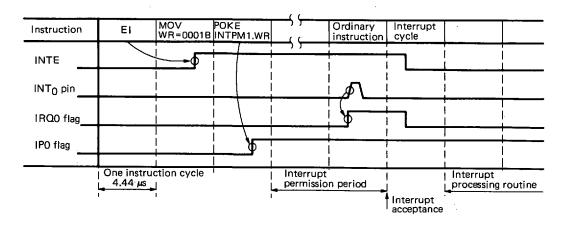

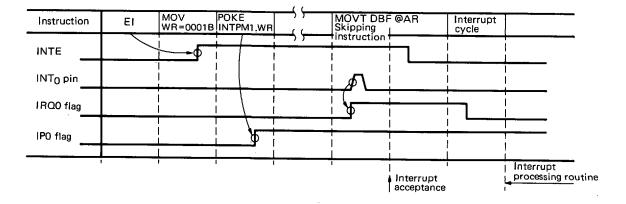

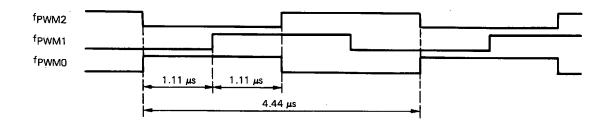

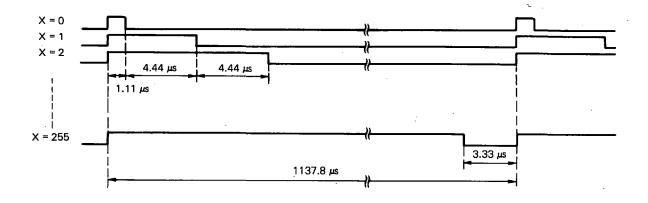

4.44 μs (using 4.5 MHz quarts oscillator)

- Decimal operation enabled

- Table reference enabled

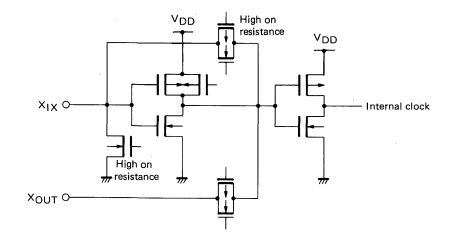

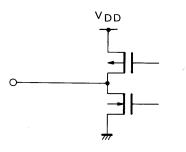

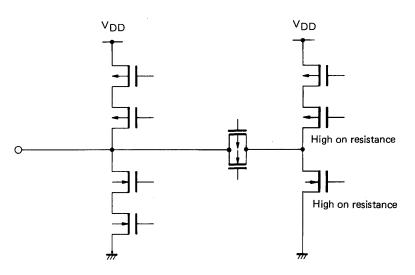

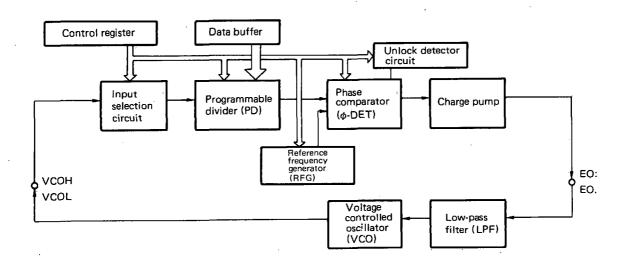

- Built-in PLL frequency synthesizer hardware Dual modules prescaler (150 MHz Max.), programmable divider, phase comparator, charge pump, and LPF amplifier

- Various types of peripheral hardware General purpose input/output ports, LCD controller/driver, serial interface, A/D converter, D/A converter (PWM output), clock generator, ports, and frequency counter

- Various types of interrupt

External interrupt: 2 channels

Internal interrupt: 3 channels

- Power On Reset, resetting by a CE pin, and built-in blackout detection circuit

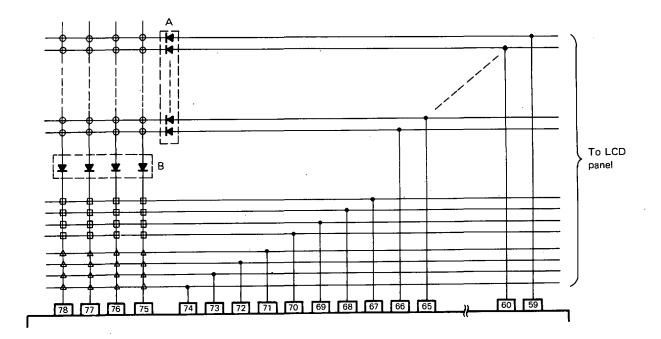

- CMOS low power consumption

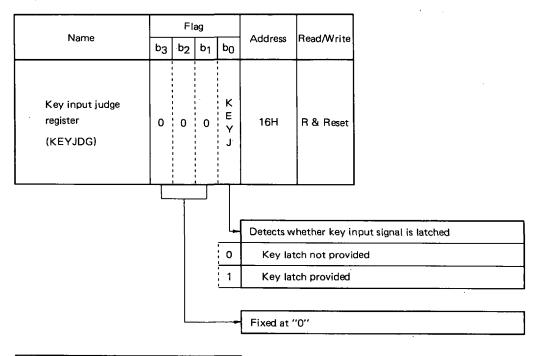

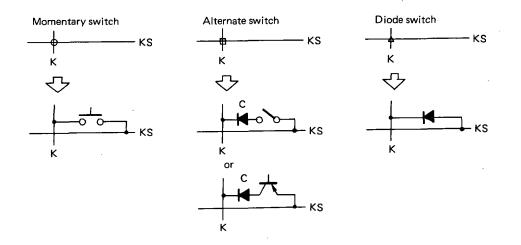

- Power supply voltage 5 V ± 10 %

### ORDERING INFORMATION

| Order Code         | Package                      | Quality Grade |

|--------------------|------------------------------|---------------|

| μPD17005GF-xxx-3B9 | 80-pin plastic QFP (14 x 20) | Standard      |

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

## $\mu \text{PD17005 FUNCTION OUTLINE}$

| ltem                                                       | Function                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program memory (ROM)                                       | <ul> <li>16K bytes (7932 steps x 16 bits)</li> <li>Table reference area:</li> <li>up to 7932 steps</li> </ul>                                                                                                                                                                                                                                                         |

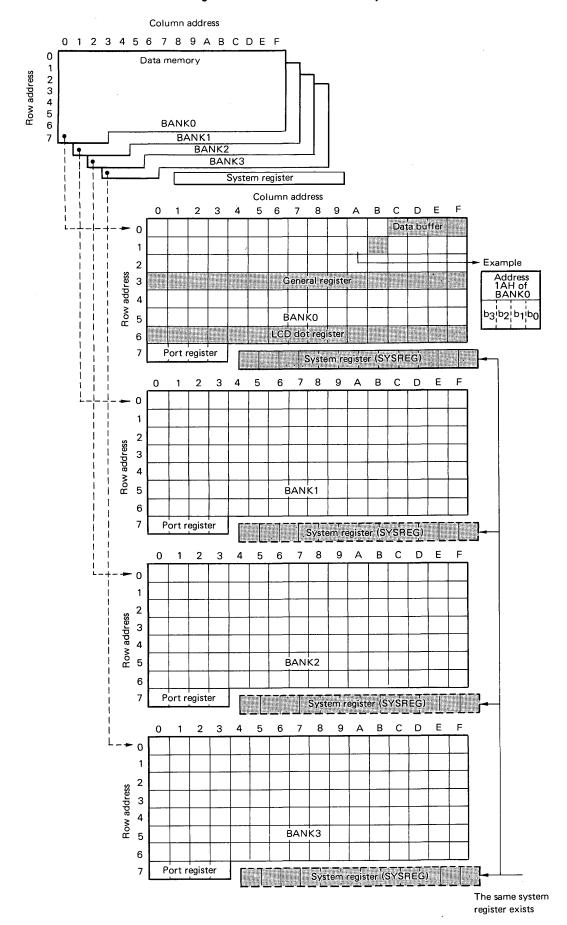

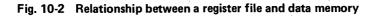

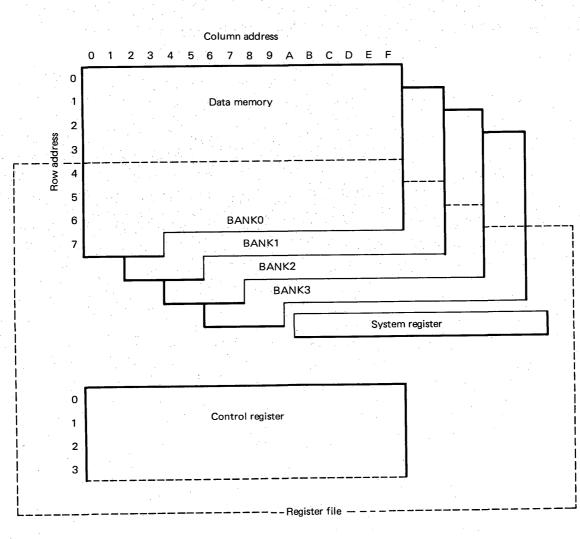

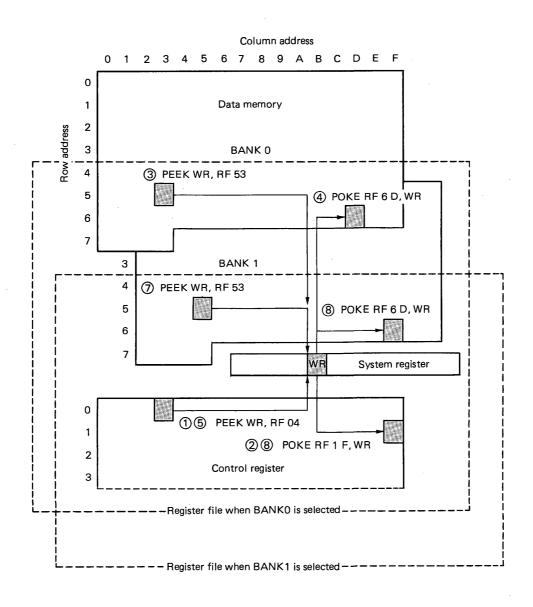

| General data memory (RAM)                                  | <ul> <li>432 nibble (432 words x 4 bits)</li> <li>Data buffer : 4 nibbles</li> <li>General register : 16 nibbles</li> </ul>                                                                                                                                                                                                                                           |

| System register                                            | • 12 nibbles                                                                                                                                                                                                                                                                                                                                                          |

| Register file                                              | 33 nibbles (control register)                                                                                                                                                                                                                                                                                                                                         |

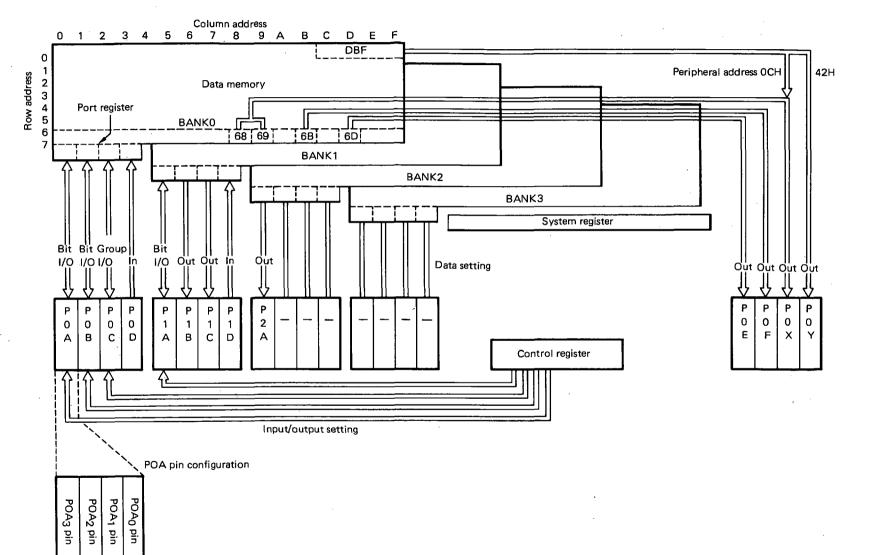

| General port register<br>(including LCD dot data register) | • 24 nibbles                                                                                                                                                                                                                                                                                                                                                          |

| Instruction execution time                                 | <ul> <li>4.44 μs (using 4.5 MHz quarts oscillator)</li> </ul>                                                                                                                                                                                                                                                                                                         |

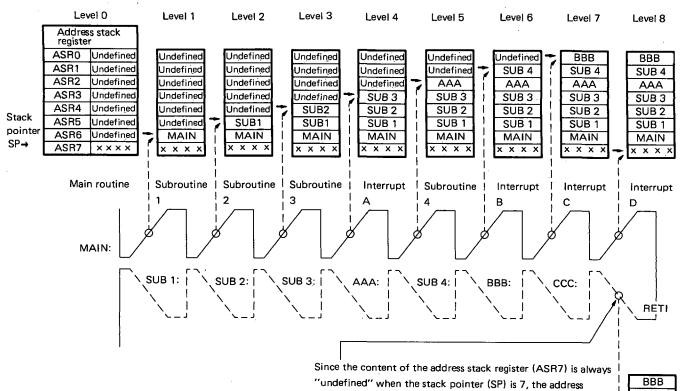

| Stack level                                                | 7 levels (stack operation enabled)                                                                                                                                                                                                                                                                                                                                    |

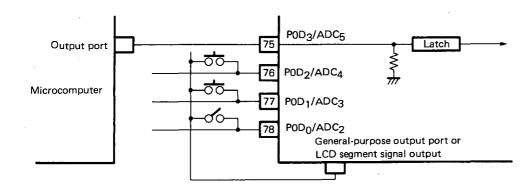

| General purpose port                                       | <ul> <li>Input/output port : 16</li> <li>Input ports : 8</li> <li>Output ports : 9 (+30: LCD segment pin)</li> </ul>                                                                                                                                                                                                                                                  |

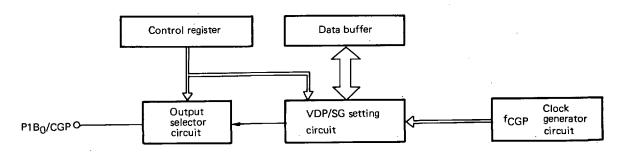

| Clock generator port (CGP)                                 | <ul> <li>1</li> <li>VDP (Variable Duty Pulse) and SG (Signal Generator) functions</li> </ul>                                                                                                                                                                                                                                                                          |

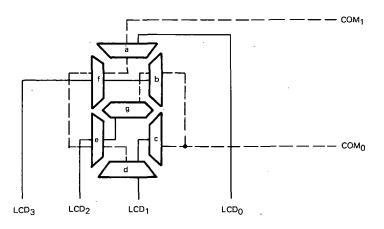

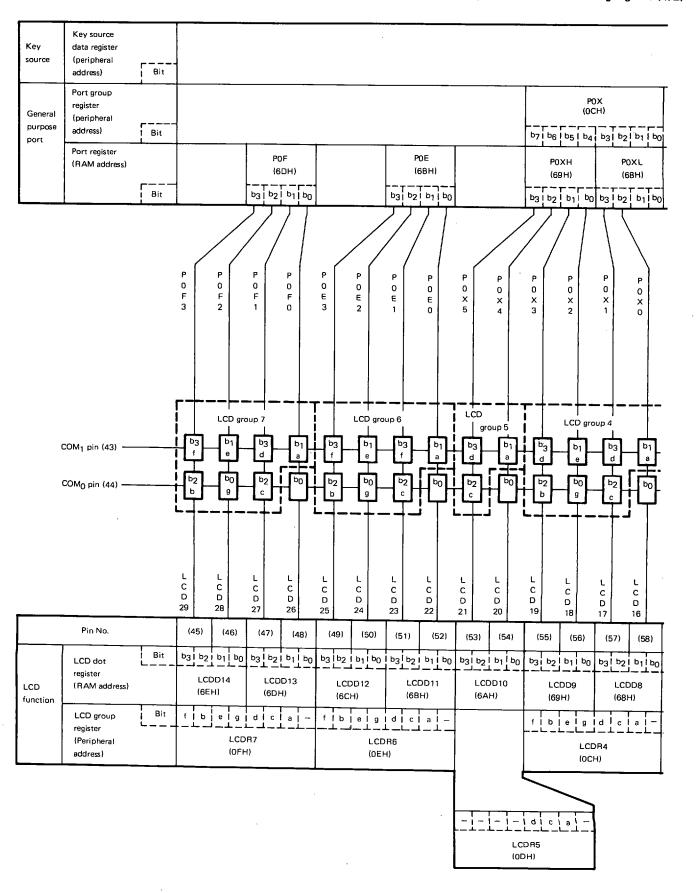

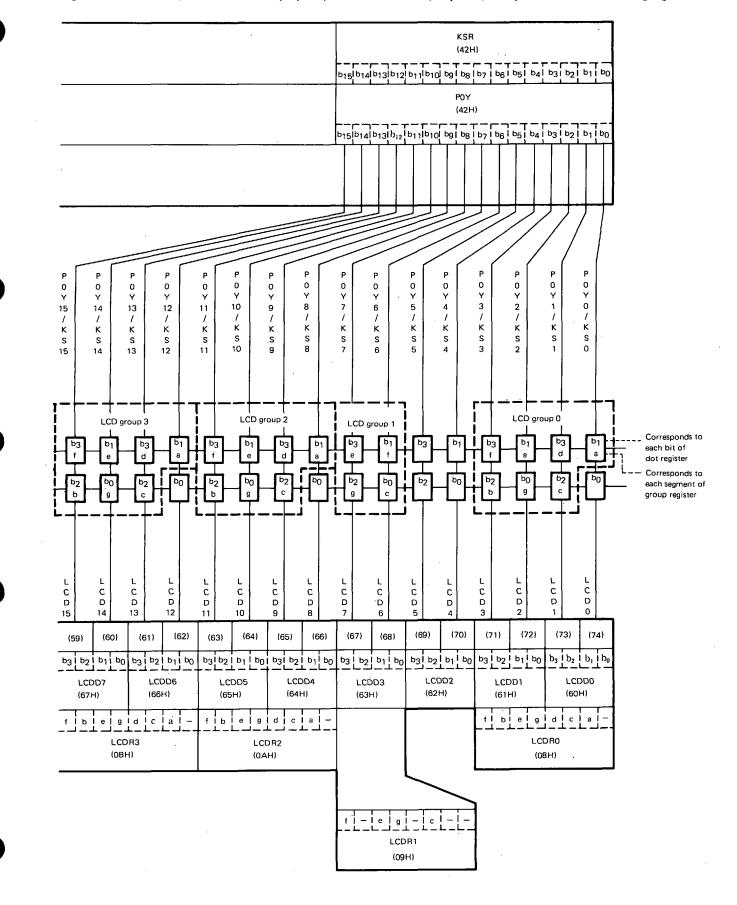

| LCD controller/driver                                      | <ul> <li>30 segments, 2 common         <ol> <li>30 segments, 2 common</li> <li>1/2 duty, 1/2 bias, frame frequency 250 Hz, driving voltage V<sub>DD</sub>, segment pin used also for key source: 16 ports</li> <li>All of the 30 ports can be used as output ports</li> <li>(4 ports, 4 ports, 6 ports, and 16 ports can be set independently)</li> </ol> </li> </ul> |

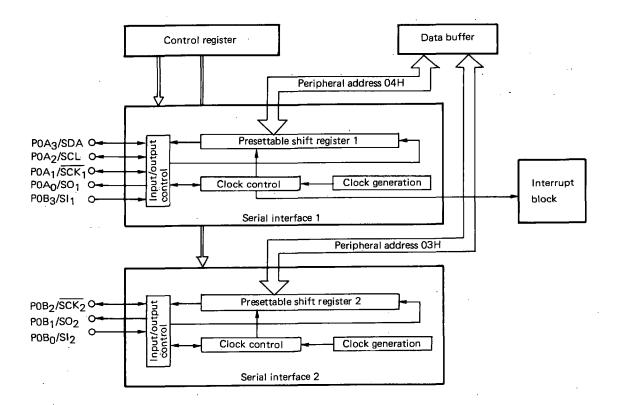

| Serial interface                                           | <ul> <li>Two types (3 channels)</li> <li>8-bit 3-wire system: 2 channels</li> <li>8-bit 2-wire system: 1 channel</li> </ul>                                                                                                                                                                                                                                           |

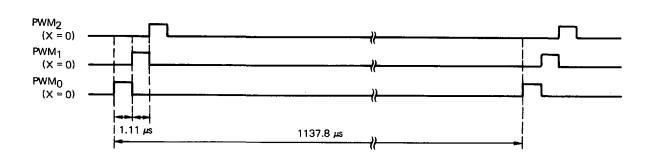

| D/A converter                                              | <ul> <li>8 bits x 3 (PWM output and output resisting pressure 16 V Max.)</li> </ul>                                                                                                                                                                                                                                                                                   |

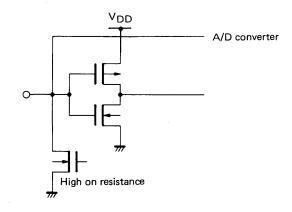

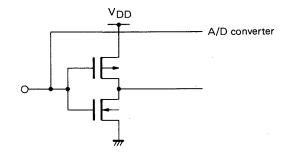

| A/D converter                                              | 6 bits x 6 (consecutive comparison method by software)                                                                                                                                                                                                                                                                                                                |

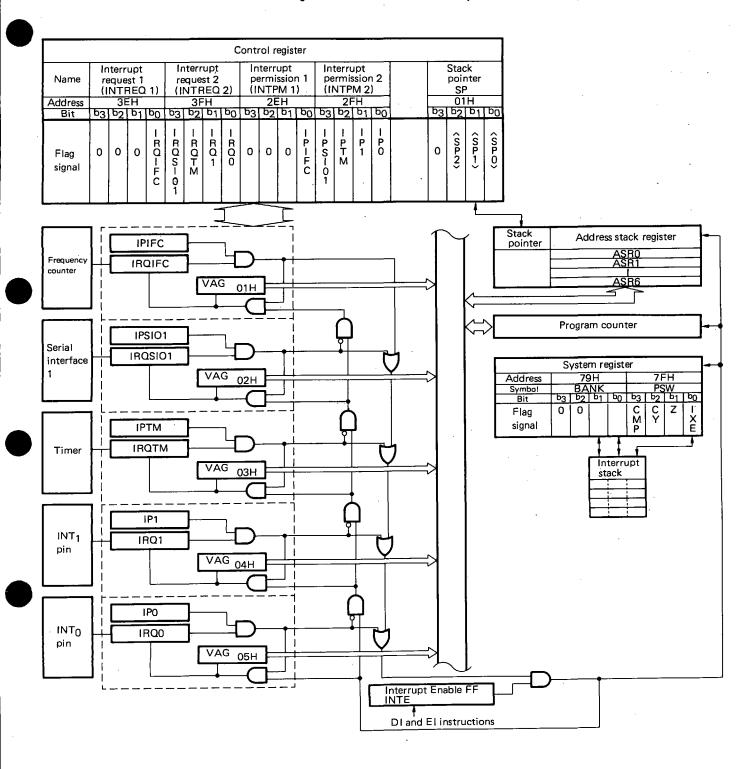

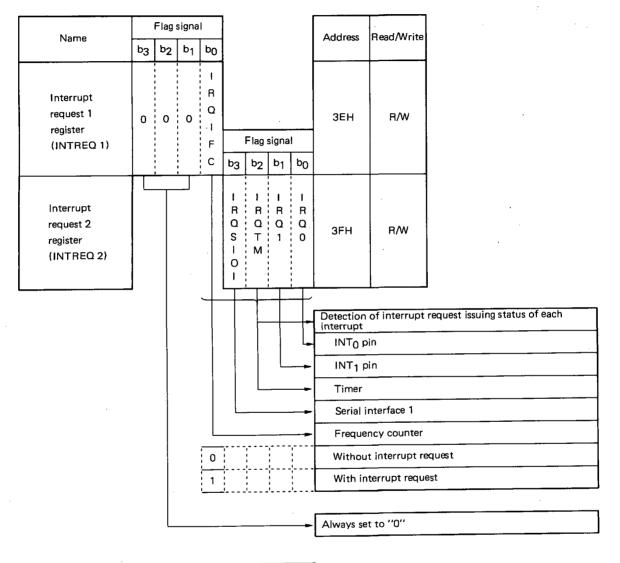

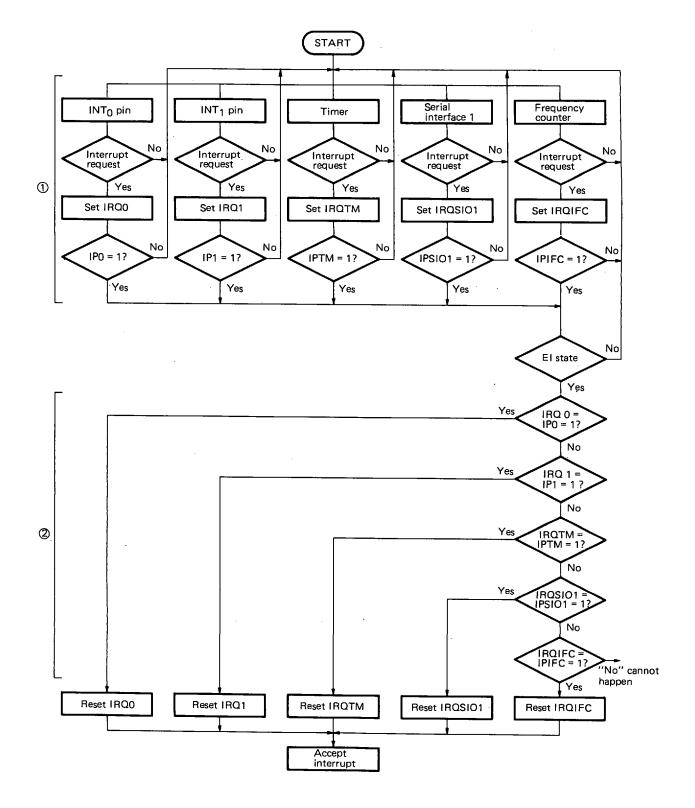

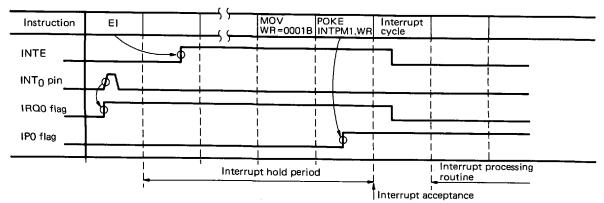

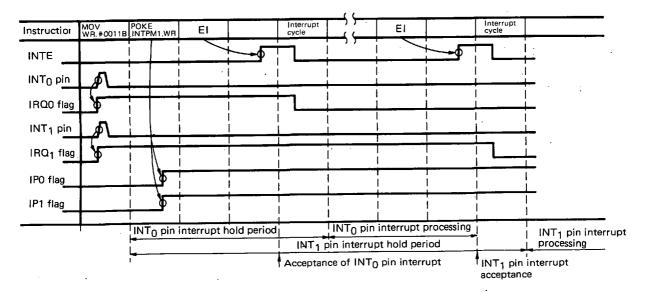

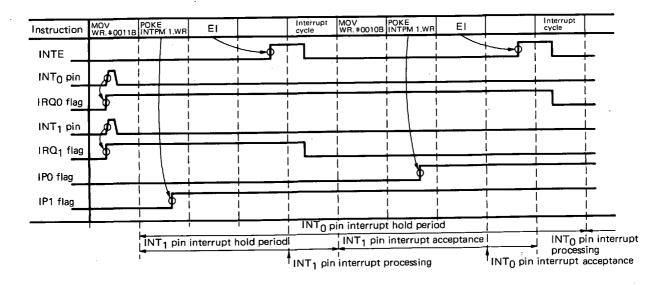

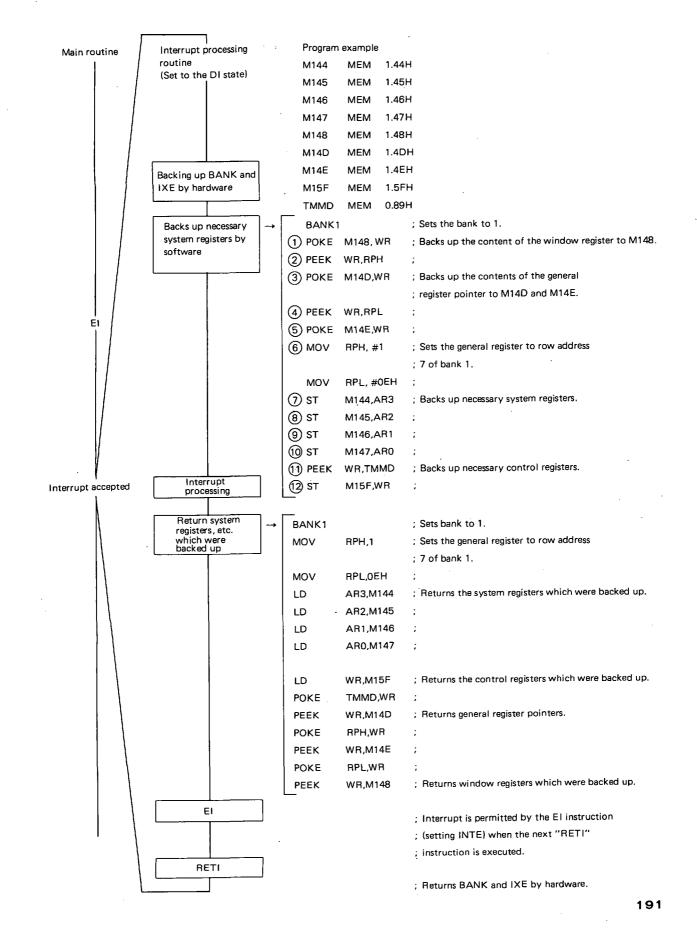

| Interrupt                                                  | <ul> <li>5 channels (maskable interrupt)</li> <li>External interrupt : 2 channels (INT<sub>0</sub> pin and INT<sub>1</sub> pin)</li> <li>Internal interrupt : 3 channels (timer, serial interface 1, and frequency counter)</li> </ul>                                                                                                                                |

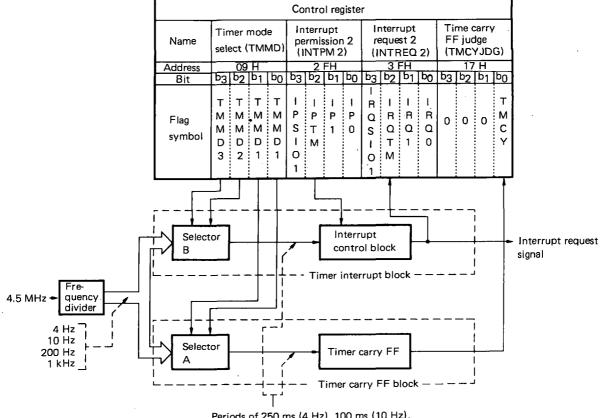

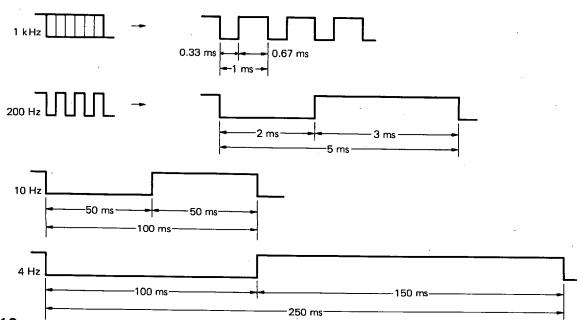

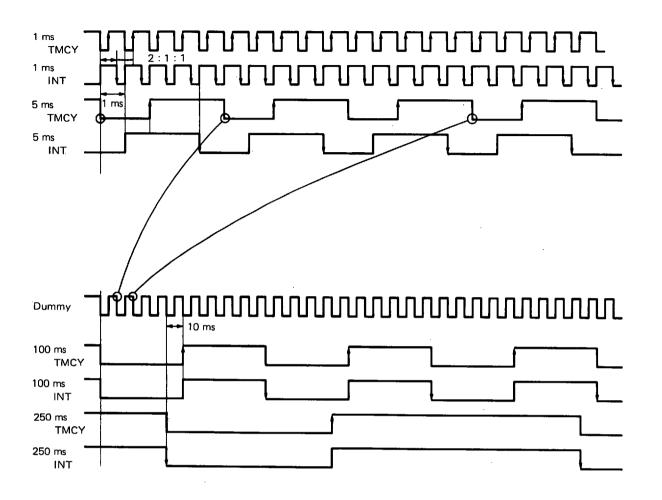

| Timer                                                      | <ul> <li>Two types</li> <li>Timer carry FF (1, 5, 100, 250 ms)</li> <li>Timer interrupt (1, 5, 100, 250 ms)</li> </ul>                                                                                                                                                                                                                                                |

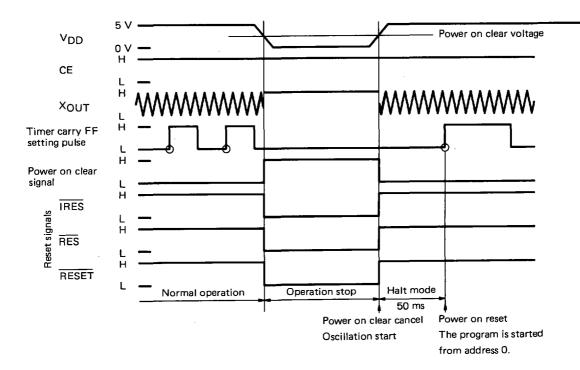

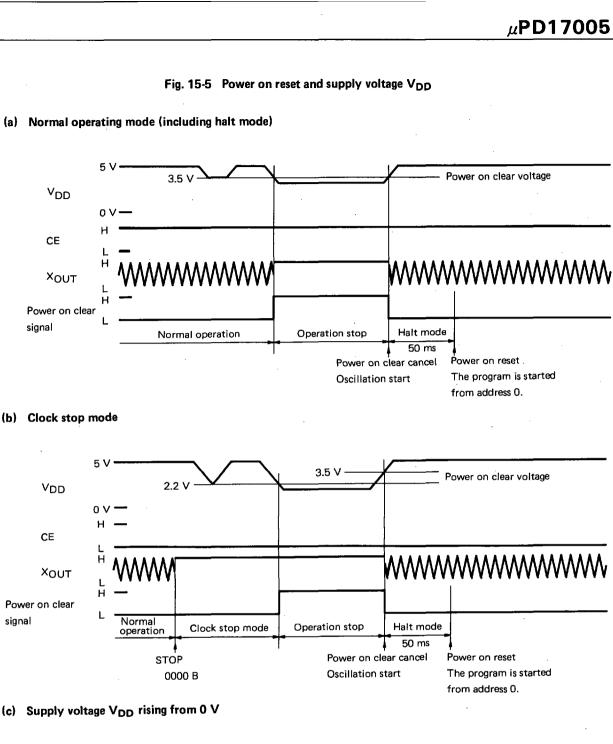

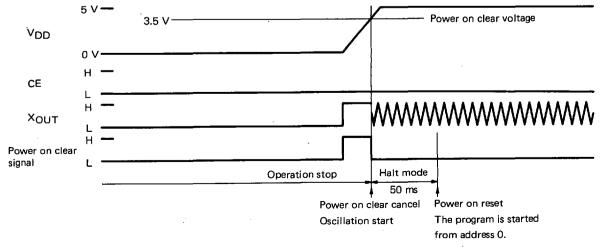

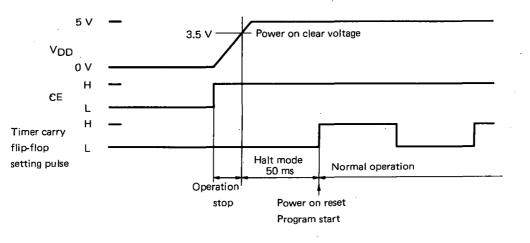

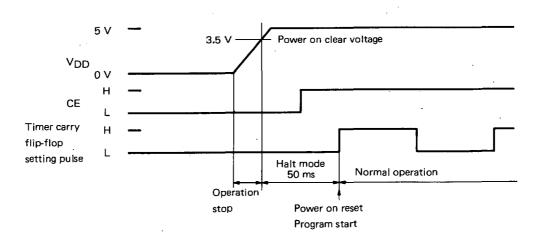

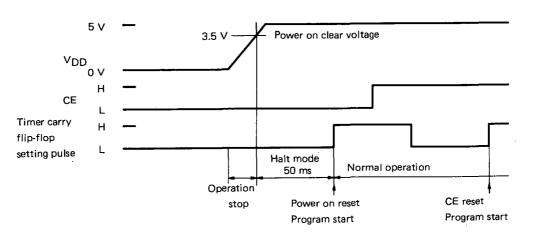

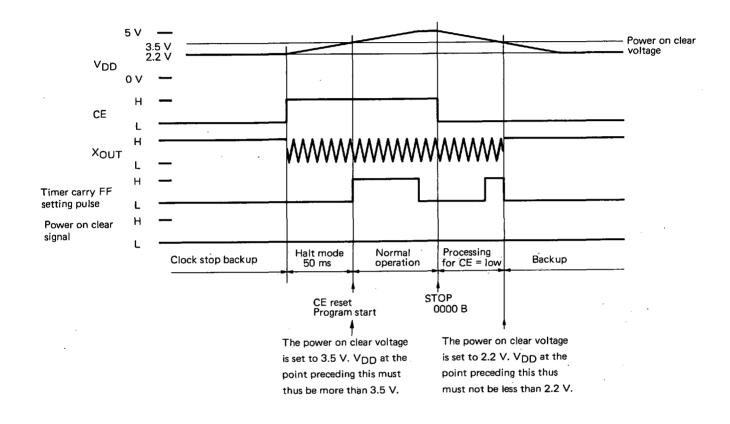

| Reset                                                      | <ul> <li>Power On Reset (at power supply connection)</li> <li>Resetting by CE pin (CE pin Low → High)</li> <li>Blackout detection function</li> </ul>                                                                                                                                                                                                                 |

| Item                      |                     | Function                                                                                                                                                                                                       |

|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLL frequency synthesizer | Division method     | <ul> <li>2 types         Direct division method             (VCOL pin 20 MHz Max.)             Pulse swallow method             (VCOL pin 40 MHz Max.)             (VCOH pin 150 MHz Max.)         </li> </ul> |

|                           | Reference frequency | <ul> <li>12 types are selected by the program</li> <li>1, 1.25, 2.5, 3, 5, 6.25, 9, 10, 12.5, 25, 50, 100 kHz</li> </ul>                                                                                       |

|                           | Charge pump         | Two independent error output                                                                                                                                                                                   |

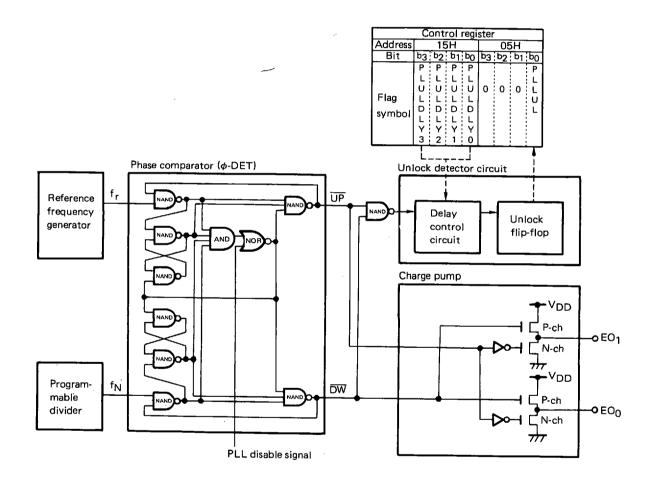

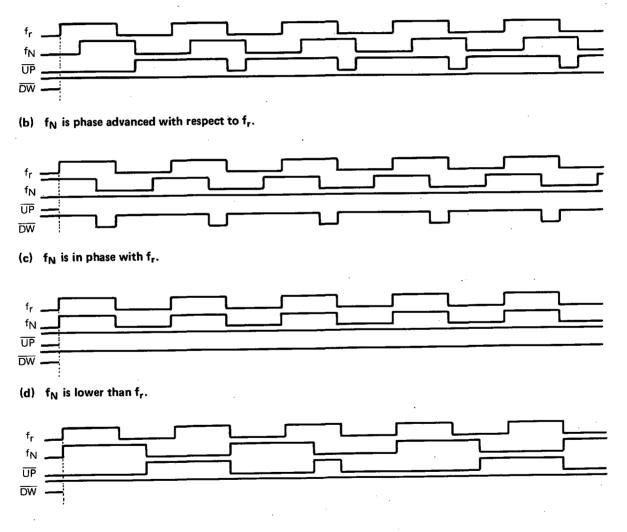

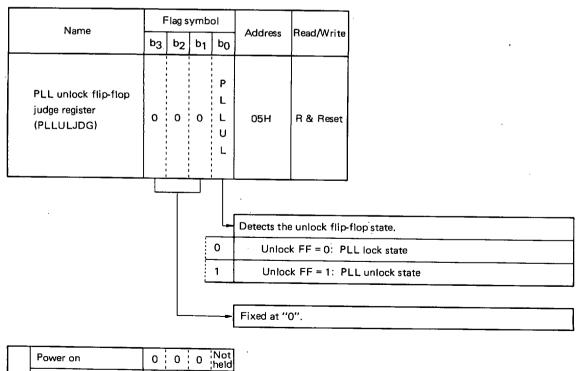

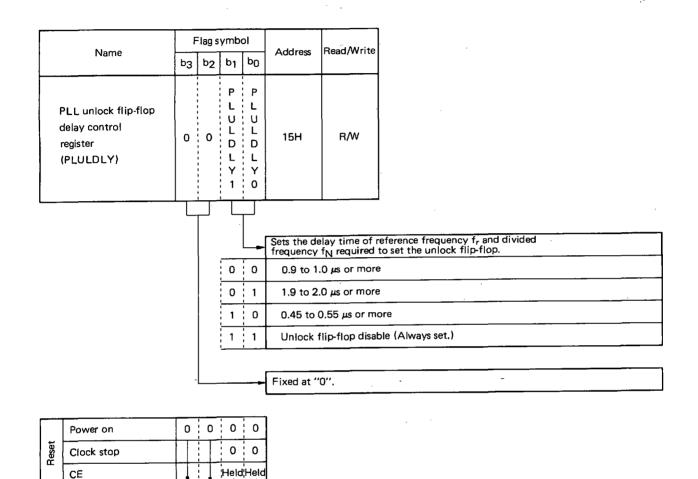

|                           | Phase comparator    | <ul> <li>Unlocking can be detected by a program</li> <li>Unlocking FF delay time can be selected</li> </ul>                                                                                                    |

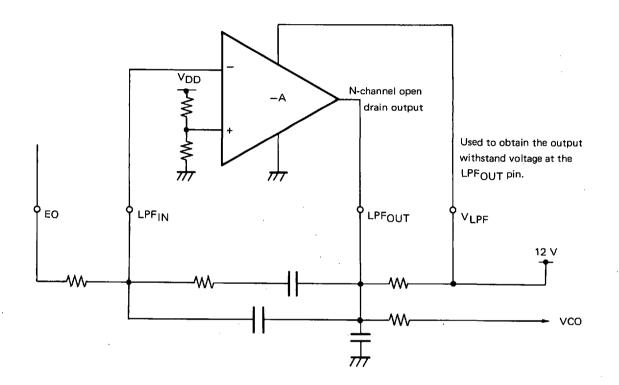

|                           | LPF amplifier       | CMOS operation amplifier output resisting pressure 16 V Max.                                                                                                                                                   |

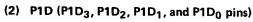

| Frequency counter         |                     | <ul> <li>Frequency test<br/>P1D<sub>3</sub>/FMIFC pin 5-15 MHz<br/>P1D<sub>2</sub>/AMIFC pin 0.1-1 MHz</li> <li>External gate width test<br/>P1A<sub>1</sub>/FCG pin</li> </ul>                                |

| Power supply voltage      |                     | 5 V ±10 %                                                                                                                                                                                                      |

| Package                   |                     | 80-pin plastic QFP (14 x 20)                                                                                                                                                                                   |

Peripheral hardware - Program memory (ROM) -Serial A/D D/A Frequency PLL Instruction All the instructions are 16-bit one-word converter interface counter converter instructions Л Clock generator Data memory (RAM) LCD controller/ driver Constant data Can be transferred to data buffer (table reference) Data buffer Setting peripheral hardware data General register Performs operation and transfer between data memory and other data memory General Control section purpose port System register Program counter Data memory address LCD dot register Λ Controls CPU peripheral Display data is set \n circuits General output port Input Window register register port Input and output data is set Stack Stack operation Ŀ Output Operation port Decimal operation enabled п enabled Input/ output - Register file • port Set peripheral hardware conditions Set data via a window register Resetting Timer Interrupt

A

Concept of µPD17005

µPD17005

NEC

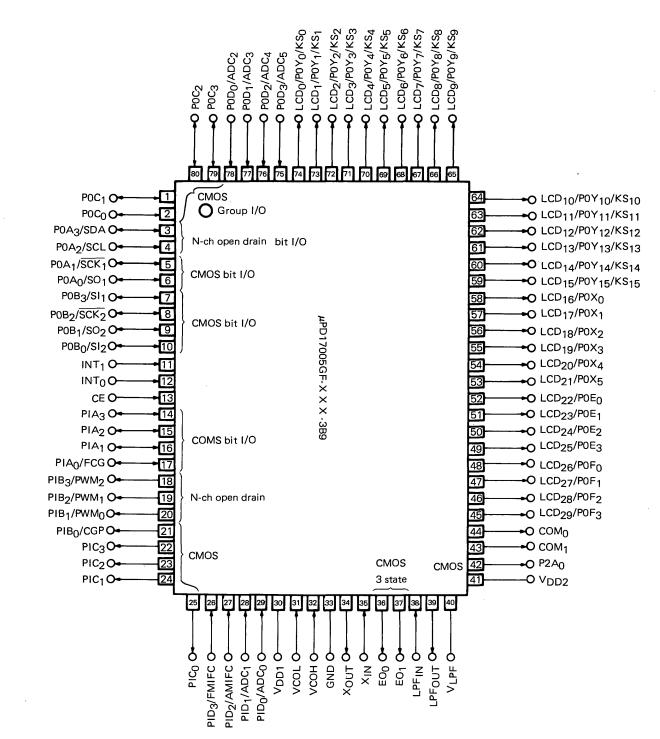

### PIN CONFIGURATION (Top View)

5

>

NEC

## CONTENTS

| 1. PIN | FUNCTIONS                                                         |

|--------|-------------------------------------------------------------------|

| 1.1    | EXPLANATION ON EACH PIN FUNCTION                                  |

| 1.2    | NOTES ON USING A GENERAL PURPOSE PORT                             |

| 1.3    | PIN EQUIVALENT CIRCUITS                                           |

|        |                                                                   |

| 2. BL( | OCK DIAGRAM                                                       |

| 3 PR(  | OGRAM MEMORY (ROM)                                                |

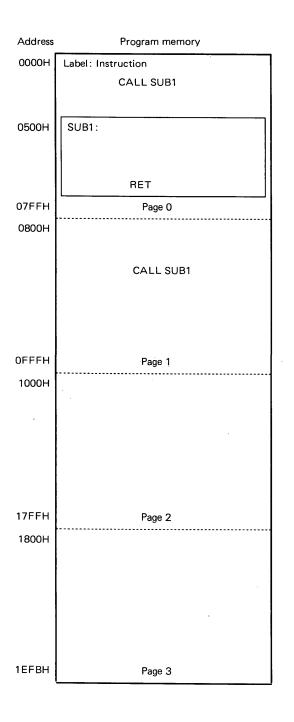

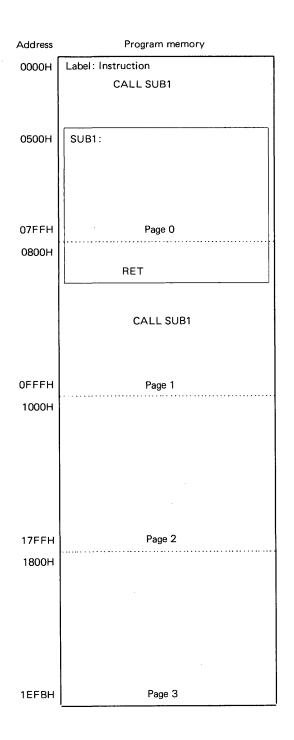

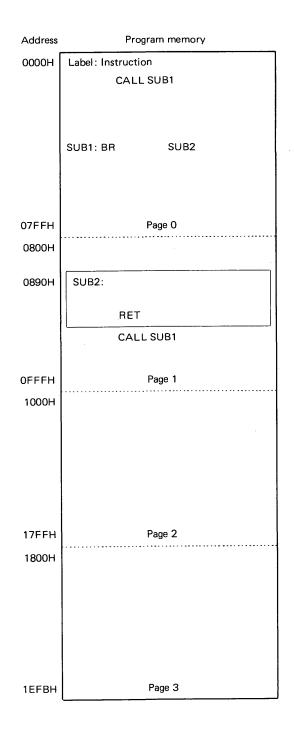

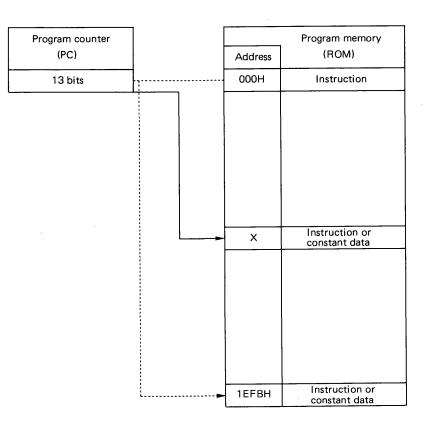

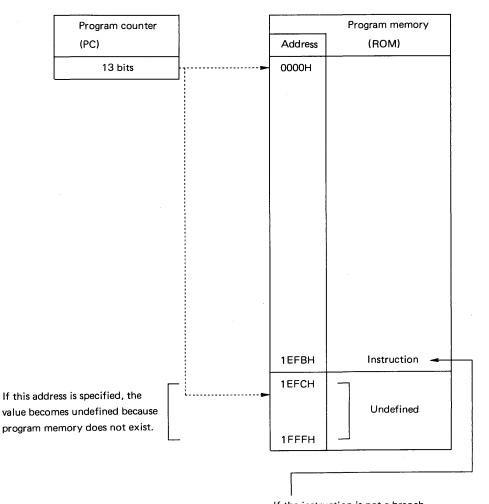

| 3.1    | STRUCTURE OF PROGRAM MEMORY                                       |

| 3.1    | PROGRAM MEMORY FUNCTIONS                                          |

| 3.3    | PROGRAM FLOW                                                      |

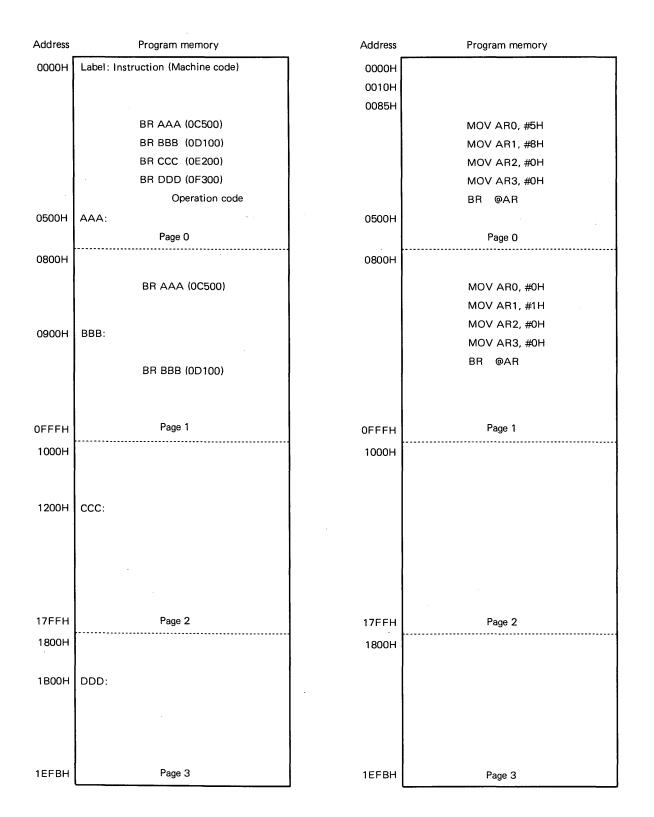

| 3.4    | PROGRAM BRANCHING                                                 |

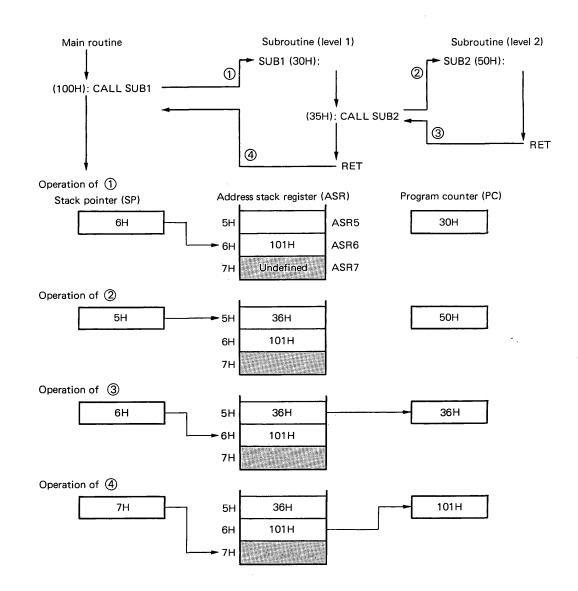

| 3.5    | SUBROUTINE                                                        |

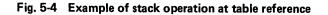

| 3.6    | TABLE REFERENCING         42                                      |

| 3.7    | NOTES ON USING A BRANCHING INSTRUCTION AND A SUBROUTINE CALL      |

| •      | INSTRUCTION                                                       |

|        | · · · · · · · · · · · · · · · · · · ·                             |

| 4. PR  | OGRAM COUNTER (PC)                                                |

| 4.1    | STRUCTURE ON A PROGRAM COUNTER                                    |

| 4.2    | FUNCTIONS OF A PROGRAM COUNTER                                    |

| 4.3    | NOTES ON PROGRAM COUNTER OPERATION                                |

|        |                                                                   |

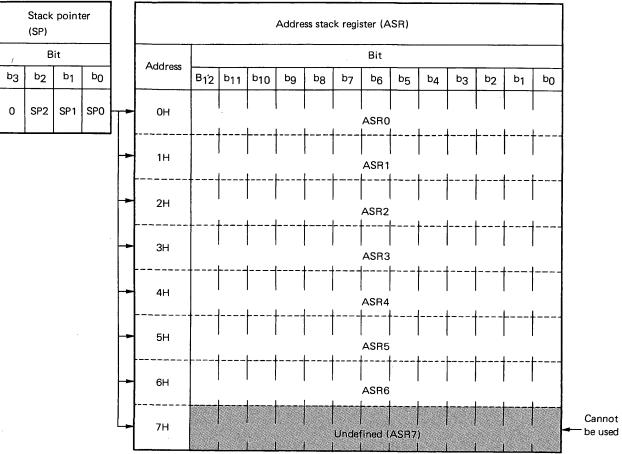

| 5. ST/ | АСК                                                               |

| 5.1    | STRUCTURE OF STACK                                                |

| 5.2    | FUNCTIONS OF A STACK                                              |

| 5.3    | STACK POINTER (SP)                                                |

| 5.4    | ADDRESS STACK REGISTER (ASR) 51                                   |

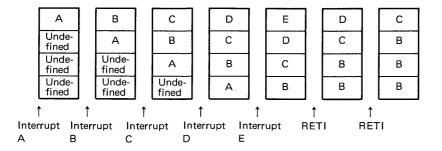

| 5.5    | INTERRUPT STACK REGISTER                                          |

| 5.6    | STACK OPERATION AT EXECUTION OF EACH STATEMENT (SUBROUTINE, TABLE |

|        | REFERENCE, AND INTERRUPT)                                         |

| 5.7    | STACK NESTING LEVEL, PUSH INSTRUCTION, AND POP INSTRUCTION 59     |

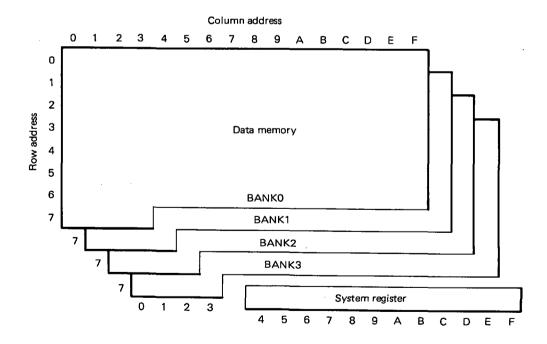

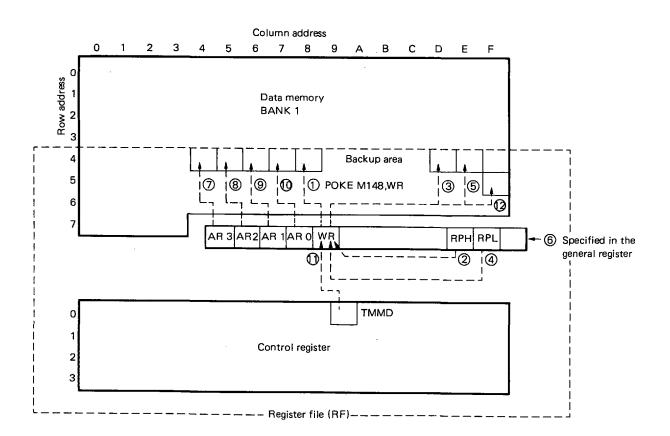

| 6. DA  | TA MEMORY (RAM)                                                   |

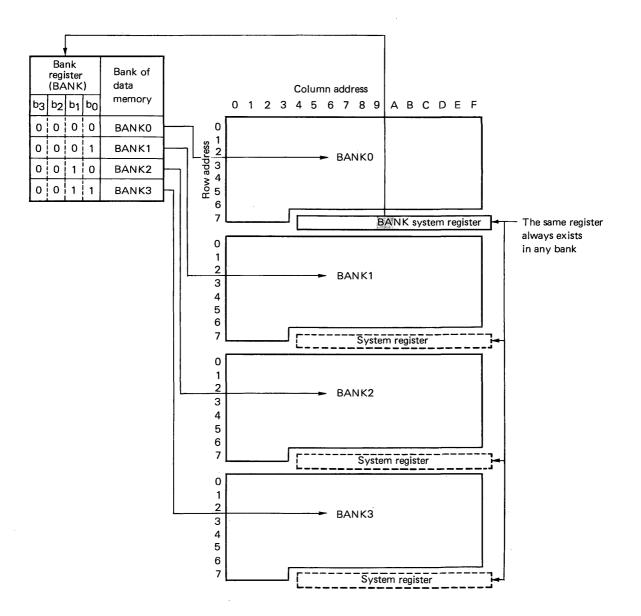

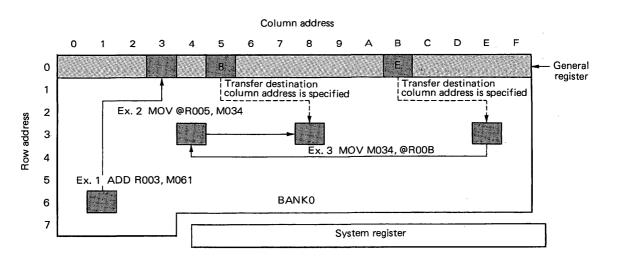

| 6.1    | STRUCTURE OF DATA MEMORY                                          |

| 6.2    | FUNCTIONS OF DATA MEMORY                                          |

| 6.3    | NOTES ON USING DATA MEMORY         70                             |

|        | · · · · · · · · · · · · · · · · · · ·                             |

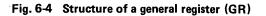

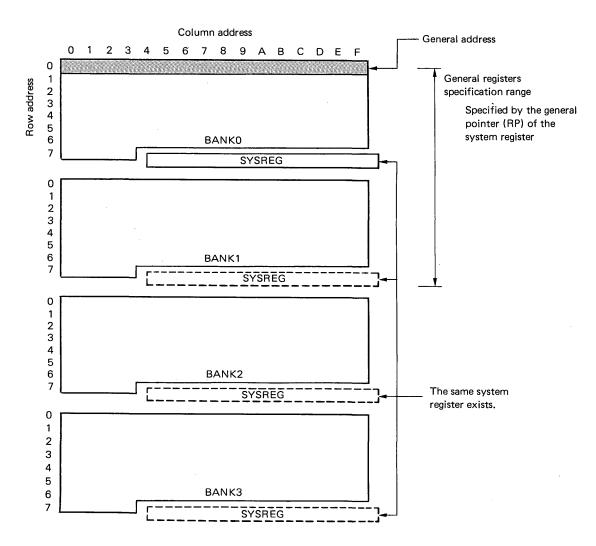

| 7. GE  | NERAL REGISTER (GR)                                               |

| 7.1    | STRUCTURE OF A GENERAL REGISTER                                   |

| 7.2    | FUNCTION OF A GENERAL REGISTER                                    |

| 7.3    | GENERAL REGISTER IN EACH INSTRUCTION AND DATA MEMORY ADDRESS      |

|        | GENERATION AND OPERATION                                          |

| 7.4    | NOTES ON USING A GENERAL REGISTER                                 |

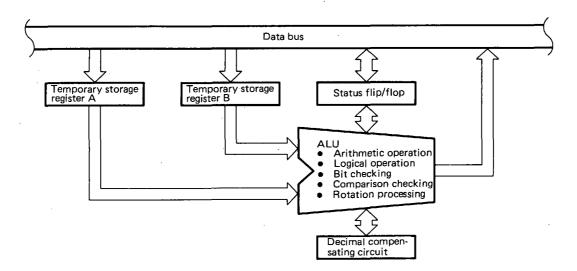

| 8. AL  | U (ARITHMETIC LOGIC UNIT) BLOCK                                     | 85  |

|--------|---------------------------------------------------------------------|-----|

| 8.1    | STRUCTURE OF AN ALU BLOCK                                           | 85  |

| 8.2    | FUNCTION OF AN ALU BLOCK                                            | 87  |

| 8.3    | ARITHMETIC OPERATION (ADDITION AND SUBTRACTION IN BINARY MODE OR    |     |

|        | DECIMAL MODE)                                                       | 93  |

| 8.4    | LOGICAL OPERATION                                                   | 105 |

| 8.5    | BIT CHECKING                                                        | 108 |

| 8.6    | COMPARISON CHECKING                                                 | 109 |

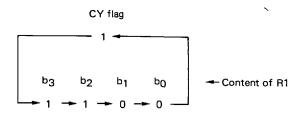

| 8.7    | ROTATION PROCESSING                                                 | 112 |

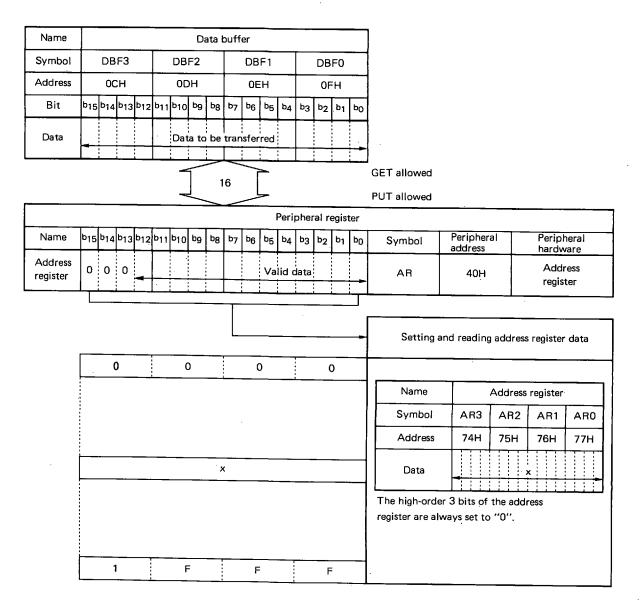

| 9. SYS | STEM REGISTER (SYSREG)                                              | 114 |

| 9.1    | STRUCTURE OF A SYSTEM REGISTER                                      |     |

| 9.2    | FUNCTION OF A SYSTEM REGISTER                                       |     |

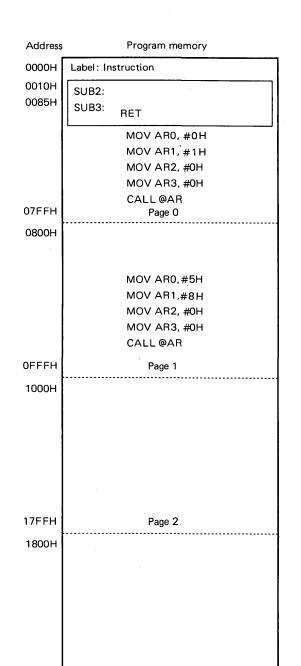

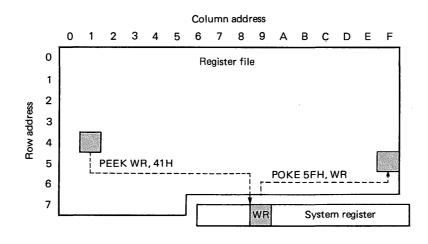

| 9.3    | ADDRESS REGISTER (AR)                                               |     |

| 9.4    | WINDOW REGISTER (WR)                                                |     |

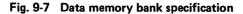

| 9.5    | BANK REGISTER (BANK)                                                |     |

| 9.6    | INDEX REGISTER (IX) AND DATA MEMORY ROW ADDRESS POINTER (MP: MEMORY |     |

|        | POINTER)                                                            | 125 |

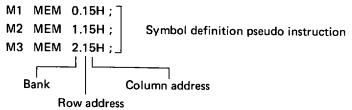

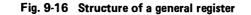

| 9.7    | GENERAL REGISTER POINTER (RP)                                       | 141 |

| 9.8    | PROGRAM STATUS WORD (PSWORD)                                        |     |

| 9.9    | NOTES ON USING SYSTEM REGISTERS                                     |     |

|        |                                                                     |     |

| 10. RE | EGISTER FILE (RF)                                                   |     |

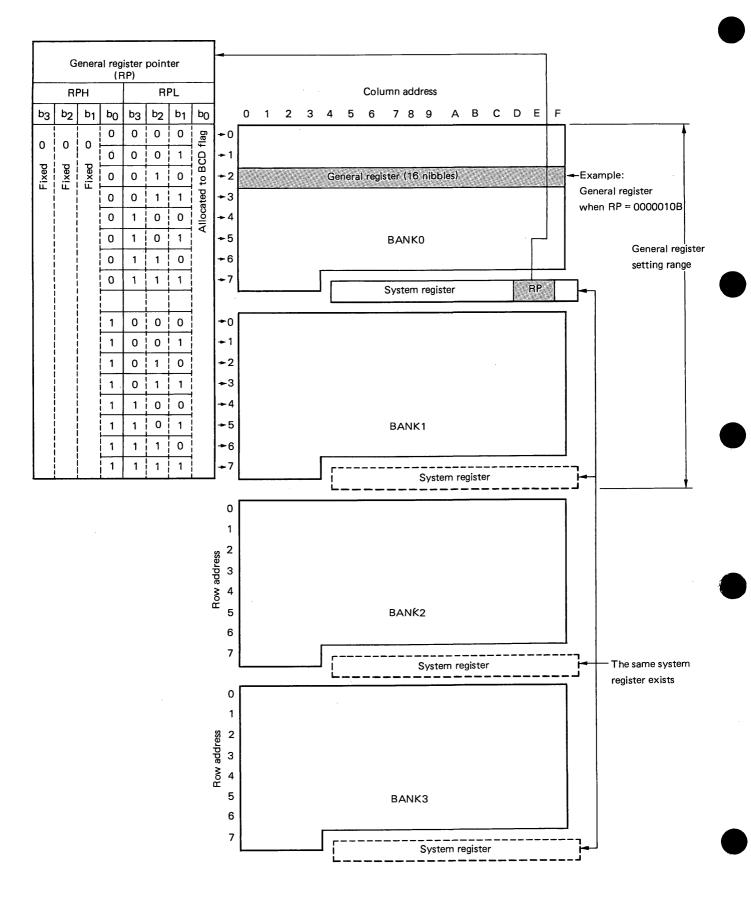

| 10.1   | STRUCTURE OF A REGISTER FILE                                        |     |

| 10.2   | FUNCTION OF A REGISTER FILE                                         |     |

| 10.3   | CONTROL REGISTER                                                    |     |

| 10.4   | NOTES ON USING A REGISTER FILE                                      | 160 |

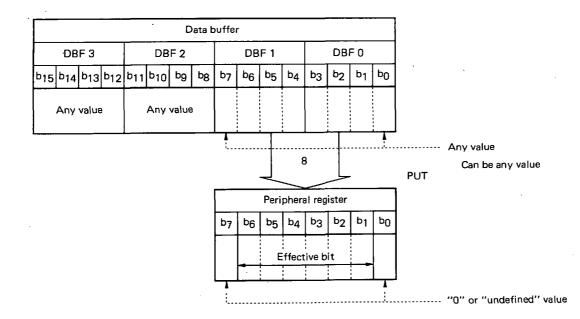

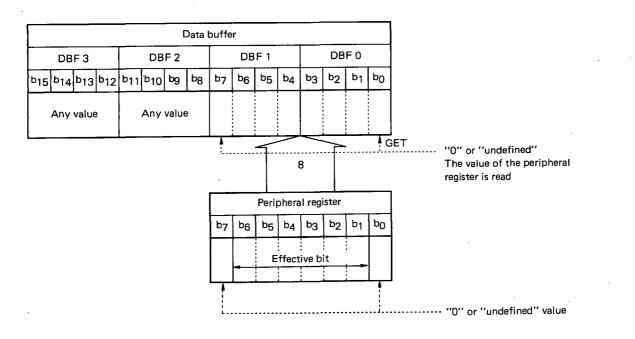

| 11. D/ | ATA BUFFER (DBF)                                                    | 163 |

| 11.1   | STRUCTURE OF A DATA BUFFER                                          | 163 |

| 11.2   | FUNCTION OF A DATA BUFFER                                           | 165 |

| 11.3   | DATA BUFFER AND TABLE REFERENCE                                     | 166 |

| 11.4   | BUFFER DATA AND PERIPHERAL HARDWARE                                 | 170 |

| 11.5   | NOTES ON USING DATA BUFFERS                                         | 175 |

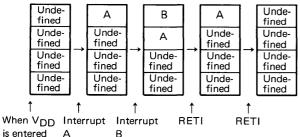

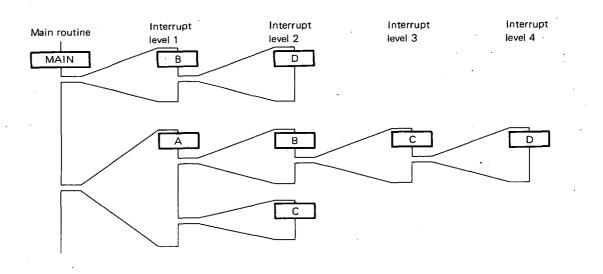

| 12. IN | ITERRUPT                                                            | 176 |

| 12.1   | STRUCTURE OF AN INTERRUPT BLOCK                                     |     |

| 12.2   |                                                                     |     |

| 12.3   |                                                                     |     |

| 12.4   | OPERATION AFTER ACCEPTANCE OF INTERRUPT                             |     |

| 12.4   | RETURN PROCESSING FROM AN INTERRUPT PROCESSING ROUTINE              |     |

| 12.5   |                                                                     |     |

| 12.0   | EXTERNAL (INT <sub>0</sub> PIN AND INT <sub>1</sub> PIN) INTERRUPT  |     |

| 12.7   | INTERNAL (TIMER, SERIAL INTERFACE 1, FREQUENCY COUNTER) INTERRUPT   |     |

| 12.0   | MULTIPLE INTERRUPT                                                  |     |

|        | ) NOTES ON USING INTERRUPT                                          |     |

|        |                                                                     |     |

| 13. T |                                                                           | 208         |

|-------|---------------------------------------------------------------------------|-------------|

| 13.1  | CONFIGURATION                                                             |             |

| 13.2  | FUNCTIONS                                                                 | 209         |

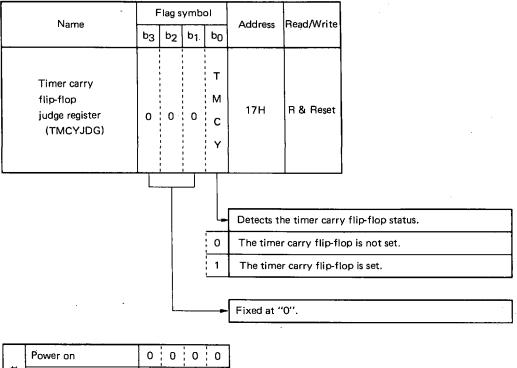

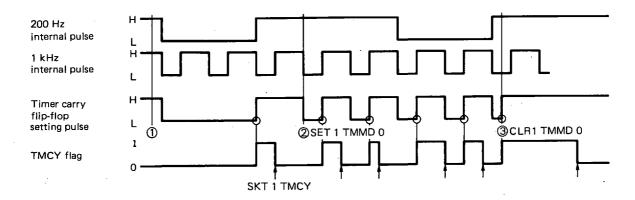

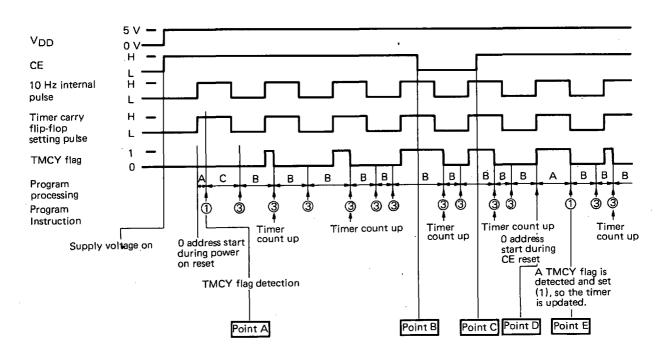

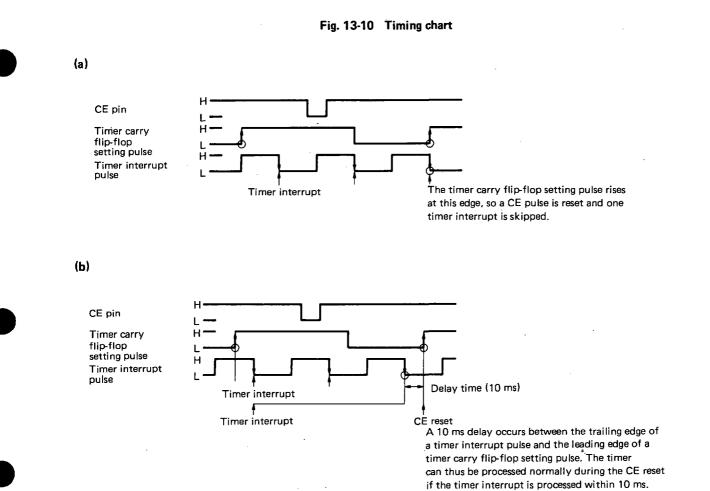

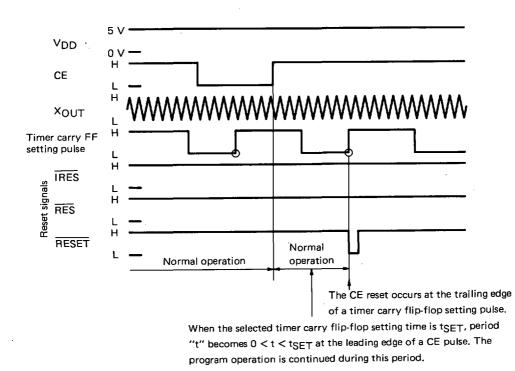

| 13.3  | TIMER CARRY FLIP-FLOP                                                     | 211         |

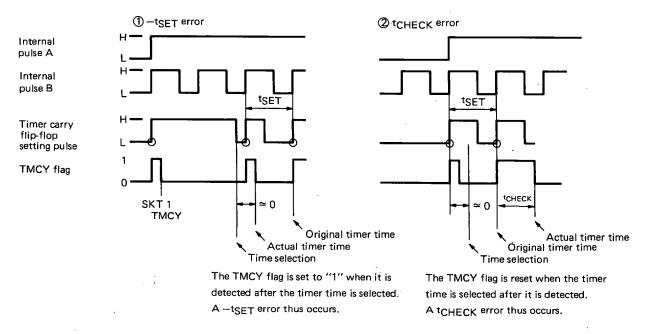

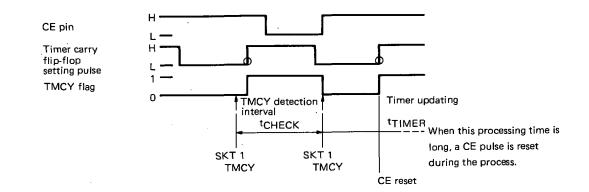

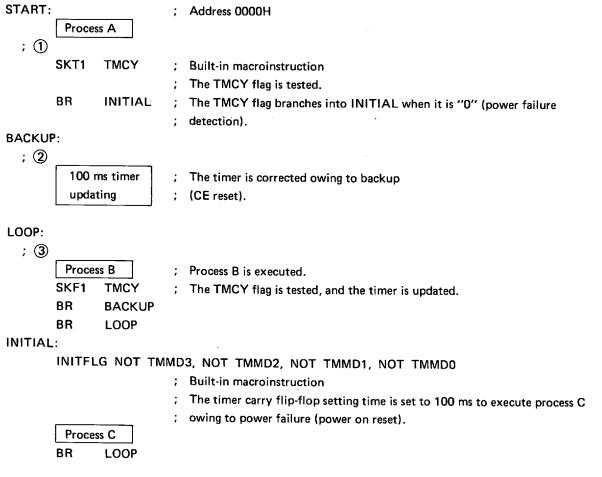

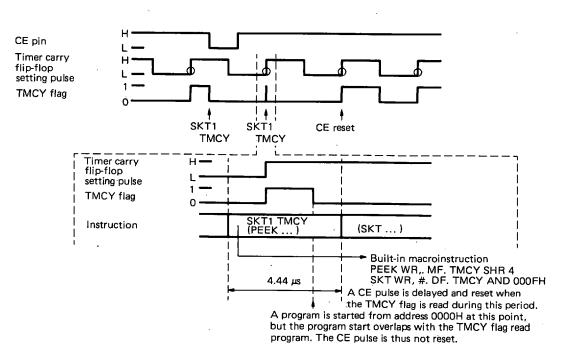

| 13.4  | CAUTIONS WHEN USING TIMER CARRY FLIP-FLOP                                 | 216         |

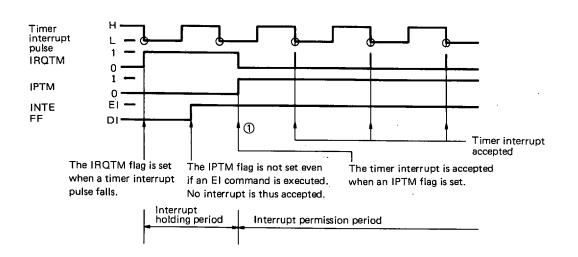

| 13.5  | TIMER INTERRUPT                                                           | 222         |

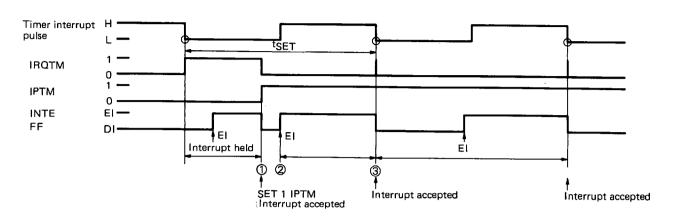

| 13.6  | CAUTIONS DURING TIMER INTERRUPT                                           | 226         |

|       |                                                                           |             |

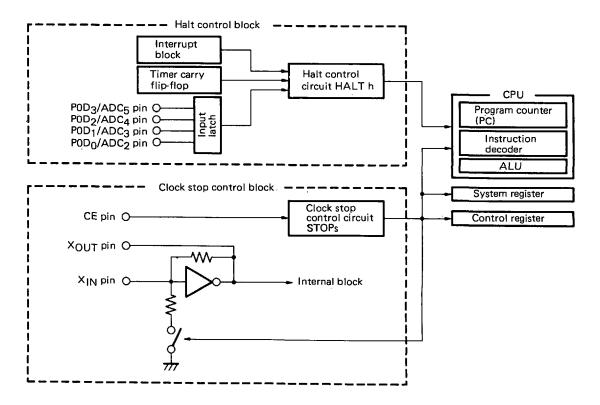

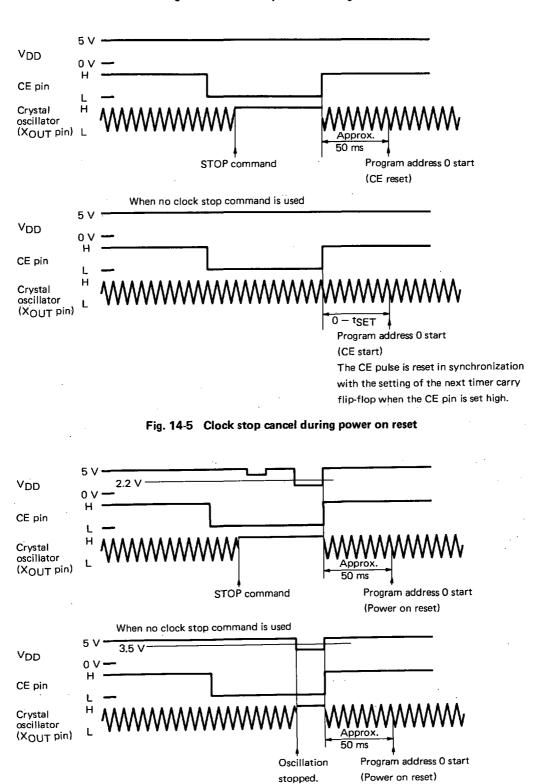

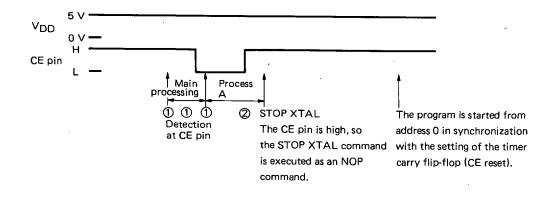

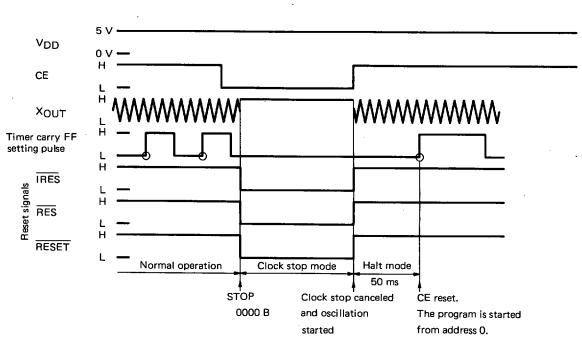

| 14. S | TANDBY                                                                    | 230         |

| 14.1  | STANDBY BLOCK CONFIGURATION                                               | 230         |

| 14.2  | STANDBY FUNCTIONS                                                         | 230         |

| 14.3  | DEVICE OPERATING MODE USING CE PIN                                        | 231         |

| 14.4  |                                                                           |             |

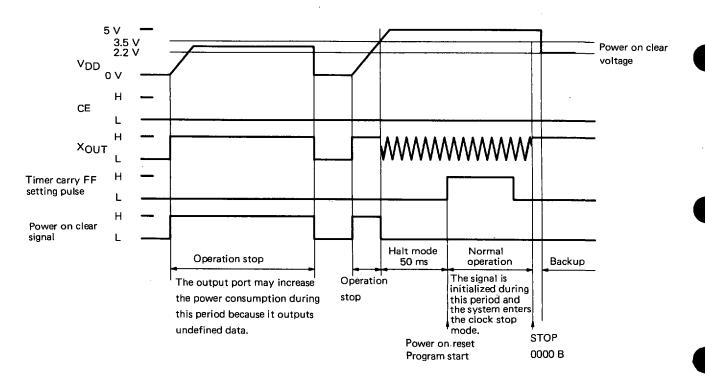

| 14.5  | CLOCK STOP FUNCTION · · · · · · · · · · · · · · · · · · ·                 | 242         |

| 14.6  | DEVICE OPERATION IN HALT AND CLOCK STOP MODES                             | 245         |

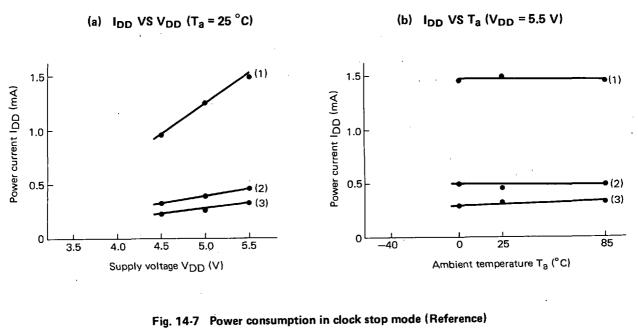

| 14.7  | POWER CONSUMPTION IN HALT AND CLOCK STOP MODES                            | 247         |

| 45 5  |                                                                           |             |

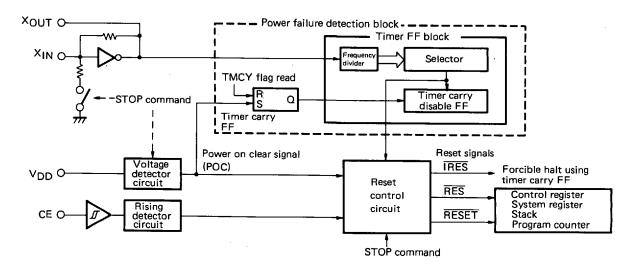

|       | ESET                                                                      |             |

| 15.1  | RESET BLOCK CONFIGURATION                                                 |             |

| 15.2  |                                                                           |             |

| 15.3  |                                                                           |             |

| 15.4  |                                                                           | 257         |

| 15.5  |                                                                           |             |

| 15.6  | POWER FAILURE DETECTION                                                   | 264         |

| 16 D  |                                                                           |             |

|       | LL FREQUENCY SYNTHESIZER                                                  |             |

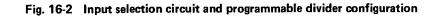

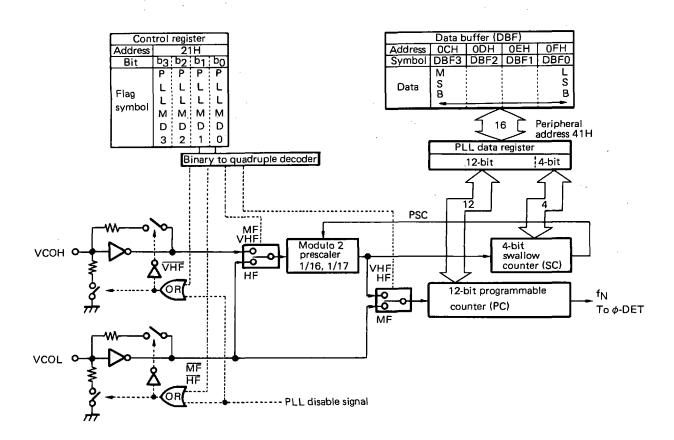

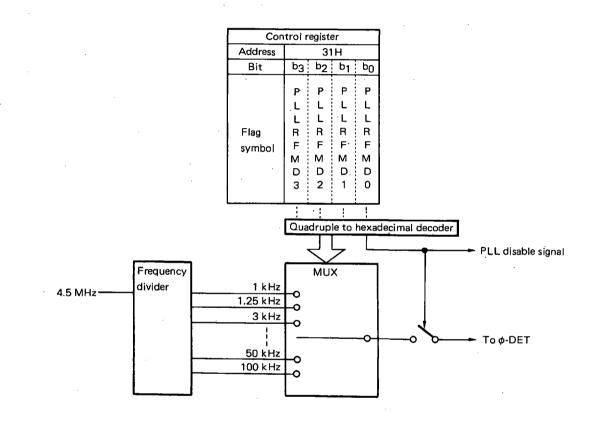

| 16.1  | PLL FREQUENCY SYNTHESIZER CONFIGURATION                                   |             |

| 16.2  |                                                                           |             |

| 16.3  |                                                                           |             |

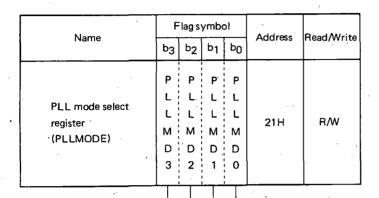

| 16.4  | REFERENCE FREQUENCY GENERATOR                                             |             |

| 16.5  | PHASE COMPARATOR ( $\phi$ -DET), CHARGE PUMP, AND UNLOCK DETECTOR CIRCUIT |             |

| 16.6  |                                                                           |             |

| 16.7  |                                                                           |             |

| 16.8  | USE OF PLL FREQUENCY SYNTHESIZER                                          |             |

| 16.9  | STATE DURING RESET                                                        | 289         |

| 17 G  |                                                                           |             |

| 17. G | ENERAL-PURPOSE PORT                                                       | <u>'90</u>  |

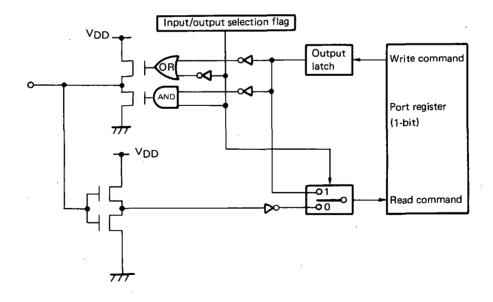

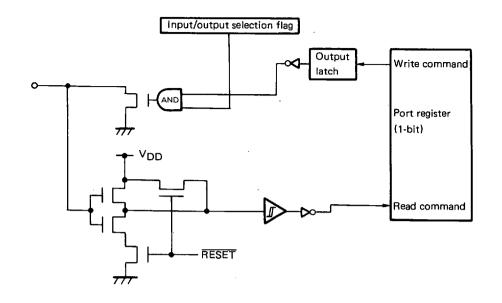

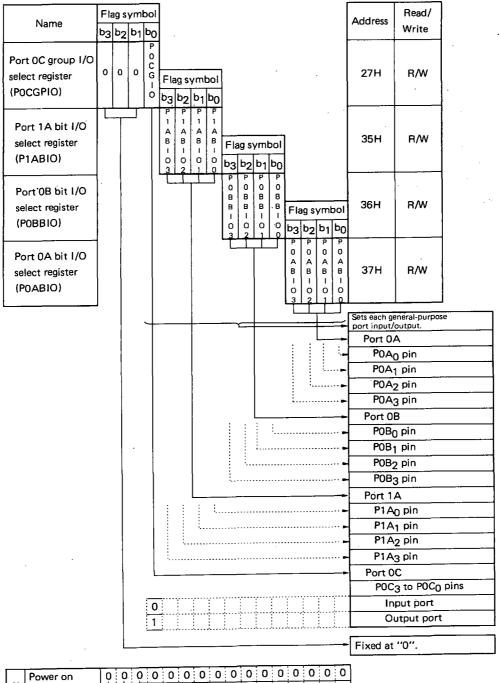

| 17.1  | GENERAL PURPOSE PORT CONFIGURATION AND FUNCTIONS                          |             |

| 17.2  |                                                                           | <u>?</u> 93 |

| 17.3  |                                                                           |             |

| 17.4  |                                                                           |             |

| 17.5  |                                                                           |             |

| 17.0  | GENERAL-PURPOSE OUTPUT PORTS (POE, POF, POX, and POY)                     | 306         |

8

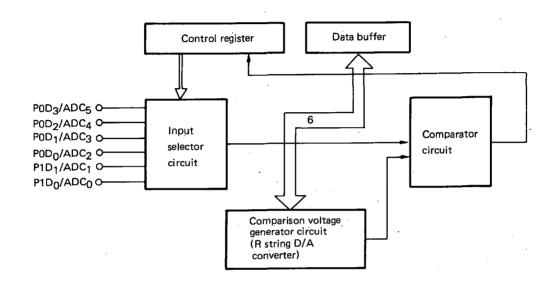

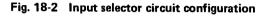

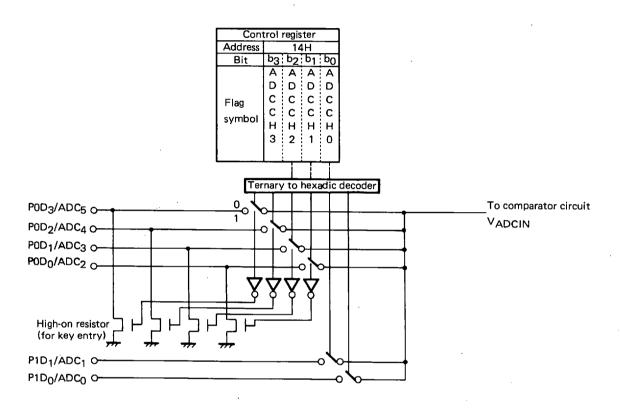

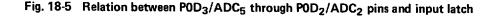

| 18. A/         | D CONVERTER (ADC)                                          |

|----------------|------------------------------------------------------------|

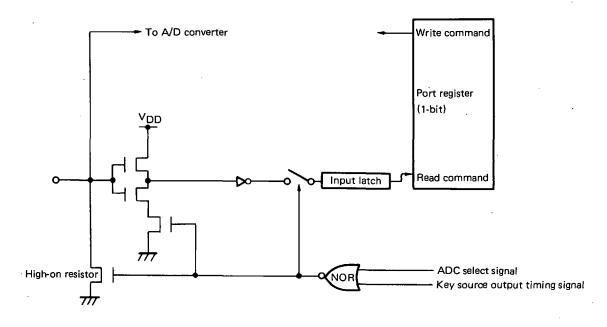

| 18.1           | A/D CONVERTER CONFIGURATION                                |

| 18.2           | A/D CONVERTER FUNCTIONS                                    |

| 18.3           | INPUT SELECTOR CIRCUIT                                     |

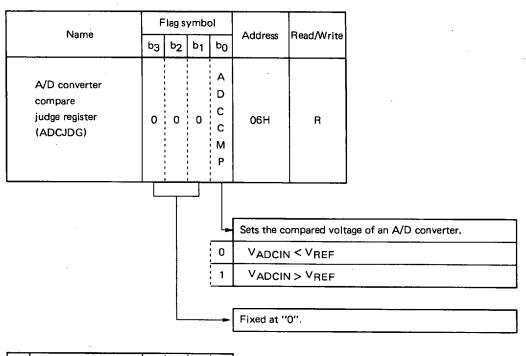

| 18.4           | COMPARISON VOLTAGE GENERATOR CIRCUIT                       |

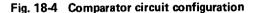

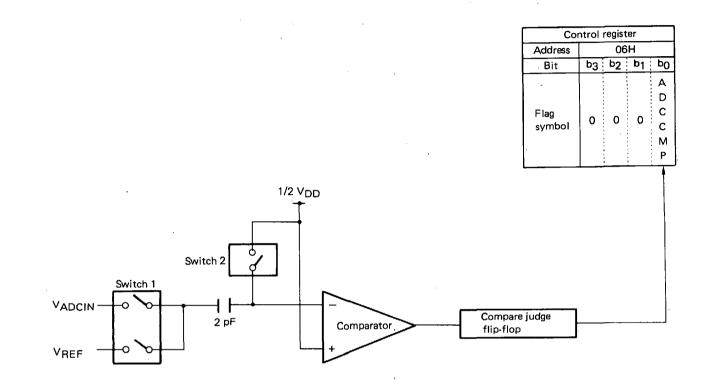

| 18.5           | COMPARATOR CIRCUIT                                         |

| 18.6           | A/D CONVERTER PERFORMANCE                                  |

| 18.7           | USE OF A/D CONVERTER                                       |

| 18.8           | CAUTIONS WHEN USING A/D CONVERTER                          |

| 18.9           | STATE DURING RESET                                         |

|                |                                                            |

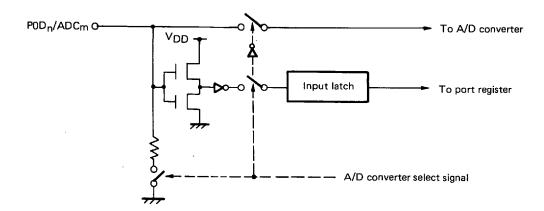

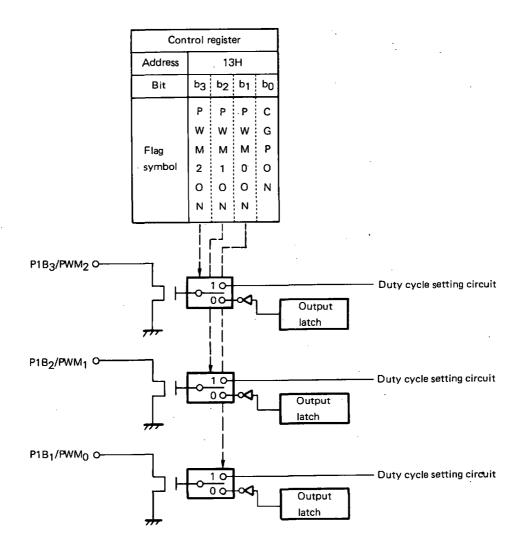

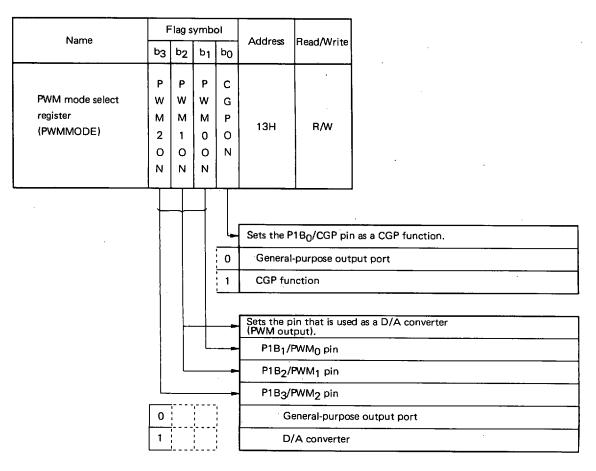

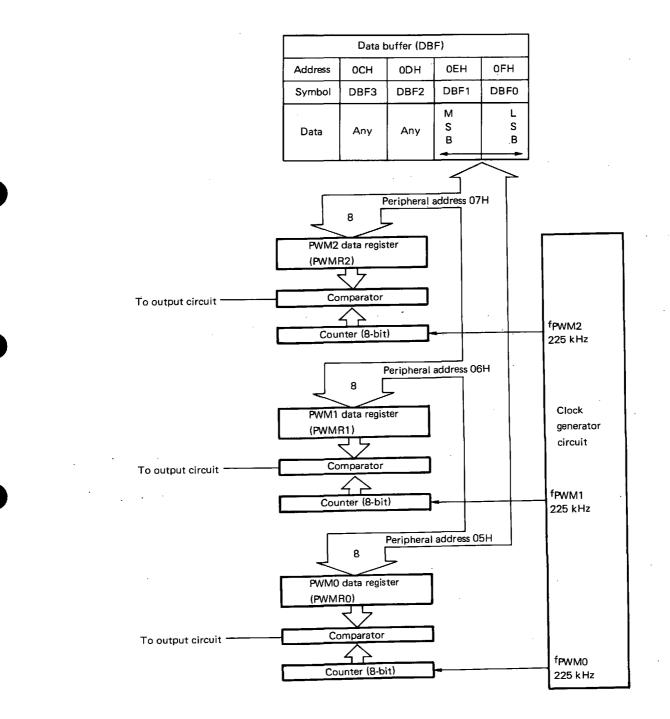

| <b>19.</b> D/. | A CONVERTER (DAC)                                          |

| 19.1           | D/A CONVERTER CONFIGURATION                                |

| 19.2           | D/A CONVERTER FUNCTIONS                                    |

| 19.3           | OUTPUT SELECTOR CIRCUITS                                   |

| 19.4           | DUTY CYCLE SETTING CIRCUITS AND CLOCK GENERATOR CIRCUIT    |

| 19.5           | STATE DURING RESET                                         |

|                |                                                            |

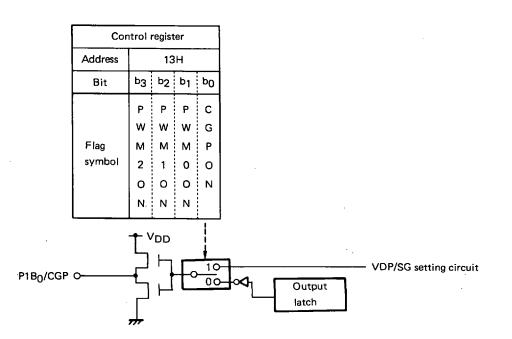

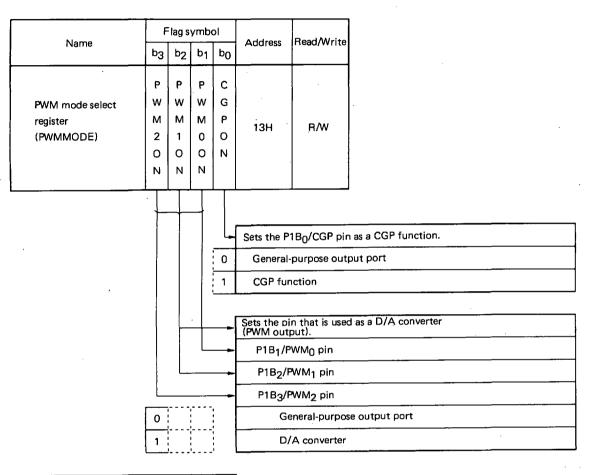

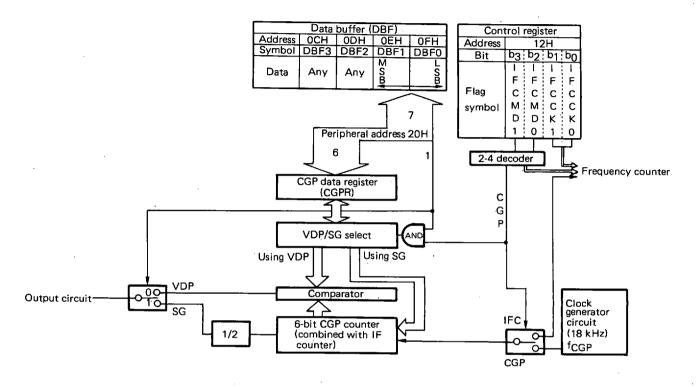

|                | OCK GENERATOR PORT (CGP)                                   |

| 20.1           | CLOCK GENERATOR PORT CONFIGURATION                         |

| 20.2           | CLOCK GENERATOR PORT FUNCTIONS                             |

| 20.3           | OUTPUT SELECTOR CIRCUIT                                    |

| 20.4           | VDP/SG SETTING CIRCUIT AND CLOCK GENERATOR CIRCUIT         |

| 20.5           | USE OF CLOCK GENERATOR PORT                                |

| 20.6           | STATE DURING RESET                                         |

| 20.7           | CAUTIONS WHEN USING CLOCK GENERATOR PORT                   |

| 04 OF          | RIAL INTERFACE                                             |

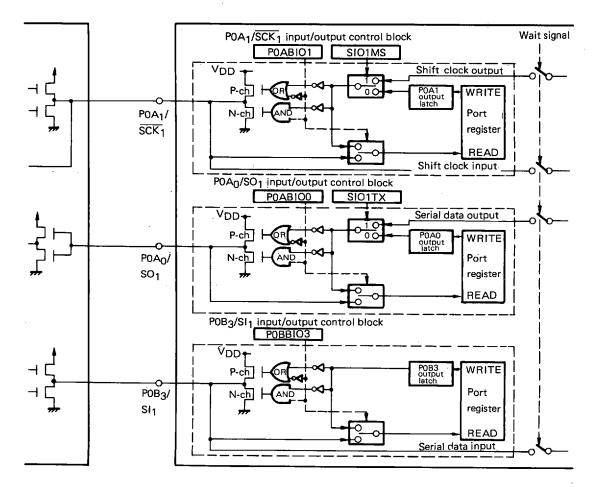

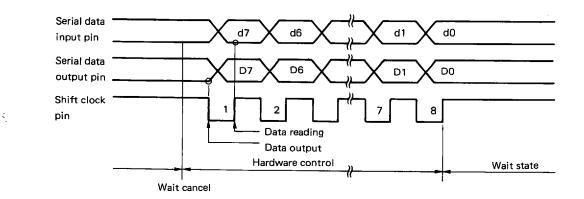

|                | SERIAL INTERFACE CONFIGURATION                             |

| 21.1           |                                                            |

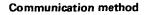

| 21.2           | OUTLINE OF FUNCTIONS OF SERIAL INTERFACE                   |

| 21.3           | CONFIGURATION OF SERIAL INTERFACE 1 (SIO1)                 |

| 21.4           | OUTLINE OF FUNCTIONS OF SERIAL INTERFACE 1                 |

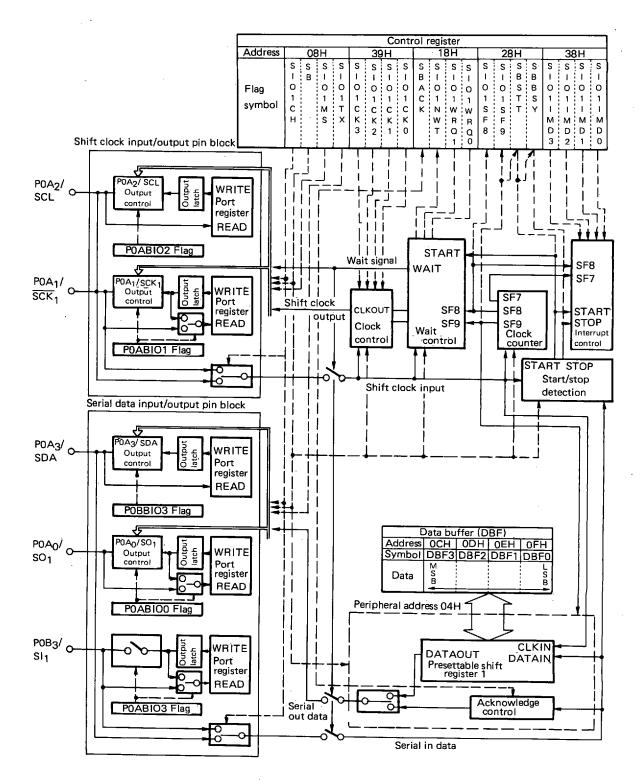

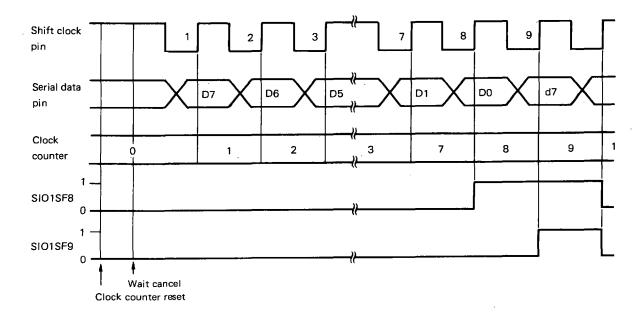

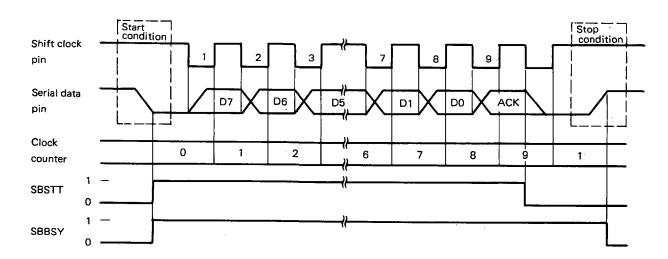

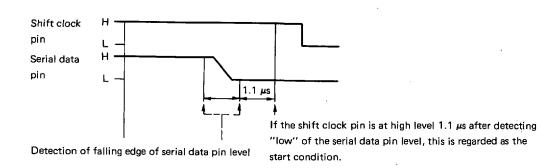

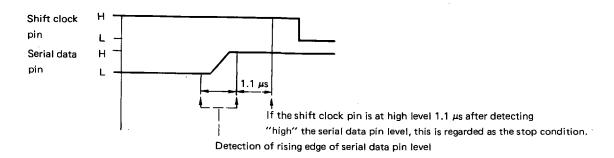

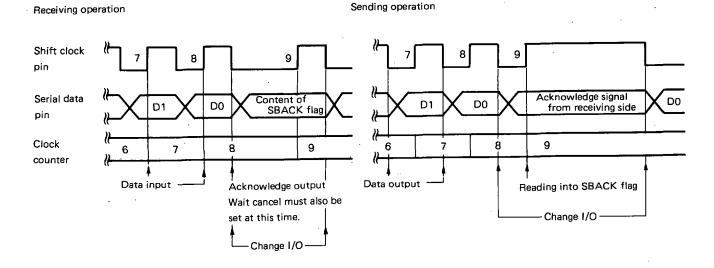

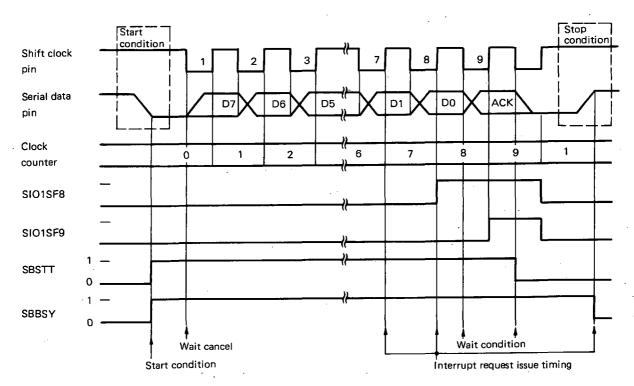

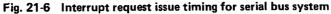

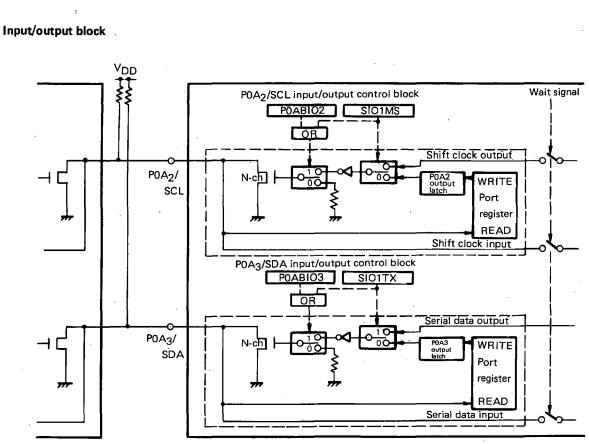

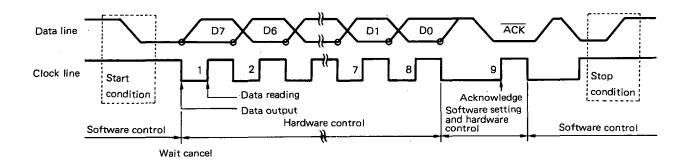

| 21.5           | SHIFT CLOCK AND SERIAL DATA INPUT/OUTPUT PIN CONTROL BLOCK |

| 21.6           |                                                            |

| 21.7           | CLOCK COUNTER AND START/STOP DETECTION BLOCK               |

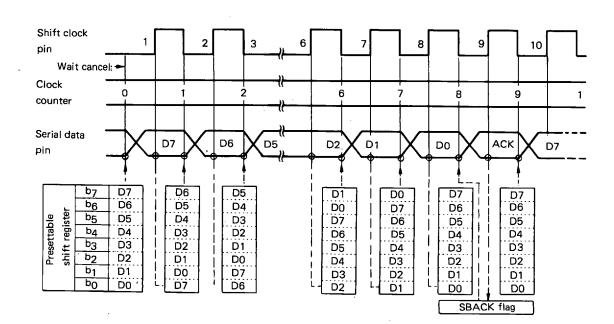

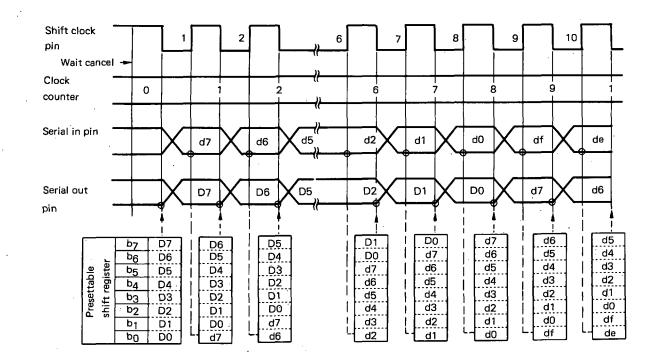

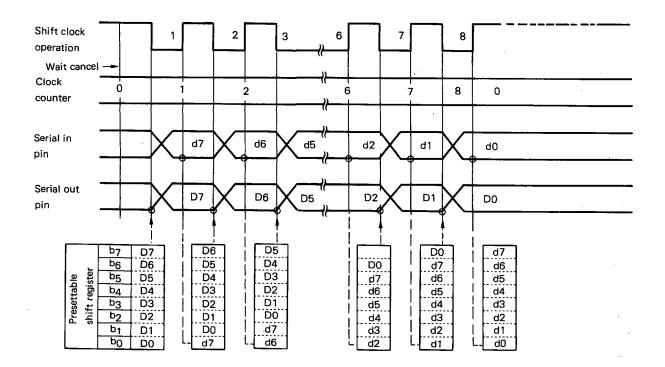

| 21.8           | PRESETTABLE SHIFT REGISTER (PSR)                           |

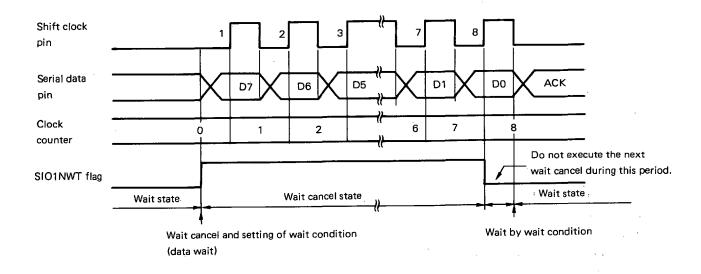

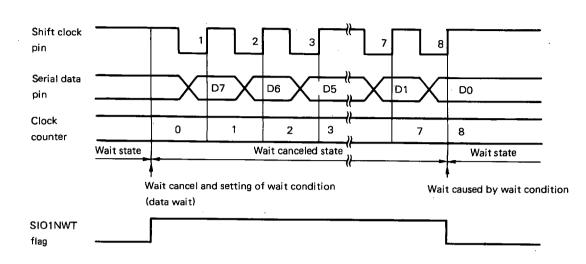

| 21.9           | WAIT BLOCK AND ACKNOWLEDGE BLOCK                           |

|                | INTERRUPT CONTROL BLOCK                                    |

|                | HOW TO USE SERIAL INTERFACE 1                              |

|                | SERIAL INTERFACE 1 RESET STATUS                            |

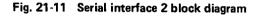

|                | CONFIGURATION OF SERIAL INTERFACE 2 (SIO2)                 |

| 21.14          | OUTLINE OF FUNCTION OF SERIAL INTERFACE 2                  |

NEC

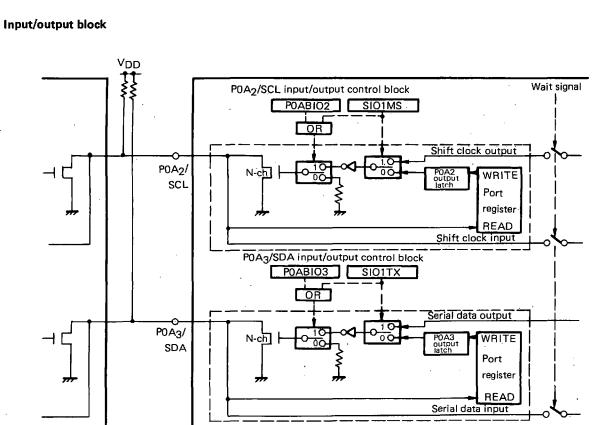

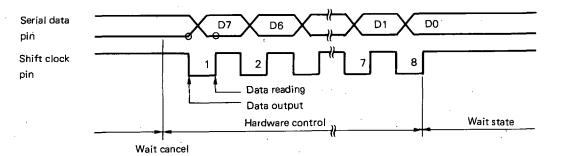

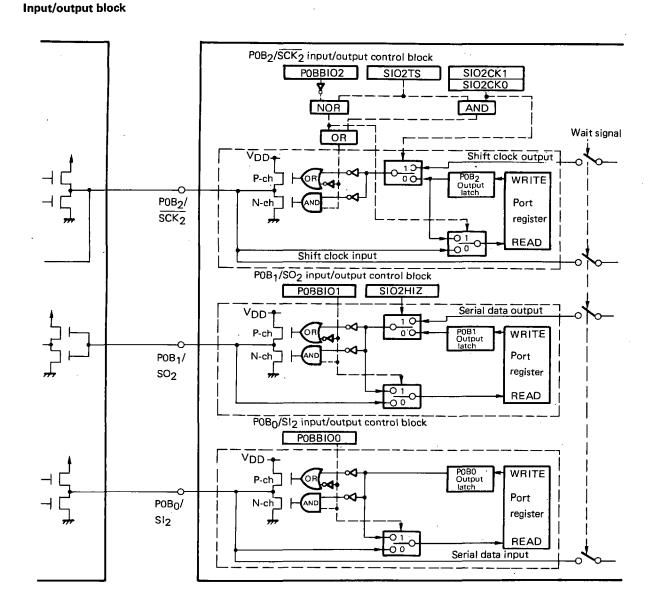

| 21.15          | SHIFT CLOCK AND SERIAL DATA INPUT/OUTPUT CONTROL BLOCK       |

|----------------|--------------------------------------------------------------|

| 21.16          | CLOCK GENERATION BLOCK                                       |

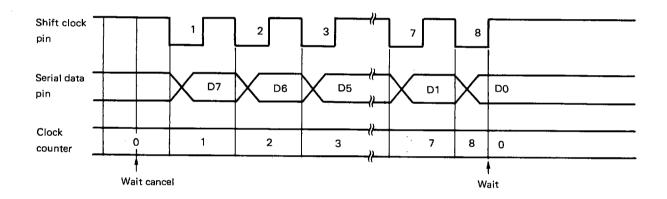

| 21.17          | CLOCK COUNTER                                                |

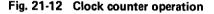

| 21.18          | PRESETTABLE SHIFT REGISTER (PSR2)                            |

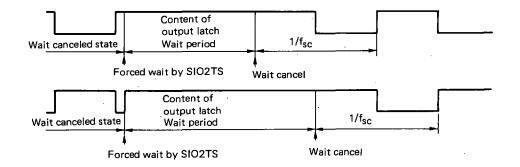

|                | WAIT BLOCK                                                   |

| 21.20          | USAGE OF SERIAL INTERFACE 2                                  |

| 21.21          | RESET STATUS OF SERIAL INTERFACE 2                           |

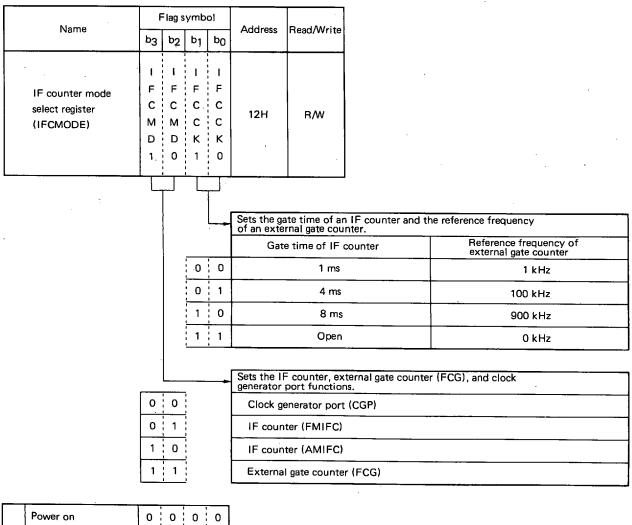

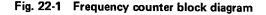

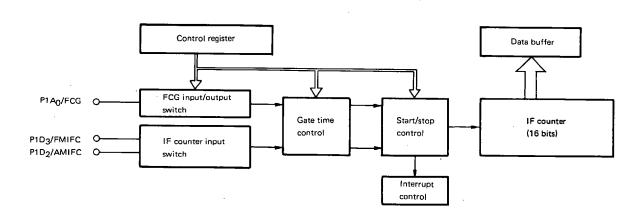

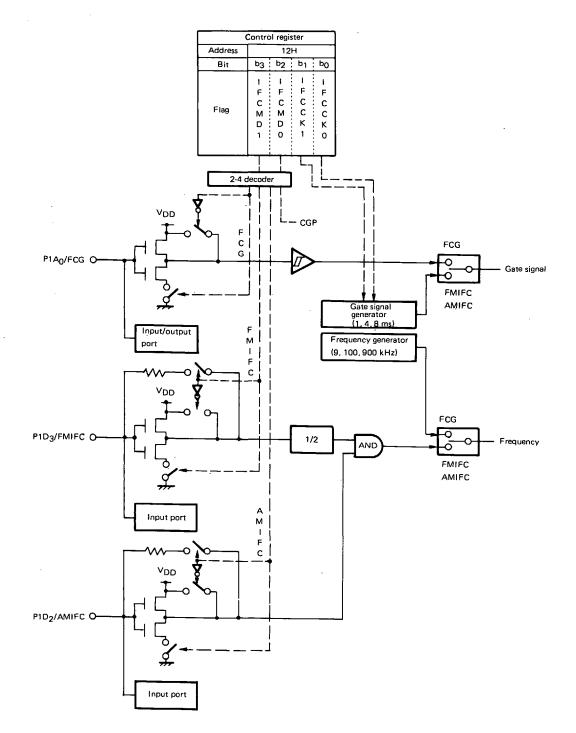

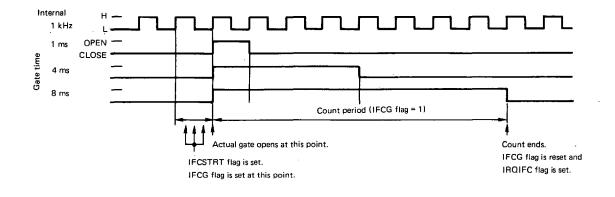

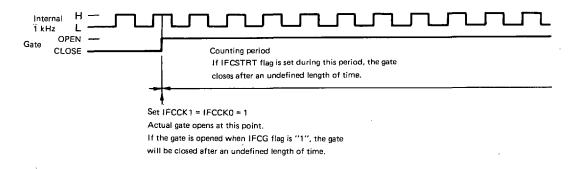

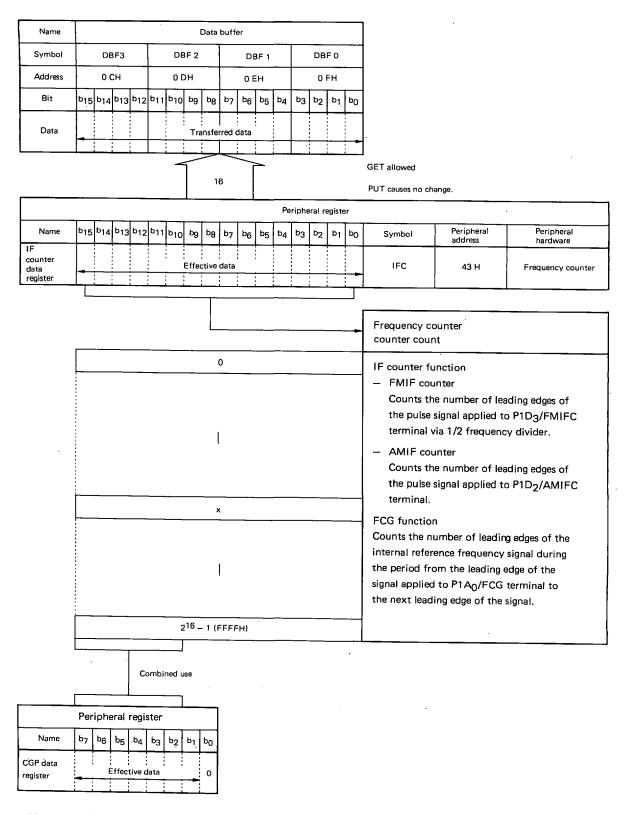

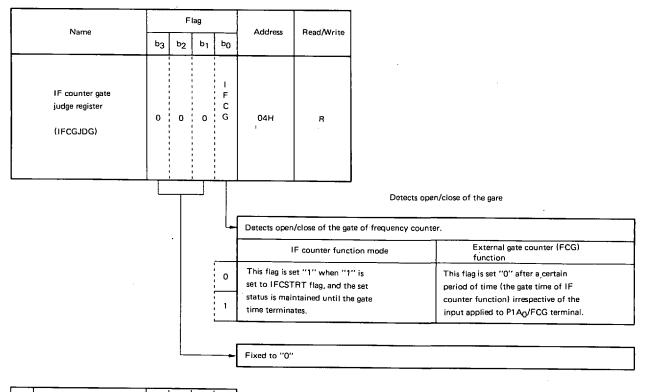

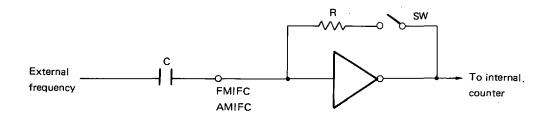

| 22. FR         | REQUENCY COUNTER (FC)                                        |

| 22.1           | CONFIGURATION OF FREQUENCY COUNTER                           |

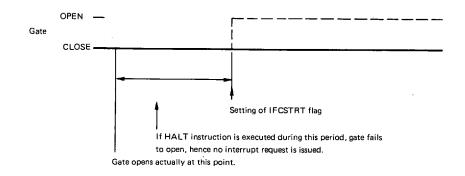

| 22.2           | OUTLINE OF FUNCTION OF FREQUENCY COUNTER                     |

| 22.3           | INPUT/OUTPUT SWITCH BLOCK AND GATE TIME CONTROL BLOCK        |

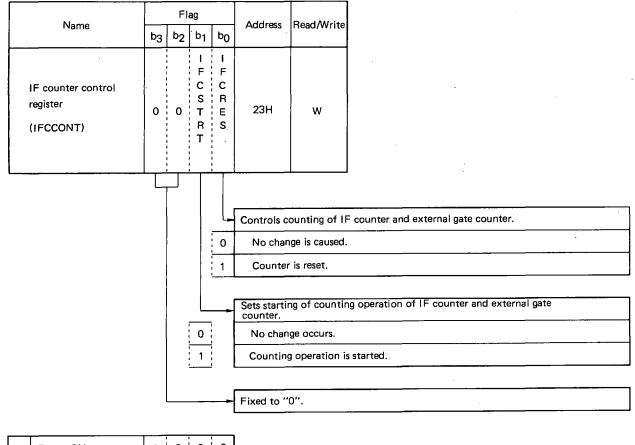

| 22.4           | START/STOP CONTROL BLOCK AND IF COUNTER                      |

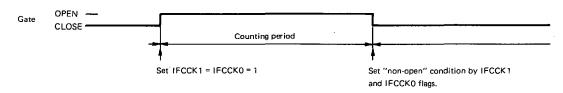

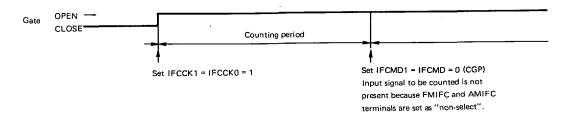

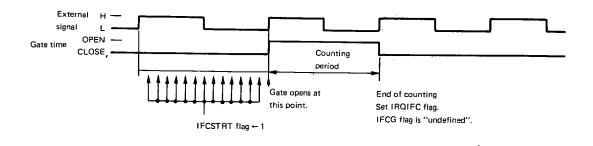

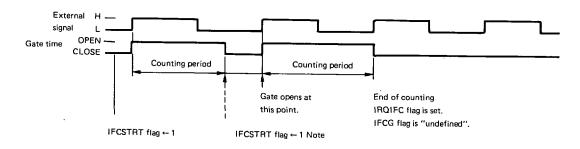

| 22.5           | USAGE OF IF COUNTER FUNCTION                                 |

| 22.6           | USAGE OF FCG FUNCTION                                        |

| 22.7           | RESET STATUS                                                 |

| 22.8           | PRECAUTIONS IN USING FREQUENCY COUNTER                       |

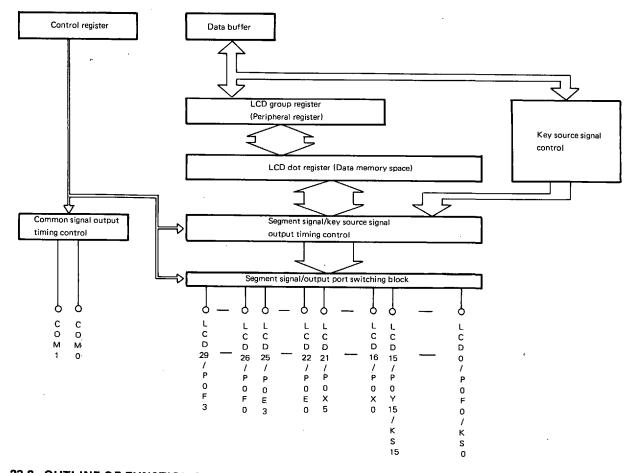

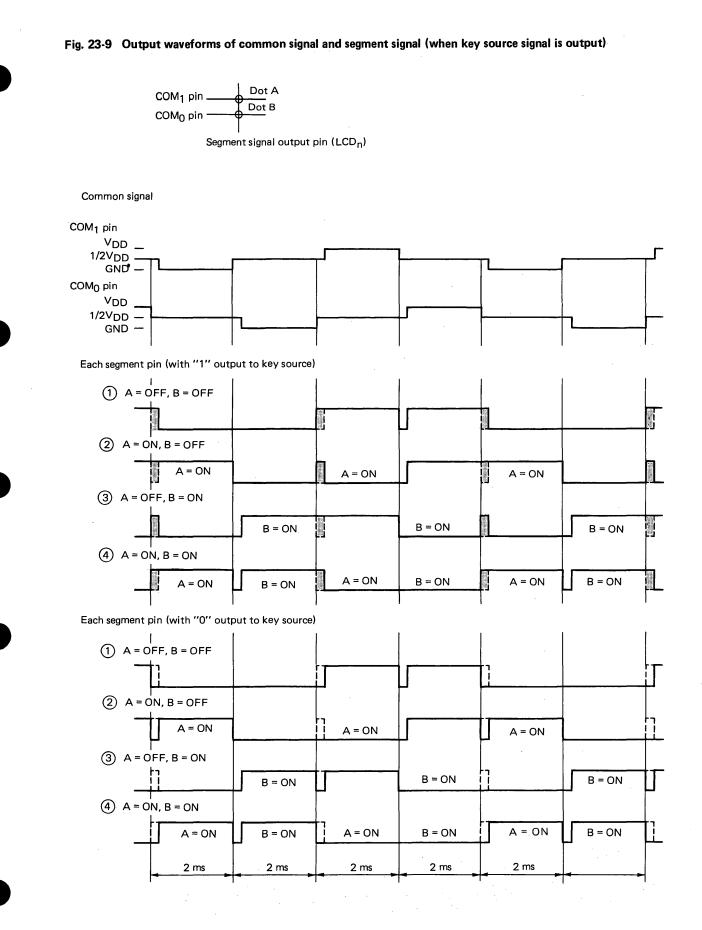

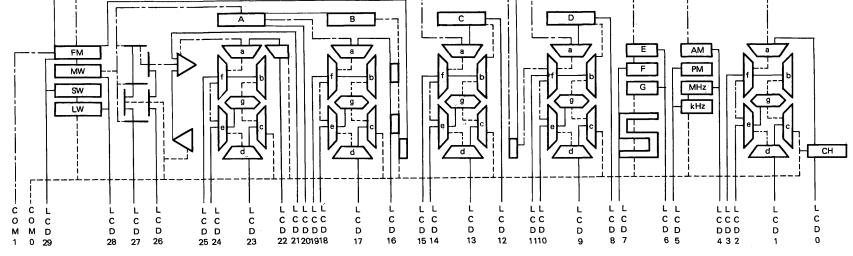

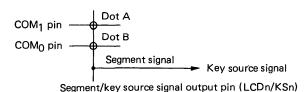

| 23. LC         | D CONTROLLER/DRIVER                                          |

| 23.1           | CONFIGURATION OF LCD CONTROLLER/DRIVER                       |

| 23.2           | OUTLINE OF FUNCTION OF LCD CONTROLLER/DRIVER                 |

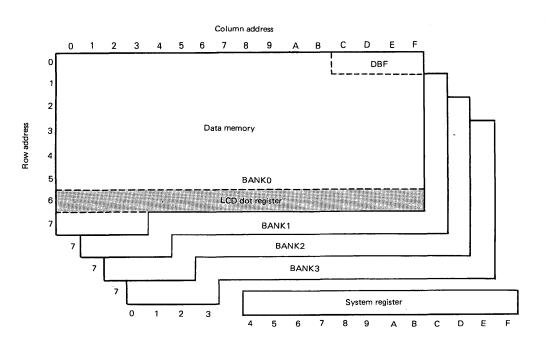

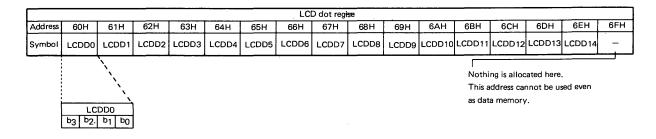

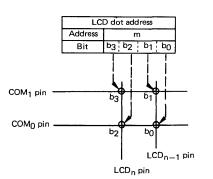

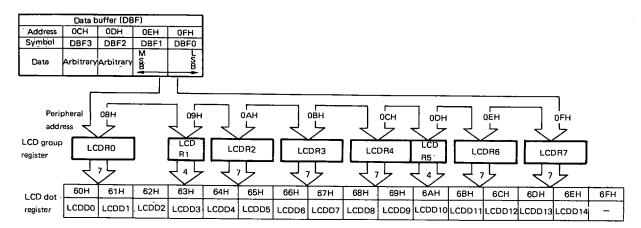

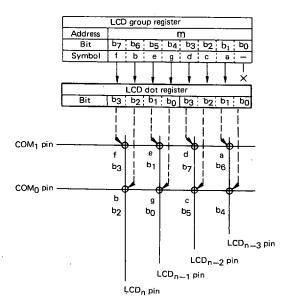

| 23.3           | LCD DOT REGISTER AND LCD GROUP REGISTER                      |

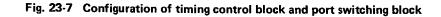

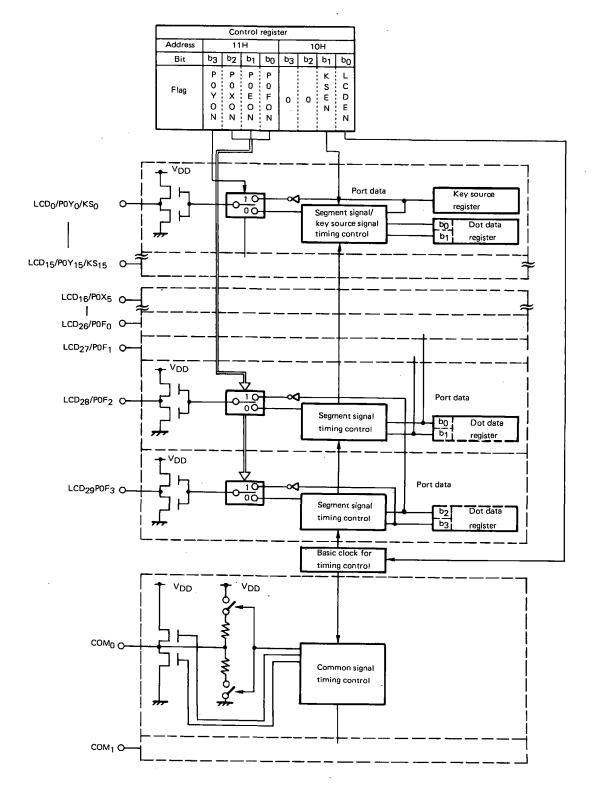

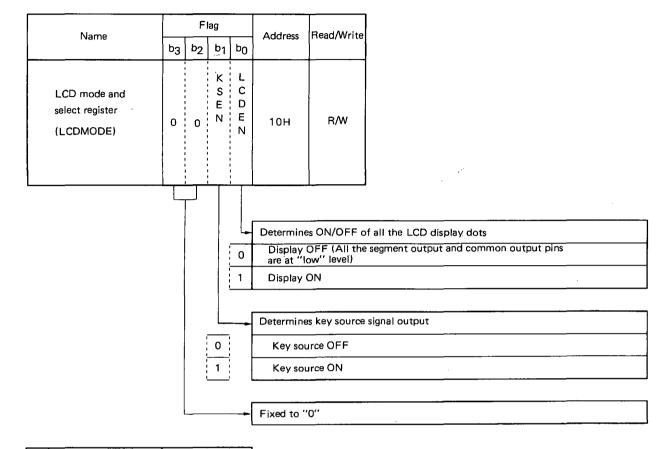

| 23.4           | OUTPUT TIMING CONTROL BLOCK AND SEGMENT/PORT SWITCHING BLOCK |

| 23.5           | USAGE OF LCD CONTROLLER/DRIVER                               |

| 23.6           | RESET STATUS                                                 |

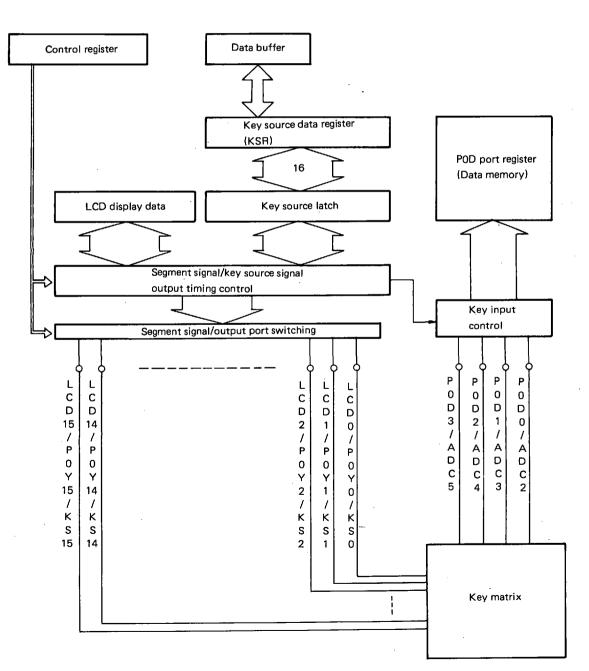

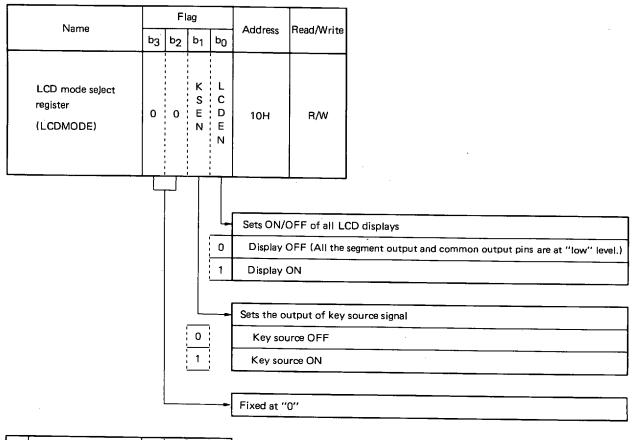

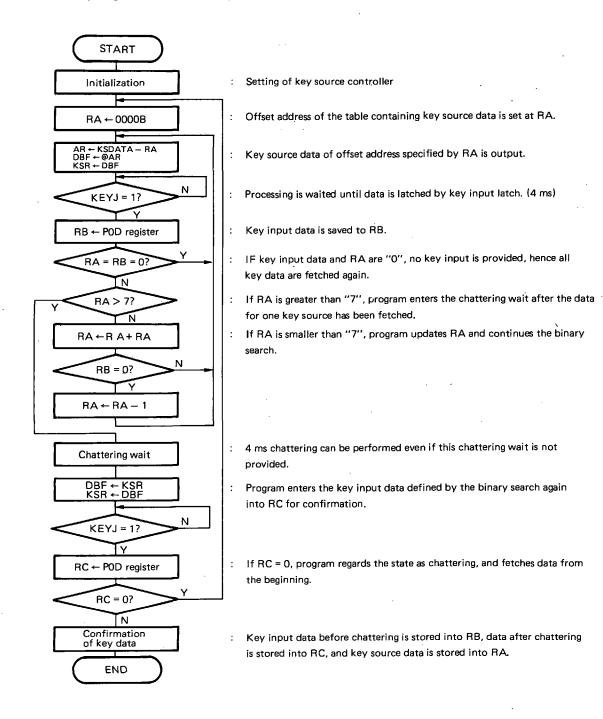

| 24. KE         | Y SOURCE CONTROLLER/DECODER                                  |

| 24.1           | CONFIGURATION OF KEY SOURCE CONTROLLER/DECODER               |

| 24.2           | OUTLINE OF FUNCTIONS OF KEY SOURCE CONTROLLER/DECODER        |

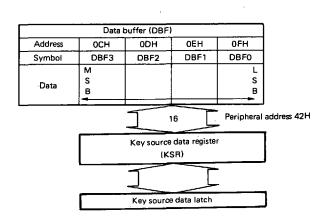

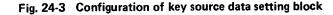

| 24.3           | KEY SOURCE DATA SETTING BLOCK                                |

| 24.4           | OUTPUT TIMING CONTROL BLOCK AND SEGMENT/PORT SWITCHING BLOCK |

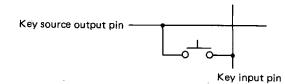

| 24.5           | KEY INPUT CONTROL BLOCK                                      |

| 24.6           | USAGE OF KEY SOURCE CONTROLLER/DECODER                       |

| 24.7           | RESET STATUS                                                 |

| <b>25.</b> μΡΙ | D17005 INSTRUCTIONS                                          |

| 25.1           | INSTRUCTION SET                                              |

| 25.2           | LIST OF INSTRUCTIONS                                         |

| 25.3           | ASSEMBLER (AS17K) BUILT-IN MACRO INSTRUCTION                 |

|        | PD17005 RESERVED WORDS                                                        |           |

|--------|-------------------------------------------------------------------------------|-----------|

| 26.1   | LIST OF RESERVED WORDS                                                        | <b>36</b> |

|        |                                                                               |           |

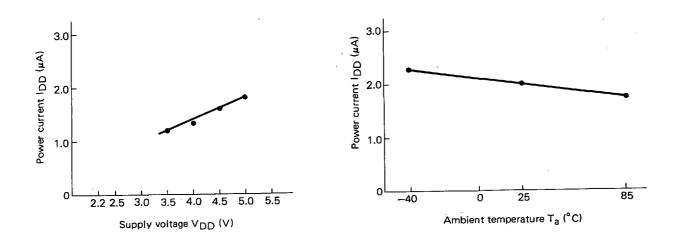

| 27. El | LECTRICAL CHARACTERISTICS                                                     | 14        |

| 27.1   | ABSOLUTE MAXIMUM RATINGS (UNLESS OTHERWISE SPECIFIED, $T_a = 25 \pm 2$ °C) 47 | 14        |

| 27.2   | RECOMMENDED OPERATING CONDITIONS                                              | /4        |

| 27.3   | DC CHARACTERISTICS (UNLESS OTHERWISE SPECIFIED, $T_a = -40$ to +85 °C,        |           |

|        | V <sub>DD</sub> = 4.5 to 5.5 V)                                               | /5        |

| 27.4   | AC CHARACTERISTICS (UNLESS OTHERWISE SPECIFIED, $T_a = -40$ to +85 °C,        |           |

|        | V <sub>DD</sub> = 4.5 to 5.5 V)                                               | 77        |

| 27.5   |                                                                               |           |

|        |                                                                               |           |

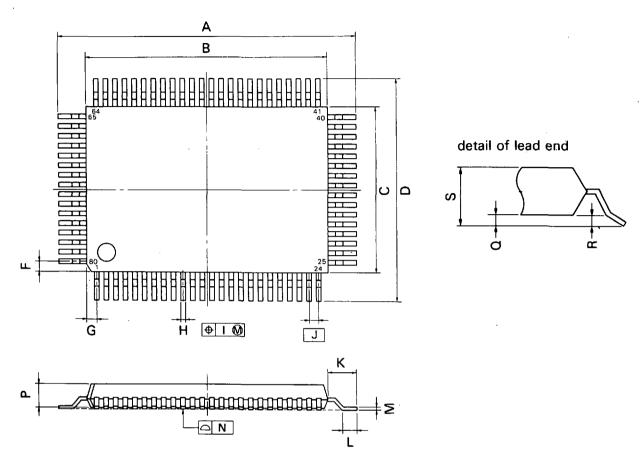

| 28. PA | ACKAGE DIMENSION                                                              | 78        |

|        |                                                                               |           |

| 29. RI | ECOMMENDED SOLDERING CONDITIONS4                                              | 79        |

|        |                                                                               |           |

| APPEN  | DIX A DIFFERENCES BETWEEN μPD17003A AND μPD1700544                            | 30        |

|        |                                                                               |           |

| APPEN  | DIX B DEVELOPMENT TOOL44                                                      | 31        |

## **1. PIN FUNCTIONS**

### 1.1 EXPLANATION ON EACH PIN FUNCTION

| Pin No.            | Pin symbol                                    | Input/<br>Output | Output<br>mode                                             | Pin name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------------------------------|------------------|------------------------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 79<br>80<br>1<br>2 | POC3<br>POC2<br>POC1<br>POC0                  | Input/<br>output | CMOS<br>Push-Pull                                          | Port OC  | <ul> <li>4-bit general purpose output port. Can be specified as an input or output port in 4-bit units (group I/O). Input/output is specified by the POCGPIO register (address 27H) of a register file.</li> <li>The POC register (address 27H of BANKO) of the port register is used for reading input data and setting output data.</li> <li>At Power On Reset, Clock Stop instruction execution, or CE Reset, these pins are specified as input ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

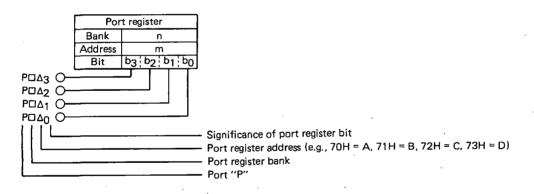

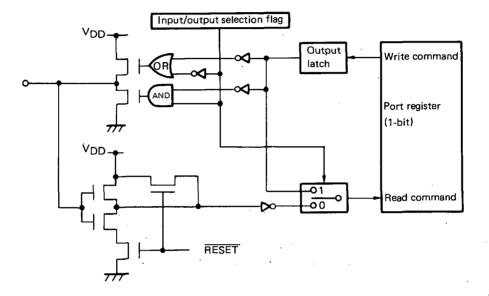

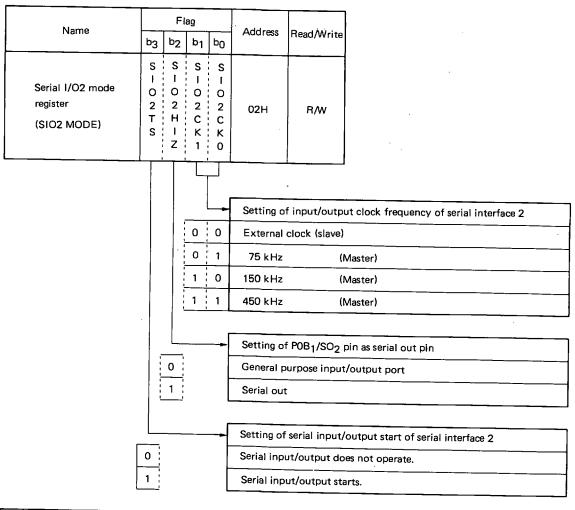

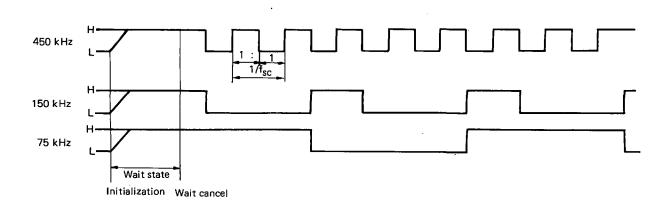

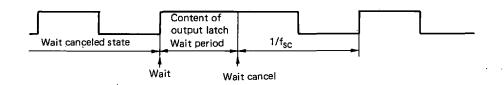

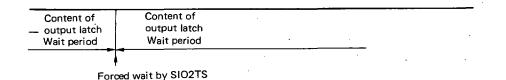

| 3<br>4<br>5<br>6   | P0A3/SDA<br>P0A2/SCL<br>P0A1/SCK1<br>P0A0/SO1 | Input/<br>Output | <pre>&gt; N-ch<br/>open drain<br/>CMOS<br/>Push-Pull</pre> | Port 0A  | <ul> <li>Used as a 4-bit general purpose input/output port and also for serial interface.</li> <li>A general purpose input/output port and serial interface is switched by the SIO1MODE register (address 08H) and SIO2MODE register of the register file.</li> <li>(1) When the pin is used as a 4-bit general purpose input/output port</li> <li>The port can be specified as an input or output port in bit units (bit I/O). Input or output is specified by the POABIO register (address 70H of BANKO) is used for reading input data and output data and setting the port register. Since POA<sub>3</sub>/SDA, and POA<sub>2</sub>/SCL pins are N-ch open drain output, pull-up resistance is required in the external section.</li> <li>(2) When the pins are used for serial interface 1 and serial interface 2 including Port OB (pin numbers 7 to 10). Serial interface 1 and serial interface 1 and serial interface 1 and serial interface 1 and one channel of a 3-wire system can be used for serial interface 1. Specify pins from the SIO1MODE register of 0.</li> <li>When using serial interface 1, specify pins from the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins from the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins from the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins from the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins from the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins for the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins for the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins for the SIO1MODE for serial interface 2.</li> <li>When using serial interface 1, specify pins listed below.</li> </ul> |

| Pin No.           | Pin symbol                                    | Input/<br>Output | Output<br>mode    | Pin name                                                                                                                    |                                                                                               | Function                                                                                                                                                                                               | ,                                                                                                                                                                         |                                                                                                        |

|-------------------|-----------------------------------------------|------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                   |                                               |                  |                   |                                                                                                                             | Pin name                                                                                      | Function                                                                                                                                                                                               |                                                                                                                                                                           | ating<br>ode                                                                                           |

|                   |                                               |                  |                   |                                                                                                                             | P0A3/SDA                                                                                      | Data<br>input/<br>output                                                                                                                                                                               | 2-                                                                                                                                                                        |                                                                                                        |

|                   |                                               |                  |                   |                                                                                                                             | POA <sub>2</sub> /SCL input/<br>output                                                        | wire                                                                                                                                                                                                   | Serial                                                                                                                                                                    |                                                                                                        |

|                   |                                               |                  |                   | POA1/SCK1                                                                                                                   | Clock<br>input/<br>output                                                                     |                                                                                                                                                                                                        | inter-<br>face 1                                                                                                                                                          |                                                                                                        |

|                   |                                               |                  |                   |                                                                                                                             | P0A0/SO1                                                                                      | Data<br>output                                                                                                                                                                                         | 3-<br>wire                                                                                                                                                                |                                                                                                        |

| 3                 | P0A3/SDA                                      | Input            | } <sup>N-ch</sup> |                                                                                                                             | POB3/SI1                                                                                      | Data<br>input                                                                                                                                                                                          |                                                                                                                                                                           |                                                                                                        |

| 4<br>5<br>6       | POA1/SCK1 COMS                                | Output           | COMS              | Port 0A                                                                                                                     | POB <sub>2</sub> /SCK <sub>2</sub>                                                            | Clock<br>input/<br>output                                                                                                                                                                              | - 3-<br>wire                                                                                                                                                              | Serial<br>inter-<br>face 2                                                                             |

|                   |                                               |                  |                   |                                                                                                                             | POB <sub>1</sub> /SO <sub>2</sub>                                                             | Data<br>output                                                                                                                                                                                         |                                                                                                                                                                           |                                                                                                        |

|                   |                                               |                  |                   |                                                                                                                             | POB <sub>0</sub> /SI <sub>2</sub>                                                             | Data<br>input                                                                                                                                                                                          |                                                                                                                                                                           |                                                                                                        |

|                   |                                               |                  |                   | Since pins POA<br>open drain, Pull<br>externally.<br>At Power On R<br>execution, and<br>are specified as<br>input/output po | ce is req<br>Stop inst<br>I of thes                                                           | uired<br>ruction<br>e pins                                                                                                                                                                             |                                                                                                                                                                           |                                                                                                        |

| 7<br>8<br>9<br>10 | P0B3/SI1<br>P0B2/SCK2<br>P0B1/SO2<br>P0B0/SI2 | Input<br>Output  | CMOS<br>Push-pull | Port 0B                                                                                                                     | The pins c<br>output po<br>Input or o<br>POBBIO re<br>register file<br>The POB re<br>BANKO) o | or serial inte<br>E register (ad<br>ister (addres<br>used for swi<br>purpose inpu<br>or vice versa<br>g the pins as<br>put/output<br>an be specifi<br>rts in bit uni<br>utput is spec<br>gister (addre | erface<br>ddress 08<br>ss 02H) of<br>tching th<br>ut/outpu<br><b>4-bit ge</b><br><b>ports</b><br>ded as inj<br>ts (bit 1/<br>cified by<br>ess 35H)<br>ess 35H)<br>ess 71H | BH) or<br>of the<br>ne func-<br>t port to<br>neral<br>out or<br>O).<br>the<br>of the<br>of<br>used for |

| Pin No.           | Pin symbol                                    | Input/<br>Output | Output<br>mode    | Pin name  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-----------------------------------------------|------------------|-------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>8<br>9<br>10 | P0B3/SI1<br>P0B2/SCK2<br>P0B1/SO2<br>P0B0/SI2 | Input<br>Output  | CMOS<br>Push-pull | Port 0B   | <ul> <li>(2) When the pins are used for serial interface</li> <li>Two types of serial interface can be used including Port OA (addresses 3 to 6), serial interface 1 and serial interface 2. See the explanation on Port OA for the function of each pin.</li> <li>At Power On Reset, Clock Stop instruction execution, and CE Reset, all of these pins are specified as input ports of general purpose input/output ports.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

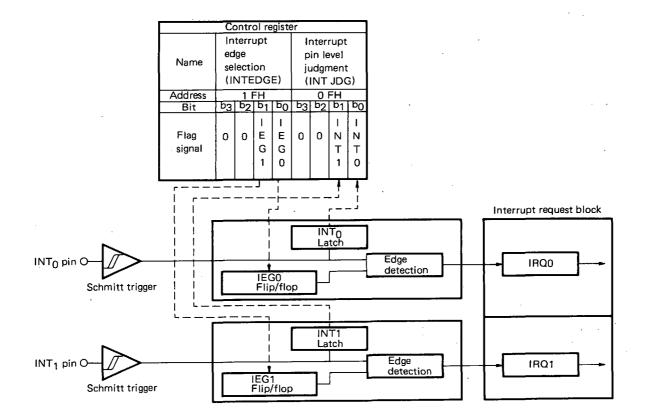

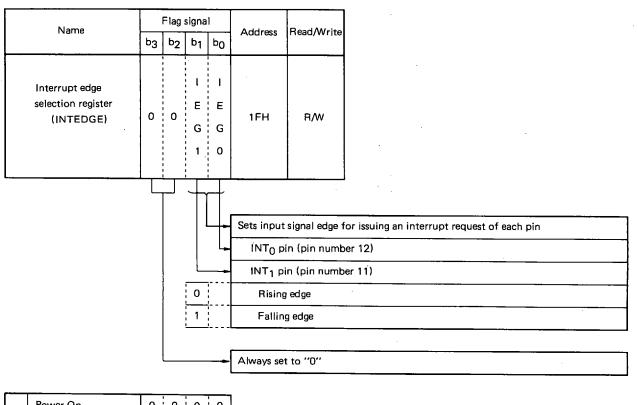

| 11<br>12          | INT1<br>INTO                                  | Input            |                   | Interrupt | External interrupt request input pin.<br>An interrupt request is issued from the input<br>signal rising edge or falling edge of the input<br>signal added to the pin. A rising edge and a<br>falling edge can be specified by the INTEDGE<br>register (address 1FH) of the register file using<br>INT <sub>0</sub> pin and INT <sub>1</sub> pin independently.<br>Even if an interrupt request is issued, interrupt<br>cannot be accepted unless it is permitted<br>(maskable interrupt).<br>Types of interrupt permission include permis-<br>sion of all the interrupts by the El instruction<br>and permission of the interrupt of each INT <sub>0</sub><br>pin and INT <sub>1</sub> pin. Permission of interrupt for<br>each pin is specified by the INTPM2 register<br>(address 2FH) of the register file.<br>When interrupt is permitted and when an<br>interrupt request is issued, the interrupt is<br>accepted. When interrupt is accepted. When<br>interrupt is accepted, control of the program<br>is passed to address 0005H in the case of<br>interrupt by the INT <sub>0</sub> pin and address 0004H<br>in the case of interrupt by the INT <sub>1</sub> pin.<br>When interrupts for both INT <sub>0</sub> pin and INT <sub>1</sub><br>pin are allowed and when interrupts for both<br>pins are issued, priority is given to the<br>interrupt by INT <sub>0</sub> pin.<br>Even if an interrupt is not permitted, the<br>issuing of an interrupt request can be checked<br>using the INTREQ2 register (address 3FH) of<br>the register file. When an interrupt function<br>is not used, the input level of each pin can be<br>detected by the INTJDG register (address<br>OFH) of the register file, and the pin can be<br>used as a general purpose input port.<br>At Power On Reset, Clock Stop Instruction<br>execution, or CE Reset, the interrupt permis-<br>sion and interrupt requests are reset. |

| Pin No. | Pin symbol | Input/<br>Output | Output<br>mode | Pin name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|------------|------------------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

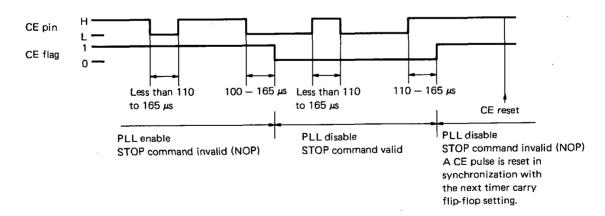

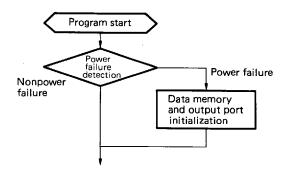

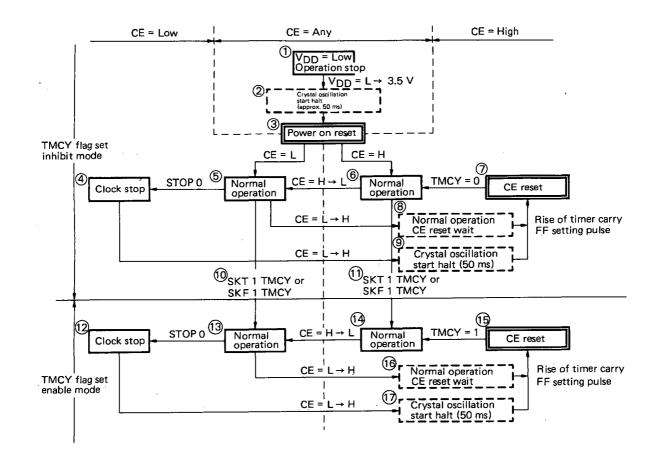

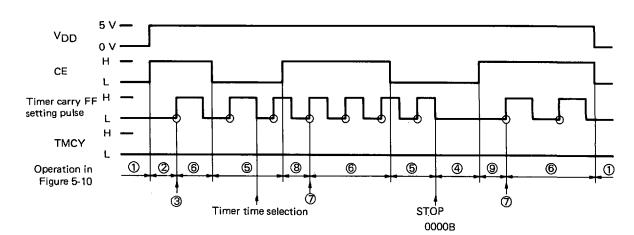

| 13      | CE         | Input            |                | Chip<br>Enable | <ul> <li>Input pins for device operation selection signal and reset signal. Device operation selection signal and reset signal. Device operation of the PLL frequency synthesizer and standby status as described below.</li> <li>(1) Device operation selection <ul> <li>When the CE pin is at a High level, the PLL frequency synthesizer section can be operated.</li> <li>When the CE pin is at a Low level, the PLL frequency synthesizer section sets the a Disable state (operation prohibited) automatically in the device internal section. When the CE pin is at a Low level, the operation of quartz oscillation circuits in the internal section and CPU carbins the operation of quartz of the present of the stopped by executing a Clock Stop instruction and data memory can be kepunder a low consumption current (15 μ/ or less) (at CE pin = High level, the Cloce Stop instruction operates as the NOP instruction). At execution of a Clock Stop instruction, the LCD controller/driver is set to a Display Off mode (LCD0-LCD2/COM0, COM1 pin are Low level output) and general purpose input-output ports (Port 0A, Port 0B, Port 0C, and Port 1A are used as input ports.</li> </ul> </li> <li>(2) Reset signal input <ul> <li>When the CE pin is changed from a Low level to High level, the device is reset by synchronizing with the Timer Carry FF of the internal section (CE Reset).</li> <li>When the device is reset, the program starts from address 0. In this case, the general purpose input/output ports are used as input ports. Since four types of internal Timer Carry FF, 1, 5, 100, and 250 ms can be selected. However, if a Cloc Stop instruction has been executed, the device is reset about 100 ms after the CI pin is changed to a High level.</li> <li>This pin does not accept a Low level or High level of less than 110-165 μs to prevent operation error due to noise.</li> </ul> </li> </ul> |

| Pin No.              | Pin symbol                       | Input/<br>Output | Output<br>mode    | Pin name       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|----------------------------------|------------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

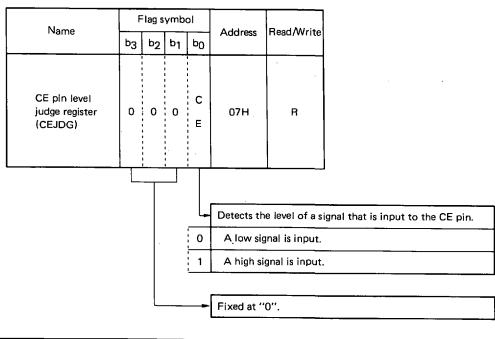

| 13                   | CE                               | Input            | _                 | Chip<br>Enable | By using the CEJDG register (address<br>07H) of the register file, the input signal<br>level of this pin can be detected. In this<br>case also, the contents of the CEJDG<br>register do not change at a Low level or<br>High level of less than 110-165 $\mu$ s.<br>Shumit Trigger input with hysterisis<br>feature is used for this pin. Note that a<br>voltage higher than that of V <sub>DD</sub> pin<br>must not be supplied at power connec-<br>tion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14<br>15<br>16<br>17 | P1A3<br>P1A2<br>P1A1<br>P1A0/FOG | Input<br>Output  | CMOS<br>Push-Pull | Port 1A        | <ul> <li>Used as a 4-bit general purpose input/output port and also as an external gate counter (P1A<sub>Q</sub>/FCG pin).</li> <li>The switching between the general purpose input/output port and an external gate counter is performed by the IFCMODE register (address 12H) of the register file.</li> <li>(1) When the port is used as a 4-bit general purpose input/output port</li> <li>The port can be specified as an input or output port in bit units (bit I/O). Input or output is specified by the P1ABIO register (address 35H) of the register file. The P1A register (address 70H of BANK1) of the port register is used for reading input data and setting output data.</li> <li>(2) When the port is used as an external gate counter (FCG) (P1A<sub>Q</sub>/FCG pin)</li> <li>The counter counts the time from one rising edge to the next rising edge of the signal sent to the P1A<sub>Q</sub>/FCG pin A reference frequency (1 kHz, 100 kHz, 900 kHz) of the internal section is counted by a 16-bit counter. The external gate counter is specified by the IFCMODE register (address 23H) of the register file. The P1A<sub>Q</sub>/FCG pin must be specified as the input port by the P1ABIO register (address 35H). Since the IFCMODE register and IFCCONT register control the frequency counter (P1D<sub>3</sub>/FMIFC and P1D<sub>2</sub>/AMIFC pins) and a clock generator port (P1B<sub>0</sub>/CGP pin) also, an external gate counter, frequency counter, and a lock generator port cannot be used concurrently. At Power On Reset, execution of a Clock Stop instruction, and CE Reset, all of these pins are specified for input ports of the general input/output ports.</li> </ul> |

| Pin No.              | Pin symbol                                      | Input/<br>Output | Output<br>mode                                                      | Pin name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

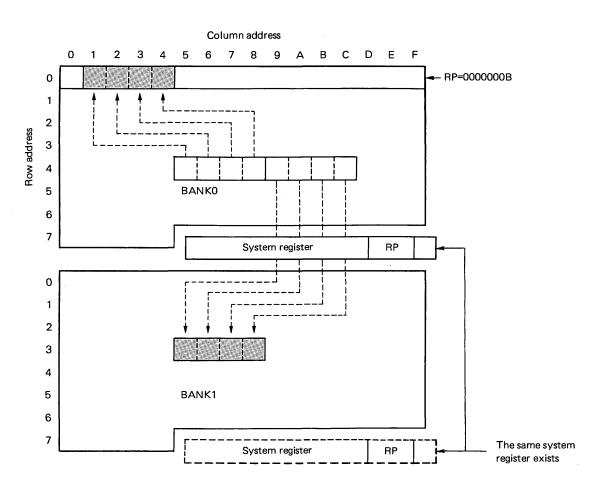

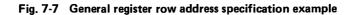

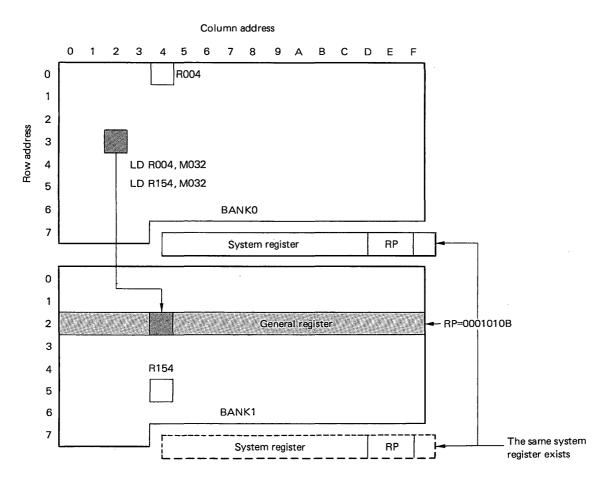

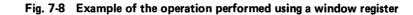

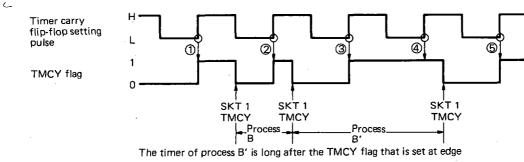

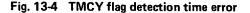

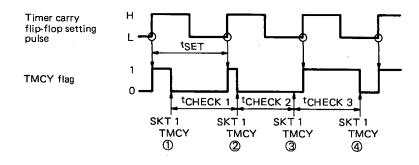

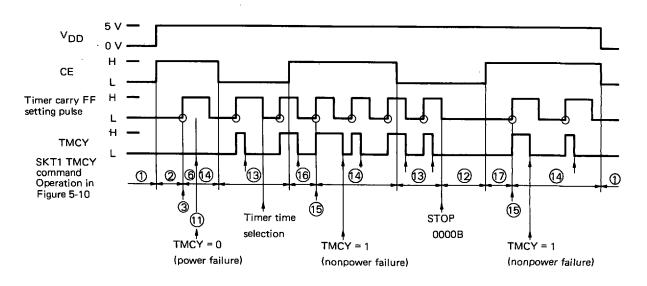

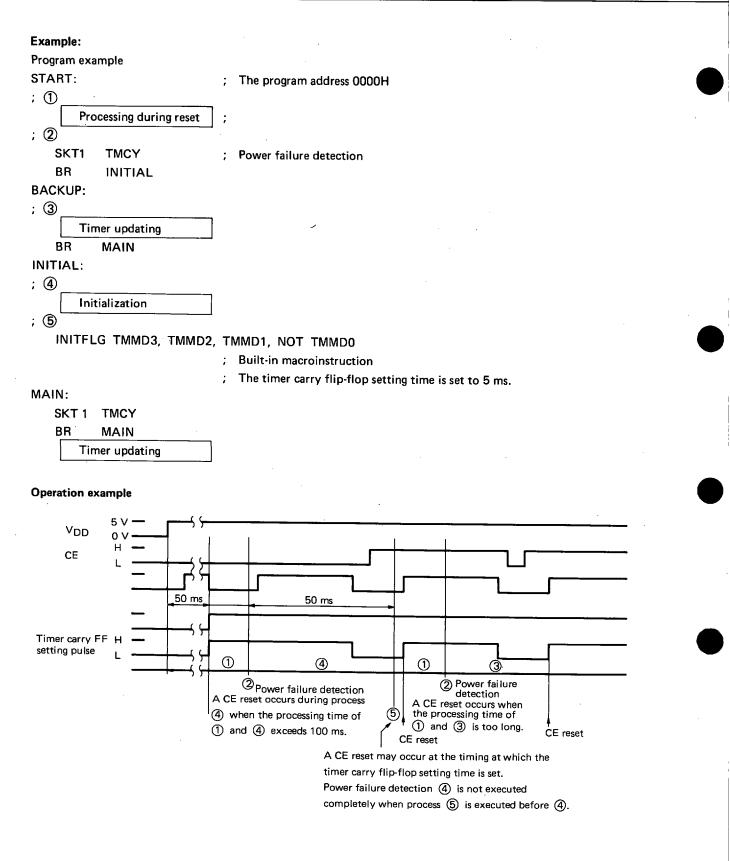

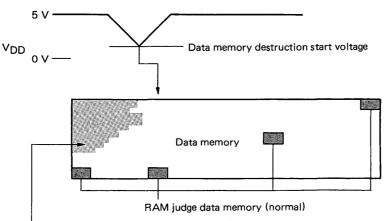

|----------------------|-------------------------------------------------|------------------|---------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|