## **VOLTAGE SYNTHESIZER SINGLE-CHIP MICROCOMPUTER**

#### DESCRIPTION

The 4-bit CMOS microcomputer  $\mu$ PD1730 designed for digital tuning purposes is capable of direct LED connections, and features a built-in D/A converter for voltage synthesizer applications.

The CPU functions include 4-bit parallel addition and subtraction (AD, SU instructions, etc.), logical operations (EXL instruction, etc.), multiple bit test (TMT instruction, etc.), CARRY F/F setting and resetting (STC instruction, etc.), interrupt, and timer functions.

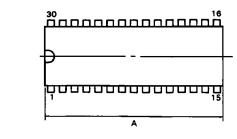

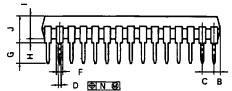

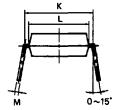

This 30-pin shrink DIP (Dual In-line Package) includes I/O (Input/Output) ports controlled by a powerful set of input and output instructions (IN, OUT instructions, etc.), a 6-bit D/A converter, and a 4-bit A/D converter.

The A/D converter can be used as an S-curve input pin during auto fine tuning (AFT) when the device is used in TV applications.

### **FEATURES**

- 4-bit microcomputer for digital tuning applications

- Built-in 13-bit D/A converter for voltage synthesizers

- 5 V ± 10 % single source power supply

- CMOS low power consumption

- Simple back-up of data memory (RAM) (using CE pin)

- Program memory (ROM): 16 bits x 1008 steps

- Data memory (RAM): 4 bits x 48 words

- Powerful set of 67 instructions (all 1-word instructions)

- Instruction execution time of 33.3 µsec (when connected to 4.5 MHz ceramic resonator)

- Wide range of addition and subtraction instructions (12 addition and 12 subtraction instructions)

- Powerful composite judgement instructions (TMT, TMF instructions, etc.)

- Storage-to-storage transfer at same row address

- Indirect transfer between registers MVRD, MVRS instructions, etc.)

- · Powerful set of 16 general registers (located in RAM space)

- Stack level: 1 level

- Instruction controlled stop watch capability (supply current 10 μA MAX.)

- 14 powerful I/O ports (PA<sub>0</sub> to PA<sub>3</sub>: 1-bit unit input and output settings, PB<sub>0</sub> to PB<sub>3</sub>: group input and output settings, PC<sub>1</sub> to PC<sub>2</sub>, PM<sub>1</sub>, PM<sub>2</sub>: output-only port, RS: input-only port)

- Direct LED drive capability (segments only, N-channel open-drain 12 V, 40 mA MAX.)

- Built-in 6-bit D/A comparator

- Built-in 4-bit A/D comparator

- Built-in horizontal synchronizing signal detector circuit

- Manual tuning with externally connected variable registance (to vary tuning D/A output)

### ORDERING INFORMATION

| Order Code    | Package                             |  |  |  |  |

|---------------|-------------------------------------|--|--|--|--|

| μPD1730CT-XXX | 30-pin plastic shrink DIP (400 mil) |  |  |  |  |

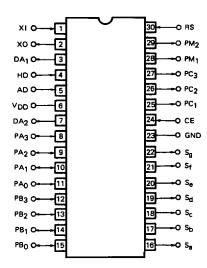

## PIN CONFIGURATION (Top View)

## PIN DESCRIPTION

| PIN NO. | SYMBOL          | NAME                                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | OUTPUT TYPE                    |

|---------|-----------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1 2     | XI<br>XO        | Ceramic<br>Resonator                        | Ceramic resonator connector pin. Use a 4.5 MHz resonator.<br>Use a quartz crystal resonator in applications (such as clocks)<br>where precision is required.                                                                                                                                                                                                                                                                                                                                                                                 | Input (XI) CMOS push-pull (XO) |

| 3       | DA <sub>1</sub> | Tuning D/A<br>Comperator<br>Output          | Voltage synthesizer 13-bit D/A (Digital to Analog) converter output pin. Since a combined 8-bit PWM (Pulse Width Modulation) and 5-bit RMP (Rate Multiplier) is used as the conversion method, integration with a simple CR filter is possible.  The output is switched to high level when reset by switching the power on (VDD: Low -> High) and when the clock is stopped.                                                                                                                                                                 | CMOS push-pull                 |

| 4       | но              | Morizontal<br>Synchronizing<br>Signal input | Horizontal synchronizing signal detector pin. When in HD mode, the PM3 internal port is set if the input frequency applied to this pin is between 14.832 and 16.480 kHz, but is reset if outside this range.  This HD pin can also be connected to a potentiometer circuit used for tuning purposes (VR mode). Connecting a capacitor and variable resistor to this pin when in VR mode enables direct control of the tuning 13-bit D/A converter (DA1 pinI by the variable resistor. Connect the circuit as shown in the following diagram. | Input                          |

| 5       | AD              | A/D<br>Converter<br>Input                   | = 1: VR mode, PG <sub>0</sub> = 0: HD mode).  A/D (Analog to Digital) converter input. The built-in 4-bit A/D converter connected internally to this pin is a programmed successive comparison type. The A/D converter reference voltage is V <sub>DD</sub> (5 V ± 10 %).                                                                                                                                                                                                                                                                    | Input                          |

| 6       | V <sub>DD</sub> | Power Supply                                | The $\mu$ PD1730's power supply pin. A 5 V ± 10 % voltage is supplied during device operations, but this can be lowered to 2.5 V during internal data memory (RAM) hold status (following execution of the CKSTP instruction). The device is reset when the voltage applied to this pin is changed from 0 to 4.5 V (power ON reset), and the program is started from address 0 (see Section 1.5 "TIMER F/F").                                                                                                                                | _                              |

| 7       | DA <sub>2</sub> | D/A<br>Converter<br>Output                  | 6-bit D/A converter output pin. Since output pulses are generated by a 1.4 kHz rate multiplier (RMP) method, the output voltage can be divided into 64 levels when passed a CR integrating circuit.  A low level output is generated by power ON reset (VDD: Low → High) and when the clock is stopped.                                                                                                                                                                                                                                      | CMOS push-pull                 |

| PIN NO.        | SYMBOL                                   | NAME                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OUTPUT TYPE             |

|----------------|------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 8<br>to<br>11  | PA <sub>3</sub><br>to<br>PA <sub>0</sub> | . Port A                          | 4-bit input/output port.  This port can be specified "input" or "output" one bit at a time. This designation is executed according to the contents of address 1FH of a data memory (RAM) called the PAIO word (see Notes 1 and 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CMOS push-pull          |

| 12<br>to<br>15 | PB3<br>to<br>PB <sub>O</sub>             | Port B                            | 4-bit input/output port.  This port can be set to 4-bit input port by executing an input instruction (IN instruction), or to 4-bit output port by executing an output instruction (OUT, SPB or RPB instruction). (See Notes 1 and 2.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOS push-pull          |

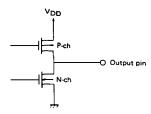

| 16<br>10<br>22 | Sa<br>to<br>Sg                           | Segment<br>Signal<br>Output       | Display segment signal output pins.  The memory contents at any address in the data memory (RAM) can be loaded into the segment PLA (Programmable: Logic Array) by the SEG instruction, and pessed to these pins via that segment PLA. The segment PLA can specify 32 different patterns. (See Section 5, "SEGMENT PLA".)  These pins can also be used as the key return signal source for the key matrix. Since the output format is N-channel opendrain, pull-up resistance is required. The segment signal outputs are switched to high level (pull-up potential) when the CE pin is changed to low level.                                                                                                                                                                                                                                                 | N-channet<br>open-drain |

| 23             | GND                                      | Ground                            | The device's ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                       |

| 24             | CE                                       | Chip Enable                       | Device selector signal input pin.  This pin is switched to high level for normal operations, but to low level when the device is not being used. Switching this CE pin to low level results in the segment signal outputs (Sa to Sg) being switched off and left at the pull-up potential (without effecting DA <sub>1</sub> , DA <sub>2</sub> , port A, port B, port C, and port M). Note, however, that inputs of less than 134 µsec are not accepted.  If the CKSTP instruction being used by a program is executed while the CE pin is at low level, the internal clock generator and CPU stop operating to enable a memory (RAM) hold state where the consumption current is low less than 250 µA).  When the CE pin is switched from low to high level, the device is reset, and the program is started from address 0. (See Section 1.5, "TIMER F/F".) | Input                   |

| 25<br>to<br>27 | PC <sub>1</sub><br>to<br>PC <sub>3</sub> | Port C                            | 3-bit output port (see Notes 1 and 3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CMOS push-pull          |

| 28<br>29       | PM <sub>1</sub><br>PM <sub>2</sub>       | Port M                            | 2-bit output port.  Since this is an N-channel open-drain output (resistivity of 14 V), an external pull-up resistance is required. (See Notes 1 and 3.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | N-channei<br>open-drain |

| 30             | RS                                       | Remote<br>Control Signal<br>Input | 1-bit input port.  The status of this pin can be checked directly by using the TRS instruction. A remote control input signal is applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Input                   |

- Notes 1: In port operation instructions (input/output, test port, and set/reset instructions), PB<sub>Q</sub> corresponds to the least significant bit of the register or operand data, and PB<sub>Q</sub> corresponds to the most significant bit. The same applies to PA, PC, and PM.

- All input/output ports (PA and PB) are switched to input mode when the device is reset (V<sub>DD</sub> and CE switched from low to high level) or when the CKSTP instruction is executed.

- Output-only ports (PC and PM) are changed to high impedance state when the device is reset (but only when VDD is switched from low to high level) or when the CKSTP instruction is executed.

Note that when CE alone is switched from low to high level, the previous state is maintained without the ports being switched to high impedance. But if CE is switched from low to high level after  $V_{DD}$  has been changed from low to high level or the CKSTP instruction has been executed, these output ports are switched to high impedance.

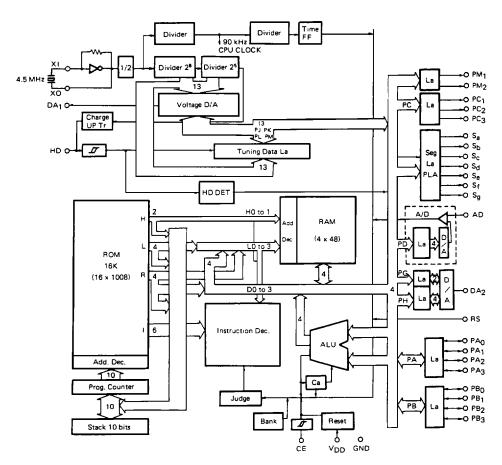

## μPD1730 BLOCK DIAGRAM

#### 1. CPU

## 1.1 PROGRAM COUNTER (PC)

The program counter used to address the program memory (ROM) (that is, programs) is a 10-bit binary counter.

The program counter is normally incremented by one each time an instruction is executed. But when a jump or subroutine call instruction is executed, the address specified in the operand is loaded. And when a skip instruction (e.g. ADS, TMT or RTS instructions) is executed, address of the next instruction after that is loaded irregardless of the skip conditions. If there are conditions to be skipped in this case, the next instruction after the skip instruction is regarded as NOP (no-operation).

That is, NOP is executed and the address of the next instruction after that is specified.

#### 1.2 STACK REGISTER (SR)

The stack register is a 1 x 10 bits register used to store the program counter contents incremented by +1 when a subroutine call instruction is executed (that is, the 10-bit return address). The stack register contents are loaded into the program counter by executing a return instruction (RT or RTS). This is followed by a return to the main program flow.

#### 1.3 PROGRAM MEMORY (ROM)

This 16 bits x 1008 steps ROM is used for program storage. The ROM address range available for use consists of the 1008 steps from 000H to 3EFH.

Fig. 1-1 ROM Configuration

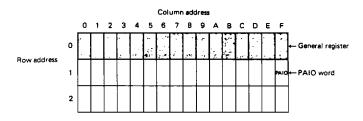

#### 1.4 DATA MEMORY (RAM)

The 4-bit x 48 words RAM is normally used to store data. The section from address 00H thru 0FH known as the general register can be used in transfers and in arithmetic operations with the memory. It can also be used as an ordinary memory.

Address 1FH (called the PAIO word) is used in specifying port A (PA<sub>0</sub> to PA<sub>3</sub>) as input or output.

Fig. 1-2 RAM Configuration

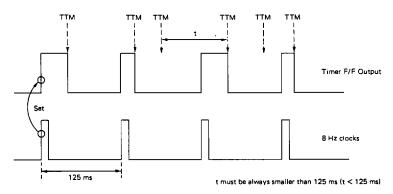

### 1.5 TIMER F/F (TM F/F)

The timer F/F is to be set with an 8 Hz (125 ms) signal and reset by the test timer instruction (TTM instruction). This timer F/F is automatically set every 125 ms so that it can be used to count the clock (one second by 8 counts) or the mute time.

Since the timer F/F can be reset only by the execution of TTM instruction this instruction must be executed within the period of 125 ms under any circumstance. When this instruction is executed within a period of 125 ms or more, the timer F/F fails to count up the clock and becomes unable to control the correct time.

Fig. 1-3 Execution Timing of TTM Instruction

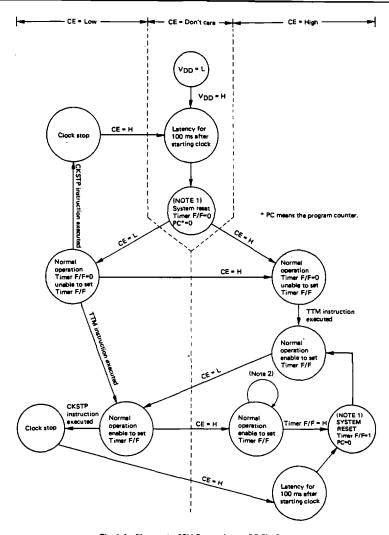

This timer F/F can be also used to judge the detection of power failure. It is reset when VDD changes from low to high or it is set again by the execution of CKSTP instruction or when CE changes from low to high. (Note 3) Fig. 1-4 shows the status transition diagram illustrating the aforementioned relations.

Fig. 1-4 Changes in CPU Status due to CE Pin Status

- Note 1: The following operations are done under the system reset status:

- 1 The program counter is reset to address 0.

- 2 BANK F/F is reset (BANKO).

- 3 I/O port becomes the input mode.

- Note 2: This loop cannot be exited if the TTM instruction is executed at the same time that the timer F/F is set. In this case, the loop is exited when the timer F/F is next executed (125 msec later), and the program jumps to address 0 with timer F/F = 1. Note, therefore, that if the TTM instruction is executed periodically, and by chance corresponds with the timer F/F setting cycle (125 msec), the program will never be cleared to address 0.

As apparent from the above illustration, the program starts from the address 0 after the power is turned on (V<sub>DD</sub> changes from Low to High), no matter what condition the CE pin is held, while the timer F/F remains reset. The timer F/F is not set again unless the TTM instruction was once executed (status unable to set the timer F/F). Once the TTM instruction was executed, however, the timer F/F can be set at any time at the intervals of 125 ms each.

If the power is being fed (V<sub>DD</sub> = high) and the CE pin changes from low to high, the program flow jumps to the address 0 immediately when the timer F/F is set<sup>(Nots 4)</sup>. The program therefore starts from the address 0 while the time F/F remains set.

As you could understand well from the above explanation, the contents of Timer F/F vary between the time the power failure is recovered (V<sub>DD</sub> changes from low to high) and the time when the power is continuously fed (V<sub>DD</sub> =high and CE=low) or when the device is restored from the backed-up condition. Through testing the contents of this timer F/F (i.e. the execution of TTM instruction) it is possible to judge if it is restored from the power failure or from the non-power failure. In other words the power failure can be judged if the execution of TTM instruction, which is executed within 125 ms from the start of program from the address 0, results in 0 (false) or it can be determined as non-power failure (backed-up condition) if the result of test turns to 1 (true).

Care must be also taken to the programming when restoring from the non-power failure ( $V_{DD}$ =high and CE changes from low to high) while the clock function of a given program, if provided, needed to be operated (without using the CKSTP instruction) even if CE was low. The program flow in this case jumps to the address 0 immediately after the timer F/F is set. It is therefore necessary to update the clock after executing the TTM instruction to detect the power failure (the execution results in finding true). Otherwise the clock delays by 125 ms each whenever the CE pin changes from low to high.

- Note 3: The program starts from the address 0 after the timer F/F was set if CE pin changed from low to high following the execution of CKSTP instruction in case of μPD1730. The timer F/F is reversely reset and the program starts from the address 0 under μPD1701, μPD1703, μPD1704, μPD1710 and μPD1719. It must be noted when executing the CKSTP instruction that the contents of timer F/F differ between μPD1730 and the group of μPD1701, μPD1703, μPD1704, μPD1710 and μPD1719.

- Note 4: Even if the CE pin changes from low to high level, the program flow does not move to address 0 when the setting of the timer F/F and the execution of the TTM instruction overlap. If this is the case, the system judges that the timer F/F is set by the TTM instruction execution and the timer F/F is reset. This point must be kept in mind when a power failure detection is done by the TTM instruction. That is, you should know that the TTM instruction has higher priority than the setting of the timer F/F when they overlap. Therefore, the clock does not become incorrect and a misjudging of a power failure does not occur. However, if the TTM instruction execution and the timer F/F setting happen to coincide in the following program, the program does not jump to address 0 forever. (The timer F/F will not be reset.)

In this example the program executes the normal TTM instruction, skips the next 'JMP B' instruction because the timer F/F is reset, and executes 'JMP A' instruction. Therefore, it cycles this loop. The cycle is 100 µs. (3 steps) The timer F/F is set once every 125 ms and the operations of B are performed. This operations take (3n + 3) steps (multiple of 100 µs). If the CE pin happens to change from low to high level during the TTM instruction execution in this program, operations in B are done due to the judgement that the timer F/F is set by the TTM instruction. However, the timer F/F is set again (125 ms later) when the next TTM instruction is executed because the time interval from the last TTM execution to the next TTM execution is a multiple of 100 µs. Therefore, the timer F/F will not be reset and the program cycles this endless loop. This problem occurs in a program where the TTM instruction is executed in every 125 ms. If this is the case, change the program so that the TTM instruction is not executed after 125 ms (3750 steps) from the TTM execution.

#### 1.6 CARRY F/F (C F/F)

The CARRY F/F is normally set when a carry or borrow is generated as the result of executing an arithmetic operation, and reset when no carry or borrow is generated. The CARRY F/F contents remain unchanged if no arithmetic operation instruction is executed. The CARRY F/F can be set and reset directly by the respective carry F/F set and reset instructions (STC and RSC).

#### 1.7 BANK F/F (B F/F)

The BANK F/F is used in port group addressing. The two operand bits of the instruction are also involved in this addressing process (see Section 2, "PORTS"). The bank and corresponding BANK F/F contents are listed in Table 1-1

Bank designations are executed by the BANKO, BANK1, or BANK2 instruction.

In μPD1700 series devices with a data memory (RAM) of at least 64 words (μPD1704, μPD1706, μPD1707, μPD1708, μPD1710, μPD1711, μPD1712, μPD1713, μPD1714, μPD1715, and μPD1719) the bank is divided into 64-word groups, and designation of these groups is also executed by the same BANK F/F.

Since the µPD1730 RAM has only 48 words, this RAM is BANKO. And this RAM cannot be accessed when not in BANKO status. Before accessing this RAM, the BANKO instruction must be executed in advance to set BANK to 0.

When the power is switched on (V<sub>DD</sub> changed from low to high) or when CE is switched from low to high (that is, when the device is reset), the BANK F/F is reset and BANK0 is specified automatically.

| BANK | BANK F/F1 | BANK F/F0 |

|------|-----------|-----------|

| 0    | 0         | 0         |

| 1    | 0         | 1         |

| 2    | 1         | 0         |

Table 1-1 Bank Designations

#### 2. PORTS

The μPD1730 input/output ports are port A (PA<sub>3</sub> to PA<sub>0</sub>) and port B (PB<sub>3</sub> to PB<sub>0</sub>), and the output ports are port C (PC<sub>3</sub> to PC<sub>1</sub>) and port M (PM<sub>2</sub> and PM<sub>1</sub>). The internal ports are port D (PD<sub>3</sub> to PD<sub>1</sub>), port G (PG<sub>3</sub>, PG<sub>2</sub>, and PG<sub>0</sub>), port H (PH<sub>3</sub> to PH<sub>0</sub>), port J (PJ<sub>3</sub> to PJ<sub>0</sub>), port K (PK<sub>3</sub> to PK<sub>0</sub>), port L (PL<sub>3</sub> to PL<sub>0</sub>), and port M (PM<sub>3</sub> and PM<sub>0</sub>). Apart from not having externally connected pins, these internal ports are handled in the same way as external ports. That is, the port operation instructions IN, OUT, SPB, and RPB can be used without modification.

Addressing of these ports is achieved by using the two direct addressing bits in the instructions operand, plus the bank F/F bank designation. These port addresses are listed in Table 2-1, and a list of ports is given in Table 2-2.

The same bank designations are used in both port and RAM addressing. Since the RAM is BANK0 in  $\mu$ PD1730, the bank must always be set to 0 for RAM access purposes.

| Direc | t Add. |        | BANK   |        |

|-------|--------|--------|--------|--------|

| #1    | #0     | 0      | 1      | 2      |

| 0     | 0      | Port A | _      | Port J |

| 0     | 1      | Port B |        | Port K |

| 1     | 0      | Port C | Port G | Port L |

| 1     | 1      | Port D | Port H | Port M |

Table 2-1 Port Address

Table 2-2 List of Ports

| BANK | Direct Add. | Port                               | 1/0 | Function                                                              |  |  |  |

|------|-------------|------------------------------------|-----|-----------------------------------------------------------------------|--|--|--|

|      | 0           | PA <sub>0</sub> to PA <sub>3</sub> | 1/0 | General purpose input/output port (I/O can be specified for each bit) |  |  |  |

| 0    | 1           | PB <sub>0</sub> to PB <sub>3</sub> | I/O | General purpose input/output port                                     |  |  |  |

|      | 2           | PC <sub>1</sub> to PC <sub>3</sub> | 0   | General purpose output port                                           |  |  |  |

|      | 3           | PD <sub>0</sub> to PD <sub>3</sub> | 0   | A/D converter comparison data                                         |  |  |  |

|      | 2           | PG <sub>0</sub>                    | 0   | HD pin mode selection (0: HD mode, 1: VR mode)                        |  |  |  |

| 1    |             | PG <sub>2</sub> to PG <sub>3</sub> | 0   | DA (Chia D/A annual) annual data                                      |  |  |  |

|      | 3           | PH <sub>0</sub> to PH <sub>3</sub> | 0   | DA <sub>2</sub> (6-bit D/A converter) control data                    |  |  |  |

|      | 0           | PJ <sub>0</sub> to PJ <sub>3</sub> | 1/0 |                                                                       |  |  |  |

|      | 1           | PK <sub>0</sub> to PK <sub>3</sub> | 1/0 | DA - /12 his D/A                                                      |  |  |  |

| 2    | 2           | PL <sub>0</sub> to PL <sub>3</sub> | 1/0 | DA <sub>2</sub> (13-bit D/A converter) control data                   |  |  |  |

| •    |             | PM <sub>O</sub>                    | 1/0 |                                                                       |  |  |  |

|      | 3           | PM <sub>1</sub> , PM <sub>2</sub>  | 0   | General purpose output port                                           |  |  |  |

|      |             | PM <sub>3</sub>                    | ı   | Station detection when in HD mode (0: Station tuned, 1: No station)   |  |  |  |

#### 2.1 PORT A

Port A (PA<sub>3</sub> to PA<sub>0</sub>) can be set to input or output in 1-bit steps. Input or output is set by the contents of address 1FH in the data memory (RAM). These contents are called the PAIO word. Input port is set by setting the corresponding PAIO word bit to "0", and output port is set by setting "1".

|                            | #3              | #2              | #1              | #0              |

|----------------------------|-----------------|-----------------|-----------------|-----------------|

| PAIO Word<br>(Address 1FH) | PA <sub>3</sub> | PA <sub>2</sub> | PA <sub>1</sub> | PA <sub>0</sub> |

Example 1. Set PA<sub>3</sub> to PA<sub>0</sub> to output ports.

|                            | #3 | #2 | #1 | #0 |

|----------------------------|----|----|----|----|

| PAIO Word<br>(Address 1FH) | 1  | 1  | 1  | 1  |

Example 2. Set PA<sub>3</sub> to output port, and PA<sub>2</sub> to PA<sub>0</sub> to input ports.

|                            | #3 | #2 | #1 | #0 |

|----------------------------|----|----|----|----|

| PAIO Word<br>(Address 1FH) | 1  | 0  | 0  | 0  |

After Port A has been set to input/output port by PAIO word, an input/output instruction must be executed. And once input or output mode has been set, it is maintained until the PAIO word contents (address 1FH data) are changed.

```

Example: BANK0

MVI 1FH, 1111B; Set all port A bits to output port mode

...

MVI 08H, 1100B; Set PA<sub>3</sub> and PA<sub>2</sub> to high level and PA<sub>1</sub> and PA<sub>0</sub> to low level

OUT 0, 08H; Output PA<sub>3</sub> and PA<sub>2</sub> = high level and PA<sub>1</sub> and PA<sub>0</sub> = low level

```

Note, however, that port A is automatically set to input port mode when the power is switched on  $(V_{DD})$  changed from low to high), when the CKSTP instruction is executed, and when the CE pin is changed from low to high. And pay special attention to the fact that the PAIO word contents may not necessarily match the port A input status at this stage. Port A remains in input mode until the PAIO word contents are set.

When output port mode is set by the PAIO word, the output latch circuit contents are passed directly to the port. Note that the output latch circuit contents are undefined when the power is switched on (V<sub>DD</sub> changed from low to high), and are held when the clock is stopped.

Therefore, where it is necessary to avoid an undefined output status when output port is first defined by PAIO word, specify output status by the SPB or RPB and OUT instructions before setting the port status.

#### 2.2 PORT B

Port B (PB<sub>3</sub> to PB<sub>0</sub>) can be specified input or output as a 4-bit group. All four bits are switched to input port status when an input instruction (IN) is executed, or to output port status when an output instruction (OUT, SPB, or RPB) is executed. That is, input/output mode can be switched by executing input and output instructions.

Data specified by the OUT instruction is output from port B to switch the port to output mode when the OUT instruction is executed. But when the SPB or RPB instruction is executed, the port B data latch contents are output at bits apart from those specified by the instruction operand, thereby switching port B to output port mode. The port B data latch contents are only changed when the OUT, SPB, or RPB instruction is executed.

Port B is automatically set to input port mode when the power is switched on  $\{V_{DD}$  changed from low to high), when the CKSTP instruction is executed, and when the CE pin is changed from low to high, and remains in input mode until an output instruction (OUT, SPB, or RPB) is executed. And note that the port B data latch contents remain unchanged when the CKSTP instruction is executed or when the CE pin is changed from low to high (and that these contents are undefined when the power is switched on  $\{V_{DD}\}$  changed from low to high)).

### 2.3 PORT C

Port C (PC<sub>3</sub> to PC<sub>1</sub>) is a CMOS push-pull type output-only port. Normally, this port is accessed by executing an output instruction (OUT, SPB, or RPB). If an input instruction (IN) is executed, the current output data is read into a specified register. There is no change to the contents output by execution of the IN instruction.

When an output instruction is executed, output of "1" results in output of a high level, and output of "0" results in output of a low level (GND potential). When the power is switched on (VDD changed from low to high) and when the CKSTP instruction is executed, port C is switched to high impedance. The internal data latch contents remain unchanged at this stage (but these contents are undefined when the power is switched on (VDD changed from low to high)).

#### 2.4 PORT M

Port M (PM<sub>2</sub> and PM<sub>1</sub>) is an N-channel open-drain type output-only port. This port is normally accessed by executing an output instruction (OUT, SPB, or RPB). If an input instruction (IN) is executed, the current output data is read into a specified register. There is no change to the contents output by execution of the IN instruction.

When an output instruction is executed, output of "1" results in output of a high level (pull-up potential), and output of "0" results in output of a low level (GND potential). When the power is switched on (VDD changed from low to high) or when the CKSTP instruction is executed, port M is switched to "1" output status (high impedance status). That is, pull-up potential output status.

The internal data latch contents remain unchanged at this stage (but these contents are undefined when the power is switched on (V<sub>DD</sub> changed from low to high)).

### 3. D/A CONVERTERS

µPD1730 features a 13-bit D/A converter (DA<sub>1</sub>) for voltage synthesizer applications and 6-bit D/A converter (DA<sub>2</sub>) ideal for volume control, etc.

### 3.1 DA<sub>1</sub>

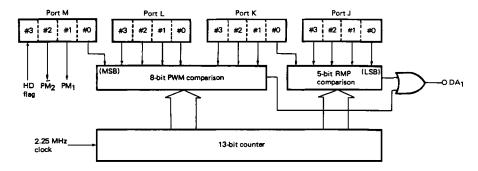

The conversion method used in the 13-bit tuning D/A converter is a combination of 8-bit pulse width modulation (PWM) and a 5-bit rate multiplier (RMP). Since output pulse signals are obtained from DA<sub>1</sub>, D/A conversion is achieved by adding an external low-pass filter.

The DA<sub>1</sub> configuration is outlined in Figure 3-1.

Fig. 3-1 DA<sub>1</sub> Configuration

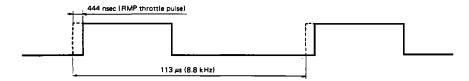

With a 2.25 MHz fundamental clock frequency, 13-bit D/A conversion is executed by applying 444 nsec throttle pulse signals to the 8-bit PWM signal from 0 to 32 times.

The output waveform is shown in Figure 3-2.

Fig. 3-2 DA<sub>1</sub> Output Waveform

The DA<sub>1</sub> output can be set to internal or external setting mode.

### 3.1.1 Internal setting mode (INT Mode)

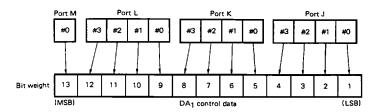

In internal setting mode, the D/A converter (DA<sub>1</sub>) output value is set by setting in the internal ports J (PJ<sub>3</sub> to PJ<sub>0</sub>), K (PK<sub>3</sub> to PK<sub>0</sub>), L (PL<sub>3</sub> to PL<sub>0</sub>), and M (PM<sub>0</sub>).

Fig. 3-3 Port Allocation

The bit weight of each port is shown in Figure 3-3. When all bits are set to 0, DA<sub>1</sub> generates a high level output rather than a pulse signal. And if all bits are set to 1, a low level output is generated.

Since D/A converter and CPU operations are asynchronous, unwanted data may appear when setting the port data. To prevent misoperation in µPD1730, the D/A converter conversion data is updated when port M data is set (OUT, SPB, or RPB instruction). The D/A converter output thus remains the same even if changes occur in the port J, port K, or port L value. Therefore, to change the D/A converter output value, data will have to be finally set in port M even if no change in port M data occurs.

#### 3.1.2 External setting mode (VR Mode)

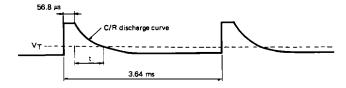

In external setting mode with a variable resistor and capacitor connected to the HD pin, the DA<sub>1</sub> output is varied by changing the variable register value. This mode is set by setting internal port PG<sub>0</sub> to 1. A 56.8 µsec output pulse is obtained from the HD pin to charge up the capacitor every 3.64 msec. And during the discharge interval, the corresponding value is set in the internal ports (ports J, K, L, and M), thereby executing the D/A conversion.

The device cannot be used in HD mode when VR mode has been set.

Fig. 3-4 HD Pin Waveform

The HD pin waveform is shown in Figure 3-4. The counter operates only during interval t from the start of discharge up to the threshold voltage (V<sub>T</sub>). Therefore, the longer the discharge time t the larger than D/A converter control data. The relationship between discharge time t, capacitor capacitance C, and variable resistor resistance R is expressed by the following equation:

$$\frac{V_{DD}}{V_T} = \exp \frac{-t}{CR}$$

For a D/A output value in the 0.5 to 31 V range in TV applications,  $C = 0.05 \,\mu\text{F}$  and R = 1.5 to 100 k $\Omega$ .

## 3.2 DA<sub>2</sub>

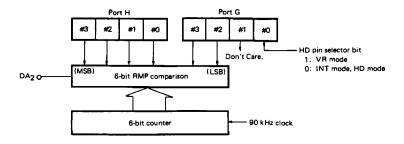

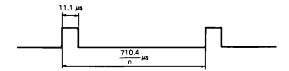

Since a 6-bit D/A converter RMP method is used, D/A conversion is executed by connecting a simple low-pass filter. Using a fundamental clock of 90.9 kHz, conversion data is set in internal ports G (PG<sub>2</sub> and PG<sub>3</sub>) and H (PH<sub>0</sub> to PH<sub>3</sub>).

Fig. 3-5 DA<sub>2</sub> Configuration

The relationship between the set data and output pulse is expressed by

Duty =

$$\frac{n}{64}$$

(where n is a decimal value in the  $0 \le n \le 63$  range)

The output waveform is shown in Figure 3-6. Low level is set when n = 0.

Fig. 3-6 DA<sub>2</sub> Output Waveform

#### 4. A/D CONVERTER

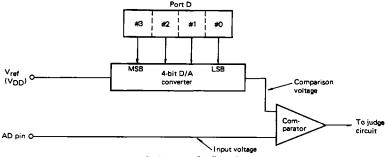

µPD1730 is equipped with a programmed successive comparison type 4-bit A/D converter. Analog inputs are applied to the AD pin. When used in TV applications, an S-curve output from the video intermediate frequency (VIF) stage is normally applied to the input, and this can be used, to judge the optimum tuning frequency during auto fine tuning (AFT). The AD pin can also be used as a 1-bit input port capable of setting the threshold level by program.

#### 4.1 OPERATING PRINCIPLES

The μPD1730 A/D converter consists of a resistance string 4-bit D/A converter and a comparator. Data is set in the D/A converter via internal port D. That is, comparison data is set in port D by executing an output instruction (OUT, SPB, or RPB), and is read by executing an input instruction (IN, TPT, or TPF).

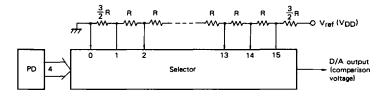

Fig. 4-1 A/D Converter Configuration

The D/A converter can generate 16 different comparison voltages (obtained by dividing the reference voltage  $V_{ref}(V_{DD})$ ) in accordance to the data set in port D. This comparison voltage is applied to the comparator together with the analog voltage applied to the AD pin (input voltage). The two voltages are compared, and the result is obtained by executing the TADT (Test A/D comparator, then skip if True) or the TADF (Test A/D comparator, then skip if False) instruction. The relationship between the input and comparison voltages is as follows:

True if input voltage > comparison voltage False if input voltage ≤ comparison voltage

#### 4.2 D/A CONVERTER CONFIGURATION

The D/A converter used in  $\mu$ PD1730 is a so-called resistance string type D/A converter where 16 resistors are connected in series between  $V_{ref}$  ( $V_{DD}$ ) and GND, and the voltage of a subsequent point is selected. It should be noted that the resistance is not the same for all resistors in the series. The value of the two resistors at both ends are 1.5/16 times the other resistors. The D/A converter configuration is outlined in Figure 4-2.

Fig. 4-2 D/A Converter Configuration

In the  $\mu$ PD1730 D/A converter, a GND level output is generated when the value set in port D is 0000B, and a 3/34 × V<sub>ref</sub> comparison voltage is generated when the port D value is 0001B. The comparison voltage V<sub>out</sub> when a value of n (decimal number) is set is given by the following equation:

$$V_{out} = V_{ref} \times \frac{2n+1}{34}$$

(where  $15 \ge n \ge 1$ )

Table 4-1 Input Data and Comparison Voltages

| Input | iata (port D) | Comp   | arison voltage |         |

|-------|---------------|--------|----------------|---------|

| DEC.  | Binary        | x Vraf | Vref = 5 V     |         |

| 0     | 0000          | 0      | 0 (V)          |         |

| 1     | 0001          | 3/34   | 0.44118        |         |

| 2     | 0010          | 5/34   | 0.73529        |         |

| 3     | 0011          | 7/34   | 1.02941        |         |

| 4     | 0100          | 9/34   | 1.32353        |         |

| 5     | 0101          | 11/34  | 1,61765        |         |

| 6     | 0110          | 13/34  | 1.91176        |         |

| 7     | 0111          | 15/34  | 2.20588        |         |

| 8     | 1000          | 17/34  | 2,50000        |         |

| 9     | 9             | 1001   | 19/34          | 2.79412 |

| 10    | 1010          | 21/34  | 3.08824        |         |

| 11    | 1011          | 23/34  | 3.38235        |         |

| 12    | 1100          | 25/34  | 3.67647        |         |

| 13    | 1 1 0 1       | 27/34  | 3.97059        |         |

| 14    | 1110          | 29/34  | 4.26471        |         |

| 15    | 1111          | 31/34  | 4.55882        |         |

In the programmed successive comparison A/D converter, the relationship between input voltage  $V_{in}$  and the comparison voltage  $V_{n}$  for data n set in the D/A converter is given by the following expression:

$$V_n < V_{in} \le V_{n+1}$$

The A/D conversion data output is usually n.

Note that the  $\mu$ PD1730 A/D converter differs from the other A/D converters used in other  $\mu$ PD1700 series devices (such as  $\mu$ PD1709 and  $\mu$ PD1716).

For actual applications, compare and judge input values using the data listed in Table 4-1. The range of A/D converter input voltages V<sub>in</sub> which can be measured is expressed as:

$$0 \le V_{in} \le V_{15}$$

(=  $V_{ref} \times 31/34$ )

If  $V_{in}$  lines in the  $V_{15} < V_{in} \le V_{ref} (V_{DD})$  range, it is handled as a "range over" voltage.

As was mentioned above, A/D conversion is achieved by executing the TADT or TADF instruction. For example, consider the input of an analog signal where  $V_{in} = V_{14}$  ( $V_{ref} \times 13.5/18$ ). When this is compared with the  $V_{13}$  comparison voltage, the result "true" (since input voltage > comparison voltage) is passed to the judge circuit. The input voltage is then compared with the  $V_{14}$  comparison voltage, resulting in output of a "false" result since input voltage  $\le$  comparison voltage.

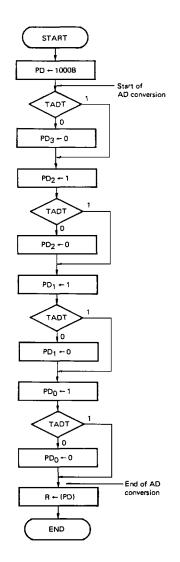

## 4.3 EXAMPLE OF AN A/D CONVERSION PROGRAM

Binary search method

START:

MVI R, 1000B OUT 3, R TADT RPB 3,1000B SPB 3,0100B TADT RPB 3,0100B SPB 3,0010B TADT RPB 3.0010B SPB 3,0001B TADT **RPB** 3,0001B IN R, 3

Example coding

Example flow chart

A/D conversion time: 366.3 µsec Total number of steps: 16 steps

### 5. HORIZONTAL SYNCHRONIZING SIGNAL DETECTOR CIRCUIT

µPD1730 features a built-in horizontal synchronizing signal detector circuit designed to detect broadcast signals during auto tuning operations.

The input signal applied to the HD pin is measured by a 5-bit counter (gate time: 1.82 msec). The internal port PM<sub>3</sub> is reset (to 0) if an input signal within the 14.831 to 16.480 kHz range is applied, but is set (to 1) if a signal outside this range is applied. That is, the presence on an input broadcast signal can be detected by testing this PM<sub>3</sub> port (using the IN, TPT, or TPF instruction) during auto tuning, etc.

Since this HD pin also serves as an external connection pin when in DA<sub>1</sub> output external setting mode (VR mode), HD mode must be set if the HD circuit is to be used. HD mode can be set by setting the PG<sub>0</sub> internal port to 0. Note that since PG<sub>2</sub> is undefined when the power is switched on, it must always be specified by program.

Table 5-1 PG<sub>2</sub> Mode Table Port G #3 #2 #0 DA<sub>1</sub> set mode HD pin operation mode DA<sub>2</sub> set data Internal setting mode HD mode (horizontal synchroniz-0 (INT mode) ing signal detector mode) Not used VR mode (output of variable External setting mode resistance to DA<sub>1</sub>)

D-9-20

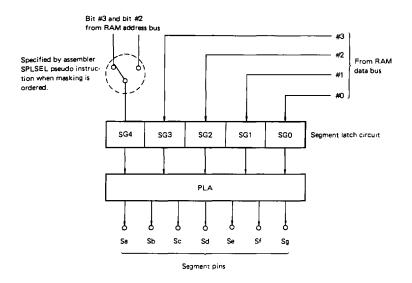

### 6. PROGRAMMABLE LOGIC ARRAY (PLA)

µPD1730 is equipped with a user program segment PLA. Normally, key return signal source patterns and dynamic switching display patterns are programmed. A total of 32 patterns (16 types x 2) can be generated.

### 6.1 SEGMENT PLA CONFIGURATION

The segment PLA consists of a 5-bit segment latch circuit, and a PLA which has seven outputs corresponding to segment pins (pins  $S_n$  to  $S_0$ ) and which accepts the segment latch circuit output.

Fig. 6-1 Segment PLA Configuration

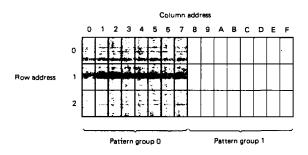

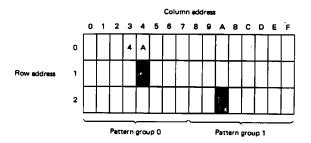

The data memory (RAM) contents specified by the SEG instruction operand are latched by the four lower bits (SG0 to SG3) of the segment latch circuit. For example, if the SEG 1,05H instruction is executed within the RAM contents shown below, the RAM contents addressed by 1 (RAM row address designation) and register 05H contents (column address designation), that is, the contents "F" of address 16H, are latched.

The contents of bit #3 or bit #2 of the RAM column address specified by the SEG instruction are latched by the most significant bit (SG4) of the segment latch circuit. When masking is ordered, it is necessary to specify which bit contents are to be latched (see Section 6.3, "PLA PROGRAM EXAMPLE"). If bit #3 is connected, 0 is latched by SG4 when the RAM in column address 00H to 07H is specified by the SEG instruction, and 1 is latched when 08H to 08H is specified. And if bit #2 is connected, 0 is latched when 00H to 03H and 08H to 08H are specified, and 1 is latched when 04H to 07H and 0CH to 0FH are specified.

The 32 segment patterns are divided into two groups of 16 patterns each by the data latched in SG4. Therefore, a different segment pattern output can be obtained from the segment pin if a different RAM column address is specified by the SEG instruction, even though the RAM data contents are the same.

The 16 patterns generated when SG4 is 0 are called "pattern group 0", and the patterns generated when SG4 is 1 "pattern group 1".

Fig. 6-2 Pattern Group Division When SG4 is Specified to Bit #3

Fig. 6-3 Pattern Group Division When SG4 is Specified to Bit #2

The pattern group division is decided when the program is written, taking into account the efficiency of the RAM and the program (ROM). And SPLSEL is used to decide whether SG4 input bit #3 or bit #2 is to be specified. Use either the

SPLSEL 3 or SPLSEL 2

Description (see Section 6.3, "PLA PROGRAM EXAMPLE").

## 6.2 SEGMENT PLA PATTERN EXAMPLE

Examples of pattern group 0 and pattern group 1 are shown in Tables 6-1 and 6-2 respectively.

Table 6-1 Pattern Group 0 Pattern Example

|     | Segment latch Segment output (Note) |     |     |      |    |    |    |    |    |   |    |                     |

|-----|-------------------------------------|-----|-----|------|----|----|----|----|----|---|----|---------------------|

| SG4 | SG3                                 | SG2 | SG1 | SG 0 | Se | Sf | S. | Sa | S, | S | S. | Output pattern      |

|     | 0                                   | 0   | 0   | 0    | 1  | 0  | 0  | 0  | 0  | 0 | 0  |                     |

|     | 0                                   | 0   | 0   | 1    | 1  | 1  | 1  | 1  | 0  | 0 | 1  | 1                   |

|     | 0                                   | 0   | 1   | o    | 0  | 1  | 0  | 0  | 1  | 0 | 0  | ĪĪ                  |

|     | 0                                   | 0   | 1   | 1    | 0  | 1  | 1  | 0  | 0  | 0 | 0  |                     |

|     | 0                                   | 1   | 0   | 0    | 0  | 0  | 1  | 1  | 0  | 0 | 1  | 1 <u> </u>          |

|     | 0                                   | 1   | 0   | 1    | 0  | 0  | 1  | 0  | 0  | 1 | 0  | <u> </u>            |

|     | 0                                   | 1   | 1   | 0    | 0  | 0  | 0  | 0  | 0  | 1 | 0  |                     |

|     | 0                                   | 1   | 1   | 1    | 1  | 0  | 1  | 1  | 0  | 0 | o  | [_]<br>             |

| "   | 1                                   | 0   | 0   | 0    | 0  | 0  | 0  | 0  | 0  | 0 | 0  | <u> </u>            |

|     | 1                                   | 0   | 0   | 1    | 0  | 0  | 1  | 0  | 0  | 0 | 0  |                     |

|     | 1_                                  | 0   | 1   | 0    | 1  | 1  | 1  | í  | 1  | 1 | 1  | Blank (Display off) |

|     | 1                                   | 0   | 1   | 1    | 0  | 0  | 0  | 0  | 1  | 1 | 0  | Ε                   |

|     | 1                                   | 1   | 0   | 0    | 0  | 1  | 1  | 1  | 1  | 1 | 1  | _                   |

|     | 1                                   | 1   | 0   | 1    | 1  | 1  | 1  | 0  | 1  | 1 | 1  |                     |

|     | 1                                   | 1   | 1   | 0    | 0  | 0  | 1  | 1  | 1  | 0 | 0  | ı                   |

|     | ı                                   | 1   | 1   | 1    | 0  | I  | 0  | 0  | 0  | 1 | I  | j 🗀                 |

## Note:

Segment outputs are set by active low. When active high, 0 is replaced by 1, and 1 is replaced by 0. And since the  $\mu$ PD1730 segment output is an N-channel open-drain format, it is normally set to active low.

Table 6-2 Pattern Group 1 Pattern Example

|     | Segment latch Segment output |     |     |     |   |    |    |    |     |    |    |                |

|-----|------------------------------|-----|-----|-----|---|----|----|----|-----|----|----|----------------|

| SG4 | SG3                          | SG2 | SG1 | SG0 | S | Si | S, | Sd | S,  | Sı | S. | Output pattern |

|     | 0                            | 0   | 0   | 0   | 0 | 0  | 0  | 0  | 0   | 0  | 0  | Key all ON     |

|     | 0                            | 0   | 0   | 1   | 1 | 1  | 1  | 1  | 1   | 1  | 0  | .Seg a (Key)   |

|     | o                            | 0   | 1   | 0   | 1 | 1  | 1  | 1  | 1   | 0  | 1  | Seg b (Key)    |

|     | 0                            | 0   | 1   | 1   | 1 | 1  | 1  | 1  | 0   | 1  | 1  | Seg c (Key)    |

|     | 0                            | 1   | 0   | 0   | 1 | 1  | 1  | 0  | 1   | 1  | 1  | Seg d (Key)    |

|     | 0                            | 1   | 0   | 1   | 1 | 1  | 0  | 1  | 1   | 1  | 1  | Seg e (Key)    |

|     | 0                            | 1   | 1   | 0   | 1 | 0  | 1  | 1  | 1   | 1  | 1  | Seg f (Key)    |

| 1   | 0                            | 1   | 1   | 1   | 0 | 1  | 1  | 1  | . 1 | 1  | 1  | Seg g (Key)    |

| •   | 1                            | 0   | 0   | 0   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Key all OFF    |

|     | 1                            | 0   | 0   | 1   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 0   | 1   | 0   | 1 | 1  | 1  | i  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 0   | 1   | 1   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 1   | 0   | 0   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 1   | 0   | 1   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 1   | 1   | 0   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

|     | 1                            | 1   | 1   | 1   | 1 | 1  | 1  | 1  | 1   | 1  | 1  | Not used.      |

When the above display pattern is used, the following output contents are obtained during execution of the SEG instruction. In this case, however, column address bit #3 is specified as the segment latch circuit SG4 input.

(1) SEG 1, 03H. . . RAM address 14H contents (0011B) are latched.

(2) SEG 2, 04H... RAM address 2AH contents (0011B) are latched.

Output pattern "Seg C"

As can be seen from this example, different output patterns can be obtained if the SG4 contents are different, even though the data set in the four lower bits of the segment latch circuit are the same.

#### 6.3 PLA PROGRAM EXAMPLE

The PLA needs to be defined in  $\mu$ PD1730. When ordering masks, those where the PLA section has not been defined cannot be accepted. The PLA definition is described at the end of the assembler source program. The following items are included. Note that all items must be described — not a single one can be omitted.

### (1) PLA pseudo instruction

In addition to the end of the program description section, this description also indicates the beginning of the PLA definition section.

#### (2) SPLSEL (Segment PLA Select) pseudo instruction

Description used to select the RAM address division for generation of segment pattern groups 0 and 1. Two description examples are given below.

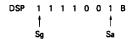

#### (3) DSP (Define Segment PLA) pseudo instruction

Definition of the 32 types of segment PLA patterns. The 16 patterns in pattern group 0 must be defined sequentially. A description example is given below. The first bit to be described is segment g (Sg pin).

The remaining bits are then described in descending order.

#### (4) END

In addition to the end of the PLA definition section, this description also indicates the end of the source program. The program is not assembled without this description.

Note 1: In μPD1700 series devices which include the DIGIT PLA function (μPD1701, μPD1703, μPD1704, μPD1705, μPD1705, μPD1707, and μPD1710), the DIGIT PLA definition is also required. DIGIT PLA is defined by using the DDP (Define Digit PLA) pseudo instruction.

Note 2: Although the PLA definition must commence with PLA and end with END, the intermediate SPLSEL, DSP, DDP, and MTDIG can be described in any order.

## PLA Program Example

```

; * * * * PLA DEFINITION * * * *

PLA

SPLSEL 3

; RAM ADDR BIT #3

. . . SEGMENT PATTERN 0 ***

gfedcba

; 0

DSP

1000000B

1111001B

DSP

; 1

DSP

0100100B

DSP

0110000B

: 3

DSP

0011001B

: 4

DSP

0010010B

; 5

: 6

DSP

0000010B

; 7

DSP

1011000B

DSP

0000000B

; 8

DSP

0010000B

; 9

DSP

111111B

; BLANK

DSP

; E

0000110B

DSP

0111111B

; SEG G ON

DSP

1110111B

; SEG D ON

DSP

0011100B

; SEG A, B, F, G ON

DSP

0100011B

; SEG C. D. E. G ON

; * * * SEGMENT PATTERN

1 ...

; SEG ALL ON, KEY RETURN

DSP

0000000B

DSP

1111110B

; SEG A ON

; SEG B ON

DSP

1111101B

; SEG C ON

DSP

1111011B

DSP

1110111B

; SEG D ON

: SEG E ON

DSP

1101111B

; SEG F ON

DSP

1011111B

; SEG.G ON

DSP

0111111B

; SEG ALL OFF

DSP

1111111B

111111B

DSP

; NO USE

; NO USE

DSP

1111111B

; NO USE

DSP

1111111B

DSP

111111B

: NO USE

DSP

1111111B

; NO USE

DSP

1111111B

; NO USE

1111111B

; NO USE

DSP

END

```

## 7. µPD1730 INSTRUCTION

## 7.1 INSTRUCTION SET

|     | $\overline{}$ | _   | bis | b14 | 0                            | 0    | 0    | 1  |   | 1                   | 0                  | 11   |      |

|-----|---------------|-----|-----|-----|------------------------------|------|------|----|---|---------------------|--------------------|------|------|

| bıs | Ьız           | bii | b10 | /   | 0                            |      |      | 1  |   | 2                   |                    | 3    |      |

| 0   | 0             | 0   | 0   | 0   | NOP                          |      |      |    | _ | -                   |                    | ST   | М, г |

| 0   | 0             | 0   | 1   | 1   | SPB<br>BANK1<br>BANK2<br>STC | P. N | ORI  | M, | 1 | SEG                 | D <sub>H</sub> , r | MVRS | М, г |

| ٥   | 0             | 1   | 0   | 2   |                              |      | MVI  | M, | 1 | OUT                 | P, r               | IN   | r, P |

| 0   | 0             | 1   | 1   | 3   | RPB<br>BANKO<br>RSC          | P, N | ANI  | M, | ı | CKSTP               |                    | MVRD | г, М |

| 0   | 1             | 0   | 0   | 4   | RT                           |      | AI   | M, | I | MVSR                | M1, M2             | AD   | r, M |

| 0   | 1             | 0   | 1   | 5   | RTS                          |      | SI   | M, | 1 | EXL                 | r, M               | su   | r, M |

| 0   | 1             | 1   | 0   | 6   | JMP                          | ADDR | AIC  | M, | 1 | LD                  | г, М               | AC   | r, M |

| o   | 1             | 1   | 1   | 7   | CAL                          | ADDR | SIB  | M, | 1 |                     |                    | SB   | r, M |

| 1   | 0             | 0   | 0   | 8   | TPF<br>TCEF                  | P, N | AIN  | M, | I | TRS<br>TADT<br>TADF |                    | ADN  | r, M |

| 1   | 0             | 0   | 1   | 9   | TPT<br>TCET                  | P, N | SIN  | M, | I | ттм                 |                    | SUN  | r, M |

| 1   | 0             | 1   | 0   | A   | TMF                          | M, N | AICN | M, | 1 |                     |                    | ACN  | r, M |

| ı   | 0             | 1   | 1   | В   | тмт                          | M, N | SIBN | M, | I |                     |                    | SBN  | r, M |

| 1   | 1             | 0   | 0   | С   | SLTI                         | м, і | AIS  | M, | I | SLT                 | r, M               | ADS  | г, М |

| 1   | 1             | 0   | 1   | D   | SGEI                         | М, І | sis  | М, | I | SGE                 | r, M               | sus  | r, M |

| 1   | 1             | 1   | 0   | E   | SEQI                         | М, І | AICS | M, | I | SEQ                 | r, M               | ACS  | r, M |

| 1   | 1             | 1   | 1   | F   | SNEI                         | M, I | SIBS | M, | I | SNE                 | r, M               | SBS  | г, М |

### 7.2 INSTRUCTIONS

NOTE: Dn: Data memory address high (row address) [2 bits]

DL: Data memory address low (column address) [4 bits]

Ra: Register number [4 bits]

I: Immediate data [4 bits]

N : Bit position [4 bits]

ADDR: Program memory address [10 bits]

—: All "1"

r : General register

One of addresses 00-0FH of BANKO

M : Data memory address

P : Port, 0≤P≤3 N₁ : Bit position of status word 1 0≤N₁≤7 N<sub>2</sub> : Bit position of status word 2 0≤N₂≤7 ( ) : Content of register or memory

: Carry Borrow

: Decoded value of content of register of memories

|             | Mnemonic | Ope | rand | Function                                                              |                                                   |                | Machia         | e code         |    |

|-------------|----------|-----|------|-----------------------------------------------------------------------|---------------------------------------------------|----------------|----------------|----------------|----|

|             | Mnemonic | 1ST | 2ND  | r unction                                                             | Operation                                         | Operation code |                |                |    |

|             | AD       | r   | м    | Add memory to register                                                | r ← (r) + (M)                                     | 110100         | D <sub>M</sub> | DL             | Ra |

|             | ADS      | r   | М    | Add memory to register, then skip if carry                            | r ←(r) +(M)<br>skip if carry                      | 111100         | D <sub>N</sub> | DL             | Rn |

|             | ADN      | •   | М    | Add memory to register, then skip if not carry                        | r ← (r) + (M)<br>skip if not carry                | 111000         | D <sub>M</sub> | D <sub>L</sub> | Ra |

| ļ           | AC       | r   | M    | Add memory to register with carry                                     | $r \leftarrow (r) + (M) + c$                      | 110110         | D <sub>M</sub> | DL             | Ra |

|             | ACS      | r   | М    | Add memory to register with carry, then skip if carry                 | r ← (r) + (M) + c<br>skip if carry                | 111110         | D <sub>H</sub> | DL             | Rn |

| Addition    | ACN      | r   | M    | Add memory to register with carry, then skip if not carry             | $r \leftarrow (r) + (M) + c$<br>skip if not carry | 111010         | D <sub>H</sub> | D <sub>L</sub> | Rn |

| 3           | AI.      | М   | ī    | Add immediate data to memory                                          | M←(M)+1                                           | 010100         | D <sub>H</sub> | DL             | I  |

|             | AIS      | М   | ı    | Add immediate data to memory, then skip if carry                      | M←(M)+1<br>skip if carry                          | 011100         | D <sub>H</sub> | $D_L$          | I  |

|             | AIN      | M   | L    | Add immediate data to memory, then skip if not carry                  | M←(M)+1<br>skip if not carry                      | 011000         | D <sub>H</sub> | $D_L$          | 1  |

|             | AIC      | М   | 1    | Add immediate data to memory with carry                               | M ← (M) + [ + e                                   | 010110         | D <sub>M</sub> | DL             | ī  |

|             | AICS     | М   | 1    | Add immediate data with carry, then skip if carry                     | M←(M)+[+e<br>skip if carry                        | 011110         | D <sub>H</sub> | DL             | ī  |

| _           | AICN     | М   | 1    | Add immediate data with carry, then skip if not carry                 | M ← (M) + I + c<br>skip if not carry              | 011010         | D <sub>H</sub> | DL             | I  |

|             | su       | r   | М    | Subtract memory from register                                         | r ← (r) − (M)                                     | 110101         | D <sub>M</sub> | DL             | Ra |

|             | sus      | ,   | м    | Subtract memory from register, then skip if borrow                    | r ← (r) − (M)<br>skip if borrow                   | 111101         | D <sub>N</sub> | D <sub>L</sub> | Ra |

|             | SUN      | r   | М    | Subtract memory from register, then skip if not borrow                | r←(r) − (M)<br>skip if not borrow                 | 111001         | D <sub>H</sub> | DL             | Ra |

|             | SB       | r   | М    | Subtract memory from register with borrow                             | $r \leftarrow (r) - (M) - b$                      | 110111         | D <sub>H</sub> | D <sub>L</sub> | Rn |

|             | SBS      | ,   | M    | Subtract memory from register with<br>borrow, then skip if borrow     | + ←(r) − (M) − b<br>skip if borrow                | 111111         | D <sub>H</sub> | DL             | Ra |

| Subtraction | SBN      | r   | м    | Subtract memory from register with<br>borrow, then skip if not borrow | r ← (r) − (M) − b<br>skip if not borrow           | 111011         | D <sub>H</sub> | DL             | Ra |

| Subt        | SI       | М   | 1    | Subtract immediate data from memory                                   | M ← (M) − I                                       | 010101         | D <sub>H</sub> | DL             | 1  |

|             | SIS      | М   | 1    | Subtract immediate data from memory,<br>then skip if borrow           | M←(M) — [<br>skip if borrow                       | 011101         | D <sub>H</sub> | DL             | ī  |

|             | SIN      | М   | 1    | Subtract immediate data from memory, then skip if not borrow          | M←(M) — [<br>skip if not borrow                   | 011001         | D <sub>M</sub> | DL             | ı  |

|             | SIB      | М   | ı    | Subtract immediate data from memory, with borrow                      | M ← (M) − I − b                                   | 010111         | D <sub>H</sub> | DL             | ī  |

|             | SIBS     | М   | 1    | Subtract immediate data with borrow, then akip if borrow              | M ← (M) − [ − b<br>skip if borrow                 | 011111         | DH             | DL             | 1  |

|             | SIBN     | М   | 1    | Subtract immediate data with borrow, then skip if not borrow          | M ← (M) − I − b<br>skip not borrow                | 011011         | D <sub>H</sub> | DL             | ī  |

| Г          | Mnemonic | Ope | rand | Function                                                                | <del></del>                                                             |                | Machi          | ne code        |        |

|------------|----------|-----|------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|----------------|----------------|--------|

| ┕          |          | IST | 2ND  | runction                                                                | Operation                                                               | Operation code |                |                |        |

|            | SEQ      | r   | М    | Skip if register equal memory                                           | r —M<br>skip if zero                                                    | 101110         | D <sub>R</sub> | DL             | Ra     |

|            | SNE      | r   | м    | Skip if register not equals memory                                      | r — M<br>skip if not zero                                               | 101111         | D <sub>H</sub> | DL             | R,     |

|            | SGE      | r   | м    | Skip if register is greater than or equal to memory                     | r - M<br>skip if not borrow (r) ≥ (M)                                   | 101101         | D <sub>H</sub> | DL             | R.     |

| Comparison | SLT      | ,   | М    | Skip if register is less than memory                                    | r - M<br>skip if borrow (r) < (M)                                       | 101100         | D <sub>H</sub> | DL             | R,     |

| Smp        | SEQI     | м   | ı    | Skip if memory equals immediate data                                    | M — I<br>skip if zero                                                   | 001110         | D <sub>H</sub> | DL             | 1      |

|            | SNEI     | М   | ι    | Skip if memory not equal immediate data                                 | M — [<br>skip if not zero                                               | 001111         | D <sub>H</sub> | DL             | 1      |

|            | SGEI     | М   | 1    | Skip if memory is greater than or equal to immediate data               | M — I<br>skip if not borrow (M) ≥ I                                     | 001101         | D <sub>H</sub> | DL             | I      |

|            | SLTI     | м   | 1    | Skip if memory is less than immediate data                              | M − 1<br>skip if borrow (M) < 1                                         | 001100         | D <sub>H</sub> | DL             | 1      |

| operation  | ANI      | М   | 1    | Logic AND of memory and immediate data                                  | M←(M) ∧ I                                                               | 010011         | DH             | DL             | Ĩ      |

|            | ORI      | М   | I    | Logic OR of memory and immediate data                                   | M←(M) ∨ 1                                                               | 010001         | D <sub>k</sub> | DL             | I      |

| Logical    | EXL      | r   | м    | Exclusive OR Logic of memory and register                               | r ← (r) ⊕ (M)                                                           | 100101         | D <sub>H</sub> | D <sub>L</sub> | R,     |

|            | LD       | r   | м    | Load memory to register                                                 | r⊷(M)                                                                   | 100110         | D <sub>H</sub> | D <sub>L</sub> | R,     |

|            | ST       | М   | r    | Store register to memory                                                | M ← (r)                                                                 | 110000         | D <sub>H</sub> | DL             | R,     |

|            | MVRD     | r   | М    | Move memory to destination memory referring to register in the same row | [D <sub>H</sub> , R <sub>n</sub> ]←(M)                                  | 110011         | D <sub>H</sub> | DL             | R.     |

| Transfer   | MVRS     | М   | r    | Move source memory referring to register to memory in the same row      | M ← [D <sub>H</sub> , R <sub>n</sub> ]                                  | 110001         | D <sub>H</sub> | DL             | R,     |

| [          | MVSR     | Mı  | Mz   | Move memory to memory in the same row                                   | [D <sub>H</sub> , DL <sub>1</sub> ]←[D <sub>H</sub> , DL <sub>2</sub> ] | 100100         | D <sub>H</sub> | DLI            | Du     |

|            | MVI      | м   | 1    | Move immediate data to memory                                           | M ← I                                                                   | 010010         | DH             | DL             | 1      |

| test       | TMT      | М   | N    | Test memory bits, then skip if all bits specified are true              | if M(N)=all "1", then skip                                              | 001011         | D <sub>H</sub> | DL             | N      |

| ĕ          | TMF      | М   | N    | Test memory bits, then skip all bits specified are false                | if M(N) = all *0", then skip                                            | 001010         | D <sub>H</sub> | DL             | N      |

| Jump       | JMP      | AD  | DR   | Jump to the address specified                                           | PC-ADDR                                                                 | 000110         |                | ADDR (10       | bits). |

| 2          | CAL      | AD  | DR   | Call subroutine                                                         | Stack←(PC) + 1, PC←ADDR                                                 | 000111         |                | ADDR (10       | bits)  |

| Subroutine | RT       |     |      | Return to main routine                                                  | PC←(stack)                                                              | 000100         | _              | _              | _      |

| Ľ          | RTS      |     |      | Return to main routine, then skip<br>unconditionary                     | PC←(stack), and skip                                                    | 000101         | -              | _              | _      |

| 7/ P       | ттм      |     |      | Test and reset timer F/F, then skip if it has not been set              | if Timer F/F=1, then Timer F/F←0<br>if Timer F/F=0, then skip           | 101001         | _              | -              |        |

| Г          | Macmonic  | Ope            | rand |                                                                 | 1                                                                                                                 | Ι .            | Machin | e code |      |

|------------|-----------|----------------|------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|--------|--------|------|

| L.         | Misemonic | IST            | 2ND  | Function                                                        | Operation                                                                                                         | Operation code |        |        |      |

|            | STC       |                |      | Set carry F/F                                                   | carry F/F← 1                                                                                                      | 000001         | -      | 0010   | ı    |

| .          | RSC       |                |      | Reset carry F/F                                                 | carry F/F 1                                                                                                       | 000011         | _      | 0010   | ı    |

| inal best  | BANKO     |                |      | Select BANKO                                                    | BANK F/F0 ← 0, BANK F/F1 ← 0                                                                                      | 000011         | 1      | 1100   |      |

| d terminal | BANKI     |                |      | Select BANK1                                                    | BANK F/F0 ← 1, BANK F/F1 ← 0                                                                                      | 000001         | -      | 0100   | -    |

| 20 E       | BANK2     |                |      | Select BANK2                                                    | BANK F/F0 ← 0, BANK F/F1 ← 1                                                                                      | 000001         | -      | 1000   | _    |

| States w   | TCET      |                |      | Test CE, skip if true                                           | if CE = 1, then skip                                                                                              | 001001         | 1      | 0010   | -    |

| ~          | TCEF      |                |      | Test CE, skip if false                                          | if CE = 0, then skip                                                                                              | 001000         | -      | 0010   | 1    |