# **NEC** NEC Electronics

#### Description

The µPD2167 is a 16,384-word by 1-bit static MOS RAM. Using a scaled-NMOS technology, its design provides the easy-to-use features associated with nonclocked static memories.

The  $\mu$ PD2167 has a three-state output and offers a standby mode that features an 83% savings in power consumption. The  $\mu$ PD2167 requires a single +5 volt supply and is fully TTL-compatible. It features equal access and cycle times and, because of its fully static operation, it requires no external clocks or timing strobes. It is packaged in a standard 20-pin, 300 mil DIP.

#### Features

- ☐ 16384 x 1 organization

- ☐ Fully static memory no clock or timing

- strobe required

- Equal access and cycle times

- ☐ Single +5V supply

- ☐ Automatic power-down☐ Standard 20-pin DIP, 300 mil

- ☐ All inputs and output directly TTL-compatible

- ☐ Separate data input and output

- ☐ Three-state output

- Power dissipation: 180 mA max (active)

30 mA max (standby)

- 2 performance ranges:

|           |                   | Power Supply |         |  |  |

|-----------|-------------------|--------------|---------|--|--|

| Device    | Access/CycleTime- | Active       | Standby |  |  |

| μPD2167-3 | 55ns              | 180mA        | 30mA    |  |  |

| μPD2167-2 |                   | 180mA        | 30mA    |  |  |

## **Pin Configuration**

# Pin Identification

| P             | ln                              |                   |

|---------------|---------------------------------|-------------------|

| No.           | Symbol                          | Description       |

| 1-7,<br>13-19 | A <sub>0</sub> -A <sub>13</sub> | Address Inputs    |

| 8             | D <sub>OUT</sub>                | Data Output       |

| 9             | WE                              | Write Enable      |

| 10            | GND                             | Ground            |

| 11            | CS                              | Chip Select       |

| 12            | D <sub>IN</sub>                 | Data Input        |

| 20            | V <sub>CC</sub>                 | + 5V Power Supply |

#### **Truth Table**

| cs       | WE | Mode         | Output | Power   |  |  |

|----------|----|--------------|--------|---------|--|--|

| H        | х  | Not selected | High-Z | Standby |  |  |

| <u> </u> | L  | Write        | High-Z | Active  |  |  |

| Ĺ        | н  | Read         | Dour   | Active  |  |  |

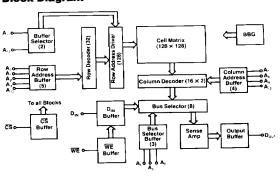

#### **Block Diagram**

## **Absolute Maximum Ratings\***

| -10°C to +85°C  |  |  |

|-----------------|--|--|

| -65°C to +150°C |  |  |

| -3.5V to +7V    |  |  |

| 20mA            |  |  |

| 1.2W            |  |  |

|                 |  |  |

\*Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Capacitance T.=25°C.f=1.0 MHz

| Parameter          | Symbol | Max. | Unit | Test<br>Conditions    |  |

|--------------------|--------|------|------|-----------------------|--|

| Input Capacitance  | Cin    | 5    | рF   | V <sub>OUT</sub> = 0V |  |

| Output Capacitance | Cour   | 6    | pF   | V <sub>IN</sub> = 0V  |  |

Note: This parameter is sampled and not 100% tested.

Rev/2

4 - 13

## **DC Characteristics** $T_A = 0^{\circ}C$ to +70°C, $V_{CC} = +5V \pm 10\%$

| Parameter                               | Syn                    | n Mir | тур  | Max | Unit       | Test<br>Condition                                                                    | ns                                              |  |  |

|-----------------------------------------|------------------------|-------|------|-----|------------|--------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| Input load<br>current<br>all input pins | I <sub>LI</sub>        |       |      | 10  | μ <b>Α</b> | V <sub>cc</sub> = max,<br>V <sub>iN</sub> = GND to V <sub>cc</sub>                   |                                                 |  |  |

| Output<br>leakage<br>current            | ILO                    |       | 0.1  | 50  | μΑ         | CS = V <sub>IH</sub> ,<br>V <sub>CC</sub> = max<br>V <sub>OUT</sub> = GN             | t,<br>ID to V <sub>cc</sub>                     |  |  |

| Operating<br>current                    | Icc                    |       |      | 170 | mA         |                                                                                      | V <sub>CC</sub> = max,<br>CS= V <sub>IL</sub> , |  |  |

|                                         |                        |       |      | 180 | mΑ         | $T_A = 0^{\circ}C$                                                                   | output oper                                     |  |  |

| Standby current                         | I <sub>SB</sub>        |       |      | 30  | mA         | V <sub>CC</sub> = min<br>CS = V <sub>IH</sub>                                        | to max,                                         |  |  |

| Peak<br>Power-On<br>current             | leo (1                 | )     | 35   | 70  | mA         | $V_{cc}$ = GND to $V_{cc}$ mln. $\overline{CS}$ = Lower of $V_{cc}$ or $V_{iH}$ min. |                                                 |  |  |

| Input low voltage                       | V <sub>IL</sub>        | -3.0  |      | 8.0 | ٧          |                                                                                      |                                                 |  |  |

| Input high<br>voltage                   | V <sub>IH</sub>        | 2.0   |      | 6.0 | ٧          |                                                                                      |                                                 |  |  |

| Output<br>low voltage                   | VoL                    | ,     |      | 0.4 | ٧          | I <sub>oL</sub> =8 mA                                                                |                                                 |  |  |

| Output high voltage                     | <b>V</b> <sub>OH</sub> | 2.4   |      |     | ٧          | I <sub>OH</sub> = -4 m                                                               | A                                               |  |  |

| Output short<br>circuit current         | I <sub>osi</sub>       |       | -150 |     | mA         | V <sub>OUT</sub> = GNI                                                               | )                                               |  |  |

| Output short circuit current            | I <sub>OS2</sub>       |       | 150  |     | mA         | $\mathbf{V}_{OUT} = \mathbf{V}_{CC}$                                                 |                                                 |  |  |

Note: ① CS valid prior to or coincident with address transition

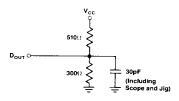

Figure 1. Loading Conditions Test Circuit

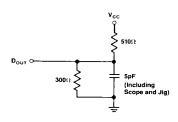

Figure 2. Input Pulse Test Circuit

### **AC Characteristics** $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = +5V \pm 10\%$

| Parameter                               | 8.              | μ_                | PD21 | PD2167-3 µ |      |     | μPD2167-2 |        | M-4  |

|-----------------------------------------|-----------------|-------------------|------|------------|------|-----|-----------|--------|------|

| - arameter                              | ЭУ              | m <u>μ</u><br>Min | Тур  | Max        |      | Тур | Max       | - Unit | Note |

|                                         |                 |                   | Rea  | ad Cy      | cle  |     |           |        |      |

| Read cycle<br>time                      | t <sub>RC</sub> | 55                |      |            | 70   |     |           | ns     |      |

| Address<br>access time                  | t <sub>AA</sub> |                   |      | 55         | , at |     | 70        | ns     | ①    |

| Chip select access time                 | t <sub>AC</sub> | s                 |      | 55         |      |     | 70        | ns (   | 2    |

| Output hold<br>from address<br>change   | t <sub>oн</sub> | 5                 |      |            | 5    |     |           | ns     | -    |

| Chip select<br>to output in<br>low-Z    | t <sub>LZ</sub> | 10                |      |            | 10   |     |           | ns     |      |

| Chip deselect<br>to output in<br>high-Z | t <sub>HZ</sub> | 0                 |      | 40         | 0    |     | 40        | ns     |      |

| Chip select<br>to power-up<br>time      | t <sub>PU</sub> | 0                 |      | -          | 0    |     |           | ns     |      |

| Chip deselect<br>to power-down<br>time  | t <sub>PD</sub> |                   | 30   |            |      | 30  |           | ns     |      |

|                                         |                 |                   | Writ | e Cy       | cle  |     |           |        |      |

| Write cycle time                        | twc             | 55                |      |            | 70   |     |           | ns     |      |

| Chip select to<br>end of write          | t <sub>cw</sub> | 45                |      |            | 55   |     | -         | ns     |      |

| Address valid to<br>end of write        | t <sub>AW</sub> | 45                |      |            | 55   |     |           | ns     |      |

| Address setup<br>time                   | t <sub>AS</sub> | 0                 |      |            | 0    |     |           | ns     |      |

| Write pulse                             | twe             | 35                |      |            | 40   |     |           | ns     |      |

| Write recovery<br>time                  | twR             | 10                |      |            | 15   |     |           | ns     |      |

| Data valid to<br>end of write           | tow             | 25                |      |            | 30   |     |           | ns     |      |

| Data hold time                          | t <sub>DH</sub> | 10                |      |            | 10   |     |           | ns     |      |

| Write enabled to<br>output in high-Z    | t <sub>wz</sub> | 0                 |      | 30         | 0    |     | 35        | ns     |      |

| Output active<br>rom end of write       | tow             | 0                 |      |            | 0    |     |           | ns     |      |

Notes: ①  $\overline{CS}$  valid prior to or coincident with address transition ② Address valid prior to or coincident with  $\overline{CS}$  transition low

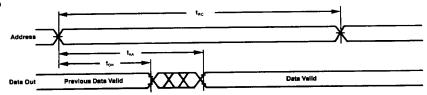

## **Timing Waveforms**

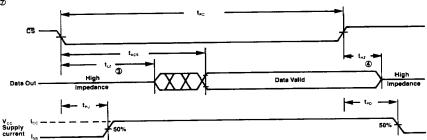

#### Read Cycle 1 5 6

#### Read Cycle 2 5 7

Notes: ① All Read Cycle timings are referenced from the last valid address to the first address in transition.

- At any given temperature and voltage condition, t<sub>HZ</sub> max is less than t<sub>LZ</sub> min both for a given device and from device to device.

Transition is measured + 200mV from steady state voltage with specified loading in Figure 2.

Transition is measured at V<sub>OL</sub> + 200mV and V<sub>OH</sub> 200mV with specified loading in Figure 2.

- WE is high for Read Cycles.

Device is continuously selected, \( \overline{CS} = V\_{ii}. \)

- Addresses valid prior to or coincident with CS transition low.

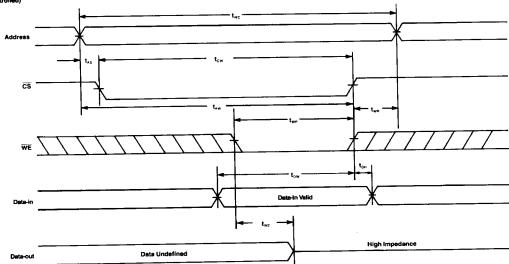

#### Write Cycle ① ② ③ ④

(CS Controlled)

- Notes: ① If CS goes high simultaneously with WE high, the output remains in a high impedance state.

② All Write Cycle timings are referenced from the last valid address to the first transitioning address.

- $\odot$  Transition is measured at  $V_{ot}$  +200 mV and  $V_{oh}$  -200 mV with specified loading in Figure 2.  $\odot$  Transition is measured  $\pm$ 200 mV from steady state voltage with specified loading in Figure 2.

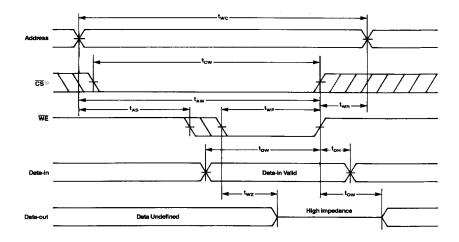

# Timing Waveforms (Cont.)

Write Cycle (WE Controlled)

## **Package Outlines**

For information, see Section 9.

Ceramic, µPD2167D

2167DS-REV2-7-83-CAT-L