## 1.8 to 5.5 V BIAS, 80 MHz to 550 MHz DUAL PLL FREQUENCY SYNTHESIZER LSI FOR CORDLESS TELEPHONES AND PORTABLE CELLULAR RADIO

#### DESCRIPTION

NEC

$\mu$ PD3140GS is a dual PLL frequency synthesizer LSI designed for cordless telephones and portable cellular radio. This LSI is manufactured using 13 GHz fr BiCMOS process and integrated 2 pairs of prescaler + PLL operate from 80 MHz to 550 MHz. This LSI realizes low power consumption: on 1.8 V, 4.3 mA at dual operation and 2.7 mA at single operation. The additional functions are high-speed lockup and lock phase sensitivity setting. The package is a 20-pin SSOP (300 mil) suitable for high-density surface mounting. Thus, this product contributes to produce physically-small, low power-consumption, long-life battery systems.

## FEATURES

- Supply voltage: Vcc1 = Vcc2 = 1.8 to 5.5 V

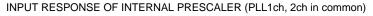

- Input operating frequency: fin = 80 MHz to 550 MHz (PLL 1ch, 2ch in common)

- Reference oscillating frequency fref = 30 MHz MAX.. Built-in high-speed reference oscillator signal can be taken out from the buffer amplifier output pin.

- Built-in power-save function: control 2 prescaler's ON/OFF operation individually.

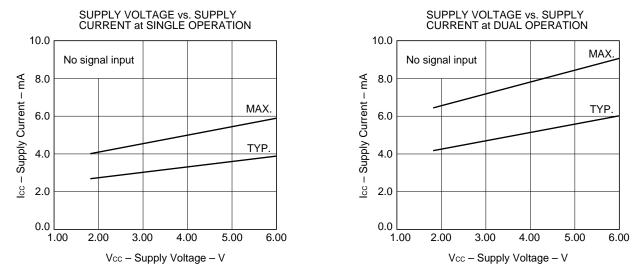

- Low power consumption: Dual operation (both ch ON): Icc OP2 = 4.3 mA TYP. @ Vcc = 1.8 V Single operation (either ch ON): Icc OP1 = 2.7 mA TYP. @ Vcc = 1.8 V

Power save mode (both ch OFF): Icc PS = 10  $\mu$ A MAX. @ Vcc = 1.8 V

- Decreased lockup time available: charge pump switch control (lockup time: 9 ms @ fstep = 12.5 kHz, 1 MHz swing, decreased lockup time mode).

- Lock phase sensitivity programmable: Phase difference allowance for lock up can be controlled as 4 stages (150 ns to 5  $\mu$ s).

- Pins and counter data are compatible to µPD2844BGS (except option data).

- High-density surface mounting: 20-pin plastic SSOP.

#### **ORDERING INFORMATION**

| PARTS NUMBER | PACKAGE                          | SUPPLYING FORM                                                                  |

|--------------|----------------------------------|---------------------------------------------------------------------------------|

| μPD3140GS-E1 | 20 pin plastic SSOP<br>(300 mil) | Embossed tape 16 mm wide. QTY 2.5 k/reel<br>Pin1 is in tape pull-out direction. |

| μPD3140GS-E2 |                                  | Embossed tape 16 mm wide. QTY 2.5 k/reel<br>Pin1 is in tape roll-in direction.  |

| μPD3140GS-T1 |                                  | Adhesive tape 32 mm wide. QTY 2 k/reel<br>Pin1 is in tape pull-out direction.   |

| μPD3140GS-T2 |                                  | Adhesive tape 32 mm wide. QTY 2 k/reel<br>Pin1 is in tape roll-in direction.    |

\* To order evaluation sample, please contact your local NEC sales office (Order number : µPD3140GS).

Caution: Electro-static sensitive device

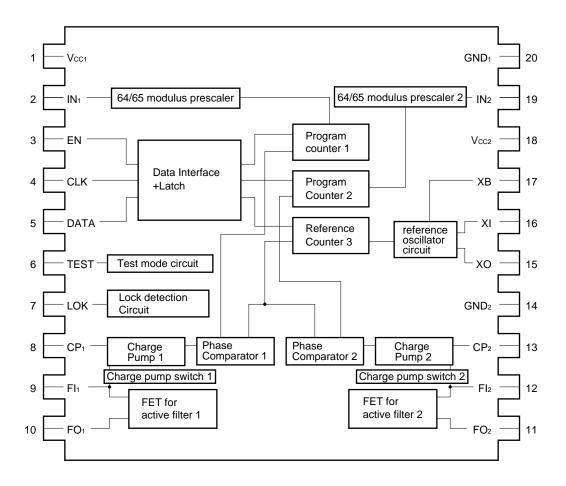

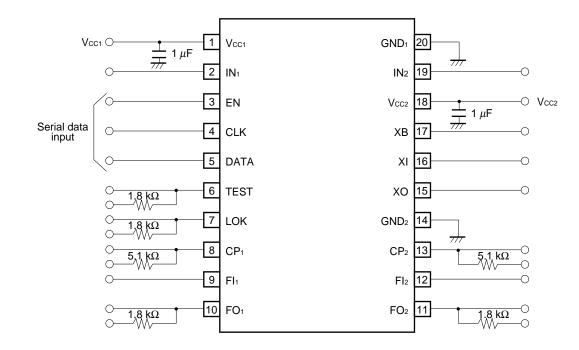

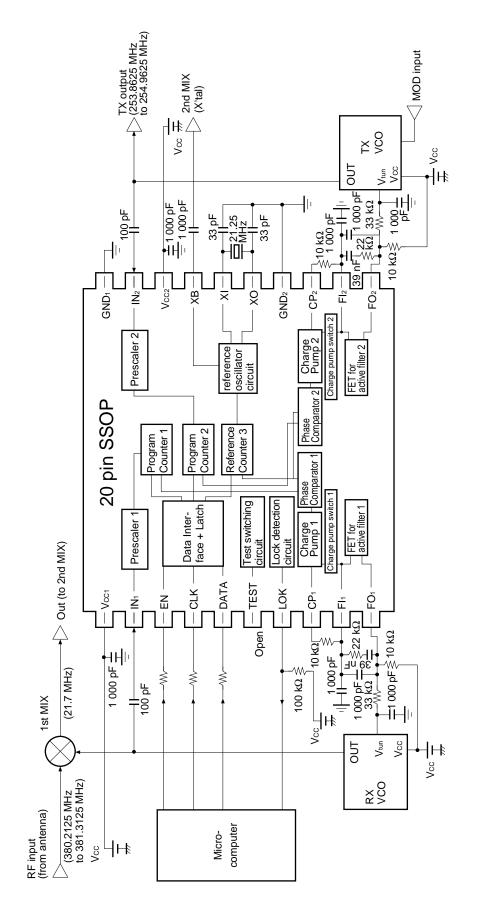

## INTERNAL BLOCK DIAGRAM

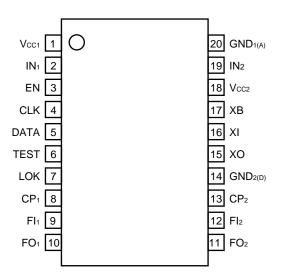

#### **PIN ASSIGNMENT (Top View)**

## **PIN EXPLANATIONS**

| PIN No. | SYMBOL | EXPLANATIONS                                                                                                                                                                                                                   |                           |  |  |  |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

| 1       | Vcc    | Supply voltage for analog block and 2 prescalers                                                                                                                                                                               |                           |  |  |  |

| 2       | IN1    | Input for 64/65 modulus prescaler. This pin must be coupled with a capacitor (e.g. 1 000 pF).                                                                                                                                  |                           |  |  |  |

| 19      | IN2    | IN1: prescaler input for PLL1ch<br>IN2: prescaler input for PLL2ch                                                                                                                                                             |                           |  |  |  |

| 3       | EN     | Load enable data input pin                                                                                                                                                                                                     |                           |  |  |  |

| 4       | CLK    | Clock data input pin                                                                                                                                                                                                           |                           |  |  |  |

| 5       | DATA   | Data input pin                                                                                                                                                                                                                 |                           |  |  |  |

| 6       | TEST   | Test pin (Refer to page 8). Used as PLL, this pin should be                                                                                                                                                                    | grounded.                 |  |  |  |

| 7       | LOK    | Lock detecter output pin. This pin is designed as open drain<br>Relation between operation mode and conditions to output i                                                                                                     |                           |  |  |  |

|         |        | OPERATE MODE CONDITION TO OUTPUT LOCK                                                                                                                                                                                          | LOCK OUTPUT               |  |  |  |

|         |        | SINGLE OPERATION 1 PLL LOCKED                                                                                                                                                                                                  |                           |  |  |  |

|         |        | DUAL OPERATION 2 PLL LOCKED                                                                                                                                                                                                    | LOW (SINK)                |  |  |  |

|         |        | (In other case, LOK pin output high as unlock.)                                                                                                                                                                                |                           |  |  |  |

| 8       | CP1    | Charge pump output pin.                                                                                                                                                                                                        |                           |  |  |  |

| 13      | CP2    | CP1: Charge pump output from PLL1ch<br>CP2: Charge pump output from PLL2ch                                                                                                                                                     |                           |  |  |  |

| 9       | FI1    | Gate input pin of active filter's FET                                                                                                                                                                                          | Example for active filter |  |  |  |

| 12      | FI2    | Also function as charge pump switch output pin.<br>FI1: for PLL1ch<br>FI2: for PLL2ch                                                                                                                                          |                           |  |  |  |

| 10      | FO1    | Drain output of active filter's FET<br>FO1: for PLL1ch                                                                                                                                                                         |                           |  |  |  |

| 11      | FO2    | FO2: for PLL2ch<br>In the case of passive filter, these pins should be opened.                                                                                                                                                 | from CPSW IC              |  |  |  |

| 14      | GND2   | Ground pin of PLL digital block (PLL 1ch, 2ch in common)                                                                                                                                                                       |                           |  |  |  |

| 15      | ХО     | Reference oscillator for both PLL                                                                                                                                                                                              | Oscillation amplifier     |  |  |  |

| 16      | XI     | XO : output<br>XI : input<br>These pins should be externally equipped with crystal.<br>In the case of TCXO, input to XI pin through coupling<br>capacitor (e.g. 1 000 pF).<br>VIN = 0.2 Vp-p to 1.0 Vp-p, fmax = 30.0 MHz MAX. |                           |  |  |  |

| 17      | ХВ     | Buffer output pin from reference oscillator<br>From<br>REF.<br>OSC.                                                                                                                                                            |                           |  |  |  |

| 18      | VCC2   | Supply voltage for PLL digital block (PLL 1ch, PLL 2ch in cc                                                                                                                                                                   |                           |  |  |  |

|         | GND1   | Ground pin of analog block and 2 prescalers                                                                                                                                                                                    |                           |  |  |  |

## ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25 $^{\circ}$ C)

| Supply Voltage        | VCC1, VCC2, VF0 | -0.3 to +6.0 | V  |

|-----------------------|-----------------|--------------|----|

| Circuit Current       | lcc             | 40           | mA |

| Operating Temperature | Topt            | -35 to +85   | °C |

| Storage Temperature   | Tstg            | -40 to +125  | °C |

#### **RECOMMENDED OPERATING RANGE**

| PARAMETER             | SYMBOL          | OPERATING RANGE   | UNIT | Note        |

|-----------------------|-----------------|-------------------|------|-------------|

| Supply Voltage        | Vcc1, Vcc2, VF0 | 1.8 to 2.0 to 5.5 | V    | Vcc1 = Vcc2 |

| Operating Temperature | Topt            | -35 to +25 to +85 | °C   |             |

## ELECTRICAL CHARACTERISTICS (Unless otherwise specified; Vcc = 1.8 to 5.5 V, T<sub>A</sub> = -35 to +85 °C)

| PARAMETER                               | SYMBOL             | MIN.     | TYP. | MAX.          | UNIT  | CONDITIONS                                                            |

|-----------------------------------------|--------------------|----------|------|---------------|-------|-----------------------------------------------------------------------|

| Circuit Current 1 (OP1)                 | IccOP1             |          | 2.7  | 4.1           | mA    | $V_{CC}$ = 1.8 V, +25 °C, total current of single operation           |

| Circuit Current 2 (OP2)                 | IccOP2             |          | 4.3  | 6.6           | mA    | Vcc = 1.8 V, +25 °C, total current of dual operation                  |

| Circuit Current 3 (PS)                  | IccPS              | _        | 0    | 10            | μA    | Vcc = 1.8 V, total current during power saving                        |

|                                         |                    |          | 0    | 10            | μη    | (both channels: off)                                                  |

| Circuit Current 1' (OP1')               | IccOP1'            |          | 3.5  | 5.3           | mA    | $V_{CC}$ = 5 V, +25 °C, total current of single operation             |

| Circuit Current 2' (OP2')               | IccOP2'            |          | 5.6  | 8.6           | mA    | $V_{CC}$ = 5 V, +25 °C, total current of dual operation               |

| High Level Input Voltage                | Vн                 | Vcc ×0.7 |      | Vcc + 0.5     | V     | EN, CLK, DATA pins                                                    |

| Low Level Input Voltage                 | VL                 | -0.5     |      | Vcc 	imes 0.3 | V     | EN, CLK, DATA pins                                                    |

| Input Operating Frequency               | fin                | 200      | _    | 550           | MHz   | $V_{in} = -12$ to 0 dBm, @ pins 2 and 19                              |

|                                         | IIN                | 80       | -    | 200           |       | $V_{\text{in}}$ = -8 to 0 dBm, @ pins 2 and 19 $^{\text{Note}}$       |

| Reference Frequency                     | fref               | -        | -    | 30            | MHz   | V <sub>in</sub> = 0.2 to 1.0 V, @ pin 16                              |

| Crystal Oscillation Stability           | X t stb            | -4       |      | +4            | ppm   | Application circuit: $f_{ref} = 21.25 \text{ MHz}$ ,                  |

|                                         | A I SID            | -4       | -    | 74            | ppm   | Vcc1, Vcc2 constant                                                   |

| Crystal Oscillation Rise Time           | X t frt            | -        | 10   | 20            | ms    | Application circuit: $f_{ref} = 21.25 \text{ MHz}, \pm 4 \text{ ppm}$ |

| Reference Oscillator Buffer Output      | V xb               |          | -3   |               | dBm   | Application circuit: fref = 21.25 MHz,                                |

| Level                                   | V X5               |          | 5    |               | ubiii | $R_L = 1 \ k\Omega$                                                   |

| Charge Pump and FI pin Leak Current     | CPLEAK             | -20      | 0    | 20            | nA    | T <sub>A</sub> = +25 °C, CP & FI pins, CP state: high impedance       |

| Charge Pump Output Current 1            | CPI000             |          | 10   |               | μA    | Vcc = 2 V, CPH/L common, CP data: 000                                 |

| Charge Pump Output Current 2            | CPI001             |          | 30   |               | μA    | Vcc = 2 V, CPH/L common, CP data: 001                                 |

| Charge Pump Output Current 3            | CPI010             |          | 100  |               | μA    | Vcc = 2 V, CPH/L common, CP data: 010                                 |

| Charge Pump Output Current 4            | CPI100             |          | 300  |               | μA    | Vcc = 2 V, CPH/L common, CP data: 100                                 |

| Charge Pump Output Voltage              | CPV111             | -        | 0.1  |               | V     | $V_{CC}$ = 2 V, CP current = ±500 $\mu$ A, CP data: 111               |

| Phase difference allowance for lockup 1 | LOPW <sub>00</sub> |          | 5.0  |               | μs    | Vcc = 2 V, LO data: 00                                                |

| Phase difference allowance for lockup 2 | LOPW <sub>10</sub> |          | 1.5  |               | μs    | Vcc = 2 V, LO data: 10                                                |

| Phase difference allowance for lockup 3 | LOPW <sub>01</sub> |          | 500  |               | ns    | Vcc = 2 V, LO data: 01                                                |

| Phase difference allowance for lockup 4 | LOPW11             |          | 150  |               | ns    | Vcc = 2 V, LO data: 11                                                |

| Clock Rate                              | Crate              | 1.0      | _    | -             | μs    | EN, CLK, DATA pins                                                    |

**Note:** Refer to AC characteristic's Guaranteed operating range (page 12)

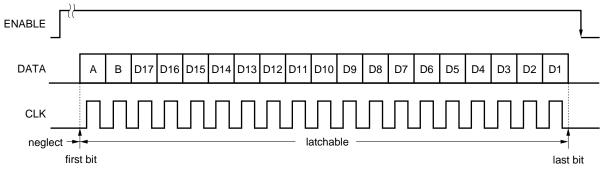

## DATA FORMAT

Note: Data can be clocked in at falling edge of the CLK. Latest 19 bits data before  $EN:H \rightarrow L$  can be latched.

#### 1. Relation between A, B data and setting data content

| Α | В | Setting data content                         |

|---|---|----------------------------------------------|

| 0 | 0 | PLL 1ch (2 pin input) N counter data         |

| 0 | 1 | PLL 2ch (19 pin input) N counter data        |

| 1 | 0 | Option data                                  |

| 1 | 1 | Reference counter data (PLL 1ch, 2ch common) |

Remarks: Stable operation against same N counter data latched.

#### 2. Counter data

• A, B = 0, 0 or 0, 1

PLL1ch, 2ch N counter Number : N =  $D17 \times 2^{16} + D16 \times 2^{15} + D15 \times 2^{14} + D14 \times 2^{13} + D13 \times 2^{12} + D12 \times 2^{11} + D11 \times 2^{10} + D10 \times 2^9 + D9 \times 2^8 + D8 \times 2^7 + D7 \times 2^6 + D6 \times 2^5 + D5 \times 2^4 + D4 \times 2^3 + D3 \times 2^2 + D2 \times 2^1 + D1 \times 2^0$

Note: Continuous setting range = 4 096 to 131 071 ('1' should be set to any of D13 to D17 data.)

• A, B = 1, 1

$\begin{array}{l} \mbox{Reference Counter Number}: R = D11 \times 2^{11} + D10 \times 2^{10} + D9 \times 2^9 + D8 \times 2^8 + D7 \times 2^7 + D6 \times 2^6 + D5 \times 2^5 + D4 \times 2^4 + D3 \times 2^3 + D2 \times 2^2 + D1 \times 2^1 \end{array}$

Note: Setting range : 64 to 4 094 (Continuous even numbers can be set.)

#### 3. Option settings (A, B = 1, 0)

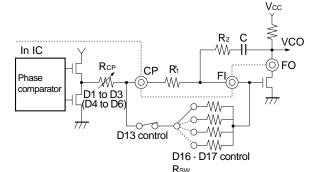

<1> D1 to D6: Charge pump driving capability setting (CP data)

| D3   | D2   | D1   | Cha        | arge pump driving | capability       |

|------|------|------|------------|-------------------|------------------|

| (D6) | (D2) | (D4) |            | Output            | Output           |

|      | (20) |      | capability | Current           | resistance Value |

| 0    | 0    | 0    | weak       | 10 <i>µ</i> A     | 100 kΩ           |

| 0    | 0    | 1    |            | 30 <i>µ</i> A     | 33 kΩ            |

| 0    | 1    | 0    |            | 100 <i>μ</i> Α    | 10 kΩ            |

| 0    | 1    | 1    |            | 130 <i>μ</i> Α    | 7.7 kΩ           |

| 1    | 0    | 0    |            | 300 <i>µ</i> A    | 3.3 kΩ           |

| 1    | 0    | 1    |            | 330 <i>µ</i> A    | 3 kΩ             |

| 1    | 1    | 0    |            | 400 <i>µ</i> A    | 2.5 kΩ           |

| 1    | 1    | 1    | strong     | Voltage output    | 0.5 kΩ           |

Output resistance values are typical at Vcc = 2 V.

2 D1 to D3: PLL1ch data D4 to D6: PLL2ch data

<2> D7: Charge pump polarity (PLL 1ch, 2ch common)

|    | Input phase stat |               |                |                |

|----|------------------|---------------|----------------|----------------|

| D7 | phase advanced   | phase delayed | Sychronized    | Filter Type    |

| 0  | Low              | High          | High impedance | Passive filter |

| 1  | High             | Low           | High impedance | Active filter  |

<sup>&</sup>lt;3> D8, D9: Prescaler ON/OFF control

| D8 | D9 | PLL1ch | PLL2ch |

|----|----|--------|--------|

| 0  | 0  | OFF    | OFF    |

| 0  | 1  | OFF    | ON     |

| 1  | 0  | ON     | OFF    |

| 1  | 1  | ON     | ON     |

| -  |    |        |        |

| <4> | D11, 12: Lock phase | sensitivity setting | (PLL1 ch, 2 cl | h in common) |

|-----|---------------------|---------------------|----------------|--------------|

|-----|---------------------|---------------------|----------------|--------------|

| D11 | D12 | Lock Phase sensitivity |

|-----|-----|------------------------|

| 0   | 0   | 5.0 <i>μ</i> s         |

| 1   | 0   | 1.5 <i>μ</i> s         |

| 0   | 1   | 500 ns                 |

| 1   | 1   | 150 ns                 |

Phase difference allowance for lock up, Input signal phase against reference signal phase.

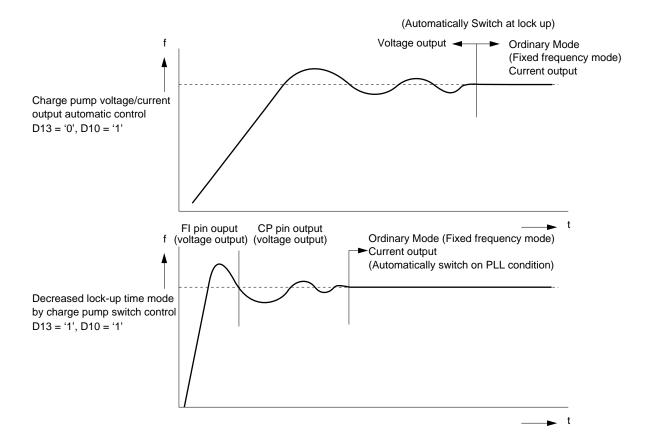

<5> D10: Charge pump voltage/current output automatic control mode (PLL1ch, 2ch in common)

| D10 | CP data D1 to D3 | Lock condition | PLL 1ch        |

|-----|------------------|----------------|----------------|

|     |                  | UNLOCK         |                |

| 0   | 0 except 111     | LOCK           | Current Output |

| 4   | august 444       | UNLOCK         | Voltage Output |

| 1   | except 111       | LOCK           | Current Output |

\* CP data D4 to D6 : PLL 2ch

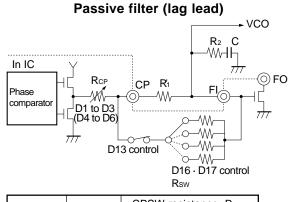

#### Recommendable Application of CP V/I output control mode

- 1. External loop filter should be designed as minimum lock-up time at D1-D3, D4-D6 = (111).

- Desired C/N and loop cut-off frequency should be optimized with chosen CP current data 000 to 110. This mode is called 'fixed frequency mode'.

- 3. On D10 = 1 setting, lock up mode and fixed frequency mode can be switched automatically.

- <6> D13 to D17: Charge pump switch control (decreased lock up time) mode: PLL 1ch, PLL 2ch in common

- D13: charge pump switch control

| D10 | D13 | CPSW              |  |

|-----|-----|-------------------|--|

| 4   | 1   | ON *1             |  |

| 1   | 0   | OFF <sup>*2</sup> |  |

| 0   | 1   | 055*2             |  |

|     | 0   | OFF <sup>*2</sup> |  |

\*1 Output route can be controlled as 'CPSWout (Flpin)  $\rightarrow$  CPout'. \*2 CPout only

| D14 | D15 | CPSW out polarity reverse time |

|-----|-----|--------------------------------|

| 0   | 0   | 1 time                         |

| 0   | 1   | 2 times                        |

| 1   | 0   | 4 times                        |

| 1   | 1   | 8 times                        |

| D16 | D17 | CPSW resistance: Rsw<br>(MOS: ON resistance) |

|-----|-----|----------------------------------------------|

| 0   | 0   | 150 Ω                                        |

| 0   | 1   | 500 Ω                                        |

| 1   | 0   | 1.5 kΩ                                       |

| 1   | 1   | 5.0 kΩ                                       |

After CPSW out polarity reverse time, output route will be switched from FI pin to CP pin.

#### Recommendable Application of decreased lock up time by CPSW control mode

This mode can realize faster lock up than CP V/I output control mode.

- For sweep to adjacent frequency, CP V/I output control mode should be used.

- For rise-up from power save mode, decreased lock up time mode should be used.

- Charge pump switch resistance should be chosen at (D10, D13) = (1, 1), (D14, D15) = (0, 0).

- After charge pump switch resistance is fixed, polarity reverse time should be chosen. Note: On passive filter application, FI pin should be used as a charge pump switch output pin.

#### SCHEMATICS FOR LOCKUP MOVEMENT

#### NOTICE FOR DESIGNING LOOP FILTER

For automatic switching on decreased lock up time mode, loop filter should be designed to suppress fluctuation of the loop gain among three modes. For example, the CP-FI resistor (R'1) may be determined as 10 k $\Omega$  to 30 k $\Omega$ .

#### **TEST MODE SETTING**

- 1. Test mode can be set at (Vcc2 other bias)  $\geq$  1.5 V

- For example, other bias = 2 V,  $Vcc_2 = 3.5 V$ .

- 2. Test mode gives us operation monitoring of each block as follows:

- <1> Test mode 1

- PLL 1ch's prescaler Output frequency of IN1 input/65 can be monitored at TEST pin.

#### <2> Test mode 2

- PLL 2ch's prescaler Output frequency of IN2 input/65 can be monitored at TEST pin.

- <3> Test mode 3

- This test mode can make PLL Lock and following operation monitor.

- Charge pump circuit Enforced high impedance outputs from CP pin to measure the leakage.

- Charge pump switch circuit When 16 or more signals are input to the CLK pin, the Charge pump switch (FI pin) changes from ON to OFF (open).

| CLK pin input count signal | CPSW (FI pin) | LOK pin |

|----------------------------|---------------|---------|

| 16 or over                 | OFF (open)    | Low     |

| less than 16               | ON            | High    |

• Lock detection circuit - When 16 or more signals are input to the CLK pin, the lock pin turns ON (L).

#### TEST MODES SETTING TABLE

| Block name                 | Test mode condition setting |        | TEST ain | Other menitor nin |          |                                       |  |

|----------------------------|-----------------------------|--------|----------|-------------------|----------|---------------------------------------|--|

| BIOCK name                 | Setting mode                | EN pin | DATA pin | CLK pin           | TEST pin | Other monitor pin                     |  |

| PLL 1 ch's prescaler       | Test Mode 1                 | Н      | L        | -                 | IN1/65   | _                                     |  |

| PLL 2 ch's prescaler       | Test Mode 2                 | L      | Н        | -                 | IN2/65   | _                                     |  |

| Change pump circuit        | Test Mode 3                 | Н      | Н        | _                 | -        | CP pin: High impedance output         |  |

| Charge pump switch circuit | Test Mode 3                 | Н      | Н        | 16 count signal   | -        | Switch control between CP and FI pins |  |

| Lock detection circuit     | Test Mode 3                 | Н      | Н        | 16 count signal   | _        | LOK pin : Low at Lock up              |  |

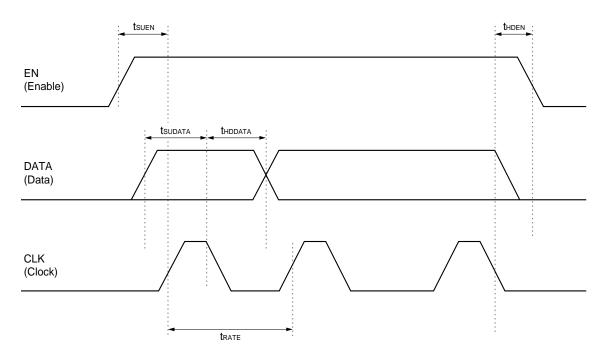

## SERIAL DATA INPUT TIMING

| Parameter        | Specification    |  |

|------------------|------------------|--|

| EN set up time   | tsuen≥500 ns     |  |

| EN hold time     | thden≥500 ns     |  |

| DATA set up time | tsudata≥100 ns   |  |

| DATA hold time   | thddata≥100 ns   |  |

| CLK rate         | 1 μs ≤trate ≤1 s |  |

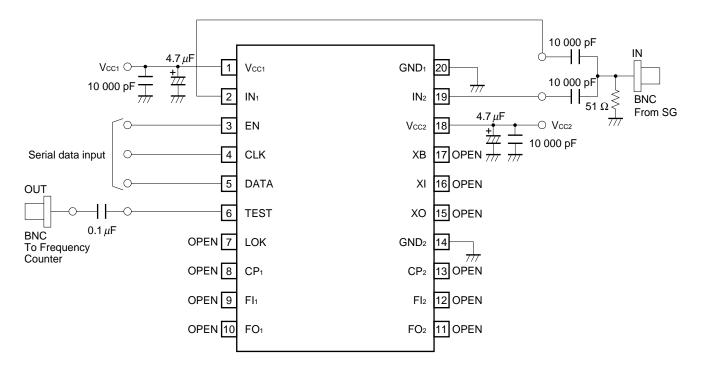

## **TEST CIRCUIT**

#### 1. DC measurement circuit

Supply current measurement flow

- 1. Supply power (Vcc1, Vcc2 ON). Except for Vcc1, Vcc2, GND1, GND2, EN, CLK and DATA pins should be opened.

- 2. Serial data input to 3, 4, and 5 pin. Prescaler operation should be set with option data D8 and D9.

- 3. Measure the supply current of Vcc1 and Vcc2.

- **ATTENTION** Serial data must be input for correct measurement. If you did not input serial data, measurement would be failed and show undesired value.

#### 2. AC measurement circuit

Input response of internal prescaler measurement flow.

- 1. Supply power (Vcc1, Vcc2 ON).

- Serial data input to 3, 4, and 5 pin.

[Command as dual operation with option data D8 and D9.]

- 3. Set TEST mode.

Vcc2 = Vcc1 + 2 (Other bias = Vcc1)

4. The 1ch (IN1) or 2ch (IN2) prescaler output can be monitored at TEST pin. (See the table below.)

| EN (3 pin) input | DATA (5 pin) input | TEST (6 pin)         |

|------------------|--------------------|----------------------|

| н                | L                  | 1ch prescaler output |

| L                | Н                  | 2ch prescaler output |

#### CHARACTERISTICS CURVES (T<sub>A</sub> = +25 °C unless otherwise specified)

#### **DC** chracteristics

#### **AC** characteristics

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

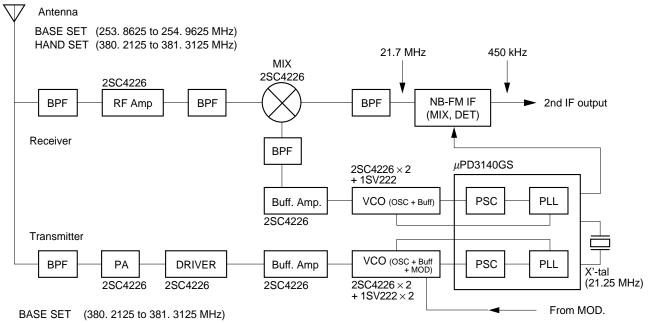

APPLICATION CIRCUIT EXAMPLE (Example for hand-held set of analog cordless phone)

## SELECTOR GUIDE OF DUAL PLL FREQUENCY SYNTHESIZER LSI FAMILY FOR CORDLESS TELEPHONE

| Item                                                    | IC number                           | μPD2840GS                     | μPD2842GS                                                      | μPD2843GS                 | μPD2844BGS                                       | μPD2844BGS(1)                                                   | μPD3140GS                                                    |

|---------------------------------------------------------|-------------------------------------|-------------------------------|----------------------------------------------------------------|---------------------------|--------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------|

| Reference counter number                                |                                     | Fixed (1 024)                 |                                                                | Variable<br>(2 to 4 096)  | Variable (4 to 8 192)<br>Note: Even number only. |                                                                 | Variable (64 to 4 094)<br><b>Note</b> : Even number<br>only. |

| Charge pi<br>mode                                       | ump output                          | Current output                | Current output type (Fixed) Current Output type (Programmable) |                           |                                                  | Current output<br>Voltage output<br>(Programmable)              |                                                              |

| Charge                                                  | Advanced                            | HIGH                          | LOW                                                            | Polarity can be switched  |                                                  |                                                                 | d.                                                           |

| pump<br>output                                          | Delayed                             | LOW                           | HIGH                                                           |                           | (Pi                                              | rogrammable)                                                    |                                                              |

| phase<br>polarity                                       | Synchronized                        | High impedance                |                                                                |                           |                                                  |                                                                 |                                                              |

| External low-pass filter type                           |                                     | Passive main  Active  Passive |                                                                |                           |                                                  |                                                                 |                                                              |

| Low-pass filter FET (for active filter) None (External) |                                     |                               | Equipped                                                       |                           |                                                  |                                                                 |                                                              |

| Reference<br>output                                     | e oscillator buffer                 |                               | None                                                           | e (external if necessary) |                                                  |                                                                 | Equipped                                                     |

| High-spee<br>pump swit                                  | gh-speed lockup charge<br>mp switch |                               |                                                                | None                      |                                                  |                                                                 | Equipped                                                     |

| Lock sensitivity data No setting                        |                                     |                               | one (Fixed at 500 ns)                                          |                           |                                                  | Programmable<br>(4 stages)                                      |                                                              |

| Data reset latch type                                   |                                     |                               | Yes                                                            |                           |                                                  | No. Stable operation<br>against same N<br>counter data latched. |                                                              |

| Supply voltage 2.2 t                                    |                                     | 2.2 to 5                      | 5.5 V 2.0 to 5.5 V                                             |                           | 1.8 to 5.5 V                                     |                                                                 |                                                              |

| Package 20 pin S0                                       |                                     | pin SOP (300 m                | nil)                                                           |                           | 20 pin SSOP (30                                  | 00 mil)                                                         |                                                              |

$\mu \text{PD3140GS}$  is recommendable due to the most excellent performance.

# SCHEMATIC BLOCK DIAGRAM FOR 200 MHz to 400 MHz WIRELESS SYSTEM (Example of Japanese analog cordless telephone)

HAND SET (253. 8625 to 254. 9625 MHz)

#### **APPLICATION SYSTEM EXAMPLES**

- Japanese analog cordless telephone

- Low-power transceiver

- VHF band radio communication system

- RF remote controller

- CT1/CT2 cordless telephone (doubler type)

- PHS/DECT digital cordless telephone (for 2nd PLL)

- Analog/digital cellular (for 2nd PLL)

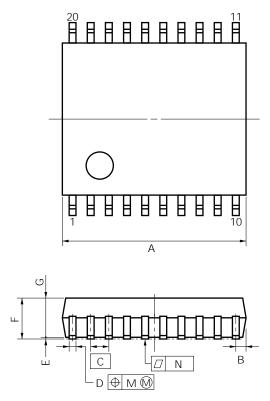

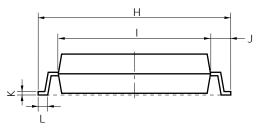

## 20 PIN PLASTIC SHRINK SOP (300 mil) (Unit : mm)

ΝΟΤΕ

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

detail of lead end

P20GM-65-300B-2

| ITEM | MILLIMETERS                     | INCHES                                    |  |

|------|---------------------------------|-------------------------------------------|--|

| А    | 7.00 MAX.                       | 0.276 MAX.                                |  |

| В    | 0.575 MAX.                      | 0.023 MAX.                                |  |

| С    | 0.65 (T.P.)                     | 0.026 (T.P.)                              |  |

| D    | 0.30±0.10                       | $0.012\substack{+0.004 \\ -0.005}$        |  |

| E    | 0.125±0.075                     | 0.005±0.003                               |  |

| F    | 2.0 MAX.                        | 0.079 MAX.                                |  |

| G    | 1.7                             | 0.067                                     |  |

| Н    | 8.1±0.3                         | 0.319±0.012                               |  |

| I    | 6.1±0.2                         | 0.240±0.008                               |  |

| J    | 1.0±0.2                         | 0.039 <sup>+0.009</sup> <sub>-0.008</sub> |  |

| К    | $0.15\substack{+0.10 \\ -0.05}$ | $0.006^{+0.004}_{-0.002}$                 |  |

| L    | 0.5±0.2                         | 0.020+0.008                               |  |

| М    | 0.12                            | 0.005                                     |  |

| N    | 0.10                            | 0.004                                     |  |

#### **RECOMMENDED SOLDERING CONDITIONS**

This product should be soldered in the following recommended conditions. Other soldering methods and conditions than the recommended conditions are to be consulted with our sales representatives.

#### μPD3140GS

| Soldering method    | Soldering conditions                                                                                           | Symbol    |

|---------------------|----------------------------------------------------------------------------------------------------------------|-----------|

| Infrared ray reflow | Package peak temperature: 235 °C, Hour: within 30 s.<br>(more than 210 °C), Time: 2 times, Limited days: no. * | IR35-00-2 |

| VPS                 | Package peak temperature: 215 °C, Hour: within 40 s.<br>(more than 200 °C), Time: 2 times, Limited days: no. * | VP15-00-2 |

| Pin part heating    | Pin area temperature: less than 300 °C, Hour: within 3 s./pin. Limited days: no. *                             |           |

\*: It is the storage days after opening a dry pack, the storage conditions are 25 °C, less than 65 % RH.

Note 1. Apply only a single process at once (except the pin part heating method.)

For details of recommended soldering conditions for surface mounting, refer to information document SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY MANUAL (C10535EJ7V0IF00)

#### NOTE ON CORRECT USE

- (1) Observe precautions for handling because of electrostatic sensitive devices.

- (2) Connect a bypass capacitor (e.g. 1 000 pF) to the Vcc pin.

- (3) External R, C values of loop filter should be determined according to the VCO specifications.

- (4) Form a ground pattern as wide as possible to minimize ground impedance.

- (5) After initial Vcc supplying, serial data should be input immediately. (Before serial data input, LSI operation is unstable or undesired.)

For details of application circuit example and setting data, refer to application note 'USAGE AND APPLICATION OF  $\mu$ PD3140GS'.

The application circuits and their parameters are for references only and are not intended for use in actual design-in's.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

M4 94.11