### Description

The µPD42102 is a 1,135-word by 8-bit line buffer fabricated with a CMOS silicon-gate process. The device helps to create a PAL flicker-free television picture (non-interlaced scan conversion) by providing intermediate storage and very high-speed read and write operation.

The  $\mu$ PD42102 can also be used as a digital delay line. The delay length is variable from 2 bits (at maximum clock speed) to 1,135 bits.

### **Features**

- □ 1,135-word x 8-bit organization

- □ Line buffer for PAL, 4f<sub>SC</sub> digital television systems

- □ Asynchronous, simultaneous read/write operation

- □ 1H (1,135-bit) delay line capability

- TTL-compatible inputs and outputs

- □ Three-state outputs

- □ Single +5-volt power supply

- 24-pin plastic DIP and miniflat packaging

### Ordering Information

| Part Number | Read Cycle<br>Time (min) | Write Cycle<br>Time (min) | Package                 |

|-------------|--------------------------|---------------------------|-------------------------|

| μPD42102C-5 | 25 ns                    | 25 ns                     | 24-pin plastic DIP      |

| C-3         | 34 ns                    | 34 ns                     | =                       |

| C-2         | 34 ns                    | 69 ns                     | •                       |

| C-1         | 69 ns                    | 69 ns                     | •                       |

| μPD42102G-5 | 25 ns                    | 25 ns                     | 24-pin plastic miniflat |

| G-3         | 34 ns                    | 34 ns                     | •                       |

| G-2         | 34 ns                    | 69 ns                     | •                       |

| G-1         | 69 ns                    | 69 ns                     | •                       |

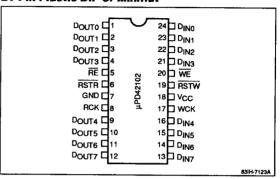

### Pin Configuration

### 24-Pin Plastic DIP or Miniflat

### Pin Identification

| Symbol                                | Function                  |

|---------------------------------------|---------------------------|

| D <sub>INO</sub> - D <sub>IN7</sub>   | Write data inputs         |

| D <sub>OUT0</sub> - D <sub>OUT7</sub> | Read data outputs         |

| RSTW                                  | Write address reset input |

| RSTR                                  | Read address reset input  |

| WE                                    | Write enable input        |

| RE                                    | Read enable input         |

| WCK                                   | Write clock input         |

| RCK                                   | Read clock input          |

| GND                                   | Ground                    |

| V <sub>CC</sub>                       | +5-volt power supply      |

www.DataSheet4U.com

#### PIN FUNCTIONS

## DINO - DIN7 (Data Inputs)

In a digital television application, the digital composite signal, luminance, chrominance, etc. information is written into these inputs.

# D<sub>OUT0</sub> - D<sub>OUT7</sub> (Data Outputs)

The tri-state outputs are used to access the stored information. In a simple digital delay line application, a delay of one-half write clock cycle plus a maximum of 300 ns is required to move data from the data inputs to the data outputs.

## **RSTW** (Write Address Reset Input)

Bringing this signal low when WE is also low resets the internal write address to 0. If WE is at a high level when the RSTW input is brought low, the internal write address is set to 1,134. The state of this input is strobed by the rising edge of WCK.

#### **RSTR** (Read Address Reset Input)

This signal is strobed by the rising edge of RCK and resets the internal read address to 0 if RE is also low. If RE is at a high level when the RSTR input is brought low, the internal read address is set to 1,134.

#### WE (Write Enable Input)

This input controls write operation. If WE is low, all write cycles proceed. If WE is at a high level, no data is written to storage cells and the write address stops increasing. The state of WE is strobed by the rising edge of WCK.

### RE (Read Enable Input)

This signal is similar to  $\overline{\text{WE}}$  but controls read operation. If  $\overline{\text{RE}}$  is at a high level, the data outpus become high impedance and the internal read address stops increasing. The state of  $\overline{\text{RE}}$  is strobed by the rising edge of RCK.

## WCK (Write Clock Input)

All write cycles are executed synchronously with WCK. The states of both  $\overline{\text{RSTW}}$  and  $\overline{\text{WE}}$  are strobed by the rising edge of WCK at the beginning of a cycle, and the data inputs are strobed by the rising edge of WCK at the end of a cycle. The internal write address increases with

each WCK cycle unless  $\overline{WE}$  is at a high level to hold the write address constant. Unless inhibited by  $\overline{WE}$ , the internal write address will automatically wrap around from 1,134 to 0 and begin increasing again.

## **RCK (Read Clock Input)**

All read cycles are executed synchronously with RCK. The states of both  $\overline{\text{RSTR}}$  and  $\overline{\text{RE}}$  are strobed by the rising edge of RCK at the beginning of a cycle. This same edge of RCK starts internal read operation, and access time is referenced to this edge. The internal read address increases with each RCK cycle unless  $\overline{\text{RE}}$  is at a high level to hold the read address constant. Unless inhibited by  $\overline{\text{RE}}$ , the internal read address will automatically wrap around from 1,134 to 0 and begin increasing again.

## **Absolute Maximum Ratings**

| Supply voltage, V <sub>CC</sub>               | - 1.5 to +7.0 V  |

|-----------------------------------------------|------------------|

| Voltages on any input pin, V <sub>I</sub>     | - 1.5 to + 7.0 V |

| Voltage on any output pin, V <sub>O</sub>     | -1.5 to +7.0 V   |

| Short-circuit output current, I <sub>OS</sub> | 20 mA            |

| Operating temperature, TOPR                   | - 20 to +70°C    |

| Storage temperature, T <sub>STG</sub>         | - 55 to +125°C   |

Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should be operated within the limits specified under DC and AC Characteristics.

# **Recommended Operating Conditions**

| Parameter             | Symbol          | Min   | Тур | Max | Unit |

|-----------------------|-----------------|-------|-----|-----|------|

| Supply voltage        | Vcc             | 4.5   | 5.0 | 5.5 | ٧    |

| Input voltage, high   | VIH             | 2.4   |     | 5.5 | ٧    |

| Input voltage, low    | V <sub>IL</sub> | - 1.5 |     | 0.8 | ٧    |

| Operating temperature | T <sub>A</sub>  | -20   |     | 70  | °C   |

#### Capacitance

$T_A = 25^{\circ}C; V_{CC} = +5.0 \text{ V} \pm 10\%; f = 1 \text{ MHz}$

| Parameter             | Symbol | Min | Max | Unit | Pins Under Test                                                         |  |  |  |  |

|-----------------------|--------|-----|-----|------|-------------------------------------------------------------------------|--|--|--|--|

| Input<br>capacitance  | Cı     |     | 5   | рF   | WE, RE, WCK, RCK,<br>RSTW, RSTR,<br>D <sub>INO</sub> - D <sub>IN7</sub> |  |  |  |  |

| Output<br>capacitance | Co     |     | 7   | pF   | D <sub>OUT0</sub> - D <sub>OUT7</sub>                                   |  |  |  |  |

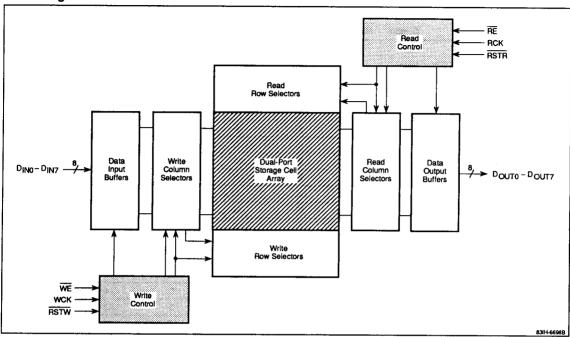

# **Block Diagram**

## **DC Characteristics**

$T_A = -20 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

| Parameter              | Symbol          | Min | Тур | Max | Unit | Test Conditions                                                                |

|------------------------|-----------------|-----|-----|-----|------|--------------------------------------------------------------------------------|

| Input leakage current  | l <sub>i</sub>  | -10 |     | 10  | μА   | V <sub>IN</sub> = 0 V to V <sub>CC</sub> ; all other pins not under test = 0 V |

| Output leakage current | lo              | -10 |     | 10  | μА   | D <sub>OUT</sub> disabled; V <sub>O</sub> = 0 to 5.5 V                         |

| Output voltage, high   | Voн             | 2.4 |     |     | V    | I <sub>OH</sub> = -1 mA                                                        |

| Output voltage, low    | V <sub>OL</sub> |     |     | 0.4 | ٧    | I <sub>OL</sub> = 2.0 mA                                                       |

## **AC Characteristics**

$T_A = -20 \text{ to } +70^{\circ}\text{C}; V_{CC} = +5.0 \text{ V} \pm 10\%$

|                                    |                  | μPD42102-5 |     | μPD42102-3 |     | μPD42102-2 |     | μPD42102-1 |     |      |                                                                                        |

|------------------------------------|------------------|------------|-----|------------|-----|------------|-----|------------|-----|------|----------------------------------------------------------------------------------------|

| Parameter                          | Symbol           | Min        | Max | Min        | Max | Min        | Max | Min        | Max | Unit | Test Conditions                                                                        |

| Write/read cycle operating current | lcc              |            | 80  |            | 80  |            | 70  |            | 40  | mA   | t <sub>WCK</sub> = t <sub>WCK</sub> (min)<br>t <sub>RCK</sub> = t <sub>RCK</sub> (min) |

| Write clock cycle time             | twck             | 25         | 880 | 28         | 880 | 56         | 880 | 56         | 880 | ns   |                                                                                        |

| WCK pulse width                    | ‡wcw             | 10         |     | 12         |     | 20         |     | 20         |     | ns   |                                                                                        |

| WCK precharge time                 | ₩CP              | 10         |     | 12         |     | 20         |     | 20         |     | ns   |                                                                                        |

| Read clock cycle time              | <sup>t</sup> RCK | 25         | 880 | 28         | 880 | 28         | 880 | 56         | 880 | ns   |                                                                                        |

| RCK pulse width                    | <sup>t</sup> RCW | 10         |     | 12         |     | 12         |     | 20         |     | ns   |                                                                                        |

| RCK precharge time                 | †RCP             | 10         |     | 12         |     | 12         |     | 20         |     | ns   |                                                                                        |

| Access time                        | t <sub>AC</sub>  |            | 18  |            | 21  |            | 21  | ·····      | 40  | ns   |                                                                                        |

| Output hold time                   | tон              | 5          |     | 5          | •   | 5          |     | 5          |     | ns   |                                                                                        |

### AC Characteristics (cont)

|                                      |                   | μPD4 | 2102-5 | μPD42 | 2102-3 | μPD42 | 2102-2 | μPD4 | 2102-1 | -1   |                 |

|--------------------------------------|-------------------|------|--------|-------|--------|-------|--------|------|--------|------|-----------------|

| Parameter                            | Symbol            | Min  | Max    | Min   | Max    | Min   | Max    | Min  | Max    | Unit | Test Conditions |

| Access time after a reset cycle      | t <sub>ACR</sub>  |      | 18     |       | 21     |       | 21     |      | 40     | ns   |                 |

| Output hold time after a reset cycle | tOHR              | 5    |        | 5     |        | 5     |        | 5    |        | ns   |                 |

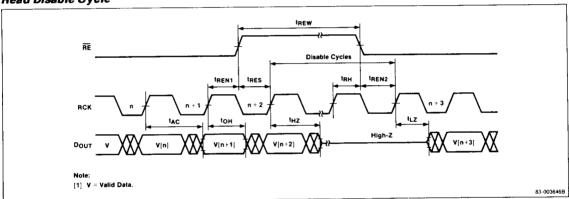

| Output active time                   | t <sub>LZ</sub>   | 5    | 18     | 5     | 21     | 5     | 21     | 5    | 40     | ns   | (Note 4)        |

| Output disable time                  | t <sub>HZ</sub>   | 5    | 18     | 5     | 21     | 5     | 21     | 5    | 40     | ns   | (Note 4)        |

| Data-in setup time                   | t <sub>DS</sub>   | 7    |        | 12    |        | 15    |        | 15   |        | ns   |                 |

| Data-in hold time                    | t <sub>DH</sub>   | 3    |        | 5     |        | 5     |        | 5    |        | ns   |                 |

| Reset active setup time              | <sup>t</sup> RS   | 7    |        | 12    |        | 12    |        | 20   |        | ns   | (Note 7)        |

| Reset active hold time               | t <sub>RH</sub>   | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 7)        |

| Reset inactive hold time             | <sup>t</sup> RN1  | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 8)        |

| Reset inactive setup time            | t <sub>RN2</sub>  | 7    |        | 12    |        | 12    |        | 20   |        | ns   | (Note 8)        |

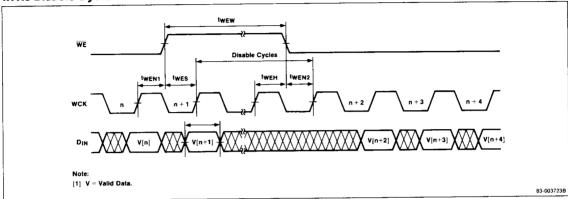

| Write enable setup time              | twes              | 7    |        | 12    |        | 20    |        | 20   |        | ns   | (Note 9)        |

| Write enable hold time               | tweH              | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 9)        |

| Write enable high delay from WCK     | twen1             | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 10)       |

| Write enable low delay to WCK        | twen2             | 7    |        | 12    |        | 20    |        | 20   |        | ns   | (Note 10)       |

| Read enable setup time               | t <sub>RES</sub>  | 7    |        | 12    |        | 12    |        | 20   |        | ns   | (Note 9)        |

| Read enable hold time                | t <sub>REH</sub>  | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 9)        |

| Read enable high delay from RCK      | t <sub>REN1</sub> | 3    |        | 5     |        | 5     |        | 5    |        | ns   | (Note 10)       |

| Read enable low delay to RCK         | t <sub>REN2</sub> | 7    |        | 12    |        | 12    |        | 20   |        | ns   | (Note 10)       |

| Write disable pulse width            | twew              | 0    |        | 0     |        | 0     |        | 0    |        | ns   | (Note 5)        |

| Read disable pulse width             | t <sub>REW</sub>  | 0    |        | 0     |        | 0     |        | 0    |        | ns   | (Note 5)        |

| Write reset time                     | testw             | 0    |        | 0     |        | 0     |        | 0    |        | ns   | (Note 5)        |

| Read reset time                      | t <sub>RSTR</sub> | 0    |        | 0     |        | 0     |        | 0    |        | ns   | (Note 5)        |

| Transition time                      | t <sub>T</sub>    | 3    | 35     | 3     | 35     | 3     | 35     | 3    | 35     | ns   |                 |

### Notes:

- (1) All voltages are referenced to ground.

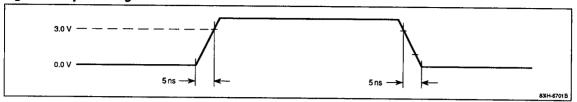

- (2) Input pulse rise and fall times assume  $t_T=5$  ns. Input pulse levels = GND to 3 V. Transition times are measured between 3 V and 0 V.

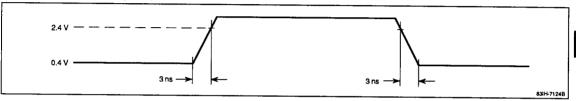

- For the -5 version only,  $t_T=3$  ns; input pulse levels =0.4 to 2.4 V; transition times are measured between 0.4 and 2.4 V. See figures 1 and 2.

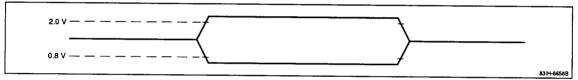

- (3) Input timing reference levels = 1.5 V. Output timing reference levels are 0.8 and 2.0 V. See figure 3.

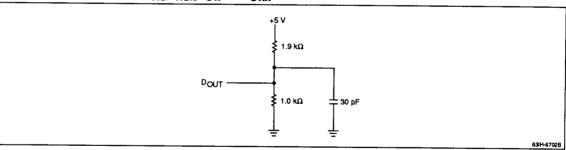

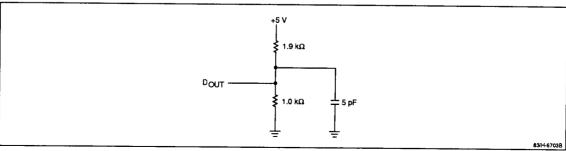

- (4) This delay is measured at 200 mV from the steady-state voltage with the load specified in figure 5. Under any conditions, t<sub>LZ</sub> ≥ t<sub>HZ</sub>.

- (5) t<sub>WEW</sub> (max) and t<sub>REW</sub> (max) must be satisfied by the following equations in 1-line cycle operation:

- t<sub>WEW</sub> + t<sub>RSTW</sub> +1,135 (t<sub>WCK</sub>) ≤ 1 ms

- $t_{REW} + t_{RSTR} + 1,135 (t_{RCK}) \le 1 \text{ ms}$

- (6) This parameter applies when t<sub>RCK</sub> ≥ t<sub>ACR</sub> (max).

- (7) If either  $t_{\rm RS}$  or  $t_{\rm RH}$  is less than the specified value, reset operations are not guaranteed.

- (8) If either t<sub>RN1</sub> or t<sub>RN2</sub> is less than the specified value, internal reset operations may extend to cycles immediately preceding or following the period of desired reset operations.

- (9) If either t<sub>WES</sub> or t<sub>WEH</sub> (t<sub>RES</sub> or t<sub>REH</sub>) is less than the specified value, write (read) disable operations are not guaranteed.

- (10) If either t<sub>WEN1</sub> or t<sub>WEN2</sub> (t<sub>REN1</sub> or t<sub>REN2</sub>) is less than the specified value, internal write (read) disable operations may extend to cycles immediately preceding or following the period of desired disable operations.

- (11) Data is guaranteed to remain valid for a minimum of 1 ms after it is written. After this time, the data stored may be invalid, since this device uses a dynamic storage element.

Figure 1. Input Timing

Figure 2. Input Timing for µPD42102-5

Figure 3. Output Timing

Figure 4. Output Load for tAC, tACR, tOH and tOHR

Figure 5. Output Load for  $t_{LZ}$  and  $t_{HZ}$

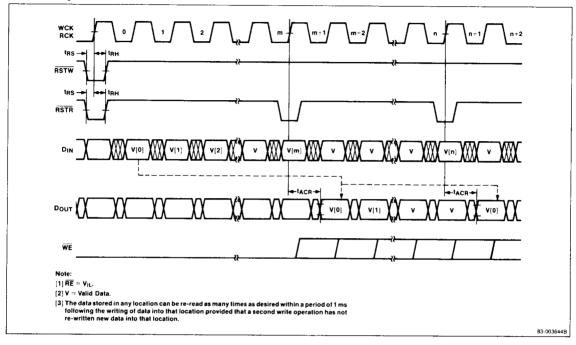

# **Timing Waveforms**

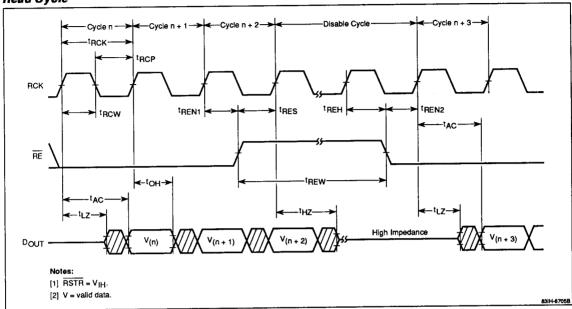

# Read Cycle

# Write Cycle

# Timing Waveforms (cont)

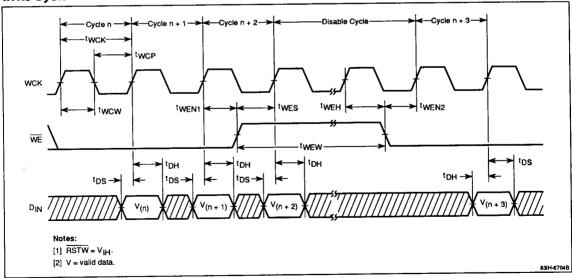

# Read Reset Cycle

# Write Reset Cycle

# Timing Waveforms (cont)

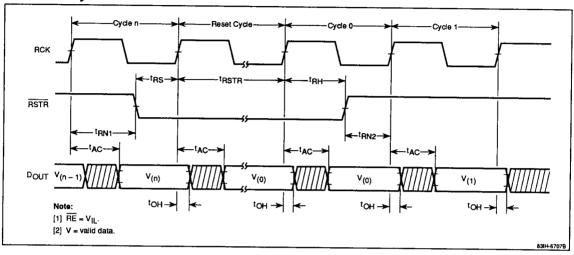

# Write Disable Cycle

# Read Disable Cycle

# Timing Waveforms (cont)

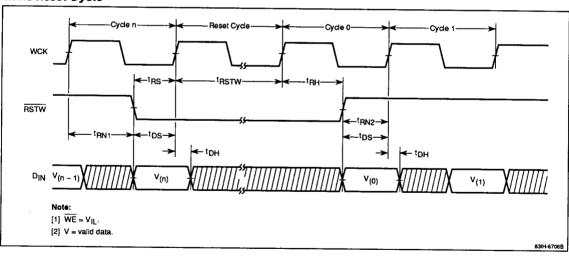

## Re-Read Cycle