# mos integrated circuit $\mu PD434001$

# 4M-BIT CMOS FAST STATIC RAM 4M-WORD BY 1-BIT

# Description

The  $\mu$ PD434001 is a high speed, low power, 4,194,304 bits (4,194,304 words by 1 bit) CMOS static RAM. The  $\mu$ PD434001 is packed in 32-pin plastic SOJ.

# **Features**

- 4,194,304 words by 1 bit organization

- Fast access time 20 ns (MAX.)

- OE input for easy application

- Test mode function on chip

# **Ordering Information**

| Part number    | Package                      | Access time<br>ns (MAX.) | Operating<br>supply current<br>mA (MAX.) | Standby<br>supply current<br>mA (MAX.) |

|----------------|------------------------------|--------------------------|------------------------------------------|----------------------------------------|

| μPD434001LE-20 | 32-pin plastic SOJ (400 mil) | 20                       | 140                                      | 10                                     |

| μPD434001LE-25 |                              | 25                       | 130                                      | 10                                     |

The information in this document is subject to change without notice.

# Pin Configuration (Marking Side)

# 32-pin plastic SOJ (400 mil)

# $\mu$ PD434001LE-20 $\mu$ PD434001LE-25

A0 - A21 : Address inputs

DIN : Data input

DOUT : Data output

CS : Chip Select

WE : Write Enable

OE : Output Enable

Vcc : Power supply

GND : Ground

TE Note : Test mode Enable

Note TE should be connected to GND in normal operation.

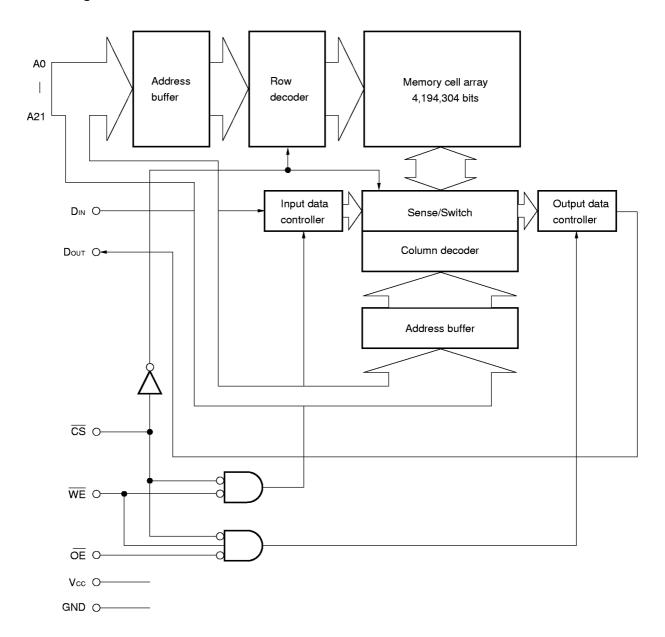

# **Block Diagram**

# **Truth Table**

| cs | ŌĒ | WE | Mode           | I/O              | Supply current  |

|----|----|----|----------------|------------------|-----------------|

| Н  | ×  | ×  | Not selected   | Hi-Z             | I <sub>SB</sub> |

| L  | Н  | Н  | Output disable | HI-Z             |                 |

| L  | L  | Н  | Read           | D <sub>оит</sub> | lcc             |

| L  | ×  | L  | Write          | Din              |                 |

Remark ×: Don't care

#### **Electrical Characteristics**

# **Absolute Maximum Ratings**

| Parameter                     | Symbol | Rating                              | Unit |

|-------------------------------|--------|-------------------------------------|------|

| Supply voltage                | Vcc    | -0.5 <sup>Note</sup> to +7.0        | >    |

| Input/Output voltage          | VT     | $-0.5^{\text{Note}}$ to $Vcc + 0.3$ | ٧    |

| Operating ambient temperature | TA     | 0 to +70                            | °C   |

| Storage temperature           | Tstg   | -55 to +125                         | °C   |

Note -2.0 V (MIN.) (Pulse width: 10 ns)

Caution Exposing the device to stress above those listed in absolute maximum ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this characteristics. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Recommended Operating Conditions**

| Parameter                     | Symbol | MIN.                 | TYP. | MAX.      | Unit |

|-------------------------------|--------|----------------------|------|-----------|------|

| Supply voltage                | Vcc    | 4.5                  | 5.0  | 5.5       | ٧    |

| High level input voltage      | Vıн    | 2.2                  |      | Vcc + 0.3 | ٧    |

| Low level input voltage       | VIL    | -0.5 <sup>Note</sup> |      | +0.8      | ٧    |

| Operating ambient temperature | Та     | 0                    |      | +70       | °C   |

Note -2.0 V (MIN.) (Pulse width: 10 ns)

# DC Characteristics (Recommended operating conditions unless otherwise noted)

| Parameter                 | Symbol           | Test con                                                                                                              | MIN.         | TYP. | MAX. | Unit |    |

|---------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|------|------|------|----|

| Input leakage current     | lu               | Vin = 0 V to Vcc                                                                                                      |              | -2   |      | +2   | μΑ |

| Output leakage current    | Іго              | $V_{OUT} = 0 \text{ V to Vcc}, \overline{CS} = V_{IH} \text{ or } \overline{OE} = V_{IH}$ or $\overline{WE} = V_{IL}$ |              | -2   |      | +2   | μΑ |

| Operating supply current  | lcc              | CS = VIL, IOUT = 0 mA,                                                                                                | μPD434001-20 |      |      | 140  | mA |

| Operating supply current  |                  | Minimum cycle                                                                                                         | μPD434001-25 |      |      | 130  | "" |

|                           | Isa              | CS = VIH,                                                                                                             | μPD434001-20 |      |      | 60   |    |

| Standby supply current    | 135              | Minimum cycle                                                                                                         | μPD434001-25 |      |      | 50   | mA |

| Standby supply current    | Is <sub>B1</sub> | CS ≥ Vcc - 0.2 V,         VIN ≥ Vcc - 0.2 V or V                                                                      | /IN ≦0.2 V   |      |      | 10   |    |

| High level output voltage | Vон              | Iон = −4.0 mA                                                                                                         | 2.4          |      |      | ٧    |    |

| Low level output voltage  | Vol              | lot = 8 mA                                                                                                            |              |      |      | 0.4  | ٧  |

Remark VIN: Input voltage

# Capacitance (T<sub>A</sub> = 25 $^{\circ}$ C, f = 1 MHz)

| Parameter                | Symbol | Test conditions | MIN. | TYP. | MAX. | Unit |

|--------------------------|--------|-----------------|------|------|------|------|

| Input capacitance        | Сім    | VIN = 0 V       |      |      | 6    | pF   |

| Input/Output capacitance | Соит   | Vout = 0 V      |      |      | 10   | pF   |

Remarks 1. VIN: Input voltage

2. These parameters are periodically sampled and not 100 % tested.

# AC Characteristics (Recommended operating conditions unless otherwise noted)

# **AC Test Conditions**

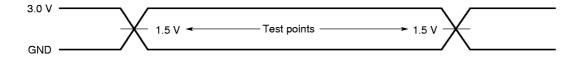

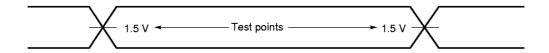

Input waveform (Rise/fall time ≤ 3 ns)

# **Output waveform**

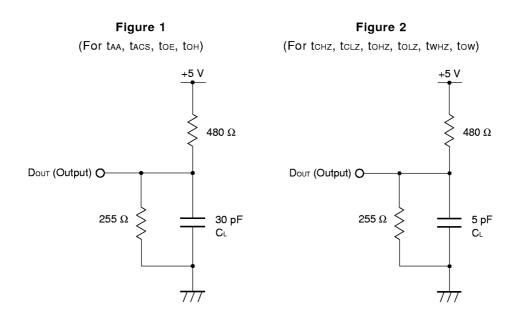

# **Output load**

AC Characteristics directed with the note should be measured with the output load shown in Figure 1 or Figure 2.

Remark CL includes capacitances of the probe and jig, and stray capacitances.

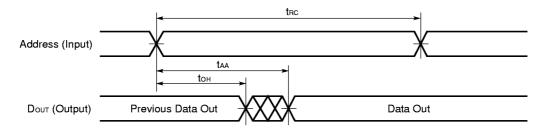

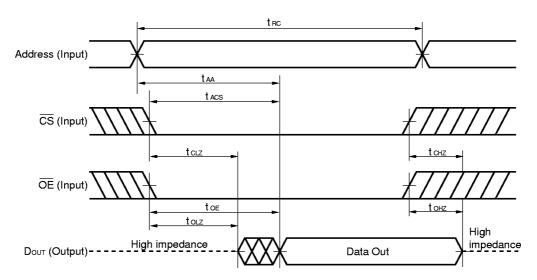

# Read Cycle

| Parameter                       | Symbol   | Symbol μPD43400 |      | 001LE-20 μPD4340 |      | Unit  | Conditions |  |

|---------------------------------|----------|-----------------|------|------------------|------|-------|------------|--|

| Parameter                       | Syllibol | MIN.            | MAX. | MIN.             | MAX. | Offic | Conditions |  |

| Read cycle time                 | tric     | 20              |      | 25               |      | ns    |            |  |

| Address access time             | taa      |                 | 20   |                  | 25   | ns    |            |  |

| CS access time                  | tacs     |                 | 20   |                  | 25   | ns    | Note 1.    |  |

| OE access time                  | toe      |                 | 10   |                  | 12   | ns    | Note 1.    |  |

| Output hold from address change | tон      | 3               |      | 3                |      | ns    |            |  |

| CS to output in low impedance   | tcLZ     | 3               |      | 3                |      | ns    |            |  |

| OE to output in low impedance   | tolz     | 0               |      | 0                |      | ns    | Note 0     |  |

| CS to output in high impedance  | tснz     |                 | 8    |                  | 10   | ns    | Note 2.    |  |

| OE to output in high impedance  | tонz     |                 | 8    |                  | 10   | ns    |            |  |

Notes 1. See the output load shown in Figure 1.

2. See the output load shown in Figure 2.

# Read Cycle Timing Chart 1 (Address Access)

**Remarks 1.** In read cycle,  $\overline{\text{WE}}$  should be fixed to high level.

2.

$$\overline{CS} = \overline{OE} = V \sqcup$$

# Read Cycle Timing Chart 2 (CS Access)

Caution Address valid prior to or coincident with  $\overline{\text{CS}}$  low level input.

**Remark** In read cycle, WE should be fixed to high level.

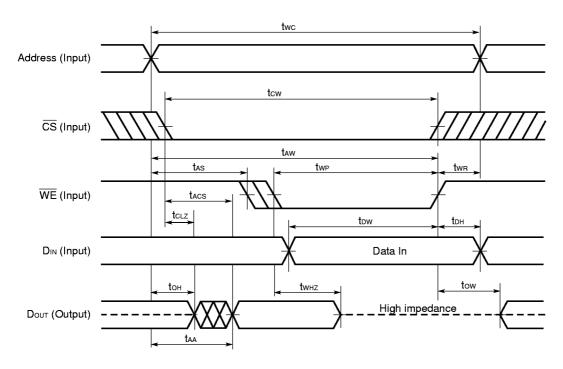

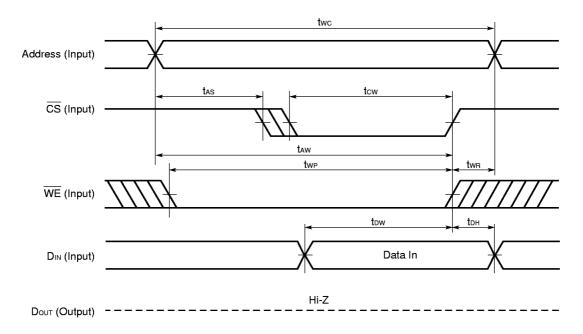

# Write Cycle

| Davamatav                       | Cumah al | μPD434001LE-20 |      | μPD434001LE-25 |      | 11   | 0         |

|---------------------------------|----------|----------------|------|----------------|------|------|-----------|

| Parameter                       | Symbol   | MIN.           | MAX. | MIN.           | MAX. | Unit | Condition |

| Write cycle time                | twc      | 20             |      | 25             |      | ns   |           |

| CS to end of write              | tcw      | 14             |      | 17             |      | ns   |           |

| Address valid to end of write   | taw      | 14             |      | 17             |      | ns   |           |

| Write pulse width               | twp      | 12             |      | 15             |      | ns   |           |

| Data valid to end of write      | tow      | 10             |      | 12             |      | ns   |           |

| Data hold time                  | tон      | 0              |      | 0              |      | ns   |           |

| Address setup time              | tas      | 0              |      | 0              |      | ns   |           |

| Write recovery time             | twn      | 3              |      | 3              |      | ns   |           |

| WE to output in high impedance  | twnz     |                | 8    |                | 10   | ns   | NI - 4 -  |

| Output active from end of write | tow      | 0              |      | 0              |      | ns   | Note      |

Note See the output load shown in Figure 2.

# Write Cycle Timing Chart 1 (WE Controlled)

Caution  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  should be fixed to high level during address transition.

**Remarks 1.** Write operation is done during the overlap time of a low level  $\overline{CS}$  and a low level  $\overline{WE}$ .

- 2. When WE is at low level, the Dout pin is always high impedance. When WE is at high level, read operation is executed. Therefore OE should be at high level to make the Dout pin high impedance.

- 3. twn is measured between rising edge of  $\overline{CS}$  or  $\overline{WE}$ , whichever occurs first, and end of twc.

- 4. twHz is measured at Vol + 200 mV and Vol 200 mV with the output load shown in Figure 2.

- 5. tow is measured at ±200 mV from steady-state voltage with the output load shown in Figure 2.

# Write Cycle Timing Chart 2 (CS Controlled)

Caution  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  should be fixed to high level during address transition.

**Remarks 1.** Write operation is done during the overlap time of a low level  $\overline{CS}$  and a low level  $\overline{WE}$ .

2. twn is measured between rising edge of  $\overline{CS}$  or  $\overline{WE}$ , whichever occurs first, and end of twc.

#### **Test Mode**

Test mode is used to test the memory cells in a shorter time than normal testing. Test mode reduces test time to 1/8. In this test mode, internal organization is apparently 512K words by 8 bits. Input levels of A19, A20 and A21 pin do not need to be controlled.

#### 1. How to enter test mode

To enter the test mode, execute the test mode set cycle.

#### 2. Read/Write in test mode

Write data of "1" or "0" from D<sub>IN</sub> pin. Write operation is performed with 8 bits written at once. Therefore, 8-bit data in total are written at a write operation.

Then user should change the write operation to read operation to read judgement data. If the data is "1", the cells operate correctly. If the data is "0", they operate incorrectly. Repeating write/read operations 524,288 (512K) times checks 4M-bit of the memory.

#### 3. How to exit from test mode

To exit the test mode, execute the test mode reset cycle.

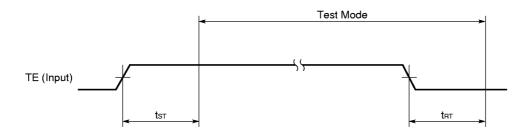

#### Test Mode Set/Reset Cycle Timing Chart

# Test Mode Set/Reset Cycle

| Parameter            | Symbol | μPD434001LE-20 |      | μPD434 | Unit |      |

|----------------------|--------|----------------|------|--------|------|------|

| Parameter            | Symbol | MIN.           | MAX. | MIN.   | MAX. | Onit |

| Test mode set time   | tsт    | 30             |      | 30     |      | ns   |

| Test mode reset time | tвт    | 30             |      | 30     |      | ns   |

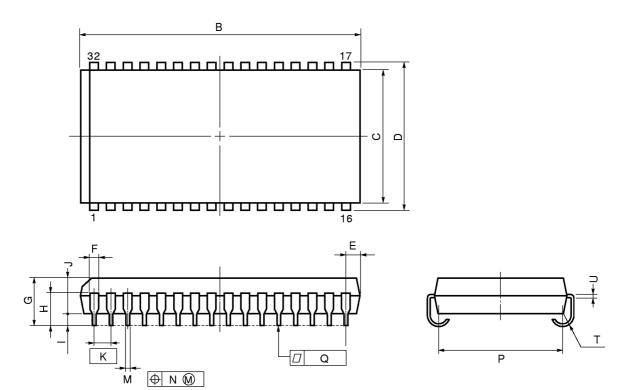

# **Package Drawing**

# 32 PIN PLASTIC SOJ (400 mil)

NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

P32LE-400A

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| В    | 21.06±0.2              | 0.829±0.008               |

| С    | 10.16                  | 0.400                     |

| D    | 11.18±0.2              | 0.440±0.008               |

| Е    | 1.005±0.1              | 0.040+0.004               |

| F    | 0.74                   | 0.029                     |

| G    | 3.5±0.2                | 0.138±0.008               |

| Н    | 2.545±0.2              | 0.100±0.008               |

| I    | 0.8 MIN.               | 0.031 MIN.                |

| J    | 2.6                    | 0.102                     |

| K    | 1.27 (T.P.)            | 0.050 (T.P.)              |

| М    | 0.40±0.10              | $0.016^{+0.004}_{-0.005}$ |

| N    | 0.12                   | 0.005                     |

| Р    | 9.4±0.20               | 0.370±0.008               |

| Q    | 0.1                    | 0.004                     |

| Т    | R 0.85                 | R 0.033                   |

| U    | $0.20^{+0.10}_{-0.05}$ | $0.008^{+0.004}_{-0.002}$ |

# **RECOMMENDED SOLDERING CONDITIONS**

Please consult with our sales offices for soldering conditions of the  $\mu PD434001$ .

# TYPE OF SURFACE MOUNT DEVICE

$\mu$ PD434001LE: 32-pin plastic SOJ (400 mil)