# MOS INTEGRATED CIRCUIT $\mu$ PD64082

## THREE-DIMENSIONAL Y/C SEPARATION LSI

## DESCRIPTION

The  $\mu$ PD64082 realizes a high precision Y/C separation and a noise reduction by the three-dimension signal processing for NTSC signal.

The three-dimension Y/C separation system can be easily realized with 4Mbit-EDO DRAM and A/D converter.

This product has a high precision 10-bit A/D converter internal, and 10-bit signal processing (only for luminance signal) for high picture quality.

This LSI includes the Wide Clear Vision ID signal decoder and Horizontal Helper signal decoder.

## FEATURES

- Includes a high performance pipeline 10-bit A/D converter for composite and luminance signal, and 8-bit A/D converter for chroma signal processing.

- · High resolution picture with 4 times of ratio in the previous system.

- Easy to make the three-dimension Y/C separation and YNR/CNR system with 4MBit-EDO DRAM.

- Includes system clock generator, 2-ch of A/D converter, and 2-ch of D/A converter.

- · Includes HH decoder (Required the field memory).

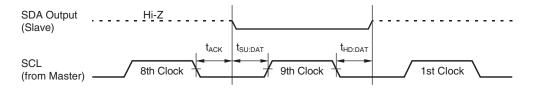

- I<sup>2</sup>C bus control.

- Single power supply of 3.3 V.

## **ORDERING INFORMATION**

Part number

Package

μPD64082GF-3BA

100-pin plastic QFP ( $14 \times 20$ )

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

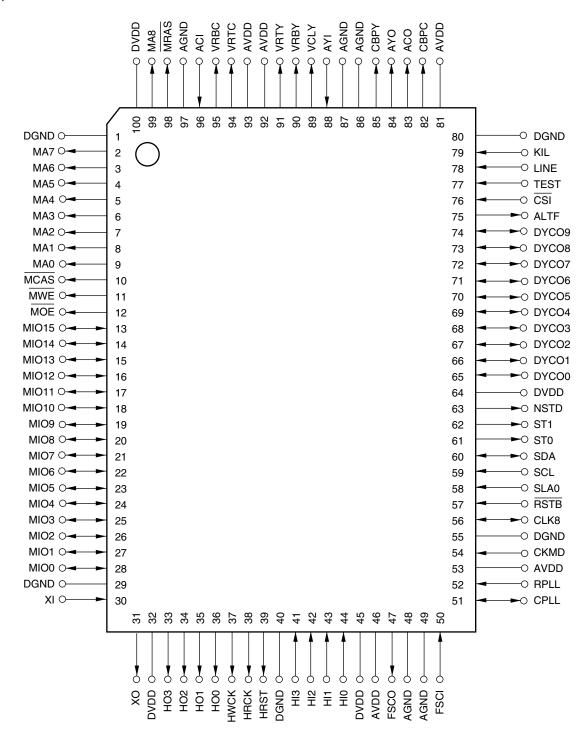

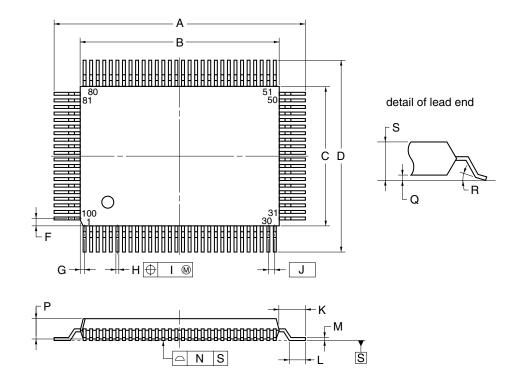

## **PIN CONFIGURATION (TOP VIEW)**

100-pin plastic QFP (14 × 20) μPD64082GF-3BA

| 4.01                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACI                                                                                            | : Analog C (Chroma) Signal Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ACO                                                                                            | : Analog C (Chroma) Signal Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AGND                                                                                           | : Analog Section Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ALTF                                                                                           | : Alternate Flag for Digital Y/C Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AVDD                                                                                           | : Analog Section Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| AYI                                                                                            | : Analog Y (Luma) Signal Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AYO                                                                                            | : Analog Y (Luma) Signal Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CBPC                                                                                           | : C-DAC Phase Compensation Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CBPY                                                                                           | : Y-DAC Phase Compensation Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CKMD                                                                                           | : Clock Mode Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLK8                                                                                           | : 8fsc Clock Input / Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CPLL                                                                                           | : Capacitor Connection for PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CSI                                                                                            | : Composite Sync. Input (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DGND                                                                                           | : Digital Section Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DVDD                                                                                           | : Digital Section Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                | 9 : Digital Y/C Signal (Alternative) Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FSCI                                                                                           | : fsc (Subcarrier) Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FSCO                                                                                           | : fsc (Subcarrier) Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| HI3 - HI0                                                                                      | : Field Memory Inputs for HH Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| HO3 - HO0                                                                                      | : Field Memory Outputs for HH Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HRCK                                                                                           | : Field Memory Read Clock for HH Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| HRST                                                                                           | : Field Memory Reset for HH Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HWCK                                                                                           | : Field Memory Write Clock for HH Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| KIL                                                                                            | : Killer Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LINE                                                                                           | : Inter-Line Separate Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MA8 - MA0                                                                                      | : EDO Memory Address Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MCAS                                                                                           | : EDO Memory Column Address Strobe (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MIO15 - MIO0                                                                                   | : EDO Memory Data Inputs/Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MOE                                                                                            | : EDO Memory Output Enable (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MRAS                                                                                           | : EDO Memory Row Address Strobe (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MWE                                                                                            | : EDO Memory Write Enable (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NSTD                                                                                           | : Non Standard Detection Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RPLL                                                                                           | : Testing Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RPLL<br>RSTB                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RSTB                                                                                           | : Testing Selection<br>: System Reset (active-low)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                | : Testing Selection<br>: System Reset (active-low)<br>: Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RSTB<br>SCL<br>SDA                                                                             | : Testing Selection<br>: System Reset (active-low)<br>: Serial Clock Input<br>: Serial Data Input / Output                                                                                                                                                                                                                                                                                                                                                                                               |

| RSTB<br>SCL<br>SDA<br>SLA0                                                                     | : Testing Selection<br>: System Reset (active-low)<br>: Serial Clock Input<br>: Serial Data Input / Output<br>: Slave Address Selection                                                                                                                                                                                                                                                                                                                                                                  |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0                                                         | : Testing Selection<br>: System Reset (active-low)<br>: Serial Clock Input<br>: Serial Data Input / Output<br>: Slave Address Selection<br>: Inner States Monitor                                                                                                                                                                                                                                                                                                                                        |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST                                                 | : Testing Selection<br>: System Reset (active-low)<br>: Serial Clock Input<br>: Serial Data Input / Output<br>: Slave Address Selection<br>: Inner States Monitor<br>: Testing Selection                                                                                                                                                                                                                                                                                                                 |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY                                         | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> </ul>                                                                                                                                                                                                               |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY<br>VRTC                                 | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> <li>: Top Voltage Reference Output for C-ADC</li> </ul>                                                                                                                                                             |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY<br>VRTC<br>VRTY                         | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> </ul>                                                                                                           |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY<br>VRTC<br>VRTC<br>VRTY<br>VRBC         | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Bottom Voltage Reference Output for C-ADC</li> </ul>                                                      |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY<br>VRTC<br>VRTC<br>VRTY<br>VRBC<br>VRBY | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Bottom Voltage Reference Output for C-ADC</li> <li>: Bottom Voltage Reference Output for Y-ADC</li> </ul> |

| RSTB<br>SCL<br>SDA<br>SLA0<br>ST1, ST0<br>TEST<br>VCLY<br>VRTC<br>VRTC<br>VRTY<br>VRBC         | <ul> <li>: Testing Selection</li> <li>: System Reset (active-low)</li> <li>: Serial Clock Input</li> <li>: Serial Data Input / Output</li> <li>: Slave Address Selection</li> <li>: Inner States Monitor</li> <li>: Testing Selection</li> <li>: Clamp Voltage Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Top Voltage Reference Output for Y-ADC</li> <li>: Bottom Voltage Reference Output for C-ADC</li> </ul>                                                      |

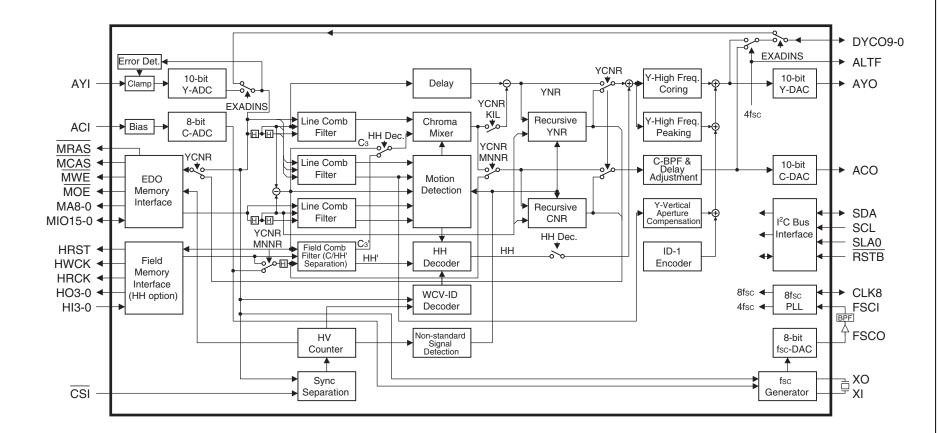

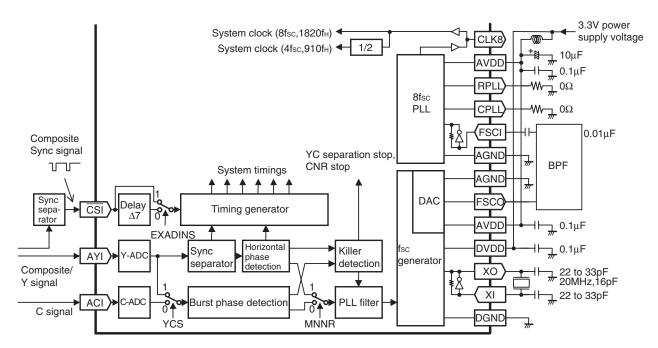

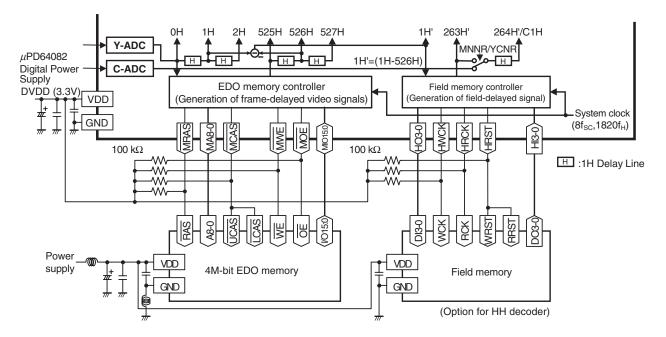

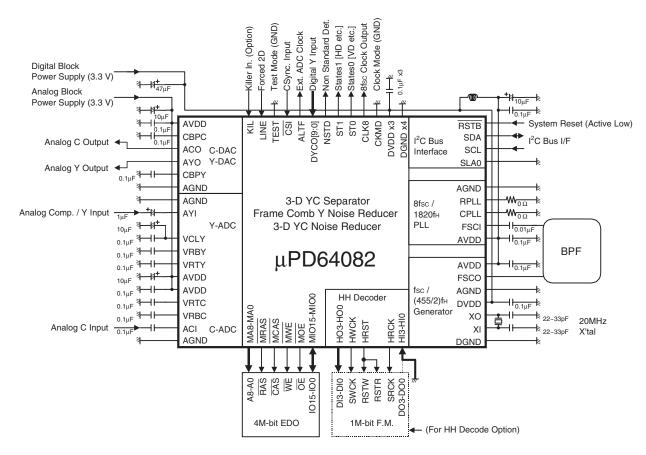

**BLOCK DIAGRAM**

$\mu$  PD64082

4

## TERMINOLOGY

This manual use the abbreviation listed below:

| ADC                 | : | A/D (Analog to Digital) converter                                          |

|---------------------|---|----------------------------------------------------------------------------|

| DAC                 | : | D/A (Digital to Analog) converter                                          |

| LPF                 | : | Low-pass filter                                                            |

| BPF                 | : | Band-pass filter                                                           |

| HPF                 | : | High-pass filter                                                           |

| Y signal, or Luma   | : | Luminance, or luminance signal                                             |

| C signal, or Chroma | : | Color signal, or chrominance signal                                        |

| MN signal           | : | MUSE-NTSC convert signal (Japan only)                                      |

| fsc                 | : | Color subcarrier frequency = 3.579545 MHz                                  |

| 4fsc                | : | 4 times fsc, burst locked clock = 14.318180 MHz                            |

| 8fsc                | : | 8 times fsc, burst locked clock = 28.636360 MHz                            |

| fн                  | : | Horizontal sync frequency = 15.734 kHz                                     |

| 910fн               | : | 910 times fH, line locked clock = 14.318180 MHz                            |

| 1820fн              | : | 1820 times fн, line locked clock = 28.636360 MHz                           |

| fv                  | : | Vertical sync frequency = 59.94 Hz                                         |

| NR                  | : | Noise reduction                                                            |

| YNR                 | : | Luminance (Y) noise reduction                                              |

| CNR                 | : | Chrominance (C) noise reduction                                            |

| WCV-ID              | : | Wide Clear Vision standard ID signal (Japan only)                          |

| НН                  | : | Horizontal Helper signal (Wide Clear Vision Standard category: Japan only) |

|                     |   |                                                                            |

In the following diagrams, a serial bus register is enclosed in a box:

## LIMITATION ITEMS

#### 1. Clamp noise

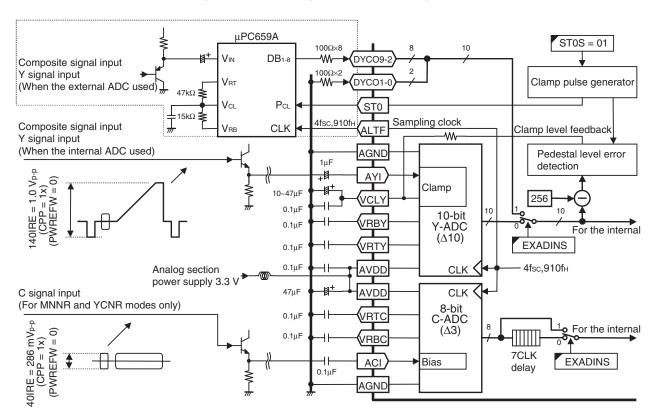

Clamp noise (about 3 mV) appears in the sync-tip of luminance signal output. Please make input signal (AYI: 88 pin) low impedance to decrease this noise.

#### 2. 2fsc noise

There is noise of the 2fsc (7.2 MHz) component in the luminance signal output. This 2fsc noise occurred by internal 10-bit A/D converter of the  $\mu$ PD64082.

Please consider to decrease this noise enough when you design output buffer and amplifier circuit.

#### [Other measures]

- (a) Using coring (by serial bus register)

- ex. SA10h, D7-D5 = 010 or 011

- (b) Using trap filter for 2fsc.

- (c) Using external ADC (refer to 3.5 External Y-ADC Connection Method).

#### 3. Trail noise

The trail noise like the afterimage sometimes occurs when the operation mode (NRMD = 00 to 01) and the sensitivity of horizontal sync nonstandard signal detection (VTRR register) are changed at the same time. In this case set to forced horizontal sync nonstandard (SA01h, D5-D4: NSDS = 11) or forced inter-line processing (SA01h, D3-D2: MSS = 10) or NR off (SA06h = 00h) in the period in the 2 fields before to 8 fields behind in the moment to change.

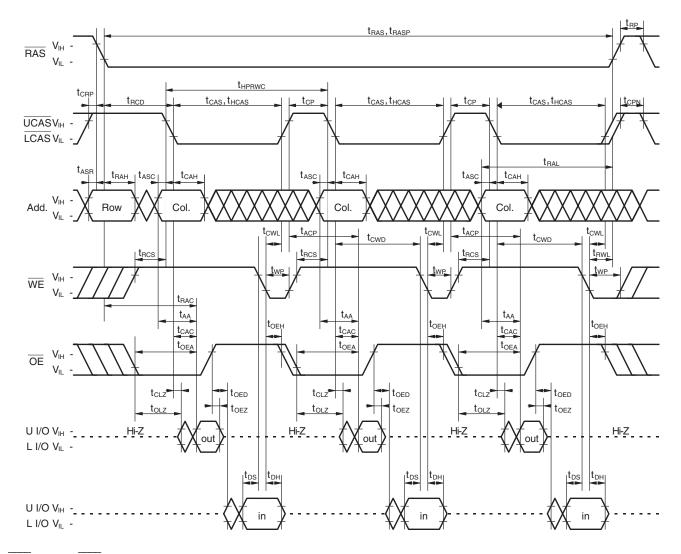

#### ★ 4. Memory power-down mode

When using the memory power-down mode (SYSPDS = 1), the memory control lines (RAS,  $\overline{CAS}$ ,  $\overline{OE}$ ,  $\overline{WE}$ ) enter a floating state and must be pulled up to DVDD (3.3 V) to avoid unstable memory operation.

#### ★ 5. Internal synchronous separator

The internal synchronous separator performance may drop slightly if non-standard signals are input or at startup. If using only this function (EXCSS = 0), evaluate the performance carefully.

#### ★ 6. Internal killer detector

The internal killer detector performance may drop for weak signals. If using this function, evaluate the performance carefully.

## CONTENTS

| 1. | PIN FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                                |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

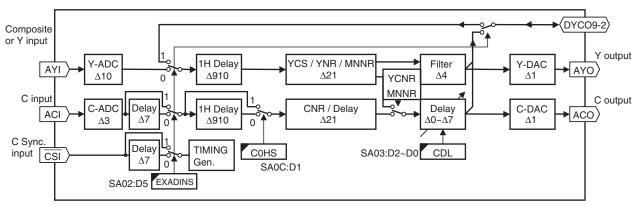

| 2. | SYSTEM OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 12                                                                             |

|    | 2.1 Operation Modes                                                                                                                                                                                                                                                                                                                                                                                                                              | . 12                                                                             |

|    | 2.2 Filter Processing                                                                                                                                                                                                                                                                                                                                                                                                                            | . 14                                                                             |

|    | 2.3 System Delay                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 14                                                                             |

| 3. | VIDEO SIGNAL INPUT BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                         | . 15                                                                             |

|    | 3.1 Video Signal Inputs                                                                                                                                                                                                                                                                                                                                                                                                                          | . 15                                                                             |

|    | 3.2 Pedestal Level Reproduction                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

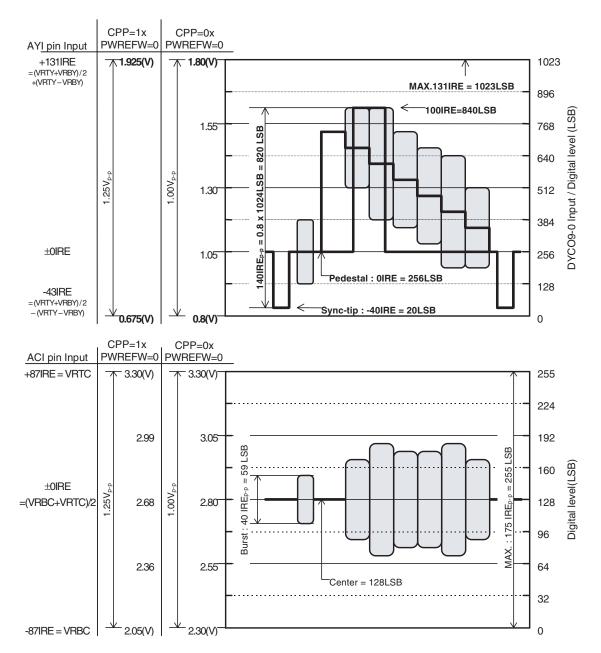

|    | 3.3 Video Signal Input Level                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|    | 3.4 Pin Treatment                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

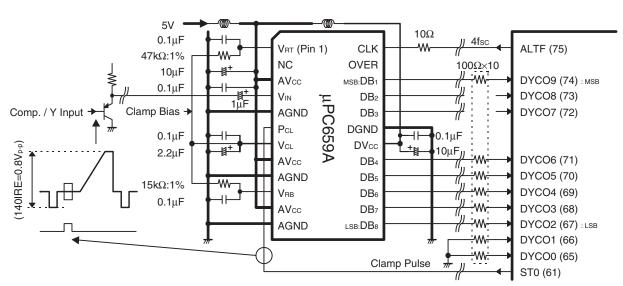

|    | 3.5 External Y-ADC Connection Method                                                                                                                                                                                                                                                                                                                                                                                                             | . 17                                                                             |

| 4. | CLOCK/TIMING GENERATION BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|    | 4.1 Sync Separator and Timing Generator                                                                                                                                                                                                                                                                                                                                                                                                          | . 19                                                                             |

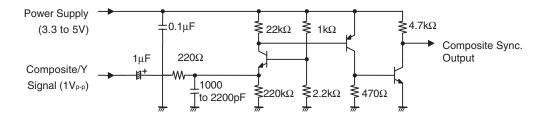

|    | 4.2 Composite Sync Signal Input                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|    | 4.3 Horizontal/Burst Phase Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|    | 4.4 PLL Filter Circuit                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|    | 4.5 Killer Detection Circuit                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|    | 4.6 fsc Generator                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|    | 4.7 8fsc-PLL Circuit                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

|    | 4.8 Pin Treatment                                                                                                                                                                                                                                                                                                                                                                                                                                | . 20                                                                             |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

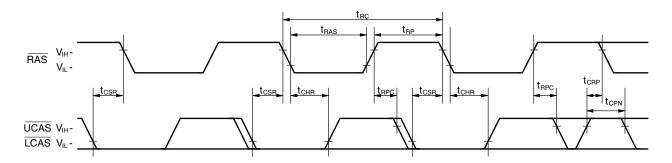

| 5. | MEMORY INTERFACE BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                           | .21                                                                              |

| 5. | 5.1 EDO Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                        | .21                                                                              |

| 5. |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | .21                                                                              |

| 5. | 5.1 EDO Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                        | . 21<br>. 21                                                                     |

| 5. | <ul><li>5.1 EDO Memory Controller</li><li>5.2 Field Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                  | .21<br>.21<br>.21                                                                |

|    | <ul> <li>5.1 EDO Memory Controller</li> <li>5.2 Field Memory Controller</li> <li>5.3 Pin Treatment</li> </ul>                                                                                                                                                                                                                                                                                                                                    | .21<br>.21<br>.21<br>.21                                                         |

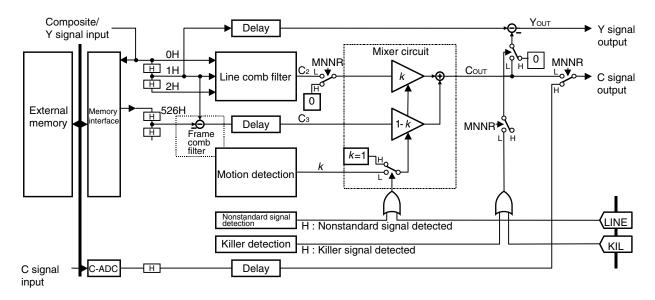

|    | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.21<br><b>.22</b><br>.22                                           |

|    | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.21<br>.22<br>.22<br>.22                                           |

|    | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.21<br>.22<br>.22<br>.22                                           |

|    | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22                                    |

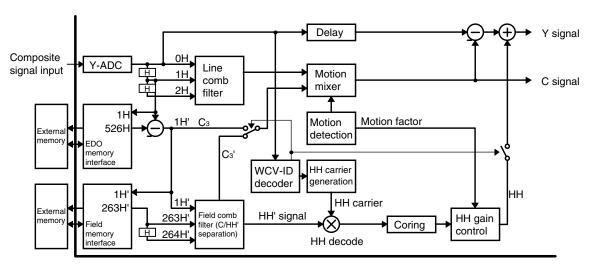

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22                             |

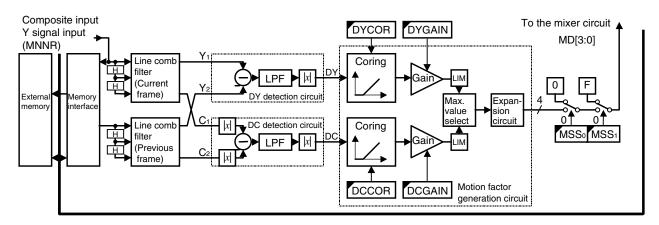

| 6. | 5.1 EDO Memory Controller         5.2 Field Memory Controller         5.3 Pin Treatment         COMB FILTER BLOCK         6.1 Line Comb Filter         6.2 Frame Comb Filter         6.3 Mixer Circuit         6.4 C Signal Subtraction         MOTION DETECTION BLOCK                                                                                                                                                                           | .21<br>.21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22               |

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23 |

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23<br>.23 |

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23<br>.23 |

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23 |

| 6. | <ul> <li>5.1 EDO Memory Controller</li> <li>5.2 Field Memory Controller</li> <li>5.3 Pin Treatment</li> <li>COMB FILTER BLOCK</li> <li>6.1 Line Comb Filter</li> <li>6.2 Frame Comb Filter</li> <li>6.3 Mixer Circuit</li> <li>6.4 C Signal Subtraction</li> </ul> MOTION DETECTION BLOCK 7.1 Line Comb Filter 7.2 DY Detection Circuit 7.3 DC Detection Circuit 7.4 Motion Factor Generation Circuit 7.5 Forcible Control for The Motion Factor | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23<br>.23 |

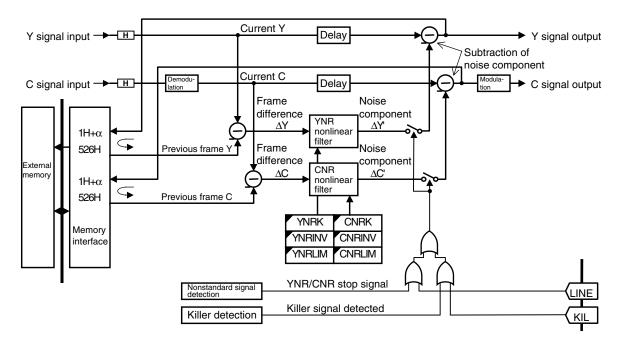

| 6. | <ul> <li>5.1 EDO Memory Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                     | .21<br>.21<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.22<br>.23<br>.23<br>.23 |

# NEC

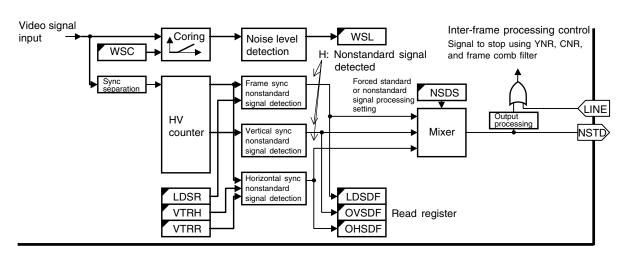

| 9.                       | NONSTANDARD SIGNAL DETECTION BLOCK                                                                                          | . 25                                                                                    |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                          | 9.1 Horizontal Sync Nonstandard Signal Detection                                                                            | .25                                                                                     |

|                          | 9.2 Vertical Sync Nonstandard Signal Detection                                                                              | .25                                                                                     |

|                          | 9.3 Frame Sync Nonstandard Signal Detection                                                                                 | .25                                                                                     |

|                          | 9.4 Forced Standard or Nonstandard Signal Control                                                                           | .25                                                                                     |

|                          | 9.5 Noise Level Detection                                                                                                   | .25                                                                                     |

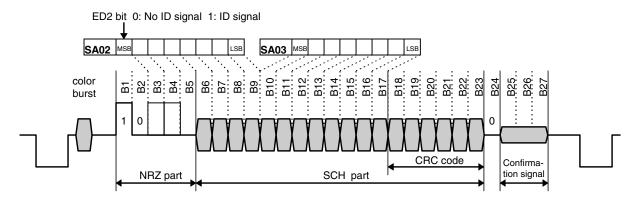

| 10.                      | WCV-ID DECODER BLOCK                                                                                                        | . 26                                                                                    |

|                          | 10.1 WCV-ID Decoder                                                                                                         | . 26                                                                                    |

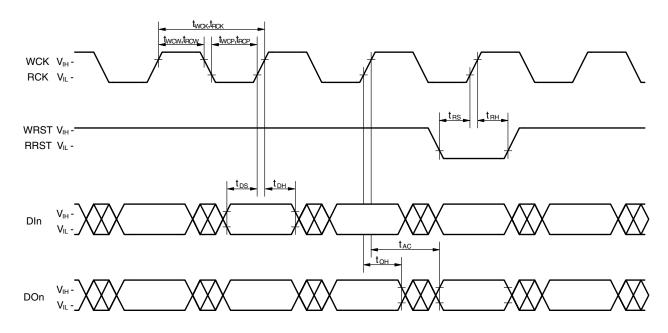

| 11.                      | HH DECODER BLOCK                                                                                                            | .27                                                                                     |

|                          | 11.1 C/HH' Separation                                                                                                       | .27                                                                                     |

|                          | 11.2 HH Decoding                                                                                                            | .27                                                                                     |

|                          | 11.3 HH Gain Control                                                                                                        | .27                                                                                     |

|                          | 11.4 Transition to HH Decoding                                                                                              | . 27                                                                                    |

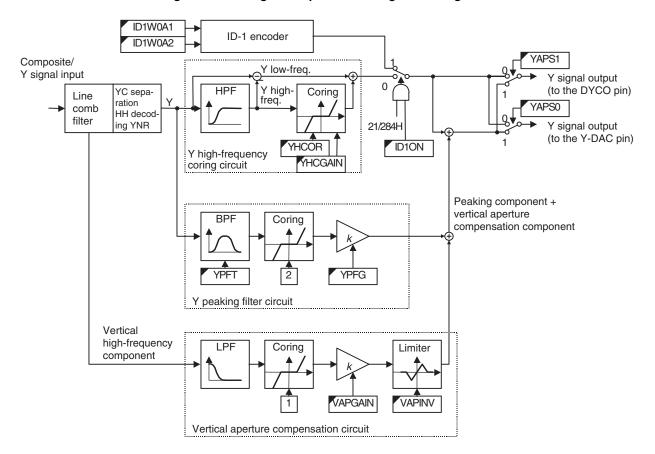

| 12.                      | Y SIGNAL OUTPUT PROCESSING BLOCK                                                                                            | .28                                                                                     |

|                          | 12.1 Y High-Frequency Coring Circuit                                                                                        | .28                                                                                     |

|                          | 12.2 Y Peaking Filter Circuit                                                                                               | .29                                                                                     |

|                          | 12.3 Vertical Aperture Compensation Circuit                                                                                 | . 29                                                                                    |

|                          | 12.4 Turning On/Off Y Peaking and Vertical Aperture Compensation                                                            | .29                                                                                     |

|                          | 12.5 ID-1 Encoder                                                                                                           | . 29                                                                                    |

|                          |                                                                                                                             |                                                                                         |

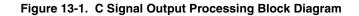

| 13.                      | C SIGNAL OUTPUT PROCESSING BLOCK                                                                                            | . 30                                                                                    |

| 13.                      | C SIGNAL OUTPUT PROCESSING BLOCK                                                                                            |                                                                                         |

| 13.                      |                                                                                                                             | . 30                                                                                    |

|                          | 13.1 C Signal Delay Adjustment                                                                                              | . 30<br>. 30                                                                            |

|                          | <ul><li>13.1 C Signal Delay Adjustment</li><li>13.2 BPF and Gain Processing</li></ul>                                       | . 30<br>. 30<br><b>. 31</b>                                                             |

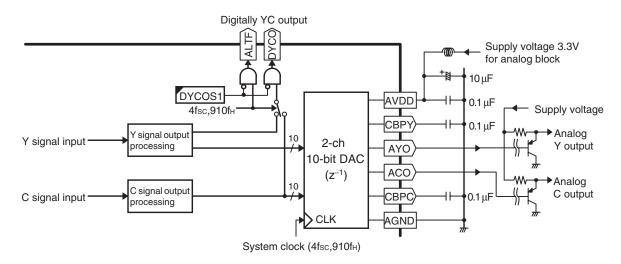

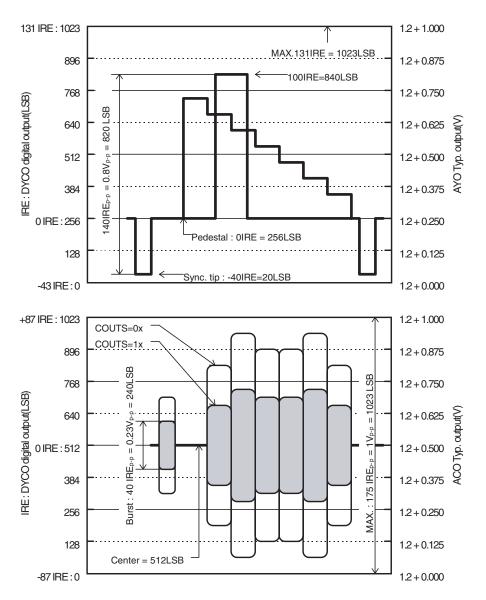

|                          | <ul> <li>13.1 C Signal Delay Adjustment</li> <li>13.2 BPF and Gain Processing</li> <li>VIDEO SIGNAL OUTPUT BLOCK</li> </ul> | . 30<br>. 30<br><b>. 31</b><br>. 31                                                     |

|                          | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br><b>. 31</b><br>. 31<br>. 31                                             |

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br>. 31<br>. 31<br>. 31<br>. 32<br>. 32                                    |

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br>. 31<br>. 31<br>. 31<br>. 32<br>. 33                                    |

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br>. 31<br>. 31<br>. 32<br>. 33<br>. 33<br>. 33                            |

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br>. 31<br>. 31<br>. 32<br>. 33<br>. 33<br>. 33                            |

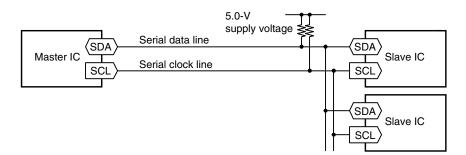

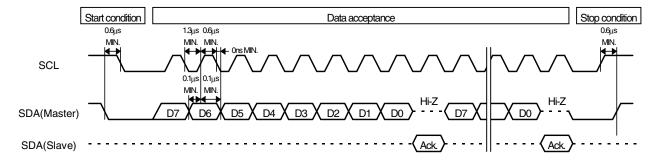

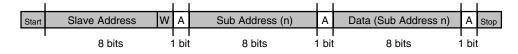

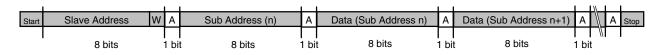

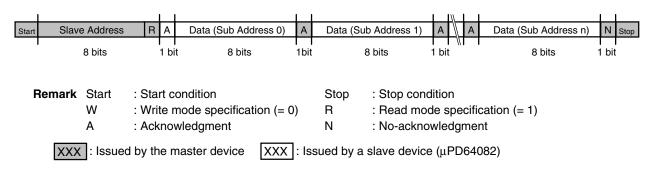

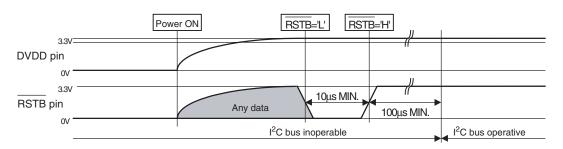

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | . 30<br>. 30<br>. 31<br>. 31<br>. 32<br>. 33<br>. 33<br>. 34<br>. 35                    |

| 14.                      | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | .30<br>.30<br>.31<br>.31<br>.32<br>.33<br>.33<br>.34<br>.35<br>.36                      |

| 14.<br>15.<br>16.        | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | .30<br>.30<br>.31<br>.31<br>.32<br>.33<br>.33<br>.34<br>.35<br>.36<br>.53               |

| 14.<br>15.<br>16.<br>17. | <ul> <li>13.1 C Signal Delay Adjustment</li></ul>                                                                           | .30<br>.30<br>.31<br>.31<br>.32<br>.33<br>.33<br>.33<br>.34<br>.35<br>.36<br>.53<br>.63 |

## 1. PIN FUNCTIONS

Table 1-1. Pin Functions (1/3)

|   | No.   | Symbol         | I/O | Level          | Buffer type<br>PU/PD [kΩ] | Description                                                         |

|---|-------|----------------|-----|----------------|---------------------------|---------------------------------------------------------------------|

|   | 1     | DGND           | -   | -              |                           | Digital section ground                                              |

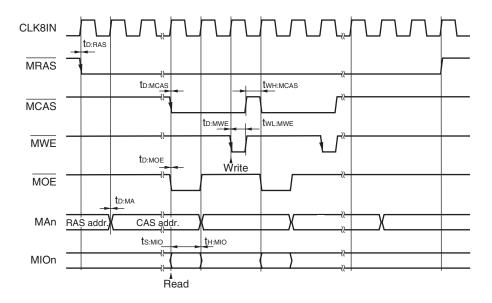

| * | 2-9   | MA7-MA0        | 0   | TTL<br>3-state | 1 mA                      | Address output for external EDO memory                              |

| * | 10    | MCAS           | 0   | TTL<br>3-state | 1 mA                      | CAS output for external EDO memory (active-low)                     |

| * | 11    | MWE            | 0   | TTL<br>3-state | 1 mA                      | WE output for external EDO memory (active-low)                      |

| * | 12    | MOE            | 0   | TTL<br>3-state | 1 mA                      | OE output for external EDO memory (active-low)                      |

|   | 13-28 | MIO15-<br>MIO0 | I/O | TTL<br>3-state | 1 mA<br>5 V resistant     | Data input/output for external EDO memory                           |

|   | 29    | DGND           | -   | -              |                           | fsc generator digital section ground                                |

|   | 30    | XI             | I   | -              |                           | fsc generator reference clock input (X'tal is connected.)           |

|   |       |                | 0   | -              |                           | fsc generator reference clock inverted output (X'tal is connected.) |

|   | 32    | DVDD           | -   | -              |                           | fsc generator digital section supply voltage                        |

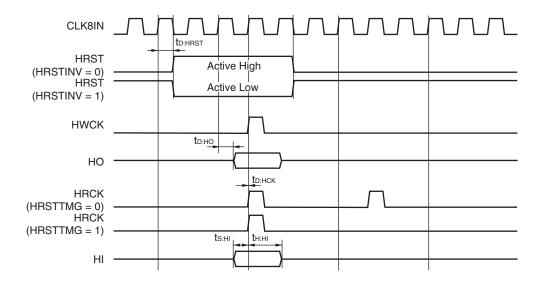

|   | 33-36 | HO3-HO0        | 0   | TTL<br>3-state | 1 mA                      | Data output for external field memory (Open when not used.)         |

|   |       |                |     |                |                           | HO3 is the MSB, HO0 is the LSB.                                     |

|   | 37    | HWCK           | 0   | TTL<br>3-state | 3 mA                      | Write clock output for external field memory (Open when not used.)  |

|   | 38    | HRCK           | 0   | TTL<br>3-state | 3 mA                      | Read clock output for external field memory (Open when not used.)   |

|   | 39    | HRST           | 0   | TTL<br>3-state | 1 mA                      | Reset signal output for external field memory (Open when not used.) |

|   | 40    | DGND           | -   | -              |                           | Digital section ground                                              |

|   | 41-44 | 41-44 HI3-HI0  |     | TTL            | 5 V resistant             | Input for external field memory (Grounded when not used.)           |

|   |       |                |     |                |                           | HI3 is the MSB, HI0 is the LSB.                                     |

|   | 45    | DVDD           | -   | -              |                           | Digital section supply voltage                                      |

|   | 46    | AVDD           |     |                |                           | fsc generator DAC section supply voltage                            |

|   | 47    | FSCO           | -   | Analog         |                           | fsc generator fsc output                                            |

|   | 48    | AGND           | -   | -              |                           | fsc generator DAC section ground                                    |

|   | 49    | AGND           | -   | -              |                           | 8fsc-PLL ground                                                     |

|   | 50    | FSCI           | -   | Analog         |                           | 8fsc-PLL fsc input                                                  |

|   | 51    | CPLL           | -   | -              |                           | 8fsc-PLL filter output (Grounded)                                   |

|   | 52    | RPLL           | -   | Schmitt        | PU:50                     | Test pin (Grounded)                                                 |

|   | 53    | AVDD           | -   | -              |                           | 8fsc-PLL section supply voltage                                     |

## Table 1-1. Pin Functions (2/3)

| No.   | Symbol                             | I/O | Level                            | Buffer type<br>PU/PD [kΩ] | Description                                                                                                                                                           |  |

|-------|------------------------------------|-----|----------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 54    | CKMD                               | I   | TTL                              | 5 V resistant<br>PD:50    | Clock mode test input ('L' : Normal mode, 'H' : Test mode)<br>(Grounded)                                                                                              |  |

| 55    | DGND                               | -   | -                                |                           | Digital section ground                                                                                                                                                |  |

| 56    | CLK8                               | 0/1 | TTL<br>3-state                   | 3 mA<br>5 V resistant     | $8 f_{SC}$ clock output ( $8 f_{SC}$ clock input when CKMD pin = H )                                                                                                  |  |

| 57    | RSTB                               | I   | Schmitt                          | 5 V resistant<br>PU:50    | System reset input (active-low)<br>(Active-low reset pulse is input from the outside.)                                                                                |  |

| 58    | SLA0                               | I   | TTL                              | 5 V resistant<br>PD:50    | l <sup>2</sup> C bus slave address selection input<br>('L' : B8 / B9h, 'H' : BA / BBh)                                                                                |  |

| 59    | SCL                                | I   | Schmitt                          | 5 V resistant             | nt I <sup>2</sup> C bus clock input (Connected to system SCL line)                                                                                                    |  |

| 60    | SDA                                | 1/0 | Schmitt<br>N-ch<br>open<br>drain | 5 mA<br>5 V resistant     | I <sup>2</sup> C bus data input/output (Connected to system SDA line)                                                                                                 |  |

| 61    | ST0                                | 0   | TTL                              | 1 mA                      | Internal signal monitor output 0                                                                                                                                      |  |

| 62    | ST1                                | 0   | TTL                              | 1 mA                      | Internal signal monitor output 1                                                                                                                                      |  |

| 63    | NSTD                               | 0   | TTL                              | 1 mA                      | Nonstandard signal detection monitor output<br>('L' : standard, 'H' : nonstandard)                                                                                    |  |

| 64    | DVDD                               | -   | -                                |                           | Digital section supply voltage                                                                                                                                        |  |

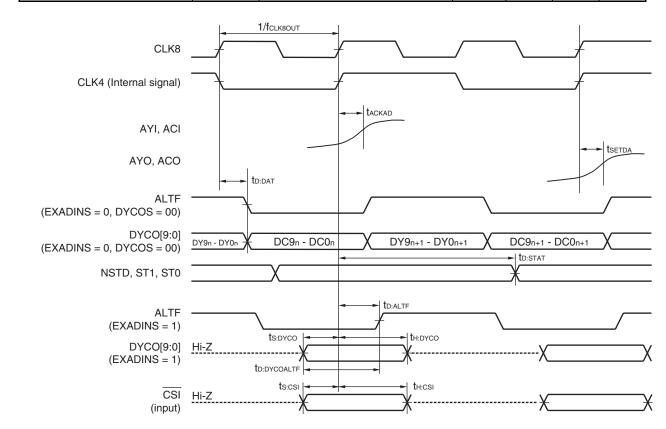

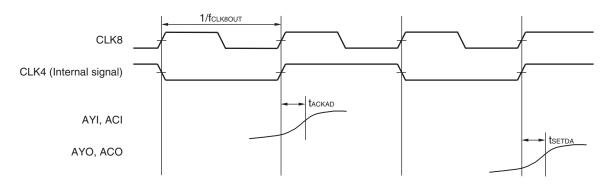

| 65-74 | DYCO0-<br>DYCO9<br>(LSB)-<br>(MSB) | I/O | TTL                              | 1 mA<br>5 V resistant     | EXADINS=0: Digital YC signal alternate output<br>EXADINS=1: Digital video data input for external Y-ADC<br>(Pull down unuse lower bit pins via 100 $\Omega$ resistor) |  |

| 75    | ALTF                               | 0   | TTL                              | 1 mA                      | DYCO0 is the LSB, DYCO9 is the MSB.<br>EXADINS=0: Digital YC signal alternate flag output<br>('L' : C, 'H' : Y)<br>EXADINS=1: 4fsc clock output for external Y-ADC    |  |

| 76    | CSI                                | I   | Schmitt                          | 5 V resistant<br>PD:50    | Composite sync input (active-low)                                                                                                                                     |  |

| 77    | TEST                               | I   | TTL                              | 5 V resistant<br>PD:50    | Test pin for IC selection ('L' : Normal mode, 'H' : Test mode)<br>(Grounded)                                                                                          |  |

| 78    | LINE                               | I   | TTL                              | 5 V resistant<br>PD:50    | Forced inter-line processing selection input<br>('L' : ordinary processing, 'H' : forced inter-line processing)                                                       |  |

| 79    | KIL                                | I   | TTL                              | 5 V resistant<br>PD:50    |                                                                                                                                                                       |  |

| 80    | DGND                               | -   | -                                |                           | Digital section ground                                                                                                                                                |  |

| 81    | AVDD                               | -   | -                                |                           | Y-DAC and C-DAC supply voltage                                                                                                                                        |  |

| 82    | CBPC                               | 0   | Analog                           |                           | C-DAC phase compensation output                                                                                                                                       |  |

| 83    | ACO                                | 0   | Analog                           |                           | C-DAC analog C signal output                                                                                                                                          |  |

| 84    | AYO                                | 0   | Analog                           |                           | Y-DAC analog Y signal output                                                                                                                                          |  |

| 85    | CBPY                               | 0   | Analog                           |                           | Y-DAC phase compensation output                                                                                                                                       |  |

| 86    | AGND                               | -   | -                                |                           | Y-DAC and C-DAC ground                                                                                                                                                |  |

| 87    | AGND                               | -   | -                                | 1                         | Y-ADC ground                                                                                                                                                          |  |

$\star$

$\star$

| No. | Symbol | I/O | Level          | Buffer type<br>PU/PD [kΩ]    | Description                                     |

|-----|--------|-----|----------------|------------------------------|-------------------------------------------------|

| 88  | AYI    | I   | Analog         |                              | Y-ADC analog composite signal or Y signal input |

| 89  | VCLY   | 0   | Analog         | Y-ADC clamp potential output |                                                 |

| 90  | VRBY   | 0   | Analog         |                              | Y-ADC bottom reference voltage output           |

| 91  | VRTY   | 0   | Analog         |                              | Y-ADC top reference voltage output              |

| 92  | AVDD   | -   | -              |                              | Y-ADC supply voltage                            |

| 93  | AVDD   | -   | -              |                              | C-ADC supply voltage                            |