# CMOS-6/6A/6V/6X 1.0-MICRON CMOS GATE ARRAYS

**April 1992**

# Description

NEC's CMOS-6 gate array families (CMOS-6, CMOS-6A, CMOS-6V and CMOS-6X) are ultra-high performance, sub-micron effective channel length CMOS products created for high-integration ASIC applications.

The device processing includes 1.0-micron (drawn) silicon-gate CMOS technology and three-layer (CMOS-6) and two-layer (CMOS-6A, CMOS-6V, CMOS-6V) metallization. This technology features channelless (sea-of-gates) architecture in densities from 1,200 to 177,408 equivalent gates, with an internal gate delay of 270 ps (F/O=1; L = 0). Output drive is variable to 18 mA. Slew rate buffers are also available.

CMOS-6 products are fully supported by NEC's advanced ASIC design technology. NEC's OpenCAD® integration system lets the designer choose the most powerful design tools and services available. The CMOS-6/6A/6V macro cell (block) library is compatible with the powerful CMOS-5 block library, which contain over 300 cells and more than 100 interface options.

NEC offers advanced packaging solutions with both through-hole and surface-mount ceramic PGAs and flat packages. These heat-sink-equipped packages give CMOS-6 devices the performance edge in high-integration applications.

#### **Features**

- □ Channelless, 1.µm CMOS high-density architecture

- □ Variable output drive: 4.5, 9.0, 13.5, or 18.0 mA

- Slew rate output buffers

- = Free size memory blocks to 64 Kbytes (16K x 4, μPD65676)

- □ Powerful block library with more than 400 macros

- 3V characterized block library

- New 0.65 mm 184-pin plastic QFP for cost effective designs

- ☐ High I/O to gate ratio for CMOS-6V and CMOS-6X

#### **Publications**

This data sheet contains preliminary specifications, package information, and operational data for the CMOS-6 gate array families. Additional design information is available in NEC's CMOS-6 Block Library and CMOS-6 Design Manual. Contact your local NEC Design Center or the NEC Literature Center for further ASIC design information; see the back of this data sheet for locations and phone numbers.

OpenCAD is a registered trademark of NEC Electronics Inc.

70020-5

Figure 1. Sample CMOS-6/6A/6V/6X Packages

# **Gate Array Sizes**

|                |           | Estimated  | i Usable Gates |              |

|----------------|-----------|------------|----------------|--------------|

| Device         | Available | •          | Design =       | I/O Pads     |

| (μ <b>PD</b> ) | Gates     | 50% Memory | All Random*    | (Max.)       |

| CMOS-6         | X Devices |            |                |              |

| 65612          | 1,200     | 1,000      | 800            | 64           |

| 65622          | 2,700     | 2,300      | 1,900          | 84           |

| 65626          | 3,900     | 3,300      | 2,700          | 104          |

| 65632          | 5,600     | 3,900      | 3,900          | 104          |

| CMOS-6         | A Devices |            |                |              |

| 65630          | 5,376     | 4,600      | 3,800          | 84           |

| 65636          | 8,000     | 6,800      | 5,600          | 100          |

| 65640          | 11,520    | 9,800      | 8,100          | 120          |

| 65646          | 16,240    | 13,800     | 11,400         | 140          |

| 65650          | 21,120    | 18,000     | 14,800         | 160          |

| 65654          | 30,720    | 26,100     | 21,500         | 192          |

| CMOS-6         | V Devices |            |                |              |

| 65631          | 5,544     | 4,700      | 3,900          | 140          |

| 65641          | 11,520    | 9,800      | 8,100          | 160          |

| 65644          | 14,040    | 11,900     | 9,800          | 160          |

| 65647          | 16,240    | 13,800     | 11,400         | 160          |

| 65648          | 18,600    | 15,800     | 13,000         | 160          |

| 65651          | 21,120    | 18,000     | 14,800         | 220          |

| 65652          | 26,640    | 22,600     | 18,600         | 220          |

| 65655          | 30,720    | 26,100     | 21,500         | <b>"</b> 220 |

| CMOS-6         | Devices   |            |                |              |

| 65658          | 42,240    | 37,000     | 21,700         | 220          |

| 65664          | 72,576    | 63,500     | 54,400         | 288          |

| 65672          | 119,232   | 104,300    | 89,400         | 368          |

| 65676          | 177,408   | 155,200    | 133,100        | 448          |

Actual gate utilitization may vary depending on circuit implementation.

Utilization is 75% for three-layer metal; 70% for two-layer metal.

Memory utilization is determined by 50% x available gates + (utilization x 50% available gates)

Depending on package and circuit specification, some pads are used for  ${\bf V}_{\rm DD}$  and GND and are unavailable as signal pads.

#### **Circuit Architecture**

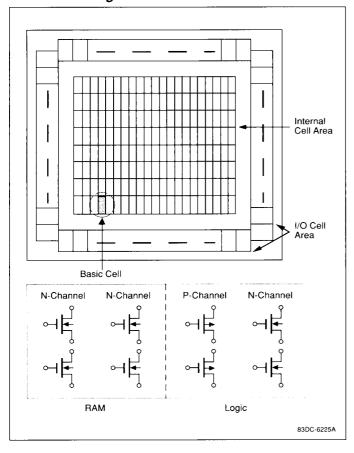

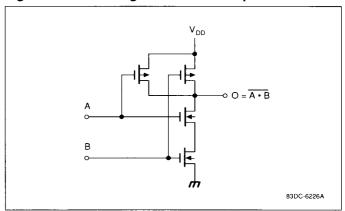

CMOS-6 products are built with NEC's 1-micron channelless architecture. As shown in figure 2, CMOS gate array chips are divided into I/O and internal cell areas. The I/O cell area contains input and output buffers that isolate the internal cells from high-energy external signals. The internal cell area is an array of basic cells, each composed of two p-channel MOS transistors and two n-channel MOS transistors, as well as four additional n-channel MOS transistors for compact RAM design. A cell configured as a two-input NAND gate is shown in figure 3. These p-channel and n-channel transistors are sized to offer a superb ratio of speed to silicon area.

Figure 2. Chip Layout and Internal Cell Configuration

Figure 3. Cell Configured as a Two-Input NAND

## **Output Slew Rate Selection**

Fast rise and fall times of CMOS output buffers can cause system noise and signal overshoot. When an unterminated line is being driven by a buffer, the maximum line length is determined by the rise and fall time of the output buffers and the round-trip signal delay of the line.

As a general rule, the round-trip delay of the line should not exceed the rise or fall time of the driving signal. Transmission lines that are longer than those determined by the above rule can cause system performance degradation because of reflections and ringing. One benefit of slew rate output buffers is that longer interconnections on a PC board (and routing flexibility) are possible with slew rate output buffers.

The ASIC designer can slow down the output edge rate by selecting the slew rate output buffer and thus allowing for a longer line.

Also, as the slew rate buffers inject less noise than their non-slew rate counterparts into the internal power and ground busses of the devices, the slew rate buffers require fewer power pairs for simultaneous switching outputs.

# **Absolute Maximum Ratings**

| Power supply voltage, V <sub>DD</sub>                 | -0.5 to +6.5 V                    |

|-------------------------------------------------------|-----------------------------------|

| Input/output voltage, V <sub>I</sub> / V <sub>O</sub> | -0.5 V to V <sub>DD</sub> + 0.5 V |

| Latch-up current, I <sub>LATCH</sub>                  | >1 A (typ)                        |

| Output current, I <sub>O</sub>                        |                                   |

| 4.5-mA drive                                          | 10 mA                             |

| 9-mA drive                                            | 20 mA                             |

| 13.5-mA drive                                         | 30 mA                             |

| 18-mA drive                                           | 40 mA                             |

| Operating temperature, T <sub>OPT</sub>               | −40 to +85°C                      |

| Storage temperature, T <sub>STG</sub>                 | −65 to +150°C                     |

|                                                       |                                   |

**Caution:** Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.

# Input/Output Capacitance

$V_{DD} = V_{I} = 0 \text{ V}; f = 1 \text{ MHz}$

| Terminal | Symbol           | Тур | Max | Unit |

|----------|------------------|-----|-----|------|

| Input    | C <sub>IN</sub>  | 10  | 25  | pF   |

| Output   | C <sub>OUT</sub> | 10  | 25  | pF   |

| I/O      | C <sub>I/O</sub> | 10  | 25  | pF   |

#### Note:

(1) Values include package pin capacitance.

## **Power Consumption**

| Description   | Limits (max) | Unit   | Test Conditions        |

|---------------|--------------|--------|------------------------|

| Internal cell | 8            | μW/MHz | F/O = 3; L = 3 mm      |

| Input block   | 46           | μW/MHz | F/O = 3; L = 3 mm      |

| Output block  | .98          | mW/MHz | C <sub>L</sub> = 15 pF |

# **Recommended Operating Conditions**

|                                  |                                 | CMOS                | Level               | TTL  | Level           | Unit |

|----------------------------------|---------------------------------|---------------------|---------------------|------|-----------------|------|

| Parameter                        | Symbol                          | Min                 | Max                 | Min  | Max             |      |

| Power supply voltage             | V <sub>DD</sub>                 | 4.5                 | 5.5                 | 4.75 | 5.25            | ٧    |

| Ambient temperature              | T <sub>A</sub>                  | -40                 | +85                 | 0    | +70             | °C   |

| Low-level input voltage          | V <sub>IL</sub>                 | 0                   | 0.3 V <sub>DD</sub> | 0    | 0.8             | V    |

| High-level input voltage         | V <sub>IH</sub>                 | 0.7 V <sub>DD</sub> | V <sub>DD</sub>     | 2.2  | V <sub>DD</sub> | V    |

| Input rise or fall time          | t <sub>R</sub> , t <sub>F</sub> | 0                   | 200                 | 0    | 200             | ns   |

| Input rise or fall time, Schmitt | t <sub>R</sub> , t <sub>F</sub> | 0                   | 10                  | 0    | 10              | ms   |

| Positive Schmitt-trigger voltage | V <sub>P</sub>                  | 1.8                 | 4.0                 | 1.2  | 2.4             | ٧    |

| Negative Schmitt-trigger voltage | V <sub>N</sub>                  | 0.6                 | 3.1                 | 0.6  | 1.8             | ٧    |

| Hysteresis voltage               | V <sub>H</sub>                  | 0.3                 | 1.5                 | 0.3  | 1.5             | V    |

## **AC Characteristics**

$V_{DD} = 5 \text{ V} \pm 10\%$ ;  $T_{\Delta} = -40 \text{ to } +85^{\circ}\text{C}$

| Parameter                     | Symbol           | Min | Тур  | Max | Unit | Conditions             |

|-------------------------------|------------------|-----|------|-----|------|------------------------|

| Toggle frequency              | f <sub>TOG</sub> | 120 |      |     | MHz  | D-F/F; F/O = 2         |

| Delay time, internal gate     | t <sub>PD</sub>  |     | 270  |     | ps   | F/O = 1; L = 0 mm      |

| Delay time, 2-input NAND gate |                  |     | 700  |     | ps   | F/O = 3; L = 3 mm      |

| Delay time, buffer            |                  |     |      |     |      |                        |

| Input (FI01)                  | t <sub>PD</sub>  |     | 1.25 |     | ns   | F/O = 3; L = 3 mm      |

| Output (FO01)                 | t <sub>PD</sub>  |     | 2.0  |     | ns   | C <sub>L</sub> = 15 pF |

| Output rise time              | t <sub>R</sub>   |     | 3.0  |     | ns   | C <sub>L</sub> = 15 pF |

| Output fall time              | t <sub>E</sub>   |     | 2.0  | -   | ns   | C <sub>1</sub> = 15 pF |

# **CMOS-6/6A/6V/6X**

## **DC Characteristics**

$V_{DD} = 5 \text{ V} \pm 10\%$ ;  $T_A = -40 \text{ to } +85 \text{ }^{\circ}\text{C}$

| Parameter                                 | Symbol          | Min                  | Тур              | Max  | Unit | Conditions                |

|-------------------------------------------|-----------------|----------------------|------------------|------|------|---------------------------|

| Quiescent current (Note 1)                | ار              |                      | 0.1              | 400  | μА   | $V_1 = V_{DD}$ or GND     |

| Input leakage current                     |                 |                      |                  |      |      |                           |

| Regular                                   | 1,              |                      | 10 <sup>-5</sup> | 10   | μΑ   | $V_{I} = V_{DD}$ or GND   |

| 50 kΩ pull-up                             | 1,              | -40                  | -100             | -270 | μΑ   | V <sub>I</sub> = GND      |

| 5 kΩ pull-up                              | 1,              | -0.35                | -1.0             | -2.2 | mA   | V <sub>I</sub> = GND      |

| 50 kΩ pull-down                           | l <sub>1</sub>  | 45                   | 120              | 300  | μΑ   | $V_I = V_{DD}$            |

| Off-state output leakage current          | l <sub>oz</sub> |                      |                  | 10   | μΑ   | $V_O = V_{DD}$ or GND     |

| Input clamp voltage                       | V <sub>IC</sub> | -1.2                 |                  |      | ٧    | I <sub>I</sub> = 18 mA    |

| Output short circuit current (Note 2)     | los             | -250                 |                  |      | mA   | V <sub>O</sub> = 0 V      |

| Low-level output current (CMOS)           |                 |                      |                  |      |      |                           |

| 4.5 mA (Note 3)                           | l <sub>OL</sub> | 4.5                  |                  |      | mA   | V <sub>OL</sub> = 0.4 V   |

| 9 mA (Note 3)                             | l <sub>OL</sub> | 9.0                  |                  | •    | mA   | V <sub>OL</sub> = 0.4 V   |

| 13.5 mA (Note 3)                          | l <sub>oL</sub> | 13.5                 |                  |      | mA   | V <sub>OL</sub> = 0.4 V   |

| 18 mA (Note 3)                            | l <sub>oL</sub> | 18.0                 |                  |      | mA   | V <sub>OL</sub> = 0.4 V   |

| High-level output current (CMOS)          |                 |                      |                  |      |      | -                         |

| 4.5 mA (Note 3)                           | Гон             | -2.5                 |                  |      | mA   | $V_{OH} = V_{DD} - 0.4 V$ |

| 9 mA (Note 3)                             | Гон             | -5.0                 |                  |      | mA   | $V_{OH} = V_{DD} - 0.4 V$ |

| 13.5 mA (Note 3)                          | Гон             | -7.5                 |                  |      | mA   | $V_{OH} = V_{DD} - 0.4 V$ |

| 18 mA (Note 3)                            | ІОН             | -10.0                |                  |      | mA   | $V_{OH} = V_{DD} - 0.4 V$ |

| Low-level output current (TTL)            |                 |                      |                  |      |      |                           |

| 9 mA (Note 4)                             | l <sub>OL</sub> | 9.0                  |                  |      | mA   | V <sub>OL</sub> = 0.4 V   |

| 18 mA (Note 4)                            | l <sub>oL</sub> | 18.0                 |                  |      | mA   | V <sub>OL</sub> = 0.4 V   |

| High-level output current (TTL)           |                 |                      |                  |      |      |                           |

| 9 mA (Note 4)                             | Гон             | -0.5                 |                  |      | mA   | V <sub>OH</sub> = 2.4 V   |

| 18 mA (Note 4)                            | l <sub>OH</sub> | -1.0                 |                  |      | mA   | V <sub>OH</sub> = 2.4 V   |

| Low-level output voltage                  | V <sub>OL</sub> |                      |                  | 0.1  | V    | I <sub>OL</sub> = 0 mA    |

| High-level output voltage (CMOS) (Note 3) | V <sub>OH</sub> | V <sub>DD</sub> -0.1 |                  |      | V    | i <sub>OH</sub> = 0 mA    |

| High-level output voltage (TTL) (Note 4)  | V <sub>OH</sub> | 2.6                  | 3.4              |      | ٧    | I <sub>OH</sub> = 0 mA    |

#### Notes:

- (1) The maximum value reflects the use of pull-up/pull-down resistors and oscillator blocks. Contact an NEC ASIC Design Center for assistance in calculation.

- (2) Rating is for only one output operating in this mode for less than 1 second.

- (3) CMOS-level output buffer ( $V_{DD}$  = 5 V ± 10%,  $T_A$  = -40 to +85°C). (4) TTL-level output buffer ( $V_{DD}$  = 5 V ± 5%,  $T_A$  = 0 to +70°C).

# Package Plan

|                                                                    |           | _      | S-62<br>65xx |        |             |             |             | S-6/<br>5xx |             |             |             |        |        |        | S-6\<br>65x) |        |        |      | !           | CM<br>μPD   | OS-(<br>65x)   |                          |

|--------------------------------------------------------------------|-----------|--------|--------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------|--------|--------|--------------|--------|--------|------|-------------|-------------|----------------|--------------------------|

|                                                                    | 612       | 622    | 626          | 632    | 630         | 636         | 640         | 646         | 650         | 654         | 631         | 641    | 644    | 647    | 648          | 651    | 652    | 655  | 658         | 664         | 672            | 676                      |

| K gates (usable w/o memory)                                        | 0.8       | 1.9    | 2.7          | 3.9    | 3.8         | 5.6         | 8.1         | 11.4        | 14.8        | 21.5        | 3.9         | 8.1    | 9.8    | 11.4   | 13.0         | 14.8   | 3 18.6 | 21.5 | 21.7        | 54.4        | 89.4           | 133                      |

| Maximum I/O Pins                                                   | 64        | 84     | 104          | 104    | 84          | 100         | 120         | 140         | 160         | 192         | 140         | 160    | 160    | 160    | 160          | 220    | 220    | 220  | 220         | 288         | 368            | 448                      |

| Plastic Quad Flatpack (QFP)                                        |           |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 44-pin<br>52-pin<br>64-pin<br>80-pin                               | A<br>A    | A<br>A | A<br>A<br>A  |        | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A |             |        |        |        |              |        |        |      |             |             |                |                          |

| 100-pin<br>120-pin<br>136-pin<br>160-pin                           |           |        |              |        |             | Α           | A<br>A      | A<br>A      | A<br>A<br>A | A<br>A<br>A | A<br>A<br>E | A<br>A | A<br>A | Α      | Α            |        |        |      | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A    | Α                        |

| 184-pin                                                            |           |        |              |        |             |             |             |             |             | Α           |             |        |        |        |              | Α      | Α      |      | Α           | Α           | Α              | Α                        |

| Thin Quad Flatpack (TQFP)                                          |           |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 80-pin                                                             |           |        | Α            |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| Shrink Plastic Quad Flatpack (QFF                                  | P-FP) (   | .5 m   | ım L         | ead Pi | tch)        |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 100-pin<br>120-pin<br>136-pin<br>144-pin                           |           |        |              |        |             | Α           | A<br>A      | A<br>A<br>A | A<br>A      | A<br>A<br>A | A<br>A<br>E | Α      | Α      |        |              |        |        |      | A<br>A      | A<br>A      | A<br>A         |                          |

| 160-pin*<br>176-pin<br>208-pin*<br>304-pin                         |           |        |              |        |             |             |             |             | A<br>A      | A<br>A      |             | A<br>A | A<br>A | A<br>A | A<br>A       | A<br>A | A<br>A | Α    | A<br>A<br>A | A<br>A<br>E | A<br>A<br>E    | A<br>A<br>E              |

| Ceramic Pin Grid Array (PGA)                                       |           |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 72-pin<br>132-pin<br>176-pin<br>208-pin                            |           |        |              |        |             |             | Α           | A<br>A      | A<br>A      | A<br>A<br>A | Α           | Α      |        |        |              | Α      | Α      |      | A<br>A<br>A | A<br>A<br>A | A<br>A<br>A    | A<br>A<br>A              |

| 280-pin<br>364-pin                                                 |           |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             | Α           | A<br>A         | A<br>A                   |

| Ceramic Pin Grid Array (PGA) (Bu                                   | itt Lead) | )      |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 288-pin<br>528-pin (with heat sink)<br>528-pin (without heat sink) |           |        |              |        |             |             |             |             |             |             |             |        | -      |        |              |        |        |      |             |             | A <sup>1</sup> | A <sup>1</sup><br>A<br>A |

| Plastic Leaded Chip Carrier (PLCC                                  | >)        |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

| 68-pin<br>84-pin                                                   |           |        | •            |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      | A<br>A      |             |                |                          |

| Λ – Available                                                      |           |        |              |        |             |             |             |             |             |             |             |        |        |        |              |        |        |      |             |             |                |                          |

A = Available

**NOTE:** NEC reserves the right to alter the package plan based on the results of qualification. For current package availability, please contact your local NEC Design Center.

A1= Need advanced notice

E = Under Evaluation

<sup>\* =</sup> Heat spreader under evaluation

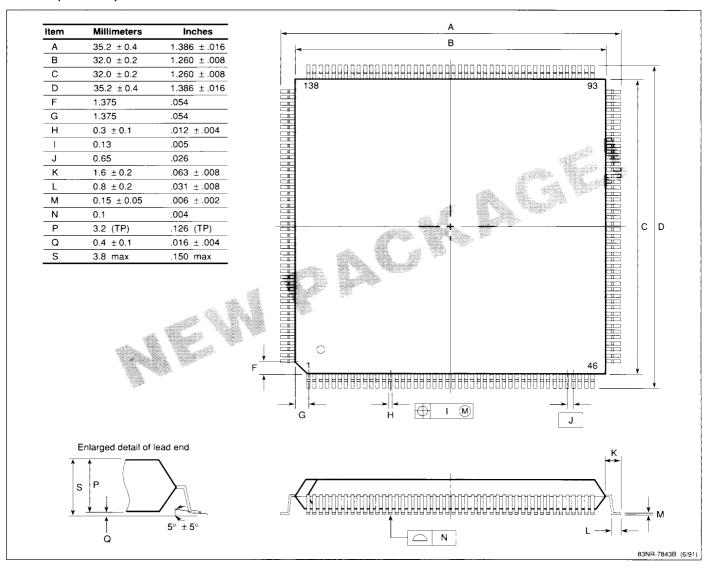

## 184-Pin (0.65 mm) Plastic QFP

The new 184-pin 0.65 mm QFP shown above is ideal for PC integrated chipsets. The package is available with a copper leadframe thereby allowing greater heat dissipation than standard 42 alloy leadframe packages. The 0.65 mm pin pitch allows the use of widely available, cost effective assembly equipment. It is currently available in two masterslices. The  $\mu PD65658$  with 25,344 usable gates and the  $\mu PD65664$  with 43,545 usable gates.

www.DataSheet4U.com

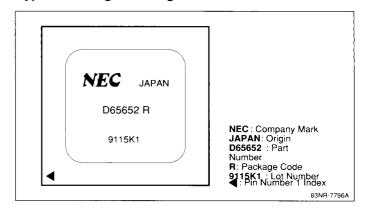

## Typical Package Marking

# **NEC's ASIC Design System**

CMOS-6/6A/6V gate arrays are fully supported by NEC's network of ASIC Design Centers, listed on the back of this data sheet.

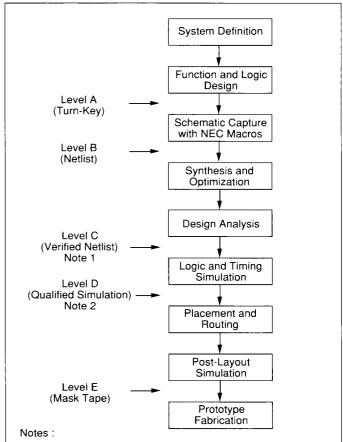

Design flow for CMOS-6/6A/6V gate arrays is shown in figure 4. Users can enlist Design Center support at any step in the design flow before actual manufacturing. Figure 4 shows the various levels at which Design Center support may begin — anywhere from level A through level E. Level C, "Verified Netlist," is the most popular interface.

NEC supports its ASIC products with a comprehensive CAD system that significantly reduces the time and expense usually associated with the development of semicustom devices. NEC's OpenCAD integration system supports tools for floorplanning, logic synthesis, automatic test generation, accelerated fault grading and full timing simulation, and advanced place-and-route algorithms. These advanced CAD tools ensure accurate designs.

Sample design kits are available at no charge to qualified users: contact an NEC ASIC Design Center for more information. (Software licensing required—NEC reserves the right to prioritize support based on user requirements.)

Figure 4. Gate Array Design Flow

- (1) NEC supports the most popular workstations, including Mentor Graphics, Valid, DAZIX®, FutureNet, Viewlogic®, and HP9000 workstations, for the NEC ASIC product line. However, NEC does not support all workstations for all products. Please contact your nearest NEC ASIC Design Center for more information.

- (2) NEC provides support of System HILO®, Verilog®, and MACH 1000/1500™ interface capability.

DAZIX is a registered trademark of DAZIX Daisy / Cadnetix Inc. Viewlogic is a registered trademark of Viewlogic Systems, Inc. System HILO is a registered trademark of GenRad. Verilog is a registered trademark of Cadence Design Systems, Inc. MACH 1000 and MACH 1500 are trademarks of Zycad Corp.

l<sub>oL</sub> (mA)

18.0

18.0

4.5

4.5

Cells

1 (6)

1 (6)

1 (5)

1 (5)

1 (5)

1 (5)

1 (6)

1 (8)

1 (8)

9.0

Description

Output buffer, CMOS 3-state out, 50 k $\Omega$  pull-up res. 4.5

B0WE Output buffer, CMOS 3-state out, 5  $k\Omega$  pull-up res. 4.5

Output buffer, CMOS 3-state out,

Output buffer, CMOS 3-state out,

Output buffer, CMOS 3-state out

Output buffer, CMOS 3-state out,

Output buffer, TTL 3-state out

50 kΩ pull-up res.

5 kΩ pull-up res.

50 k $\Omega$  pull-down res.

## **Block Library List**

The CMOS-6 families offer a variety of blocks, including gates, flip-flop circuits, and shift registers. The functions of these blocks are designed to be compatible with those of the CMOS-4 and CMOS-5 families.

In addition, such memory blocks as RAM and ROM and low-power gates are provided. The low-power block, in particular, was designed with low fan-out taken into consideration; the number of cells is less than that of the standard block, contributing to low power consumption and high efficiency.

|                      | .g., e., e., e., e.                                                                                                                                   |                         |                         | BTU8                 | Output buffer, TTL 3-state out, 50 k $\Omega$ pull-up res.                                                                                             | 9.0            | 1 (6           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|

| Bloc                 | k List                                                                                                                                                |                         |                         | BTW8                 | Output buffer, TTL 3-state out, 50 k $\Omega$ pull-up res.                                                                                             | 9.0            | 1 (6           |

| Block<br>Name        | Description                                                                                                                                           | I <sub>OL</sub><br>(mA) | Cells                   | BT09<br>BTU9<br>BTW9 | Output buffer, TTL 3-state out Output buffer, TTL 3-state out, 50 k $\Omega$ pull-up res.                                                              | 18.0<br>18.0   | 2 (12<br>2 (12 |

|                      | Interface Blocks                                                                                                                                      |                         |                         | EXT1                 | Output buffer, N-ch open drain                                                                                                                         | 9.0            | 1 (2           |

| Inputs               |                                                                                                                                                       |                         | . (2)                   |                      | Output buffer, N-ch open drain, 50 k $\Omega$ pull-up res Output buffer, N-ch open drain, 5 k $\Omega$ pull-up res.                                    | 9.0            | ٠,             |

| FI01<br>FID1         | Input buffer, CMOS in Input buffer, CMOS in, 50 kΩ pull-down res.                                                                                     | -                       | 1 (3)<br>1 (3)          | EXT2                 | Output buffer, P-ch open drain                                                                                                                         | *9.0           |                |

| FIU1<br>FIW1         | Input buffer, CMOS in, 50 k $\Omega$ pull-up res. Input buffer, CMOS in, 50 k $\Omega$ pull-up res.                                                   | -                       | 1 (3)                   | EXT4<br>EXT5<br>EXT7 | Output buffer, P-ch open drain, 50 k $\Omega$ pull-up res. Output buffer, N-ch open drain<br>Output buffer, N-ch open drain, 50 k $\Omega$ pull-up res | 18.0           | 1 (2           |

| FI02                 | Input buffer, TTL in                                                                                                                                  | -                       | 1 (3)                   | EXW7                 | Output buffer, N-ch open drain, 5 k $\Omega$ pull-up res.                                                                                              | 18.0           | 1 (2           |

| FID2<br>FIU2<br>FIW2 | Input buffer, TTL in, 50 k $\Omega$ pull-down res. Input buffer, TTL in, 50 k $\Omega$ pull-up res. Input buffer, TTL in, 5 k $\Omega$ pull-up res.   | -<br>-<br>•             | 1 (3)<br>1 (3)<br>1 (3) | EXT6<br>EXT8         | Output buffer, P-ch open drain, 50 k $\Omega$ pull-up res. Output buffer, P-ch open drain, 50 k $\Omega$ pull-down res.                                | *18.0<br>*18.0 | •              |

| FIB1<br>FIB2         | Input buffer, CMOS in, high fanout for clock driver Input buffer, TTL in, high fanout for clock driver                                                | -                       | 1 (24)<br>1 (24)        | EXT9<br>EXTB         | Output buffer, N-ch open drain Output buffer, N-ch open drain, 50 k $\Omega$ pull-up res                                                               | 13.5<br>13.5   |                |

| FDS1<br>FIS1         | Input buffer, CMOS Schmitt in, 50 k $\Omega$ pull-down re Input buffer, CMOS Schmitt in                                                               | ·S                      | 1 (6)<br>1 (6)          |                      | Output buffer, N-ch open drain, 5 k $\Omega$ pull-up res.                                                                                              | 13.5           | 1 (2           |

| FUS1                 | Input buffer, CMOS Schmitt in, 50 kΩ pull-up res.                                                                                                     | _                       | 1 (6)                   | * India              | cates I <sub>OH</sub>                                                                                                                                  |                |                |

| FWS1                 | Input buffer, CMOS Schmitt in, 5 k $\Omega$ pull-up res.                                                                                              | -                       | 1 (6)                   | I/O But              | ffers                                                                                                                                                  |                |                |

| FDS2<br>FIS2         | Input buffer, TTL Schmitt in, 50 k $\Omega$ pull-down res. Input buffer, TTL Schmitt in                                                               | -                       | 1 (6)<br>1 (6)          | B001<br>B0D1         | I/O buffer, CMOS in, CMOS 3-state out I/O buffer, CMOS in, CMOS 3-state out,                                                                           | 13.5<br>13.5   | ,              |

| FUS2<br>FWS2         | Input buffer, TTL Schmitt in, 50 k $\Omega$ pull-up res. Input buffer, TTL Schmitt in, 5 k $\Omega$ pull-up res.                                      | -                       | 1 (6)<br>1 (6)          | B0U1                 | 50 k $\Omega$ pull-down res. I/O buffer, CMOS in, CMOS 3-state out,                                                                                    | 13.5           |                |

| Output               | ds.                                                                                                                                                   |                         |                         | DOM/1                | 50 kΩ pull-up res. I/O buffer, CMOS in, CMOS 3-state out,                                                                                              | 13.5           | 1 (9           |

| FO01                 | Output buffer, CMOS out                                                                                                                               | 9.0                     | 1 (2)                   | B0W1                 | 5 k $\Omega$ pull-up res.                                                                                                                              | 13.5           | 1 (8           |

| FO02<br>FO03         | Output buffer, CMOS out<br>Output buffer, CMOS out                                                                                                    | 13.5<br>18.0<br>4.5     | 1 (4)<br>1 (4)<br>1 (2) | B002<br>B0D2         | I/O buffer, TTL in, CMOS 3-state out I/O buffer, TTL in, CMOS 3-state out,                                                                             | 13.5<br>13.5   | ,              |

| FO04                 | Output buffer, CMOS out                                                                                                                               |                         | 1 (4)                   | BOL IO               | 50 kΩ pull-down res.                                                                                                                                   | 10 E           | 1 /0           |

| FT01<br>FT02         | Output buffer, TTL out Output buffer, TTL out                                                                                                         | 9.0<br>18.0             | 2 (6)                   | 6002                 | I/O buffer, TTL in, CMOS 3-state out, 50 k $\Omega$ pull-up res.                                                                                       | 13.5           | 1 (9           |

| B007<br>B0D7         | Output buffer, CMOS 3-state out<br>Output buffer, CMOS 3-state out,                                                                                   | 13.5<br>13.5            | 1 (6)<br>1 (6)          | B0W2                 | I/O buffer, TTL in, CMOS 3-state out, 5 k $\Omega$ pull-up res.                                                                                        | 13.5           | 1 (9           |

|                      | 50 kΩ pull-down res.                                                                                                                                  | _                       |                         | B003                 | I/O buffer, CMOS in, CMOS 3-state out                                                                                                                  | 9.0            | ,              |

| B0U7                 | Output buffer, CMOS 3-state out, 50 kΩ pull-up res.                                                                                                   | 13.5                    | 1 (6)                   | B0D3                 | I/O buffer, CMOS in, CMOS 3-state out, 50 kΩ pull-down res.                                                                                            | 9.0            | `              |

| B0W7<br>B008         | Output buffer, CMOS 3-state out, 5 k $\Omega$ pull-up res<br>Output buffer, CMOS 3-state out                                                          | 9.0                     | 1 (6)<br>1 (5)          | B0U3                 | I/O buffer, CMOS in, CMOS 3-state out, 50 k $\Omega$ pull-up res.                                                                                      | 9.0            | 1 (8           |

| B0D8                 | Output buffer, CMOS 3-state out, $\Omega = 0.000$ Output buffer, CMOS 3-state out, $\Omega = 0.000$ Output buffer, CMOS 3-state out, $\Omega = 0.000$ | 9.0                     | 1 (5)                   | B0W3                 | 1/O buffer, CMOS in, CMOS 3-state out, $5 \text{ k}\Omega$ pull-up res.                                                                                | 9.0            | 1 (8           |

| B0U8<br>B0W8         | Output buffer, CMOS 3-state out, 50 k $\Omega$ pull-up re Output buffer, CMOS 3-state out, 5 k $\Omega$ pull-up res                                   |                         | 1 (5)<br>1 (5)          | B004<br>B0D4         | I/O buffer, TTL in, CMOS 3-state out I/O buffer, TTL in, CMOS 3-state out,                                                                             | 9.0<br>9.0     | ,              |

18.0

18.0

1 (6)

1 (6)

B0U4

50 k $\Omega$  pull-down res.

50 kΩ pull-up res.

I/O buffer, TTL in, CMOS 3-state out,

B0W4 I/O buffer, TTL in, CMOS out, 5 k $\Omega$  pull-up res.

**Block**

Name

B00E

**BODE**

B0UE

Outputs (Cont.)

Note: Number of internal cells required is shown in parentheses.

Output buffer, CMOS 3-state out

Output buffer, CMOS 3-state out,

50 k $\Omega$  pull-down res.

B009

B0D9

| Block<br>Name | Description                                                                                         | (mA)       | Cells           | Block<br>Name | Description                                                                         | I <sub>OL</sub><br>(mA) | Cells          |

|---------------|-----------------------------------------------------------------------------------------------------|------------|-----------------|---------------|-------------------------------------------------------------------------------------|-------------------------|----------------|

|               | Interface Blocks (Cont.)                                                                            |            |                 |               | Interface Blocks (Cont.)                                                            |                         |                |

| /O Buf        | fers (Cont.)                                                                                        |            |                 | I/O Buf       | fers (Cont.)                                                                        |                         |                |

| B005          | I/O buffer, CMOS in, CMOS 3-state out                                                               | 18.0       | 1 (9)           | BSD4          | I/O buffer, TTL Schmitt in, CMOS 3-state out,                                       | 9.0                     | 1 (11)         |

| B0D5          | I/O buffer, CMOS in, CMOS 3-state out, 50 kΩ pull-down res.                                         | 18.0       | 1 (9)           | BSI4          | 50 k $\Omega$ pull-down res. I/O buffer, TTL Schmitt in, CMOS 3-state out           | 9.0                     | 1 (11)         |

| B0U5          | I/O buffer, CMOS in, CMOS 3-state out, 50 kΩ pull-up res.                                           | 18.0       | 1 (9)           | BSU4          | I/O buffer, TTL Schmitt in, CMOS 3-state out, 50 k $\Omega$ pull-up res.            |                         | 1 (11)         |

| B0W5          | I/O buffer, CMOS in, CMOS 3-state out, 5 k $\Omega$ pull-up res.                                    | 18.0       | 1 (9)           | BSW4          | I/O buffer, TTL Schmitt in, CMOS 3-state out, 5 k $\Omega$ pull-up res.             | 9.0                     | 1 (11)         |

| B006          | I/O buffer, TTL in, CMOS 3-state out                                                                | 18.0       | 1 (9)           | BSD5          |                                                                                     | 18.0                    | 1 (12)         |

| 30D6          | I/O buffer, TTL in, CMOS 3-state out, 50 k $\Omega$ pull-down res.                                  | 18.0       | 1 (9)           | BSI5          | 50 k $\Omega$ pull-down res. I/O buffer, CMOS Schmitt in, CMOS 3-state out          | 18.0                    | 1 (12)         |

| B0U6          | I/O buffer, TTL in, CMOS 3-state out,                                                               | 18.0       | 1 (9)           | BSU5          |                                                                                     | 18.0                    | 1 (12)         |

| B0 <b>W</b> 6 | 50 k $\Omega$ pull-up res. I/O buffer, TTL in, CMOS 3-state out, 5 k $\Omega$ pull-up res.          | 18.0       | 1 (9)           | BSW5          | $1/O$ buffer, CMOS Schmitt in, CMOS 3-state out, $5 \text{ k}\Omega$ pull-up res.   | 18.0                    | 1 (12)         |

| B00A          | I/O buffer, TTL in, TTL 3-state out I/O buffer, TTL in, TTL 3-state out,                            | 9.0<br>9.0 | 1 (9)<br>1 (9)  | BSD6          | I/O buffer, TTL Schmitt in, CMOS 3-state out, 50 k $\Omega$ pull-down res.          | 18.0                    | 1 (12)         |

|               | 50 kΩ pull-up res.                                                                                  |            | , ,             | BSI6          | I/O buffer, TTL Schmitt in, CMOS 3-state out                                        |                         | 1 (12)         |

| B0WA<br>B00B  | I/O buffer, TTL in, TTL 3-state out, 5 k $\Omega$ pull-up re I/O buffer, TTL in, TTL 3-state out    |            | 1 (9)<br>2 (15) | BSU6          | I/O buffer, TTL Schmitt in, CMOS 3-state out, 50 k $\Omega$ pull-up res.            | 16.0                    | 1 (12)         |

|               | I/O buffer, TTL in, TTL 3-state out, 50 kΩ pull-up res.                                             | 18.0       | • /             | BSW6          | I/O buffer, TTL Schmitt in, CMOS 3-state out, 5 k $\Omega$ pull-up res.             | 18.0                    | 1 (12)         |

|               | I/O buffer, TTL in, TTL 3-state out, 5 k $\Omega$ pull-up re                                        |            |                 | BSIA          | I/O buffer, TTL Schmitt in, TTL 3-state out                                         |                         | 1 (12)         |

| B00C<br>B0DC  | I/O buffer, CMOS in, CMOS 3-state out I/O buffer, CMOS in, CMOS 3-state out,                        | 4.5<br>4.5 | 1(8)<br>1(8)    | BSUA          | I/O buffer, TTL Schmitt in, TTL 3-state out, 50 k $\Omega$ pull-up res.             | 9.0                     | 1 (12)         |

| 0000          | 50 k $\Omega$ pull-down res.                                                                        |            | . (-)           | BSWA          | I/O buffer, TTL Schmitt in, TTL 3-state out, 5 kΩ pull-up res.                      | 9.0                     | 1 (12)         |

| B0UC          | I/O buffer, CMOS in, CMOS 3-state out,                                                              | 4.5        | 1 (8)           | BSIB          | I/O buffer, TTL Schmitt in, TTL 3-state out                                         | 18.0                    | 2 (18)         |

| B0WC          | 50 k $\Omega$ pull-up res. I/O buffer, CMOS in, CMOS 3-state out, 5 k $\Omega$ pull-up res.         | 4.5        | 1 (8)           | BSUB          | I/O buffer, TTL Schmitt in, TTL 3-state out, 50 k $\Omega$ pull-up res.             | 18.0                    | 2 (18)         |

| B00D<br>B0DD  | I/O buffer, TTL in, CMOS 3-state out I/O buffer, TTL in, CMOS 3-state out,                          | 4.5<br>4.5 | 1 (8)<br>1 (8)  | BSWB          | I/O buffer, TTL Schmitt in, TTL 3-state out, 5 k $\Omega$ pull-up res.              | 18.0                    | 2 (18)         |

|               | 50 k $\Omega$ pull-down res.                                                                        |            |                 | BSDC          | I/O buffer, CMOS Schmitt in, CMOS 3-state out,                                      | 4.5                     | 1 (11)         |

|               | I/O buffer, TTL in, CMOS 3-state out, 50 k $\Omega$ pull-up res.                                    | 4.5        | 1 (8)           | BSIC          | 50 k $\Omega$ pull-down res. I/O buffer, CMOS Schmitt in, CMOS 3-state out          | 4.5                     | 1 (11)         |

| B0WD          | I/O buffer, TTL in, CMOS 3-state out, 5 kΩ pull-up res.                                             | 4.5        | 1 (8)           | BSUC          | I/O buffer, CMOS Schmitt in, CMOS 3-state out,                                      | 4.5                     | 1 (11)         |

| BSD1          | $1/O$ buffer, CMOS Schmitt in, CMOS 3-state out, $50 \text{ k}\Omega$ pull-down res.                |            | 1 (12)          | BSWC          | 50 kΩ pull-up res. I/O buffer, CMOS Schmitt in, CMOS 3-state out, 5 kΩ pull-up res. | 4.5                     | 1 (11)         |

| BSI1          | I/O buffer, CMOS Schmitt in, CMOS 3-state out                                                       |            | 1 (12)          | BSDD          | I/O buffer, TTL Schmitt in, CMOS 3-state out,                                       | 4.5                     | 1 (11)         |

| BSU1          | I/O buffer, CMOS Schmitt in, CMOS 3-state out, 50 k $\Omega$ pull-up res.                           | 13.5       | 1 (12)          | BSID          | 50 k $\Omega$ pull-down res. I/O buffer, TTL Schmitt in, CMOS 3-state out           | 45                      | 1 (11)         |

| BSW1          | I/O buffer, CMOS Schmitt in, CMOS 3-state out,                                                      | 13.5       | 1 (12)          | BSUD          | I/O buffer, TTL Schmitt in, CMOS 3-state out,                                       |                         | 1 (11)         |

| BSD2          | 5 kΩ pull-up res. I/O buffer, TTL Schmitt in, CMOS 3-state out, 50 kΩ pull-down res.                | 13.5       | 1 (12)          |               | 50 k $\Omega$ pull-up res. I/O buffer, TTL Schmitt in, CMOS 3-state out,            |                         | 1 (11)         |

| BSI2          | I/O buffer, TTL Schmitt in, CMOS 3-state out                                                        | 13.5       | 1 (12)          |               | 5 k $\Omega$ pull-up res.                                                           |                         |                |

| BSU2          | I/O buffer, TTL Schmitt in, CMOS 3-state out,                                                       | 13.5       | 1 (12)          | Slew F        | Rate Output Buffers                                                                 |                         |                |

| BSW2          | 50 kΩ pull-up res.  I/O buffer, TTL Schmitt in, CMOS 3-state out,                                   | 13.5       | 1 (12)          | FE03<br>BE09  | 18 mA CMOS level slew rate output buffer 18 mA CMOS 3-state slew rate output buffer |                         | 1 (4)<br>1 (5) |

| BSD3          | 5 kΩ pull-up res. I/O buffer, CMOS Schmitt in, CMOS 3-state out, 50 kΩ pull-down res.               | 9.0        | 1 (11)          | BED9          | 18 mA CMOS 3-state slew rate output buffer with 50K pull-down res.                  |                         | 1 (5)          |

| BSI3          | I/O buffer, CMOS Schmitt in, CMOS 3-state out                                                       | 9.0        | 1 (11)          | BEU9          | 18 mA CMOS 3-state slew rate output buffer with 50K pull-up res.                    |                         | 1 (5           |

| BSU3          | I/O buffer, CMOS Schmitt in, CMOS 3-state out,                                                      | 9.0        | 1 (11)          | BEW9          | 18 mA CMOS 3-state slew rate output buffer                                          |                         | 1 (5           |

| BSW3          | 50 k $\Omega$ pull-up res. I/O buffer, CMOS Schmitt in, CMOS 3-state out, 5 k $\Omega$ pull-up res. | 9.0        | 1 (11)          | BE05          | with 5K pull-up res. 18 mA I/O slew rate buffer (CMOS in / CMOS out)                |                         | 1 (8           |

|               | Number of internal cells required is shown in parer                                                 |            |                 | BED5          | 18 mA I/O slew rate buffer (CMOS in / CMOS out) with 50K pull-down res.             |                         | 1 (8           |

| Block<br>Name | Description                                                                                                           | Cells            | Block<br>Name        | Description                                                                                          | Cells       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|------------------|----------------------|------------------------------------------------------------------------------------------------------|-------------|

|               | Interface Blocks (Cont.)                                                                                              | _                |                      | Function Blocks - Normal Power                                                                       | <u></u>     |

| Slew F        | late Output Buffers (Cont.)                                                                                           |                  | Invert               | ers                                                                                                  |             |

|               | 18 mA I/O slew rate buffer (CMOS in / CMOS out) with 50K pull-up res.                                                 | 1 (8)            | F101<br>F102         | Inverter $(F/O = 17)$<br>Inverter $(F/O = 37)$                                                       | 1 2         |

| BEW5          | 18 mA I/O slew rate buffer (CMOS in / CMOS out) with 5K pull-up res.                                                  | 1 (8)            | F103<br>F104         | Inverter $(F/O = 60)$<br>Inverter $(F/O = 92)$                                                       | 3<br>4      |

| BE06<br>BED6  | 18 mA I/O slew rate buffer (TTL in / CMOS out) 18 mA I/O slew rate buffer (TTL in / CMOS out) with 50K pull-down res. | 1 (8)<br>1 (8)   | F108 <b>Buffer</b>   | Inverter (F/O = 160) s                                                                               | 12          |

| BEU6          | 18 mA I/O slew rate buffer (TTL in / CMOS out) with 50K pull-up res.                                                  | 1 (8)            | F111<br>F112         | Non-inverting buffer (F/O = 17)<br>Non-inverting buffer (F/O = 35)                                   | 2<br>3      |

| BEW6          | 18 mA I/O slew rate buffer (TTL in / CMOS out) with 5K pull-up res.                                                   | 1 (8)            | F113<br>F114         | Non-inverting buffer (F/O = 54)<br>Non-inverting buffer (F/O = 74)                                   | 4<br>5      |

| BFI5          | 18 mA Schmitt I/O slew rate buffer (CMOS in / CMOS out)                                                               | 1 (11)           | F118                 | Non-inverting buffer (F/O = 180)                                                                     | 11          |

| BFD5          | 18 mA Schmitt I/O slew rate buffer (CMOS in / CMOS out) with 50K pull-down res.                                       | 1 (11)           | NOR (                | Gates 2-input NOR                                                                                    | 2           |

| BFU5          | 18 mA Schmitt I/O slew rate buffer (CMOS in / CMOS out) with 50K pull-up res.                                         | 1 (11)           | F203<br>F204         | 3-input NOR<br>4-input NOR                                                                           | 3           |

|               | 18 mA Schmitt I/O slew rate buffer (CMOS in / CMOS out) with 5K pull-up res.                                          | 1 (11)           | F208<br>F222         | 8-input NOR<br>2-input NOR, power                                                                    | 7<br>4      |

| BFI6          | 18 mA Schmitt I/O slew rate buffer<br>(TTL in / CMOS out)                                                             | 1 (11)           | F223<br>F224         | 3-input NOR, power<br>4-input NOR, power                                                             | 6<br>8      |

| BFD6          | 18 mA Schmitt I/O slew rate buffer (TTL in / CMOS out) with 50K pull-down res.                                        | 1 (11)           | OR Ga                | ,                                                                                                    | ·           |

| BFU6<br>BFW6  | 18 mA Schmitt I/O slew rate buffer (TTL in / CMOS out) with 50K pull-up res. 18 mA Schmitt I/O slew rate buffer       | 1 (11)           | F212<br>F213<br>F214 | 2-input OR<br>3-input OR<br>4-input OR                                                               | 2<br>3<br>3 |

| Specia        | (TTL in / CMOS out) with 5K pull-up res.                                                                              |                  | F232<br>F233         | 2-input OR, power<br>3-input OR, power                                                               | 3<br>4      |

| FIB1<br>FIB2  | Input buffer, CMOS in, high fanout for clock driver Input buffer, TTL in, high fanout for clock driver                | 1 (24)<br>1 (24) | F234                 | 4-input OR, power  Gates                                                                             | 4           |

| OSF1<br>OSF2  | Feedback resistance for oscillator (low freq.) Feedback resistance for oscillator (high freq.)                        | 1<br>1           | F302                 | 2-input NAND                                                                                         | 2           |

| OSF3          | Feedback resistance for oscillator with Enable (low freq.)                                                            | 1                | F303<br>F304         | 3-input NAND<br>4-input NAND                                                                         | 3<br>4      |

| OSF4          | Feedback resistance for oscillator with Enable (high freq.)                                                           | 1                | F305<br>F306         | 5-input NAND<br>6-input NAND                                                                         | 5<br>5      |

| OSI1<br>OSI2  | Oscillator input buffer Oscillator input buffer with Enable                                                           | 1                | F308<br>F322         | 8-input NAND<br>2-input NAND, power                                                                  | 6<br>4      |

| OSO2          | Oscillator output buffer with feedback res. (low freq.) Oscillator output buffer with feedback res. (high freq.)      | 1                | F323<br>F324         | 3-input NAND, power<br>4-input NAND, power                                                           | 6<br>8      |

| OSO4          | Oscillator output buffer (low freq.) Oscillator output buffer (high freq.)                                            | 1<br>1           | AND C                | Gates                                                                                                |             |

| OSO7          | Oscillator output buffer with feedback res. & Enable (low freq.)                                                      | 1                | F312<br>F313         | 2-input AND<br>3-input AND                                                                           | 2           |

| OSO8          | Oscillator output buffer with feedback res. & Enable (high freq.)                                                     | 1                | F314<br>F332         | 4-input AND<br>2-input AND, power                                                                    | 3           |

| SHT1          | Monostable multivibrator                                                                                              | 1                | F333<br>F334         | 3-input AND, power<br>4-input AND, power                                                             | 4           |

|               | Oscillator pins must be used in combination. Some validations are:                                                    | d                |                      | IOR Gates                                                                                            |             |

| 0             | SI1 + OSO1 Low Frequency<br>SI1 + OSO3 + OSF1 Low Frequency                                                           |                  | F421<br>F422         | 2-wide 1-2-input AND-OR inverter<br>3-wide 1-1-2-input AND-OR inverter                               | 3<br>4      |

|               | SI1 + OSO2 High Frequency SI2 + OSO7 Low Frequency with oscillator Ena                                                | able             | F423<br>F424         | 2-wide 1-3-input AND-OR inverter<br>2-wide 2-2-input AND-OR inverter                                 | 4           |

| 0             | SI2 + OSO3 + OSF3 Low Frequency with oscillator Ena<br>SI2 + OSO8 High Frequency with oscillator Ena                  | able<br>able     | F424<br>F425<br>F426 | 3-wide 2-2-2-input AND-OR inverter 2-wide 3-3-input AND-OR inverter 2-wide 3-3-input AND-OR inverter | 6<br>6      |

| 10            | SI2 + OSO4 + OSF4 High Frequency with oscilator Ena                                                                   | able             | F429                 | 4-wide 2-2-2-input AND-OR inverter                                                                   | 8           |

| Block<br>Name                | Description                                                                                                                                    | Cells                   | Block<br>Name                | Description (                                                                                                                                             | Cells                |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                              | Function Blocks - Normal Power (Cont.)                                                                                                         |                         |                              | Function Blocks - Normal Power (Cont.)                                                                                                                    |                      |

| OR-NA                        | AND Gates                                                                                                                                      |                         | Flip-Fle                     | ops                                                                                                                                                       |                      |

| F431<br>F432<br>F433<br>F434 | 2-wide 1-2-input OR-AND inverter<br>3-wide 1-1-2-input OR-AND inverter<br>2-wide 1-3-input OR-AND inverter<br>2-wide 2-2-input OR-AND inverter | 3<br>4<br>4<br>4        | F596<br>F611<br>F614<br>F617 | Synchronous R-S F/F with Set-Reset<br>D-F/F<br>D-F/F with Set-Reset<br>D-F/F with Set-Reset low                                                           | 11<br>8<br>10<br>10  |

| F435<br>F436<br>F454         | 2-wide 2-3-input OR-AND inverter<br>2-wide 3-3-input OR-AND inverter<br>4-wide 2-2-2-2-input OR-AND inverter                                   | 5<br>6<br>8             | F631<br>F637<br>F641<br>F647 | D-F/F C low D-F/F C low with Set-Reset low D-F/F, buffered D-F/F with Set-Reset low, buffered                                                             | 8<br>10<br>8<br>10   |

| Clock                        | Drivers                                                                                                                                        |                         | F661                         | D-F/F C low, buffered                                                                                                                                     | 8                    |

| F501<br>F502<br>FCK1         | Clock driver Dual clock driver Clock driver (F/O = 360)                                                                                        | 0<br>0<br>40            | F667<br>F714<br>F717         | D-F/F C low with Set-Reset low, buffered Toggle F/F with Set-Reset Toggle F/F with Set-Reset low                                                          | 10<br>9<br>9         |

| FCK3                         | Clock driver (F/O = 720)  Clock driver (F/O = 1080)  Clock driver (F/O = 1440)  Clock driver (F/O = 1800)                                      | 80<br>120<br>160<br>200 | F737<br>F744<br>F747<br>F767 | Toggle low F/F with Set-Reset low Toggle F/F with Set-Reset, buffered Toggle F/F with Set-Reset low, buffered Toggle low F/F with Set-Reset low, buffered | 9<br>9<br>9          |

| <b>EX-OR</b><br>F511         | R Gate<br>Exclusive-OR                                                                                                                         | 4                       | F771<br>F774<br>F777<br>F781 | J-K F/F, buffered J-K F/F with Set-Reset, buffered J-K F/F with Set-Reset low, buffered J-K F/F C low, buffered                                           | 10<br>12<br>12<br>10 |

| EX-NO                        | DR Gate                                                                                                                                        |                         | F787                         | J-K F/F C low with Set-Reset low, buffered                                                                                                                | 12                   |

| F512                         | Exclusive-NOR                                                                                                                                  | 4                       | F791<br>F792<br>F922         | Toggle F/F with Set-Reset and Tog. Enable Toggle low F/F with Set-Reset and Tog. Enable low 4-bit D-F/F with Reset                                        | 12<br>12<br>33       |

| F521                         | 1-bit full-adder                                                                                                                               | 9                       | F924                         | 4-bit D-F/F                                                                                                                                               | 28                   |

| F523                         | 4-bit binary full-adder                                                                                                                        | 32                      | Count                        | ers                                                                                                                                                       |                      |

| Buffer                       | s                                                                                                                                              |                         | F961<br>F962                 | 4-bit synchronous binary counter with Reset low, buffered 4-bit synchronous binary up counter with Reset low                                              | 52<br>38             |

| F531<br>F532                 | 3-state buffer with Enable<br>3-state buffer with Enable low                                                                                   | 5<br>5                  |                              | , , ,                                                                                                                                                     | 30                   |

| Decod                        |                                                                                                                                                | · ·                     | Compa<br>F985                | 4-bit magnitude comparator                                                                                                                                | 32                   |

| F561                         | 2-to-4 decoder                                                                                                                                 | 10                      |                              | , bit magnitude comparate.                                                                                                                                | -                    |

| F981<br>F982                 | 2-to-4 decoder with Enable low<br>3-to-8 decoder with Enable low                                                                               | 13<br>26                | Scan<br>S000<br>S002         | Scan path D-F/F with Set-Reset Scan path D-F/F                                                                                                            | 11<br>9              |

|                              | Registers                                                                                                                                      | 0.0                     | S050<br>S052                 | Scan path D-F/F with Set-Reset, Hold<br>Scan path D-F/F with Hold                                                                                         | 14<br>12             |

| F911<br>F912<br>F913<br>F914 | 4-bit shift register with Reset 4-bit serial/parallel shift register 4-bit parallel shift register with Reset low, Load 4-bit shift register   | 33<br>35<br>39<br>28    | S100<br>S102<br>S150<br>S152 | Scan path J-K F/F with Set-Reset<br>Scan path J-K F/F<br>Scan path J-K F/F with Set-Reset, Hold<br>Scan path J-K F/F with Hold                            | 14<br>12<br>17<br>15 |

|                              | elexers                                                                                                                                        |                         | S201                         | Scan path D-latch with Reset                                                                                                                              | 12                   |

| F569<br>F570<br>F571<br>F572 | 8-to-1 multiplexer<br>4-to-1 multiplexer<br>2-to-1 multiplexer<br>Quad 2-to-1 multiplexer                                                      | 18<br>10<br>6<br>14     | S202<br>S301<br>S302<br>S999 | Scan path D-latch Scan path D-latch with Reset (ATG) Scan path D-latch (ATG) Scan path 2-to-1 data selector                                               | 11<br>8<br>7<br>4    |

| Latche                       | es                                                                                                                                             |                         | Delays                       | s                                                                                                                                                         |                      |

| F595<br>F601<br>F602<br>F603 | R-S latch D-latch D-latch with Reset D-latch with Reset low                                                                                    | 5<br>6<br>6<br>7        | F130<br>F131<br>F132         | Delay block (for monostable multivibrator) Delay gate Delay gate                                                                                          | 8<br>6<br>1          |

| F604<br>F605<br>F901         | D-latch with G driver low D-latch with G low, Reset low 4-bit D-latch                                                                          | 6<br>7<br>20            |                              |                                                                                                                                                           |                      |

# **CMOS-6/6A/6V/6X**

| Block<br>Name | Description                                      | Cells    | Block<br>Name | Description                                                            | Cells  |

|---------------|--------------------------------------------------|----------|---------------|------------------------------------------------------------------------|--------|

|               | Function Blocks - Low Power                      |          |               | Function Blocks - Low Power                                            |        |

| Multip        | lexer                                            |          | OP-NA         | ND Gates                                                               |        |

| L572          | Quad 2-to-1 multiplexer                          | 10       |               |                                                                        |        |

|               |                                                  |          | L431<br>L432  | 2-wide 1-2-input OR-AND inverter<br>3-wide 1-1-2-input OR-AND inverter | 2<br>2 |

| Latche        | es ·                                             |          | L433          | 2-wide 1-3-input OR-AND inverter                                       | 2      |

| L601          | D-latch                                          | 3        | L434          | 2-wide 2-2-input OR-AND inverter                                       | 2      |

| L602          | D-latch with Reset                               | 4        |               |                                                                        |        |

| L603<br>L604  | D-latch with Reset low D-latch with G low driver | 4        | L435          | 2-wide 2-3-input OR-AND inverter                                       | 3      |

|               |                                                  |          | L436          | 2-wide 3-3-input OR-AND inverter                                       | 3      |

| L605          | D-latch with G low, R low                        | 4        | L454          | 4-wide 2-2-2-input OR-AND inverter                                     | 4      |

| L901<br>L902  | 4-bit latch<br>8-bit latch                       | 10<br>18 |               |                                                                        |        |

| L902          | o-bit lateri                                     | 10       | EX-OR         | Gate                                                                   |        |

| Inverte       | er                                               |          | L511          | EX-OR                                                                  | 3      |

| L101          | Inverter                                         | 1        | EX-NO         |                                                                        |        |

| Buffer        |                                                  |          | L512          | EX-NOR                                                                 | 3      |

| L111          | Non-inverting buffer                             | 1        | 1 Decoders    |                                                                        |        |

| NOR G         | ates                                             |          | L561          | 2-to-4 decoder                                                         | 6      |

|               |                                                  | 4        | L981          | 2-to-4 decoder with Enable low                                         | 8      |

| L202<br>L203  | 2-input NOR 3-input NOR                          | 1<br>2   | L982          | 3-to-8 decoder with Enable low                                         | 17     |

| L203          | 4-input NOR                                      | 2        | Flip Flo      | ops                                                                    |        |

| OR Gates      |                                                  |          | L611 D-F/F    |                                                                        | 5      |

|               |                                                  | _        | L614          | D-F/F with Set-Reset                                                   | 7      |

| L212          | 2-input OR                                       | 2        | L617          | D-F/F with Set-Reset low                                               | 7      |

| L213<br>L214  | 3-input OR<br>4-input OR                         | 2<br>3   | L631          | D-F/F with C low                                                       | 5      |

|               | - input of t                                     | J        | L637          | D-F/F with R low, S low, C low                                         | 7      |

| NAND          | Gates                                            |          | L714          | Toggle-F/F with Set-Reset                                              | 7      |

| L302          | 2-input NAND                                     | 1        | L717<br>L737  | Toggle-F/F with Set-Reset low Toggle low F/F with Set-Reset low        | 7<br>7 |

| L303          | 3-input NAND                                     | 2        |               |                                                                        |        |

| L304          | 4-input NAND                                     | 2        | L922          | 4-bit D-F/F with Reset                                                 | 23     |