# **Preliminary User's Manual**

# V850/DB1<sup>TM</sup> AVALON

32-/16-bit Single-Chip Microcontroller

**Hardware**

μPD70F3080 μPD703081

## NOTES FOR CMOS DEVICES

## (1) PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

## (3) STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

# MS-DOS and MS-Windows are either registered trademarks or trademarks of Microsoft Corporation in the United States and/or other countries. PC/AT and PC DOS are trademarks of IBM Corp.

The related documents in this publication may include preliminary versions. However, preliminary versions are not marked as such.

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by th customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

The information in this document is current as of 29.10.2002. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information. No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information. While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and antifailure features. NEC semiconductor products are classified into the following three quality grades: "Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular

"Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, antidisaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

"Specific": Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc.

If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.

**Notes:** (1) "NEC" as used in this statement means NEC Corporation and also includes its majority-owned subsidiaries.

(2) "NEC semiconductor products" means any semiconductor product developed or manufactured by or for NEC (as defined above).

M5 2000 03

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

## NEC Electronics (Europe) GmbH

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

## Sucursal en España

Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

#### Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

## Filiale Italiana

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

## Branch The Netherlands

Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

#### **Branch Sweden**

Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

# **United Kingdom Branch**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

## NEC Electronics Singapore Pte. Ltd.

Singapore

Tel: 65-6253-8311 Fax: 65-6250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos, Brasil

Tel: 55-11-6465-6810 Fax: 55-11-6465-6829

## **Preface**

**Readers** This manual is intented for users who want to understand the functions of the

V850/DB1 (nickname Avalon).

**Purpose** This manual presents the hardware manual of V850/DB1.

**Organization** This system specification describes the following sections:

Pin function

CPU function

Internal peripheral function

Flash memory

**Legend** Symbols and notation are used as follows:

Weight in data notation: Left is high-order column, right is low order column

Active low notation :  $\overline{xxx}$  (pin or signal name is over-scored) or

/xxx (slash before signal name)

Memory map address: : High order at high stage and low order at low stage

Note : Explanation of (Note) in the text

Caution : Item deserving extra attention

**Remark** : Supplementary explanation to the text

Numeric notation : Binary . . . xxxx or xxxB

$\textbf{Decimal} \dots \textbf{x} \textbf{x} \textbf{x} \textbf{x}$

Hexadecimal . . . xxxxH or 0x xxxx

Prefixes representing powers of 2 (address space, memory capacity)

$K \text{ (kilo)} : 2^{10} = 1024$

M (mega) :  $2^{20} = 1024^2 = 1,048,576$ G (giga) :  $2^{30} = 1024^3 = 1,073,741,824$

# **Table of Contents**

|        |     | Preta   | ce                                                   | . 5 |

|--------|-----|---------|------------------------------------------------------|-----|

| Chapte | r 1 | Introd  | luction                                              | 21  |

| 1.     |     |         | I                                                    |     |

| 1.     |     |         | Features                                             |     |

| 1.     | _   |         | ation Fields                                         |     |

| 1.     | _   |         | ng Information                                       |     |

| 1.     | -   |         | nfiguration (Top View)                               |     |

| 1.     | _   |         | uration of Function Block                            |     |

|        | -   | .6.1    | Block Diagram of V850/DB1                            |     |

|        | -   | .6.2    | On-chip units.                                       |     |

|        |     | .0.2    | On-drip units.                                       | ۷1  |

| Chapte | r 2 | Pin F   | unctions                                             | 31  |

| 2.     |     |         | Pin Functions                                        |     |

| 2.     |     |         | otion of Pin Functions                               |     |

| 2.     |     |         | of Pin I/O Circuit and Connection of Unused Pin      |     |

|        |     | ,,,     |                                                      |     |

| Chapte | r 3 | CPU I   | Functions                                            | 61  |

| 3.     |     | Feature | 98                                                   | 61  |

| 3.     | 2   | CPU Re  | egister Set                                          | 62  |

|        | 3   | .2.1    | Program register set                                 |     |

|        | 3   | .2.2    | System register set                                  |     |

| 3.     | 3   | Operati | on Modes                                             | 66  |

| 3.     | 4   | Addres  | s Space                                              | 67  |

|        | 3   | .4.1    | CPU address space                                    | 67  |

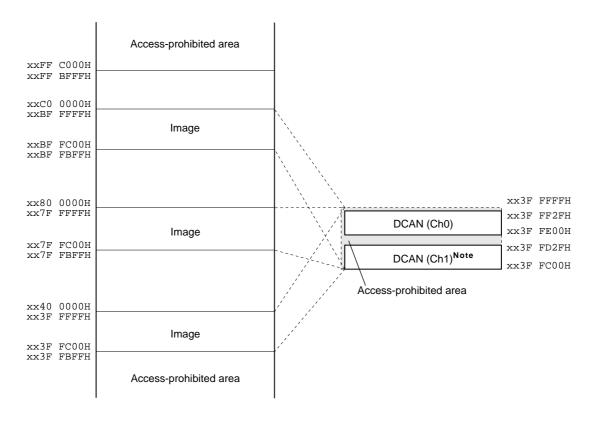

|        | 3   | .4.2    | Image                                                | 68  |

|        | 3   | .4.3    | Wrap-around of CPU address space                     | 69  |

|        | 3   | .4.4    | Memory map                                           | 70  |

|        | 3   | .4.5    | Area                                                 | 71  |

|        | 3   | .4.6    | Recommended use of address space                     | 76  |

|        | 3   | .4.7    | Peripheral I/O registers                             | 79  |

|        | 3   | .4.8    | Non-Peripheral I/O Registers for DCAN1 and DCAN0     | 86  |

|        | 3   | .4.9    | Specific registers                                   | 06  |

|        |     |         |                                                      |     |

| Chapte |     | Interr  | upt/Exception Processing Function                    | 09  |

| 4.     | -   |         | es                                                   |     |

| 4.     | _   |         | askable Interrupts                                   |     |

|        |     |         | Operation                                            |     |

|        |     | .2.2    | Restore                                              |     |

|        |     | .2.3    | Non-maskable interrupt status flag (NP)1             |     |

|        |     | .2.4    | Edge detection function of NMI pin1                  |     |

| 4.     | -   |         | ble Interrupts1                                      |     |

|        |     | .3.1    | Operation                                            |     |

|        |     | .3.2    | Restore                                              |     |

|        |     | .3.3    | Priorities of maskable interrupts                    |     |

|        |     | .3.4    | Interrupt control register (xxICn)                   |     |

|        |     | .3.5    | In-service priority register (ISPR)                  |     |

| -      |     | .3.6    | Maskable interrupt status flag (ID)                  |     |

| 4.     | -   |         | Elimination Circuit                                  |     |

|        |     | .4.1    | Analog Filter (INTPn pins)                           |     |

|        |     | .4.2    | Interrupt trigger mode selection with edge detection |     |

| 4.     | •   |         | re Exception                                         |     |

|        |     | .5.1    | Operation                                            |     |

|        |     | .5.2    | Restore                                              |     |

|        | 4   | .5.3    | Exception status flag (EP)                           | 35  |

|        | 4.6        | Except   | ion Trap                                                 | 136   |

|--------|------------|----------|----------------------------------------------------------|-------|

|        |            | 4.6.1    | Illegal opcode definition                                |       |

|        | 4.7        | Multiple | e Interrupt Processing Control                           |       |

|        |            | 4.7.1    | Priorities of interrupts and exceptions                  |       |

|        |            | 4.7.2    | Multiple interrupt processing                            |       |

|        | 4.8        |          | pt Response Time                                         |       |

|        | 4.9        | Periods  | s in Which Interrupts Are Not Acknowledged               | 140   |

| Ch a m |            | Clask    | Generator                                                | 4 4 4 |

| Chap   |            |          | es                                                       |       |

|        | 5.1<br>5.2 |          | uration                                                  |       |

|        | 5.2<br>5.3 |          | ystem Clock Oscillator                                   |       |

|        | 5.4        |          | Registers                                                |       |

|        | J.4        | 5.4.1    | Processor Clock Control Register (PCC)                   |       |

|        |            | 5.4.1    | Power Save Control Register (PSC)                        |       |

|        |            | 5.4.3    | Writing a special Register                               |       |

|        |            | 5.4.4    | Processor Clock Output Mode Register (CLOM)              |       |

|        |            | 5.4.5    | Oscillation stabilization time selection register (OSTS) |       |

|        | 5.5        |          | Saving Functions                                         |       |

|        | J.J        | 5.5.1    | General                                                  |       |

|        |            | 5.5.2    | Power Save Modes Outline                                 |       |

|        |            | 5.5.3    | Operating States in Power Save Functions Mode            |       |

|        |            | 5.5.4    | HALT mode                                                |       |

|        |            | 5.5.5    | WATCH mode.                                              |       |

|        |            | 5.5.6    | Software STOP mode                                       |       |

|        | 5.6        |          | ng Oscillation Stabilization Time                        |       |

|        | J.U        | 5.6.1    | Oscillation stabilization time security specification    |       |

|        |            | 0.0.1    | Osomation stabilization time security specimoation       | 101   |

| Chapt  | ter (      | 3 Timer  | r                                                        | 161   |

| -      | 6.1        |          | 3                                                        |       |

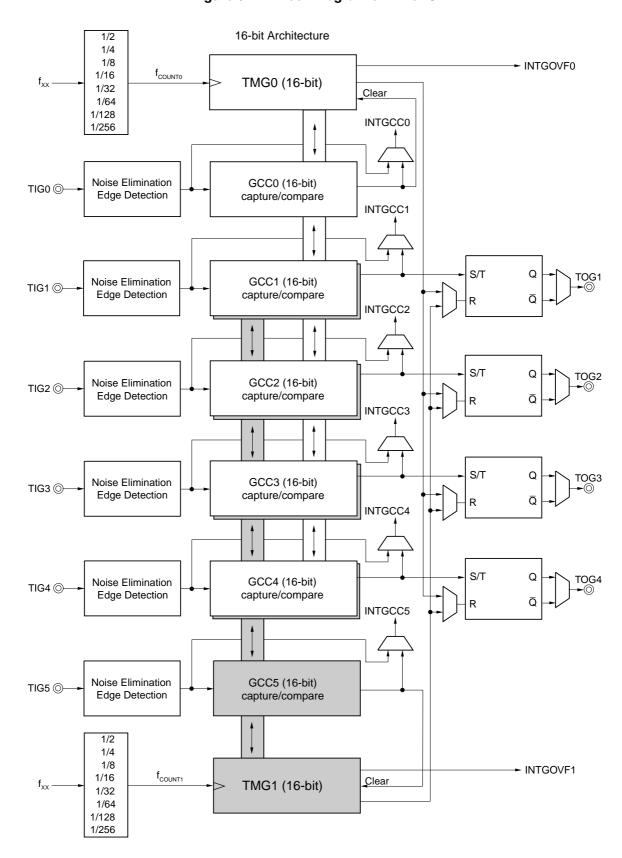

|        |            | 6.1.1    | Features (Timer G)                                       |       |

|        |            | 6.1.2    | Function overview (Timer G)                              |       |

|        |            | 6.1.3    | Basic configuration                                      |       |

|        |            | 6.1.4    | Control Registers                                        |       |

|        |            | 6.1.5    | Output delay operation                                   |       |

|        |            | 6.1.6    | Explanation of Basic Operation                           |       |

|        |            | 6.1.7    | Operation in Free-run mode                               | 175   |

|        |            | 6.1.8    | Match and clear mode                                     | 185   |

|        |            | 6.1.9    | Edge detection noise elimination                         | 196   |

|        |            | 6.1.10   | Precautions Timer G                                      | 197   |

|        | 6.2        | Timer C  | · · · · · · · · · · · · · · · · · · ·                    | 199   |

|        |            | 6.2.1    | Features (Timer C)                                       | 199   |

|        |            | 6.2.2    | Function overview (Timer C)                              | 200   |

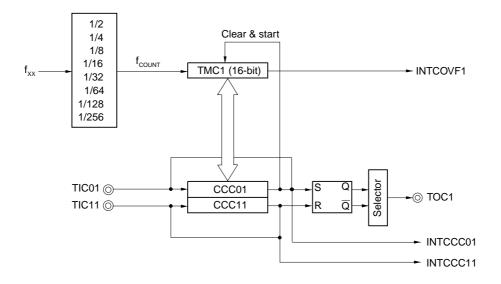

|        |            | 6.2.3    | Basic configuration                                      | 202   |

|        |            | 6.2.4    | Control registers                                        | 206   |

|        |            | 6.2.5    | Operation                                                |       |

|        |            | 6.2.6    | Precautions Timer C                                      | 221   |

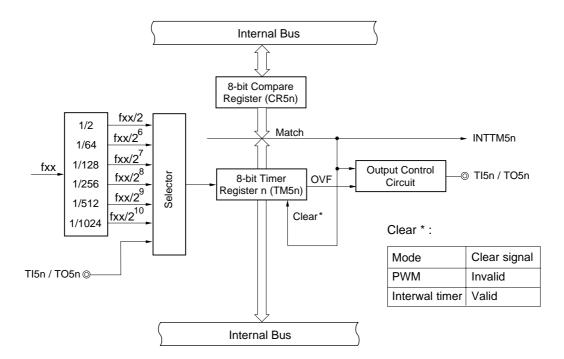

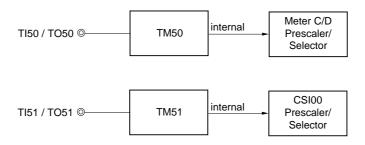

|        | 6.3        | Timer 5  | 5 (TM50, TM51)                                           |       |

|        |            | 6.3.1    | Functions                                                |       |

|        |            | 6.3.2    | Configuration                                            | 224   |

|        |            | 6.3.3    | Timer 5n control register                                |       |

|        |            | 6.3.4    | 8-Bit Timer Operation                                    |       |

|        |            | 6.3.5    | Operating as interval timer (16 bits)                    | 238   |

|        |            | 6.3.6    | Precautions Timer 5                                      | 240   |

|        |            |          |                                                          |       |

| Chapt  | ter 7      |          | h Timer                                                  |       |

|        | 7.1        |          | on                                                       |       |

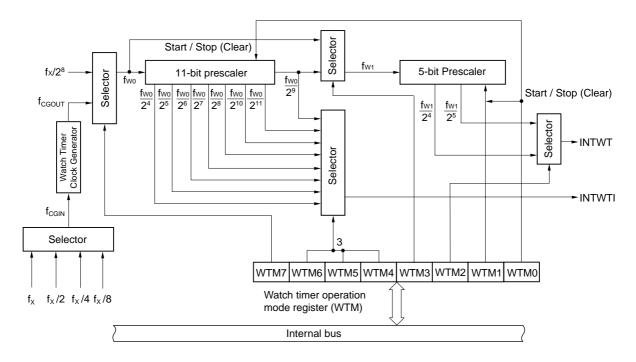

|        | 7.2        | Configu  | uration                                                  | 244   |

|      | 7.3   | Watch          | Timer Control Register                                    | 244   |

|------|-------|----------------|-----------------------------------------------------------|-------|

|      | 7.4   | Watch          | Timer Clock Generator                                     | 246   |

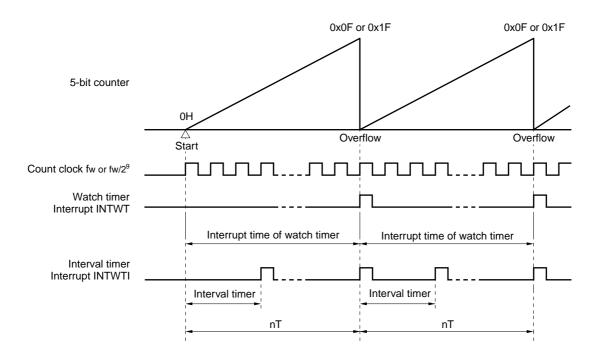

|      | 7.5   | Opera          | tions                                                     | 248   |

|      |       | 7.5.1          | Operation as watch timer                                  | 248   |

|      |       | 7.5.2          | Operation as interval timer                               | 249   |

|      |       | 7.5.3          | Watch timer and Interval timer simultaneously             | 250   |

|      |       |                |                                                           |       |

| Chap | ter a |                | chdog Timer Function                                      |       |

|      | 8.1   |                | ons                                                       |       |

|      | 8.2   |                | guration                                                  |       |

|      | 8.3   |                | dog Timer Control Register                                |       |

|      | 8.4   | •              | tion                                                      |       |

|      |       | 8.4.1          | Operating as watchdog timer                               |       |

|      |       | 8.4.2          | Operating as interval timer (maskable interrupt INTWDTM)  | 256   |

| Char | tor   | n Soria        | al Interface Function                                     | 257   |

| Chap | 9.1   |                | 'es                                                       |       |

|      | 9.1   |                | chronous Serial Interfaces 50, 51 (UART50, UART51)        |       |

|      | 9.2   | -              |                                                           |       |

|      |       | 9.2.1<br>9.2.2 | Features                                                  |       |

|      |       | 9.2.2          | Configuration                                             |       |

|      |       | 9.2.3          | Control registers                                         |       |

|      |       | 9.2.4          | Interrupt requests                                        |       |

|      |       | 9.2.5          | Dedicated baud rate generators (BRG) of UART5n (n = 0, 1) |       |

|      |       | 9.2.7          | Precautions                                               |       |

|      | 9.3   |                | ed Serial Interfaces 0 to 2 (CSI00, CSI01, CSI02)         |       |

|      | 9.3   | 9.3.1          | Features                                                  |       |

|      |       | 9.3.1          | Configuration                                             |       |

|      |       | 9.3.2          | Control registers                                         |       |

|      |       | 9.3.4          | Operation                                                 |       |

|      |       | 9.3.4          | Output pins                                               |       |

|      |       | 9.3.6          | TM51 output as dedicated baud rate generator for CSI00    |       |

|      |       | 3.3.0          | TWO TOULPUL as dedicated badd rate generator for Coloo    |       |

| Char | ter   | 10 DCA         | N                                                         | . 317 |

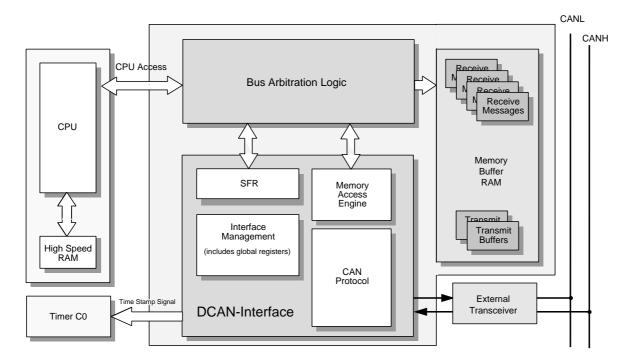

| ٦    | 10.1  |                | e Description                                             |       |

|      | 10.2  |                | nemory                                                    |       |

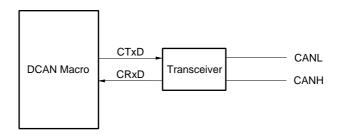

|      | 10.3  |                | ection with Target System                                 |       |

|      | 10.4  |                | Controller Configuration                                  |       |

|      | 10.5  |                | al Function Register for DCAN-module                      |       |

|      | 10.6  |                | age Buffer Configuration                                  |       |

|      | 10.7  |                | mit Buffer Structure                                      |       |

|      | 10.8  |                | mit Message Buffer Format                                 |       |

|      | 10.9  |                | ve Message Buffer Structure                               |       |

|      | 10.1  | 0 Receiv       | ve Message Buffer Format                                  | 329   |

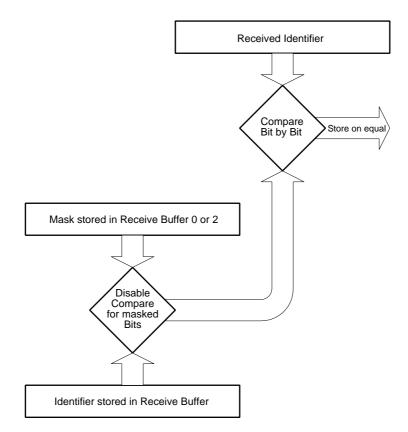

|      | 10.1  | 1 Mask         | Function                                                  | 335   |

|      | 10.1  | 2 Opera        | tion of the DCAN Controller                               |       |

|      |       | 10.12.1        | DCAN Control Register (DCANCn) (n = 0, 1)                 | 339   |

|      |       | 10.12.2        | CAN Control Register (CANCn)                              | 340   |

|      |       | 10.12.3        | DCAN Error Status Register                                |       |

|      |       | 10.12.4        | CAN Transmit Error Counter                                | 348   |

|      |       | 10.12.5        | CAN Receive Error Counter                                 | 348   |

|      |       | 10.12.6        | Message Count Register                                    | 349   |

|      | 10.1  | 3 Baudr        | ate Generation                                            | 350   |

|      | 10.1  | 4 Functi       | on Control                                                | 357   |

|      |       | 10.14.1        | Transmit Control                                          | 357   |

|      |       | 10.14.2        | Receive Control                                           | 360   |

|      |       | 10.14.3        | Mask Control                                              | 361   |

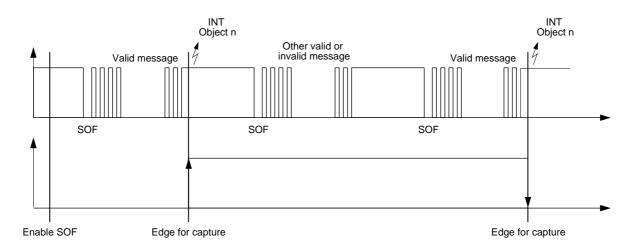

|      |       | 10 14 4        | Special Functions                                         | 363   |

| 365                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 366                                                                                                                                                          |

| 366                                                                                                                                                          |

| 366                                                                                                                                                          |

| 366                                                                                                                                                          |

| 367                                                                                                                                                          |

| 3 <b>68</b><br>368                                                                                                                                           |

| 368                                                                                                                                                          |

| 368                                                                                                                                                          |

| 368                                                                                                                                                          |

| 370                                                                                                                                                          |

| 371                                                                                                                                                          |

| 371                                                                                                                                                          |

| 372                                                                                                                                                          |

| 373                                                                                                                                                          |

| 374                                                                                                                                                          |

| 375                                                                                                                                                          |

|                                                                                                                                                              |

| 377                                                                                                                                                          |

| 377                                                                                                                                                          |

| 379<br>381                                                                                                                                                   |

| 381                                                                                                                                                          |

| 3 <b>8</b> 6                                                                                                                                                 |

| 386                                                                                                                                                          |

| 388                                                                                                                                                          |

|                                                                                                                                                              |

| 390                                                                                                                                                          |

|                                                                                                                                                              |

| 390<br><b>392</b>                                                                                                                                            |

| 390<br><b>392</b><br>3 <b>95</b>                                                                                                                             |

| 390<br><b>392</b><br>3 <b>95</b><br>3 <b>95</b>                                                                                                              |

| 390<br><b>392</b><br><b>395</b><br><b>395</b>                                                                                                                |

| 390<br><b>392</b><br><b>395</b><br><b>395</b><br><b>397</b>                                                                                                  |

| 390<br>3 <b>92</b><br>3 <b>95</b><br>3 <b>95</b><br>3 <b>99</b><br>4 <b>03</b>                                                                               |

| 390<br><b>392</b><br><b>395</b><br><b>397</b><br><b>399</b><br><b>403</b>                                                                                    |

| 390<br>392<br>395<br>395<br>397<br>399<br>403                                                                                                                |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403                                                                                                         |

| 390<br>392<br>395<br>395<br>397<br>399<br>403                                                                                                                |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404                                                                                                  |

| 390<br>3 <b>92</b><br>3 <b>95</b><br>3 <b>95</b><br>3 <b>99</b><br>403<br>404<br>405                                                                         |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404                                                                                                  |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405                                                                                           |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>107<br>407                                                                             |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>408<br>4108<br>4112<br>4113                                              |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>405<br>407<br>407<br>407<br>412<br>4113<br>4114                                                      |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>408<br>411<br>411<br>411<br>411                                                 |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>417<br>417                                                               |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>408<br>411<br>411<br>411<br>411                                                 |

| 390<br>392<br>395<br>395<br>395<br>399<br>403<br>404<br>405<br>407<br>407<br>408<br>4109<br>4112<br>4113<br>4114<br>417                                      |

| 390<br>392<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>417<br>417<br>417<br>417                                                 |

| 390<br>392<br>395<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>412<br>413<br>417<br>420<br>423<br>423                            |

| 390<br>392<br>395<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>41 |

| 390<br>392<br>395<br>395<br>395<br>397<br>403<br>403<br>404<br>405<br>107<br>408<br>411<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417       |

| 390<br>392<br>395<br>395<br>395<br>397<br>399<br>403<br>403<br>404<br>405<br>407<br>407<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>417<br>41 |

|                                                                                                                                                              |

| 1          |            | Port 2                               |       |

|------------|------------|--------------------------------------|-------|

| 1          | 14.3.4     | Port 3                               | . 445 |

| 1          |            | Port 4                               |       |

| 1          |            | Port 5                               |       |

| 1          |            | Port 6                               |       |

| 1          | 14.3.8     | Port 7                               | . 455 |

| 1          | 14.3.9     | Port 8                               | . 456 |

| 1          | 14.3.10    | Port 9                               | . 458 |

| 1          | 14.3.11    | Port 10                              | . 460 |

| 1          | 14.3.12    | Port 11                              | . 463 |

|            |            | Port 12                              |       |

|            |            | Port 13                              |       |

|            |            | Port 14                              |       |

| •          | 14.0.10    | 1 010 17                             | . 712 |

| Chanter 1  | DECE       | T Function                           | 175   |

| •          |            |                                      |       |

|            |            | \$                                   |       |

| 15.2       |            | ctions                               |       |

| 15.3       | Initializa | ation                                | . 477 |

| _          |            |                                      |       |

|            |            | ator                                 |       |

| 16.1       |            |                                      |       |

| 16.2       | Operation  | on                                   | . 479 |

|            |            |                                      |       |

| Chapter 17 | 7 Flash    | Memory                               | 481   |

| 17.1       |            | S                                    |       |

| 17.2       |            | by Flash writer                      |       |

| 17.3       |            | nming Environment                    |       |

| 17.4       | _          | inication System                     |       |

| 17.5       |            | rogramming Circuitry                 |       |

| _          |            | idling                               |       |

|            |            | V <sub>PP</sub> pin                  |       |

|            |            | Serial interface pins                |       |

|            |            |                                      |       |

|            |            | RESET pin                            |       |

|            |            | NMI pin                              |       |

|            |            | Flash memory programming mode        |       |

|            |            | Port pins                            |       |

|            |            | Other signal pins                    |       |

|            |            | Power supply                         |       |

|            |            | mming Method                         |       |

|            |            | Flash memory control                 |       |

|            |            | Selection of communication mode      |       |

|            |            | gramming Mode                        |       |

| 17.9       | Secure     | Selfprogramming                      | . 493 |

| 1          | 17.9.1     | General description                  | . 493 |

| 1          | 17.9.2     | Signature structure                  | . 493 |

| 1          |            | Secure selfprogramming flow          |       |

|            |            | Advantages of Secure Selfprogramming |       |

|            |            |                                      |       |

| Annondiv   | A List of  | f Instruction Sets                   | 107   |

| Thheilaix  | ₩ FISE O   | : III3II UUIIUII 9513                | 43/   |

|            |            |                                      |       |

| Appendix   | B Index    |                                      | 509   |

|            |            |                                      |       |

| Appendix   | C Revisi   | ion History                          | 517   |

# **List of Figures**

| Figure 1-1:  | Pin Configuration of the V850/DB1 Microcontroller                  |     |

|--------------|--------------------------------------------------------------------|-----|

| Figure 1-2:  | Block Diagram of the V850/DB1 Microcontroller                      | 26  |

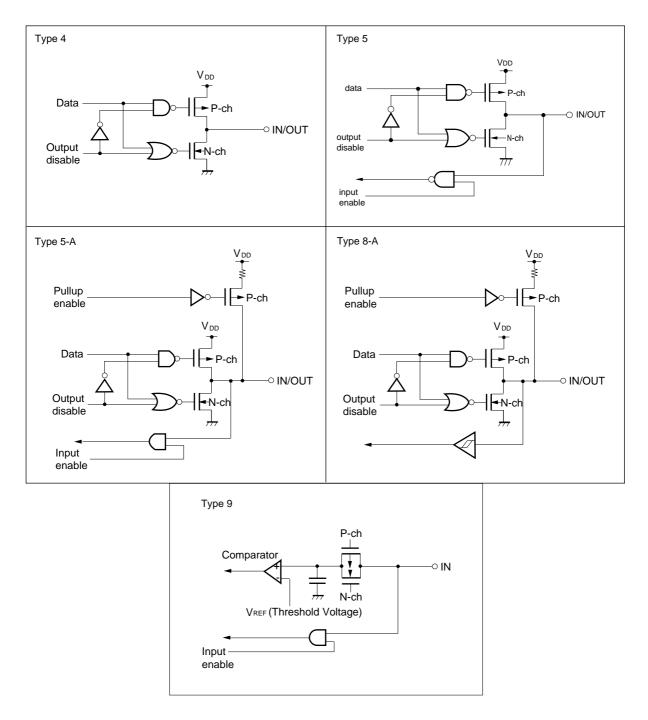

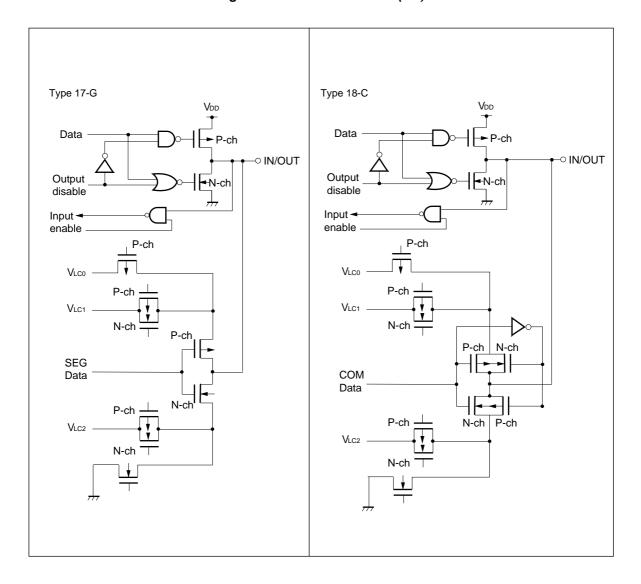

| Figure 2-1:  | Pin I/O Circuits (1/2)                                             |     |

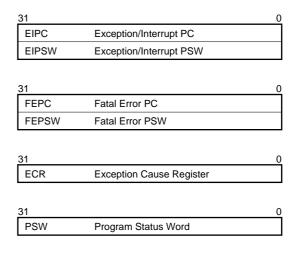

| Figure 3-1:  | CPU Register Set                                                   | 62  |

| Figure 3-2:  | Program Counter (PC)                                               |     |

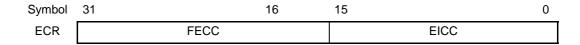

| Figure 3-3:  | Interrupt Source Register (ECR)                                    |     |

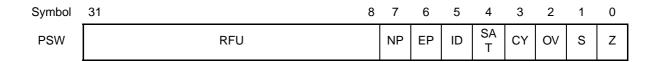

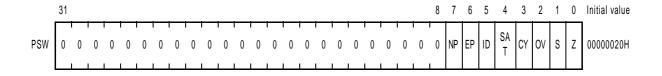

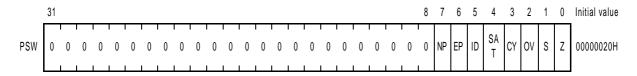

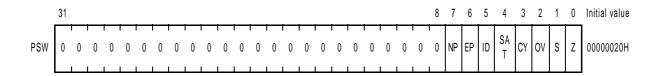

| Figure 3-4:  | Program Status Word (PSW)                                          | 65  |

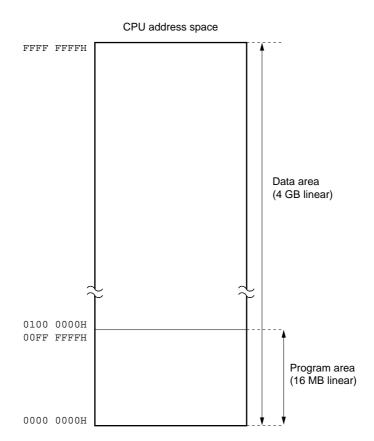

| Figure 3-5:  | CPU Address Space                                                  | 67  |

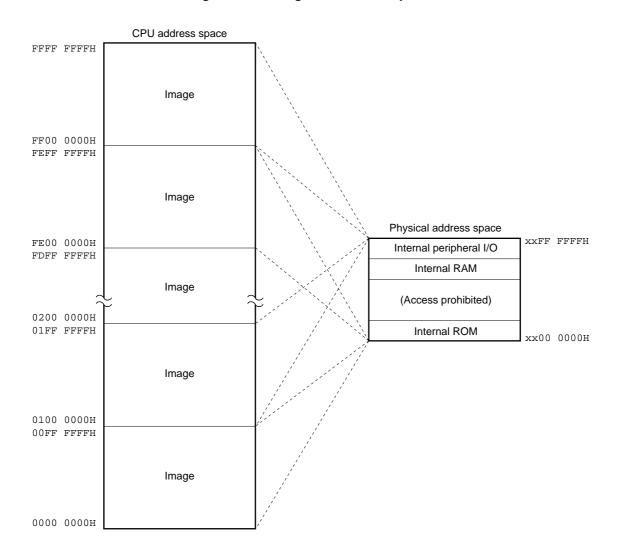

| Figure 3-6:  | Image on Address Space                                             |     |

| Figure 3-7:  | Wrap-around Program Space                                          |     |

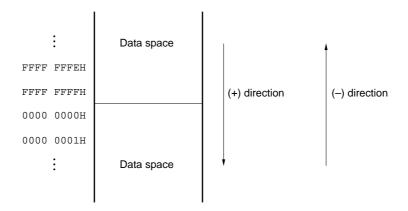

| Figure 3-8:  | Data Space                                                         | 69  |

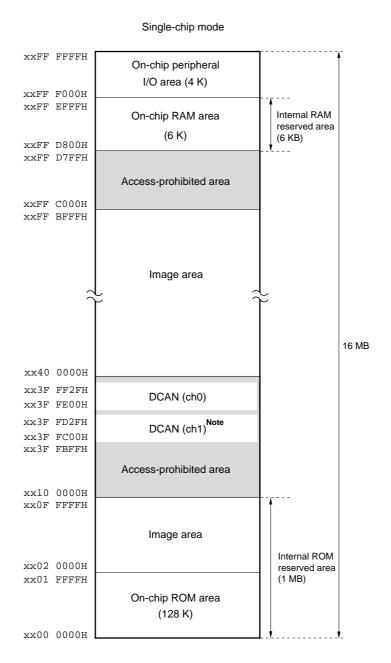

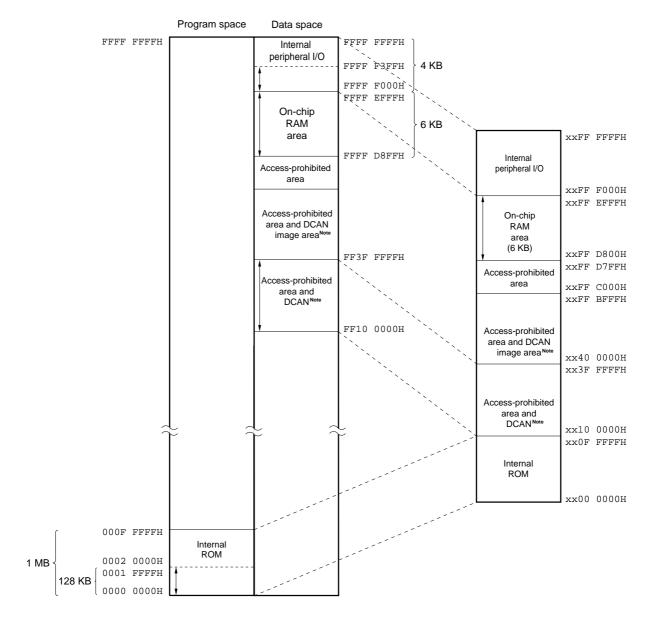

| Figure 3-9:  | Memory Map                                                         |     |

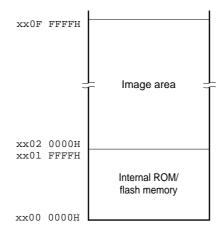

| Figure 3-10: | Internal ROM/Flash Memory Area                                     | 71  |

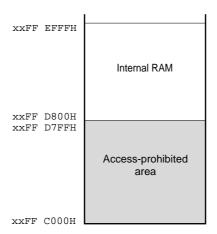

| Figure 3-11: | Internal RAM Area                                                  | 74  |

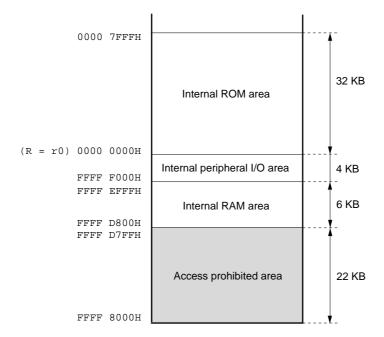

| Figure 3-12: | Internal Peripheral I/O Area                                       |     |

| Figure 3-13: | Application of Wrap-Around                                         | 77  |

| Figure 3-14: | Recommended Memory Map (Flash Memory Version)                      | 78  |

| Figure 3-15: | Command Register (PRCMD)                                           | 107 |

| Figure 3-16: | System Status Register (SYS)                                       |     |

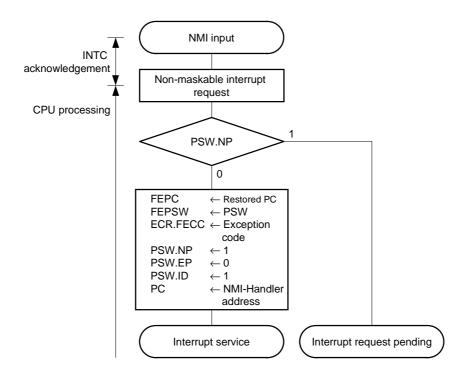

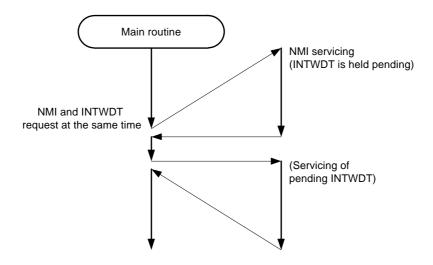

| Figure 4-1:  | Processing Configuration of Non-Maskable Interrupt                 | 114 |

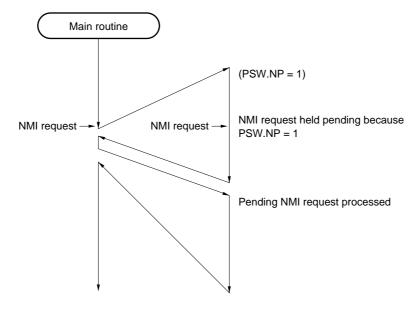

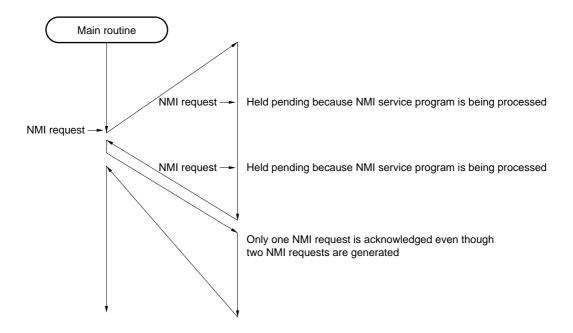

| Figure 4-2:  | Acknowledging Non-Maskable Interrupt Request                       | 115 |

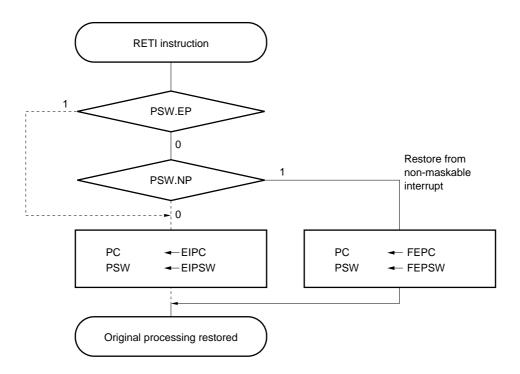

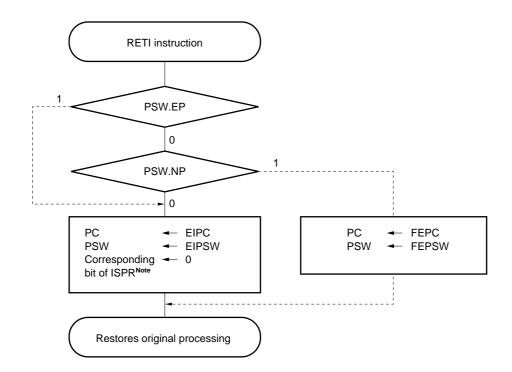

| Figure 4-3:  | RETI Instruction Processing                                        | 117 |

| Figure 4-4:  | Non-maskable Interrupt Status Flag (NP)                            | 118 |

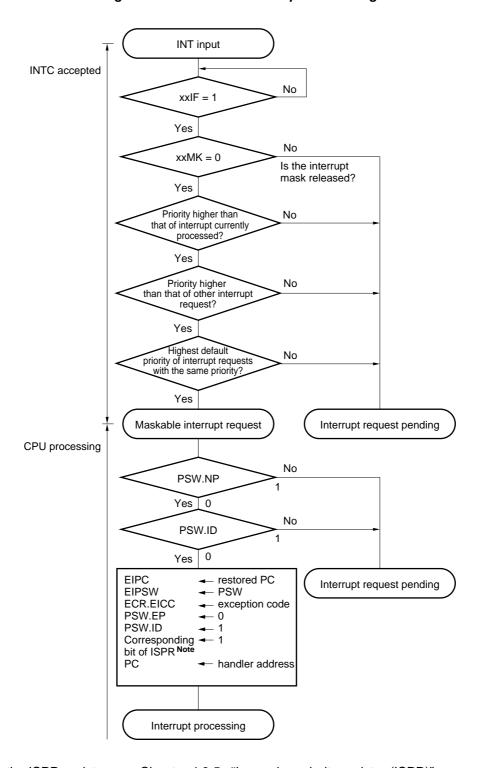

| Figure 4-5:  | Maskable Interrupt Processing                                      | 120 |

| Figure 4-6:  | RETI Instruction Processing                                        | 121 |

| Figure 4-7:  | Example of Processing in Which Another Interrupt Request Is Issued |     |

| _            | While an Interrupt Is Being Processed (1/2)                        | 123 |

| Figure 4-8:  | Example of Processing Interrupt Requests Simultaneously Generated  | 125 |

| Figure 4-9:  | Interrupt Control Register (xxICn)                                 | 126 |

| Figure 4-10: | In-Service Priority Register (ISPR)                                | 128 |

| Figure 4-11: | Maskable Interrupt Status Flag (ID)                                | 129 |

| Figure 4-12: | Rising Edge Specification Register (EGP0) Format                   | 131 |

| Figure 4-13: | Falling Edge Specification Register (EGN0) Format                  | 132 |

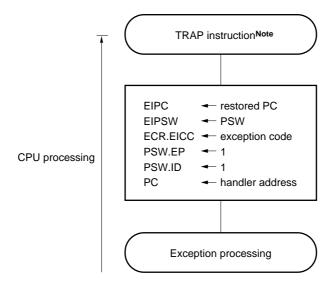

| Figure 4-14: | Software Exception Processing                                      | 133 |

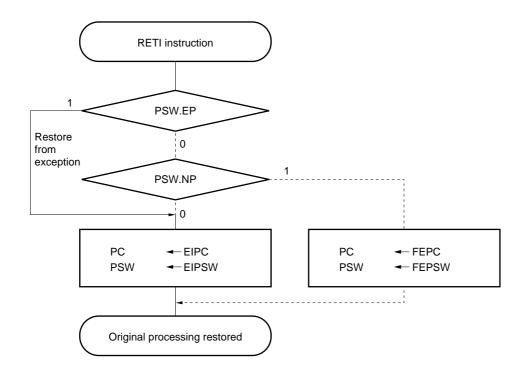

| Figure 4-15: | RETI Instruction Processing                                        | 134 |

| Figure 4-16: | Exception Status Flag (EP)                                         | 135 |

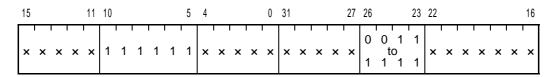

| Figure 4-17: | Illegal opcode definition                                          | 136 |

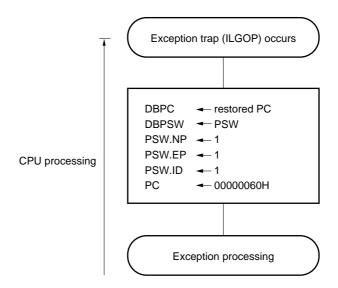

| Figure 4-18: | Exception Trap Processing                                          | 137 |

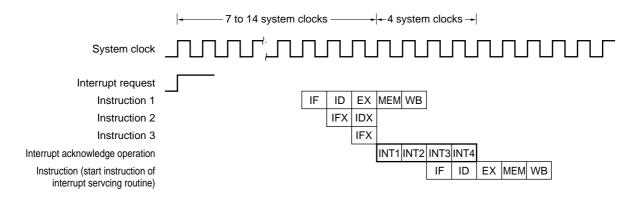

| Figure 4-19: | Pipeline Operation at Interrupt Request Acknowledgment (Outline)   | 140 |

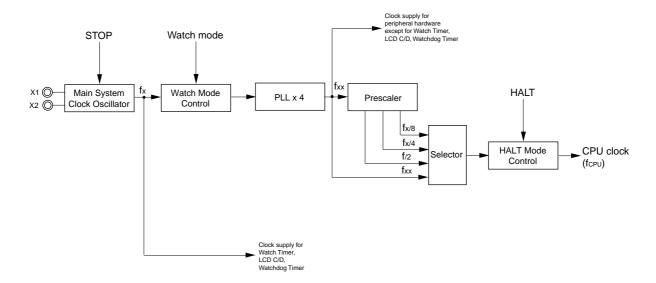

| Figure 5-1:  | Block Diagram of the Clock Generator                               | 141 |

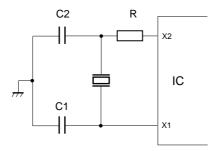

| Figure 5-2:  | Main System Cock Oscillator                                        | 142 |

| Figure 5-3:  | Format of Processor Clock Control Register (PCC)                   | 143 |

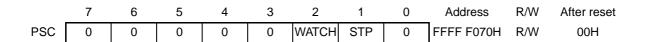

| Figure 5-4:  | Format of Power Save Control Register (PSC)                        | 144 |

| Figure 5-5:  | Format of Clock Output Mode Register (CLOM)                        |     |

| Figure 5-6:  | Format of Oscillation Stabilization Time Selection Register (OSTS) | 147 |

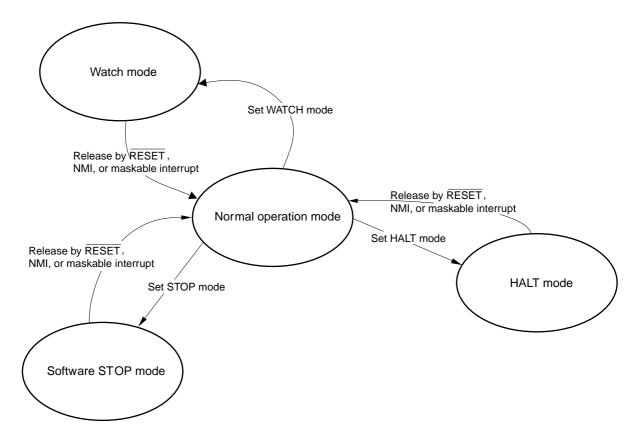

| Figure 5-7:  | Power Save Mode State Transition Diagram                           |     |

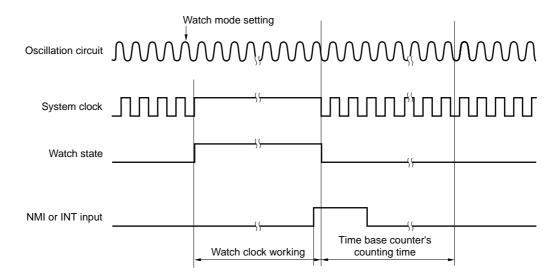

| Figure 5-8:  | WATCH mode release by NMI or INTPn                                 |     |

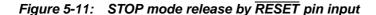

| Figure 5-9:  | STOP mode release by NMI or INTPn                                  | 158 |

| Figure 5-10: | WATCH mode release by RESET-pin input or watchdog timer            | 159 |

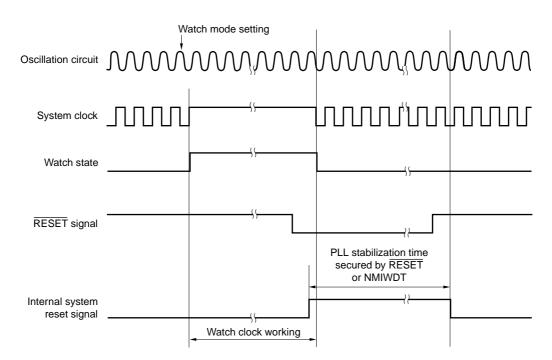

| Figure 5-11: | STOP mode release by RESET pin input                               |     |

| Figure 6-1:  | Block Diagram of Timer G                                           |     |

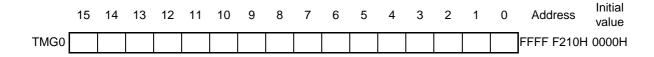

| Figure 6-2:  | Timer G Counter Value Registers TMG0                               |     |

| Figure 6-3:  | Timer G Counter Value Registers TMG1                               |     |

| Figure 6-4:  | Timer G counter TMG0 assigned Capture/Compare Register (GCC0)      |     |

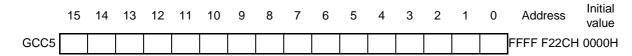

| Figure 6-5:  | Timer G counter TMG1 assigned Capture/Compare Register (GCC5)      |     |

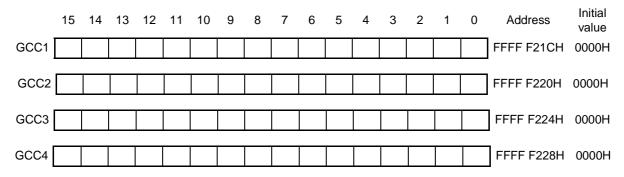

| Figure 6-6:  | Timer G free assignable Capture/Compare Registers (GCCm) (m = 1 to 4)  | 166 |

|--------------|------------------------------------------------------------------------|-----|

| Figure 6-7:  | Timer G Mode Register High (TMGMH)                                     |     |

| Figure 6-8:  | Timer G Mode Register Low (TMGML)                                      | 168 |

| Figure 6-9:  | Timer G Channel Mode Register (TMGCMH, TMGCML)                         | 169 |

| Figure 6-10: | Timer G Output Control Register (OCTLGH, OCTLGL)                       | 170 |

| Figure 6-11: | Timer G Status Register (TMGST)                                        |     |

| Figure 6-12: | Timing of Output delay operation                                       |     |

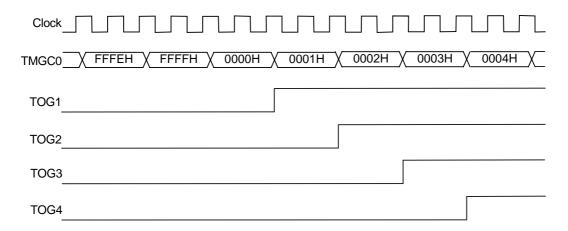

| Figure 6-13: | Timing when both edges of TIG0 are valid (free run)                    |     |

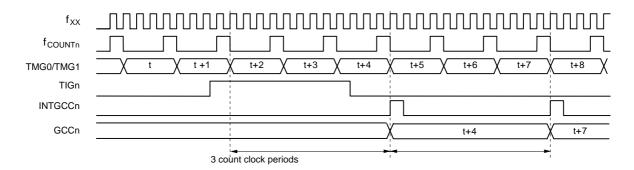

| Figure 6-14: | Timing of capture trigger edge detection (free run)                    |     |

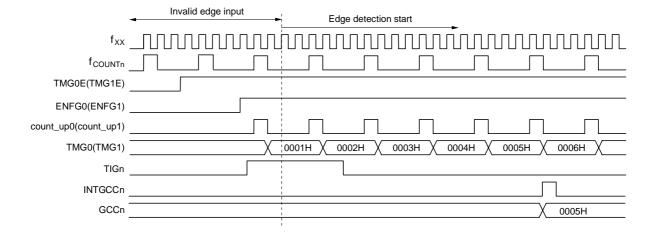

| Figure 6-15: | Timing of starting capture trigger edge detection                      |     |

| Figure 6-16: | Timing of compare mode (free run)                                      |     |

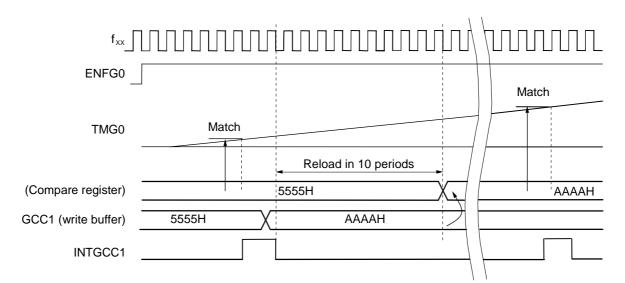

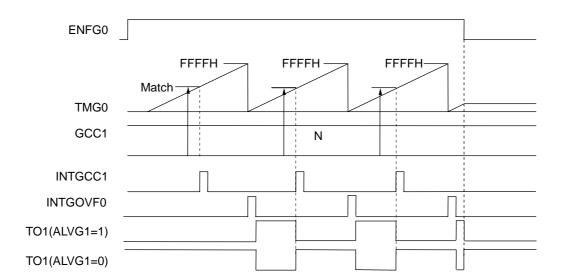

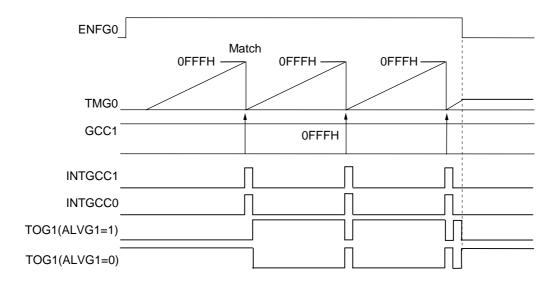

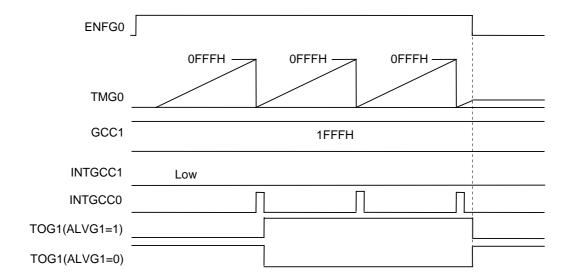

| Figure 6-17: | Timing when GCC1 is rewritten during operation (free run)              |     |

| Figure 6-18: | Timing of PWM operation (free run)                                     | 182 |

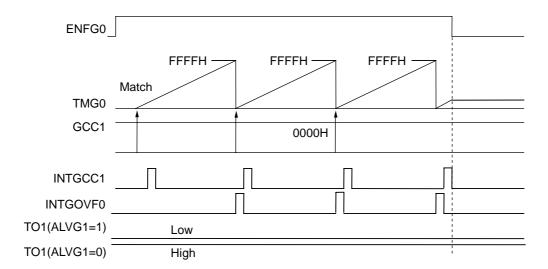

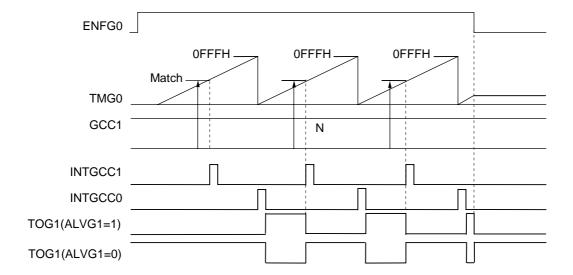

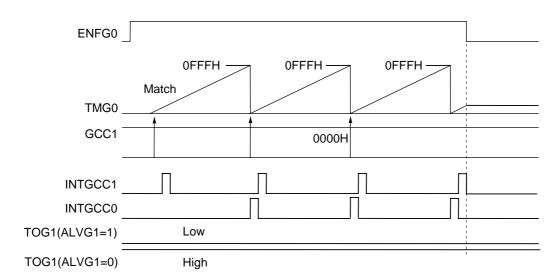

| Figure 6-19: | Timing when 0000H is set in GCCm (free run)                            |     |

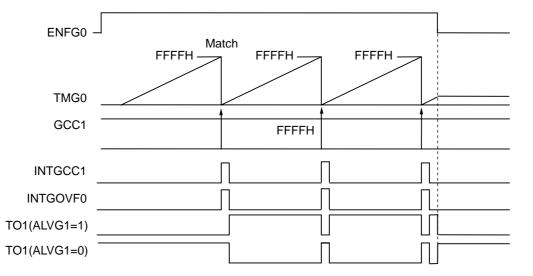

| Figure 6-20: | Timing when FFFFH is set in GCCm (free run)                            |     |

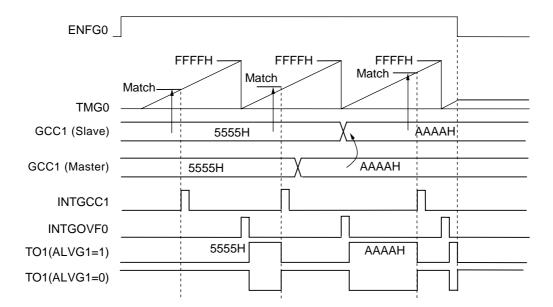

| Figure 6-21: | Timing when GCCm is rewritten during operation (free run)              |     |

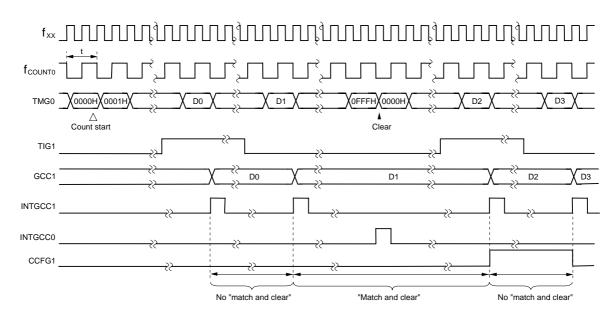

| Figure 6-22: | Timing when both edges of TIGm are valid (match and clear)             |     |

| Figure 6-23: | Timing of compare operation (match and clear)                          |     |

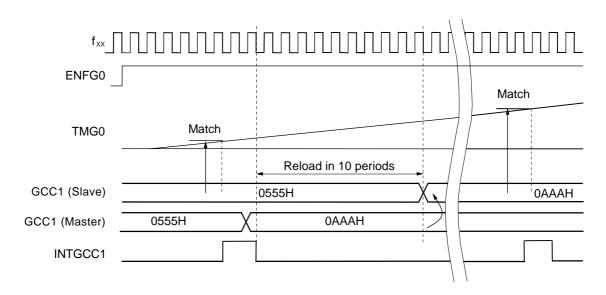

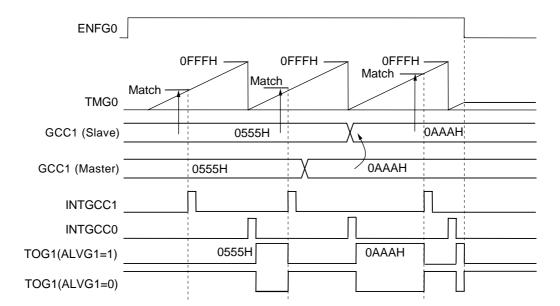

| Figure 6-24: | Timing when GCCm is rewritten during operation (match and clear)       |     |

| Figure 6-25: | Timing of PWM operation (match and clear)                              |     |

| Figure 6-25: | Timing when 0000H is set in GCCm (match and clear)                     |     |

| -            | ·                                                                      | 192 |

| Figure 6-27: | Timing when the same value as set in GCC0/GCC5 is set in GCCm          | 102 |

| Ciaura 6 20. | (match and clear)                                                      |     |

| Figure 6-28: | Timing when the value of GCCm exceeding GCC0 or GCC5 (match and clear) |     |

| Figure 6-29: | Timing when GCCm is rewritten during operation (match and clear)       |     |

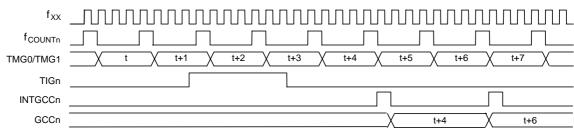

| Figure 6-30: | Timing of Edge detection noise elimination                             |     |

| Figure 6-31: | Block Diagram of Timer C0                                              |     |

| Figure 6-32: | Block Diagram of Timer C1                                              |     |

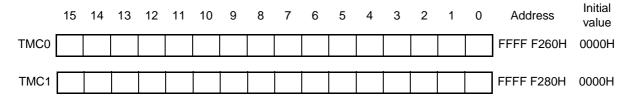

| Figure 6-33: | Timer C counter (TMC0)                                                 |     |

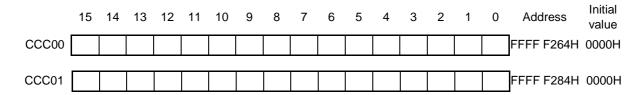

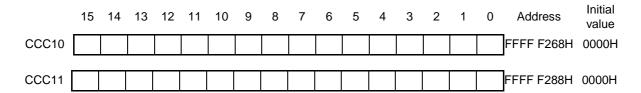

| Figure 6-34: | Capture/Compare Register 0 of TMCn (CCC0n) (n = 0, 1)                  |     |

| Figure 6-35: | Capture/Compare Register 1 of TMC1 (CCC1n) (n = 0, 1)                  |     |

| Figure 6-36: | Timer C control Register 0 (TMCC0n) $(n = 0, 1) (1/2)$                 |     |

| Figure 6-37: | Timer C control Register 1 (TMCC1n) (n = 0, 1) $(1/2)$ )               |     |

| Figure 6-38: | Valid Edge Selection Register (SESCn) (n = 0, 1) (1/2))                |     |

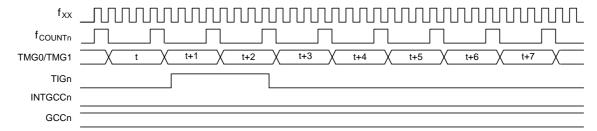

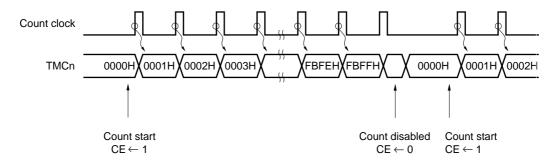

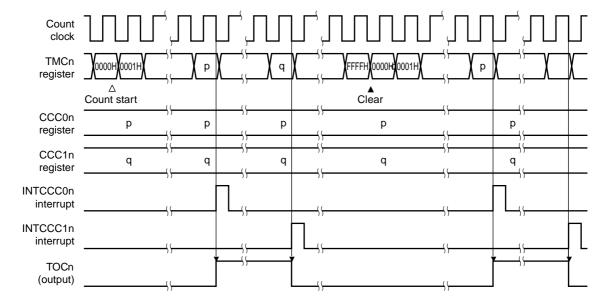

| Figure 6-39: | Timing of basic operation of Timer C                                   |     |

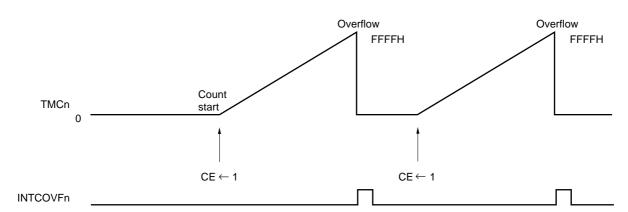

| Figure 6-40: | Timing of interrupt operation after overflow                           |     |

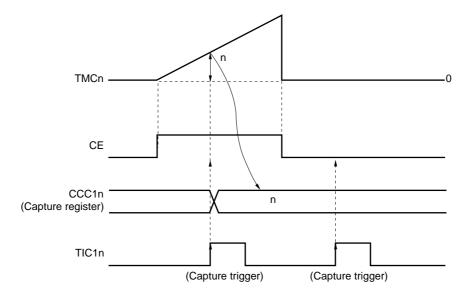

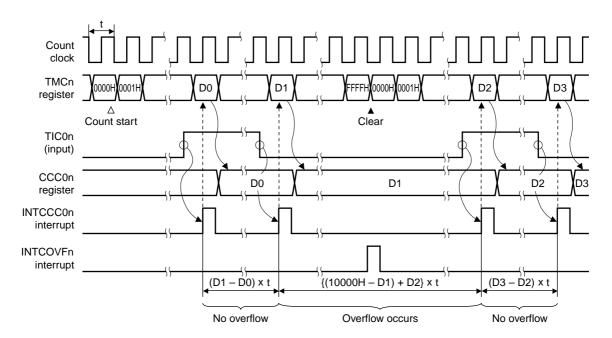

| Figure 6-41: | Timing of capture for pulse cycle measurement (rising edge)            |     |

| Figure 6-42: | Timing of capture for pulse width measurement (both edges)             |     |

| Figure 6-43: | Timing of cycle measurement operation                                  |     |

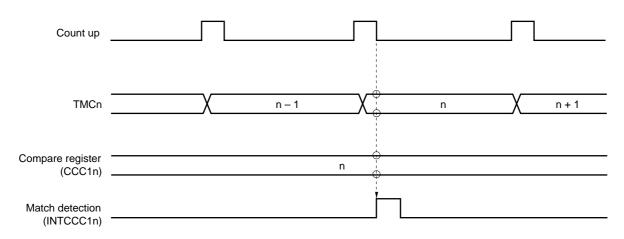

| Figure 6-44: | Timing of compare operation                                            | 217 |

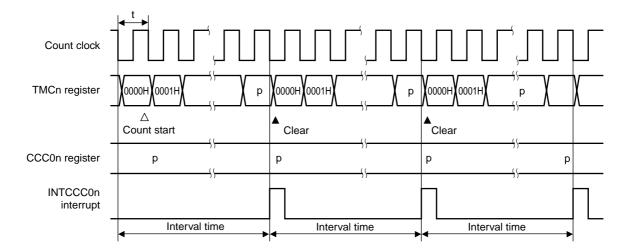

| Figure 6-45: | Timing of interval timer operation                                     |     |

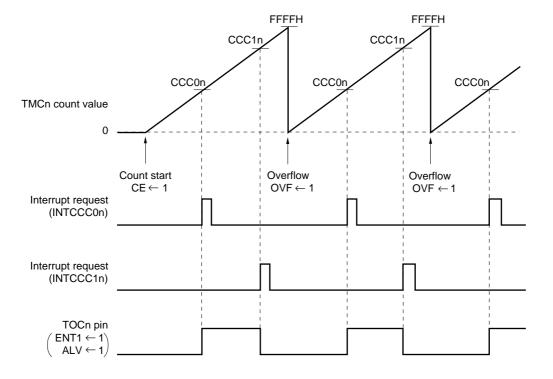

| Figure 6-46: | Timing of PWM output operation (overview)                              | 219 |

| Figure 6-47: | Timing of PWM output operation (detail)                                |     |

| Figure 6-48: | Block Diagram of Timer 50, Timer 51                                    |     |

| Figure 6-49: | Timer 50 and Timer 51 as clock source for Meter and CSI00              | 223 |

| Figure 6-50: | TM50, TM51 Timer Count Registers (TM50, TM51)                          | 224 |

| Figure 6-51: | TM50, TM51 Compare Registers (CR50, CR51)                              | 225 |

| Figure 6-52: | Timer 5 Clock Select Registers (TCL50, TCL51)                          | 226 |

| Figure 6-53: | Timer 5 Mode Control Registers (TMC50, TMC51) (1/2)                    |     |

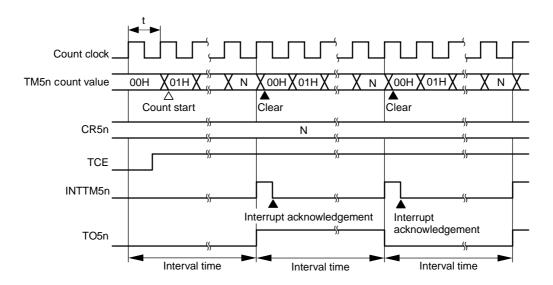

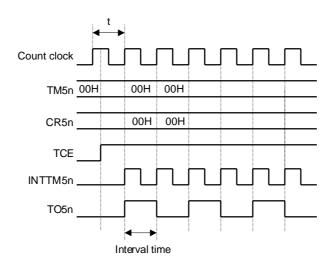

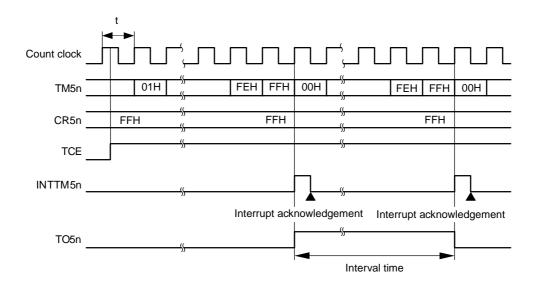

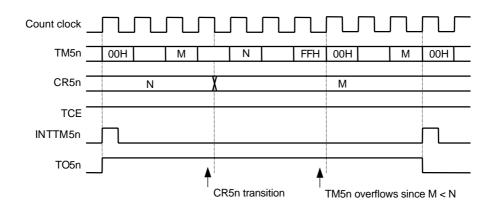

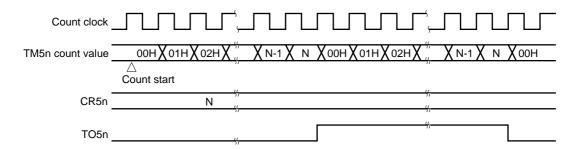

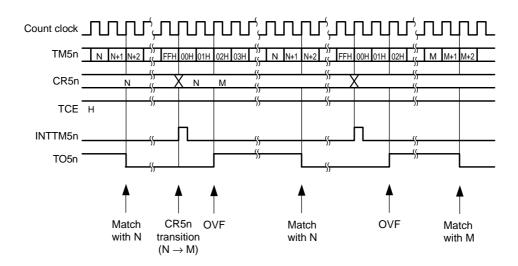

| Figure 6-54: | Timing of Interval Timer Operation (1/3)                               | 229 |

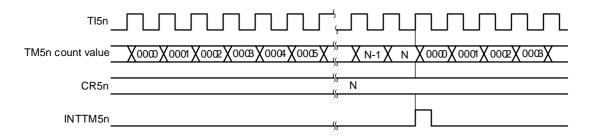

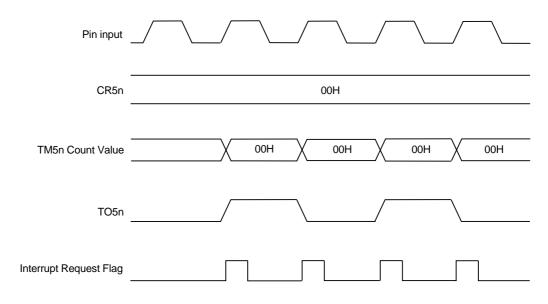

| Figure 6-55: | Timing of external event counter operation                             |     |

| Figure 6-56: | Timing of Square Wave Output Operation Timing                          |     |

| Figure 6-57: | Timing of PWM Output (1/2)                                             |     |

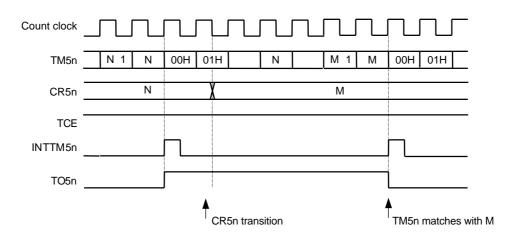

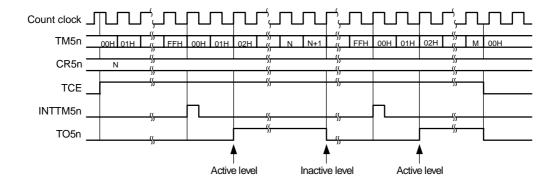

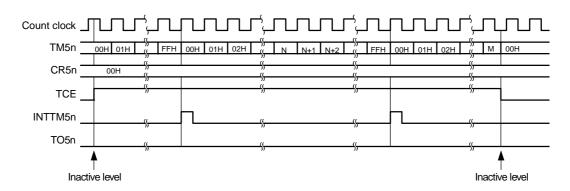

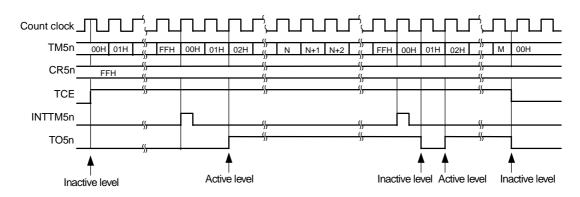

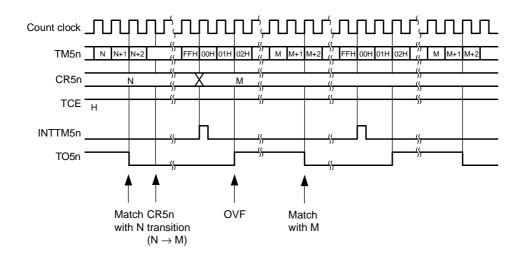

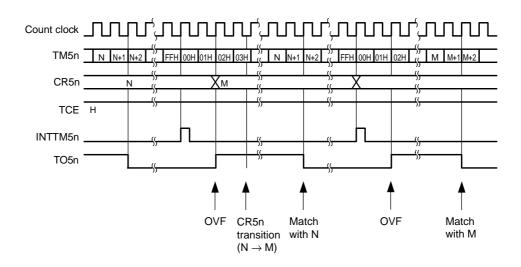

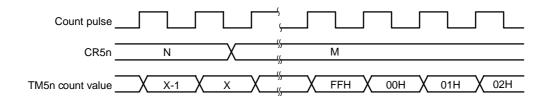

| Figure 6-58: | Timing of Operation Based on CR5n Transitions (1/2)                    |     |

| Figure 6-59: | Cascade connection mode with 16 bit resolution                         |     |

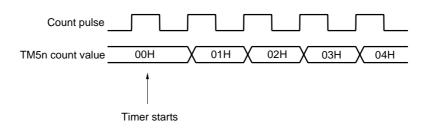

| Figure 6-60: | Start Timing of Timer n                                                |     |

| Figure 6-61: | External Event Counter Operation Timings                               |     |

| Figure 6-62: | Timing after compare register changes during timer count operation     |     |

| Figure 7-1:   | Block Diagram of Watch Timer                                                     |       |

|---------------|----------------------------------------------------------------------------------|-------|

| Figure 7-2:   | Watch Timer Mode Control Register (WTM)                                          | . 245 |

| Figure 7-3:   | Prescaler Compare Register (PRSCM)                                               | . 246 |

| Figure 7-4:   | Prescaler Mode Register                                                          | . 246 |

| Figure 7-5:   | Example Watch Timer and Interval Timer simultaneously                            | . 250 |

| Figure 8-1:   | Block Diagram of Watchdog Timer                                                  | . 251 |

| Figure 8-2:   | Watchdog Timer Clock Selection Register (WDCS)                                   | . 253 |

| Figure 8-3:   | Watchdog Timer Mode Register (WDTM)                                              | . 254 |

| Figure 9-1:   | Asynchronous Serial Interfaces 50, 51 Block Diagram                              | . 260 |

| Figure 9-2:   | Asynchronous Serial Interface Mode Registers 0, 1 (ASIM50, ASIM51) (1/3)         | . 261 |

| Figure 9-3:   | Asynchronous Serial Interface Status Registers 0, 1 (ASIS50, ASIS51)             |       |

| Figure 9-4:   | Asynchronous Serial Interface Transmit Status Registers 0, 1 (ASIF50, ASIF51)    |       |

| Figure 9-5:   | Reception Buffer Registers 0, 1 (RXB50, RXB51)                                   |       |

| Figure 9-6:   | Transmission Buffer Registers 0, 1 (TXB50, TXB51)                                |       |

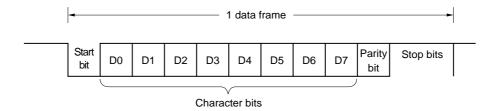

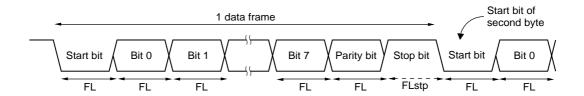

| Figure 9-7:   | Asynchronous Serial Interface Transmit/Receive Data Format                       |       |

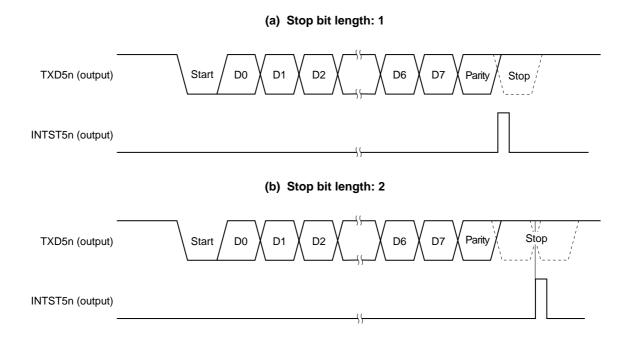

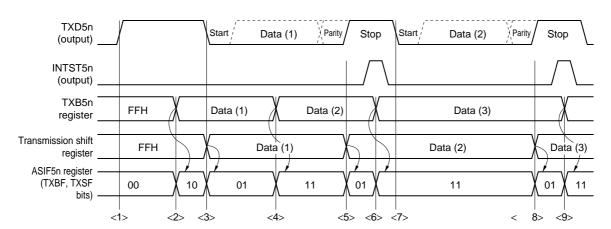

| Figure 9-8:   | Asynchronous Serial Interface Transmission Completion Interrupt Timing (n = 0, 1 |       |

| Figure 9-9:   | Continuous Transmission Starting Procedure                                       |       |

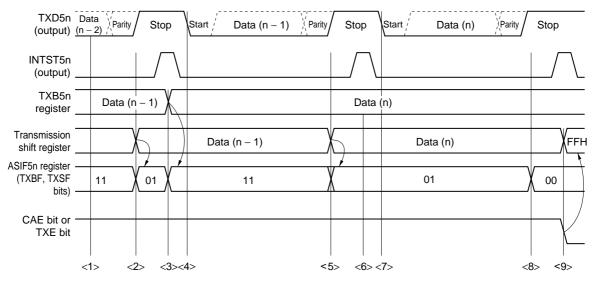

| Figure 9-10:  | Continuous Transmission End Procedure                                            |       |

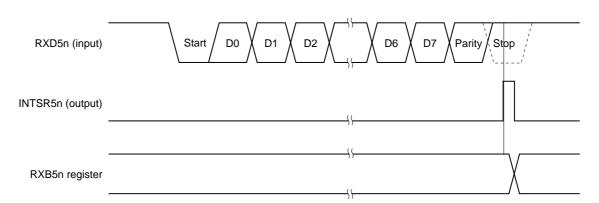

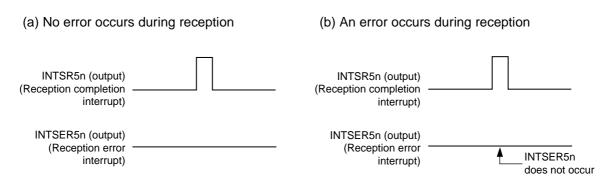

| Figure 9-11:  | Asynchronous Serial Interface Reception Completion Interrupt Timing              |       |

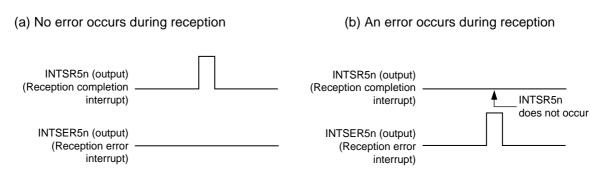

| Figure 9-12:  | When Reception Error Interrupt Is Separated from INTSR5n Interrupt               |       |

|               | (ISRM Bit = 0)                                                                   |       |

| Figure 9-13:  | When Reception Error Interrupt Is Included in INTSR5n Interrupt (ISRM Bit = 1)   |       |

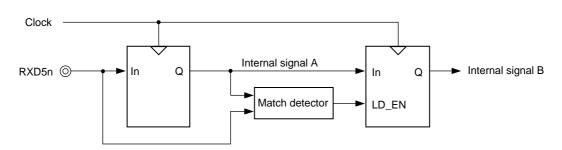

| Figure 9-14:  | Noise Filter Circuit                                                             |       |

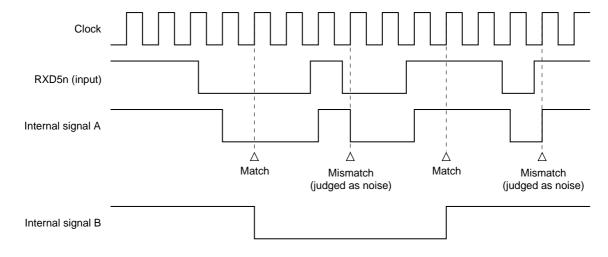

| Figure 9-15:  | Timing of RXD5n Signal Judged as Noise                                           |       |

| Figure 9-16:  | Baud Rate Generator (BRG) Configuration of UART5n (n = 0, 1)                     | . 278 |

| Figure 9-17:  | Clock Select Registers 0, 1 (CHKSR0 to CHKSR1)                                   | . 279 |

| Figure 9-18:  | Baud Rate Generator Control Registers 0, 1 (BRGC50, BRGC51)                      | . 280 |

| Figure 9-19:  | Allowable Baud Rate Range During Reception                                       | . 283 |

| Figure 9-20:  | Transfer Rate During Continuous Transmission                                     |       |

| Figure 9-21:  | Block Diagram of Clocked Serial Interfaces                                       | . 288 |

| Figure 9-22:  | Clocked Serial Interface Mode Registers (CSIM00, CSIM01, CSIM02) (1/2)           | . 289 |

| Figure 9-23:  | Clocked Serial Interface Clock Selection Registers (CSICK00 to CSICK02) (1/2)    | . 291 |

| Figure 9-24:  | Clocked Serial Interface Reception Buffer Registers (SIRB00 to SIRB02)           | . 293 |

| Figure 9-25:  | Clocked Serial Interface Reception Buffer Registers (SIRBL00 to SIRBL02)         | 294   |

| Figure 9-26:  | Clocked Serial Interface Transmission Buffer Registers 0, 1, 2 (SOTB0n)          | . 295 |

| Figure 9-27:  | Clocked Serial Interface Transmission Buffer Registers (SOTBL0n)                 | . 296 |

| Figure 9-28:  | Clocked Serial Interface Initial Transmission Buffer Registers 0, 1, 2 (SOTBF0n) | 297   |

| Figure 9-29:  | Clocked Serial Interface Initial Transmission Buffer Registers (SOTBFL0n)        | . 298 |

| Figure 9-30:  | Serial I/O Shift Registers 0, 1, 2 (SIO0n)                                       | . 299 |

| Figure 9-31:  | Serial I/O Shift Registers L00, L01, L02 (SIOL0n)                                | . 300 |

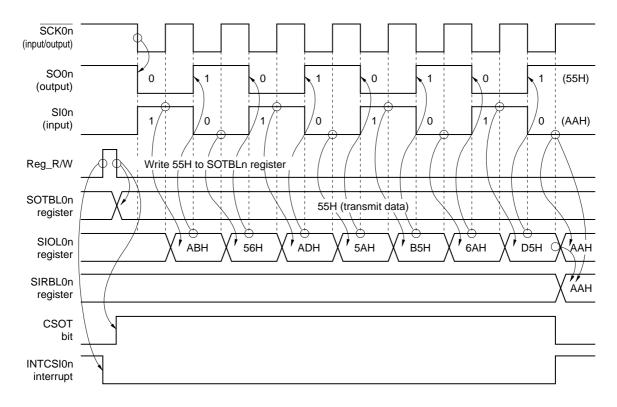

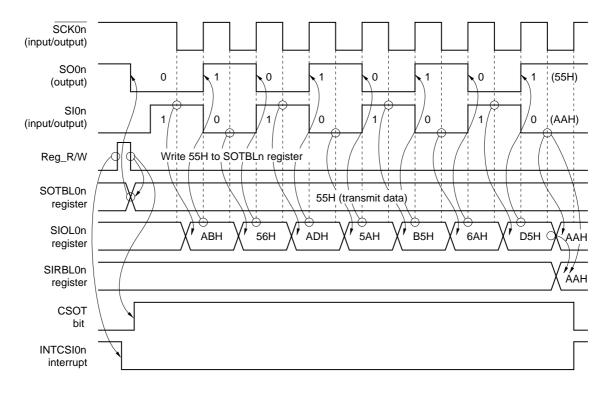

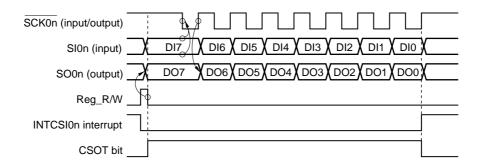

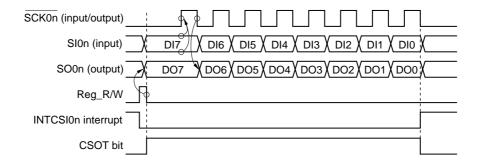

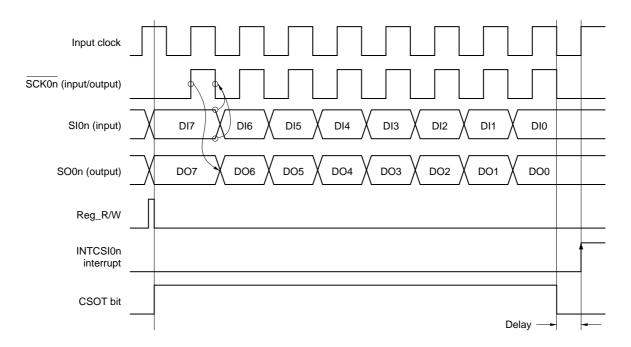

| Figure 9-32:  | Timing Chart in Single Transfer Mode (DAP = 0) (1/2)                             | . 302 |

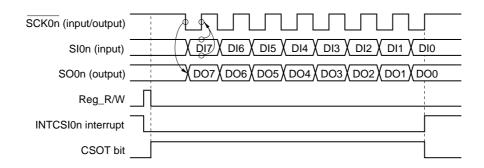

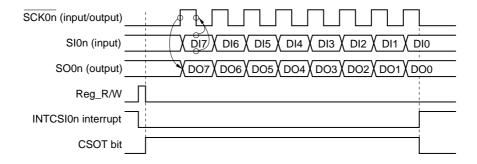

| Figure 9-33:  | Timing Chart According to Clock Phase Selection (1/2)                            |       |

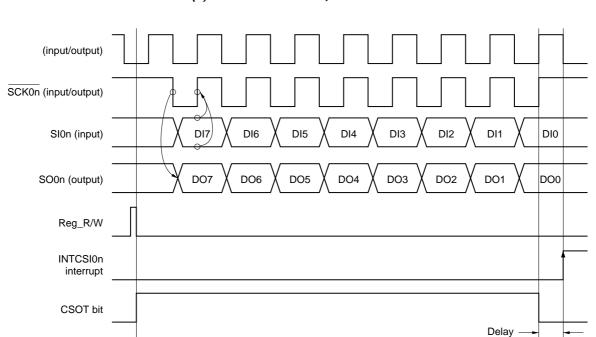

| Figure 9-34:  | Timing Chart of Interrupt Request Signal Output in Delay Mode (1/2)              | . 306 |

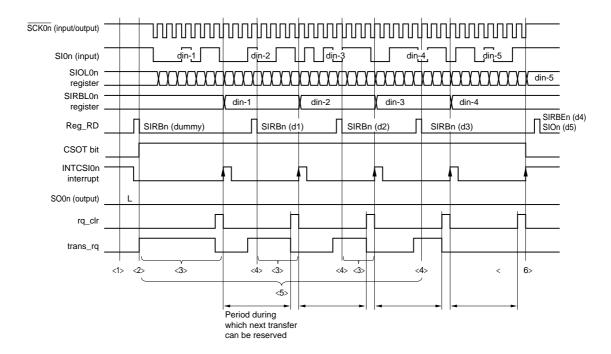

| Figure 9-35:  | Repeat Transfer (Receive-Only) Timing Chart                                      |       |

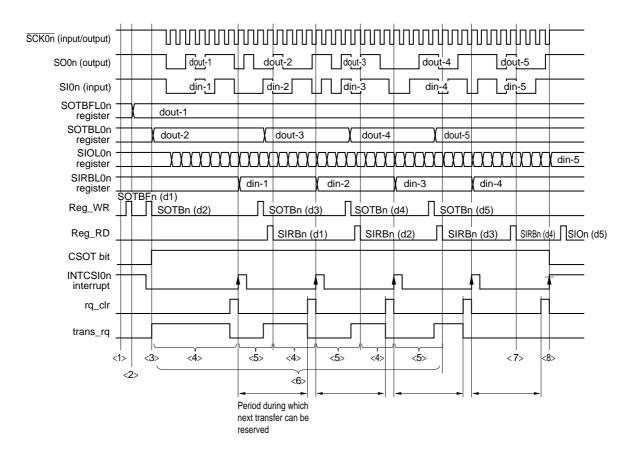

| Figure 9-36:  | Repeat Transfer (Transmission/Reception) Timing Chart                            |       |

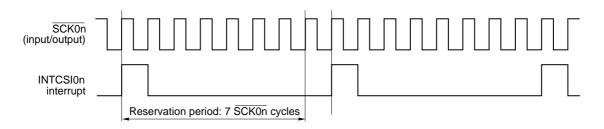

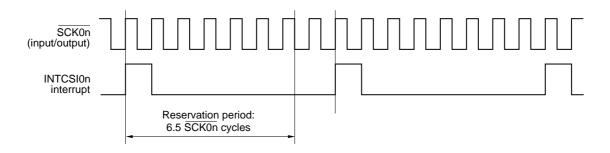

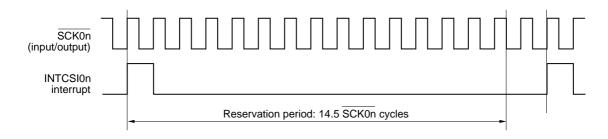

| Figure 9-37:  | Timing Chart of Next Transfer Reservation Period                                 |       |

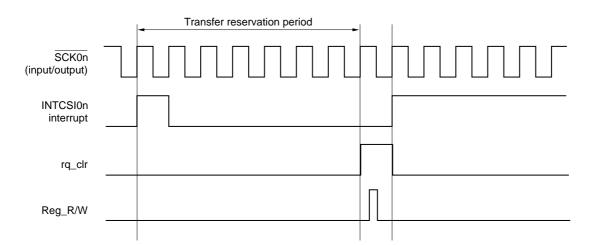

| Figure 9-38:  | Transfer Request Clear and Register Access Contention                            |       |

| Figure 9-39:  | Interrupt Request and Register Access Contention                                 |       |

| Figure 10-1:  | Structural Block Diagram                                                         |       |

| Figure 10-2:  | DCAN Memory                                                                      |       |

| Figure 10-3:  | Connection to the CAN Bus                                                        |       |

| Figure 10-4:  | Transmit Message Definition register (TCON)                                      |       |

| Figure 10-5:  | Transmit Identifier register (IDTXn) (n = 0 to 4)                                |       |

| Figure 10-6:  | Transmit Data                                                                    |       |

| Figure 10-7:  | Control Bits for Receive Identifier register (IDCON)                             |       |

| Figure 10-8:  | Control Bits for Receive Identifier register (IDCON)                             |       |

| Figure 10-9:  | Receive Status Bits register (DSTAT) (1/2)                                       |       |

| Figure 10-10: | Receive Identifier                                                               |       |

| Figure 10-11: | Receive Data                                                             | 334 |

|---------------|--------------------------------------------------------------------------|-----|

| Figure 10-12: | Identifier Compare with Mask                                             | 336 |

| Figure 10-13: | Control Bits for Mask Identifier                                         | 337 |

| Figure 10-14: | Mask Identifier register (MRESC0) (n = 0 to 4)                           | 338 |

| Figure 10-15: | DCAN Control Register (DCANCn) (n = 0, 1)                                | 339 |

| Figure 10-16: | CAN Control Register (CANCn) (n = 0, 1) (1/2)                            | 340 |

| Figure 10-17: | DCAN Time Stamp Support                                                  |     |

| Figure 10-18: | Time Stamp Function                                                      |     |

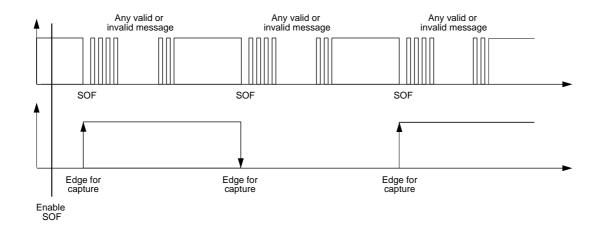

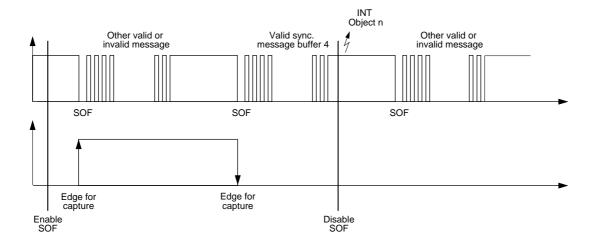

| Figure 10-19: | SOFOUT Toggle Function                                                   |     |

| Figure 10-20: | Global Time System Function                                              |     |

| Figure 10-21: | Transmission/Reception Flag                                              |     |

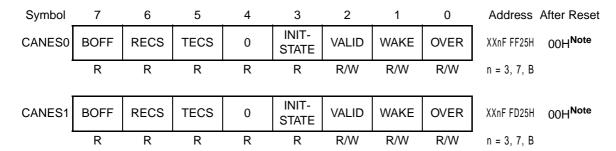

| Figure 10-22: | DCAN Error Status Register (CANESn) (n = 0, 1) (1/3)                     |     |

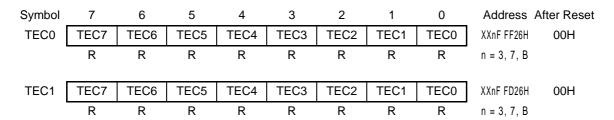

| Figure 10-23: | Transmit Error Counter register (TECn) (n = 0, 1)                        |     |

| Figure 10-24: | Receive Error Counter Register (RECn) (n = 0, 1)                         |     |

| Figure 10-25: | Message Count Register (MCNTn) (n = 0, 1)                                |     |

| Figure 10-26: | Bit Rate Prescaler Register (BRPRSn) (n = 0, 1) (1/2)                    |     |

| Figure 10-27: | Synchronization Control Register 0 (SYNC0n) (n = 3, 7, B)                |     |

| Figure 10-28: | Synchronization Control Register 1 (SYNC1n) (n = 3, 7, B)                |     |

| Figure 10-29: | Transmit Control Register (TCRn) (n = 0, 1) (1/3)                        |     |

| Figure 10-30: | Receive Message Register (RMESn) (n = 0, 1)                              |     |

| Figure 10-31: | Mask Control Register (MASKCn) (n = 0, 1)                                |     |

| Figure 10-32: | Redefinition Control Register (REDEFn) (n = 0, 1) (1/2)                  |     |

| Figure 10-33: | Data Wait Control Register (DWC)                                         |     |

| Figure 10-34: | Initialization Flow Chart                                                |     |

| Figure 10-35: | Transmit Preparation                                                     |     |

| Figure 10-36: | Transmit Abort                                                           |     |

| Figure 10-37: | Handling of Semaphore Bits by DCAN-Module                                |     |

| Figure 10-38: | Receive with Interrupt in case of Data New Flag behavior                 |     |

| Figure 10-39: | Receive, Software Polling in case of Data New Flag behavior              |     |

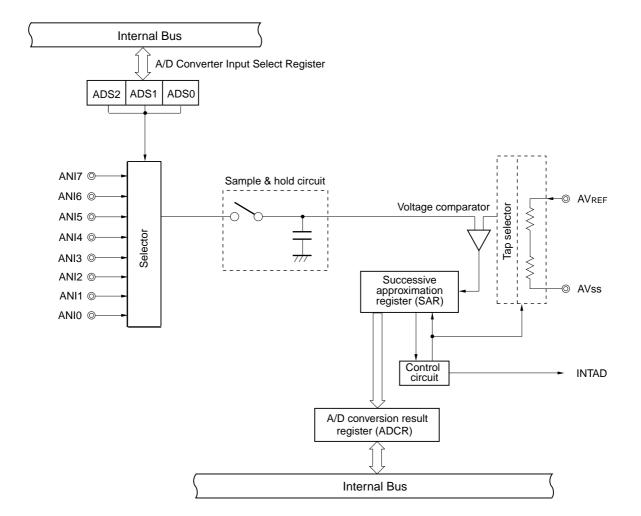

| Figure 11-1:  | A/D Converter Block Diagram                                              |     |

| Figure 11-2:  | Power-Fail Detection Function Block Diagram                              |     |

| Figure 11-3:  | A/D Converter Mode Register (ADM) Format                                 |     |

| Figure 11-4:  | Analog Input Channel Specification Register (ADS) Format                 |     |

| Figure 11-5:  | Power-Fail Compare Mode Register (PFM) Format                            |     |

| Figure 11-6:  | Power-fail compare threshold value register (PFT)                        |     |

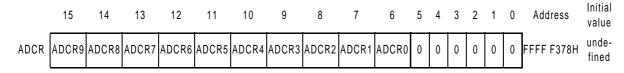

| Figure 11-7:  | A/D Conversion Result Registers (ADCR)                                   |     |

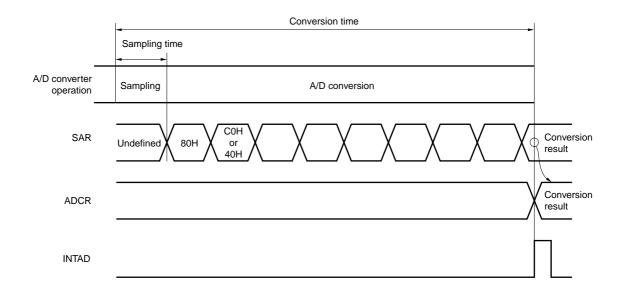

| Figure 11-8:  | Basic Operation of 10-bit A/D Converter                                  |     |

| Figure 11-9:  | Relation between Analog Input Voltage and A/D Conversion Result          |     |

| Figure 11-10: | A/D Conversion                                                           |     |

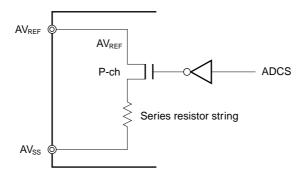

| Figure 11-11: | Example Method of Reducing Current Consumption in Standby Mode           |     |

| Figure 11-12: | Analog Input Pin Handling                                                |     |

| Figure 11-13: | A/D Conversion End Interrupt Request Generation Timing                   |     |

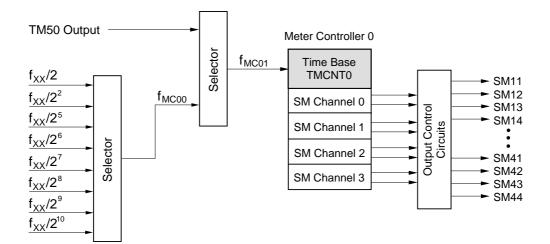

| Figure 12-1:  | Meter Controller/Driver 0 Block Diagram                                  |     |

| Figure 12-2:  | Meter Controller/Driver 1 Block Diagram                                  |     |

| Figure 12-3:  | 1-bit Addition Circuit Block Diagram                                     |     |

| Figure 12-4:  | Timer Mode Control Register (MCNTC0, MCNTC1) Format (1/2)                |     |

| Figure 12-5:  | Compare Control Register (MCMPCn) Format (1/2)                           |     |

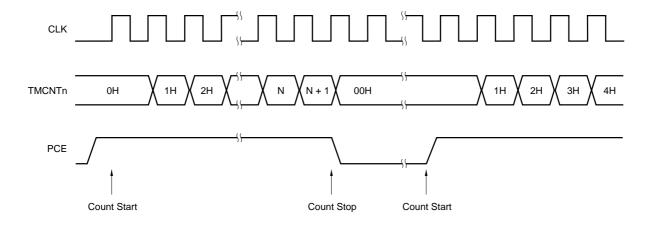

| Figure 12-6:  | Restart Timing after Count Stop (Count Start → Count Stop → Count Start) |     |

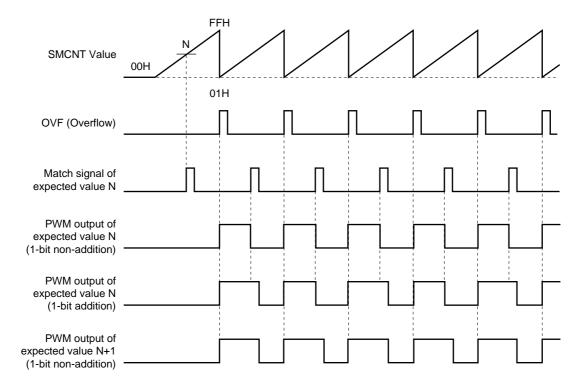

| Figure 12-7:  | Timing in 1-bit Addition Circuit Operation                               |     |

| Figure 12-8:  | Timing of Output with 1 Clock Shifted                                    |     |

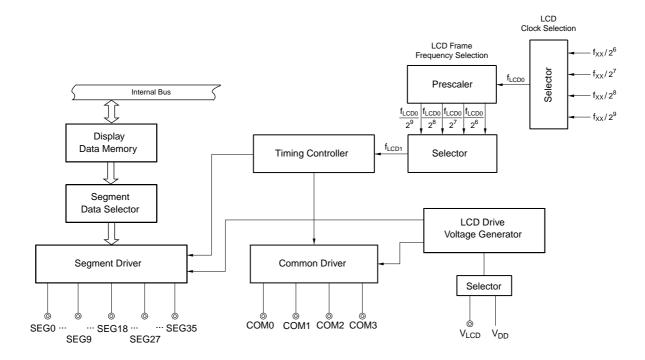

| Figure 13-1:  | LCD Controller/Driver Block Diagram                                      |     |

| Figure 13-2:  | LCD Display Mode Register Format                                         |     |

| Figure 13-3:  | LCD Display Clock Control Register (LCDC)                                |     |

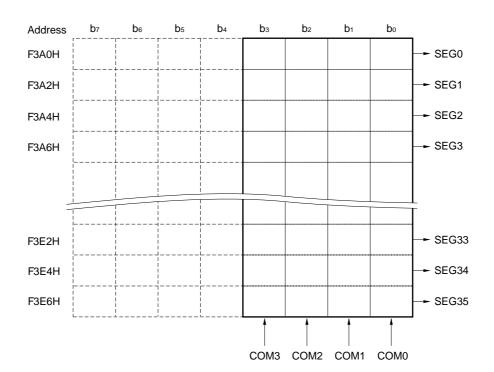

| Figure 13-4:  | Relationship between LCD Display Data Memory Contents                    |     |

| _             | and Segment/Common Outputs                                               | 413 |

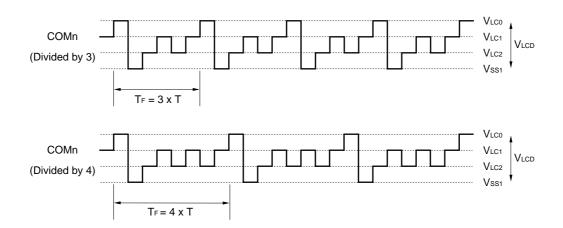

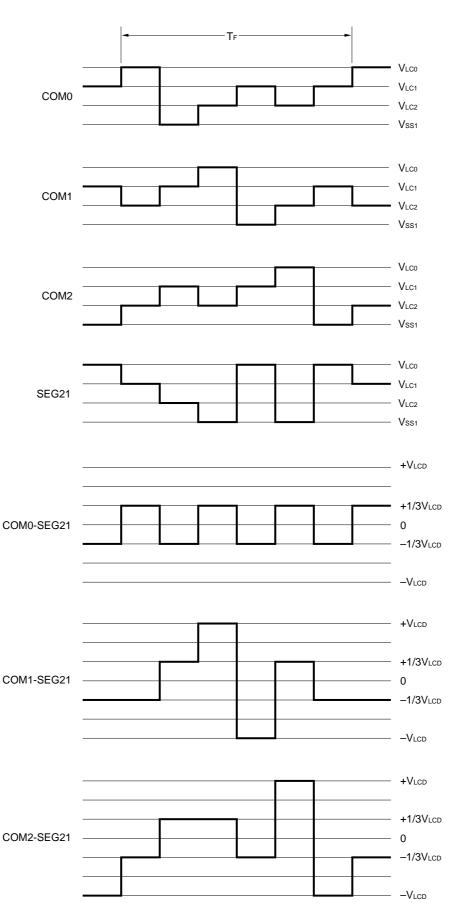

| Figure 13-5:  | Common Signal Waveform 1/3 bias method                                   |     |

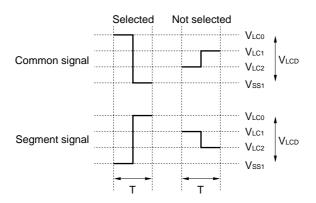

| Figure 13-6:  | Common Signal and Static Signal Voltages and Phases 1/3 bias method      |     |

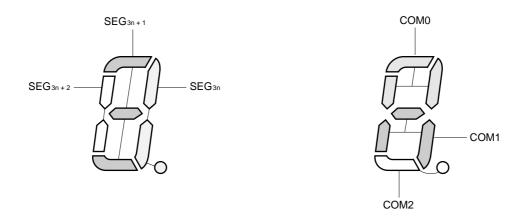

| Figure 13-7:  | 3-Time-Division LCD Display Pattern and Electrode Connections            |     |

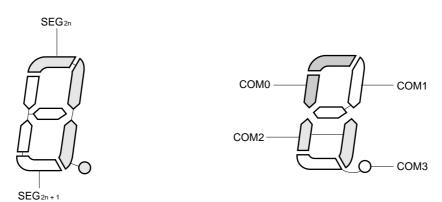

| Figure 13-8:                | 3-Time-Division LCD Panel Connection Example                  |     |

|-----------------------------|---------------------------------------------------------------|-----|

| Figure 13-9:                | 3-Time-Division LCD Drive Waveform Examples (1/3 Bias Method) |     |

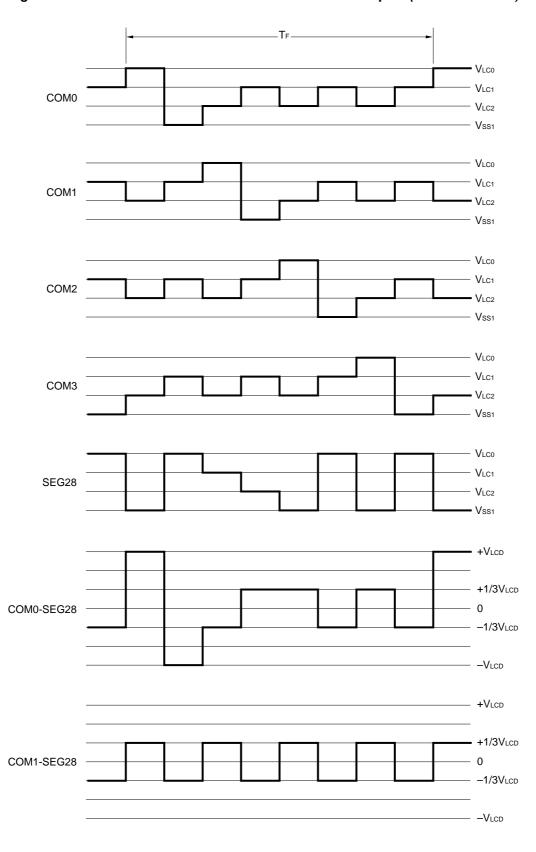

| Figure 13-10:               | 4-Time-Division LCD Display Pattern and Electrode Connections |     |

| Figure 13-11:               | 4-Time-Division LCD Panel Connection Example                  |     |

| Figure 13-12:               | 4-Time-Division LCD Drive Waveform Examples (1/3 Bias Method) |     |

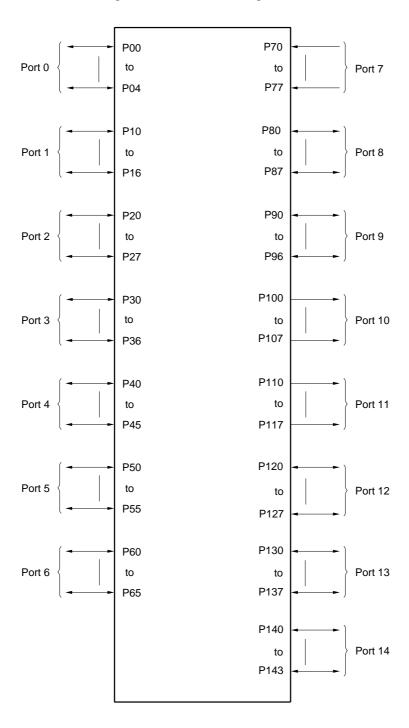

| Figure 14-1:                | Port Configuration                                            |     |

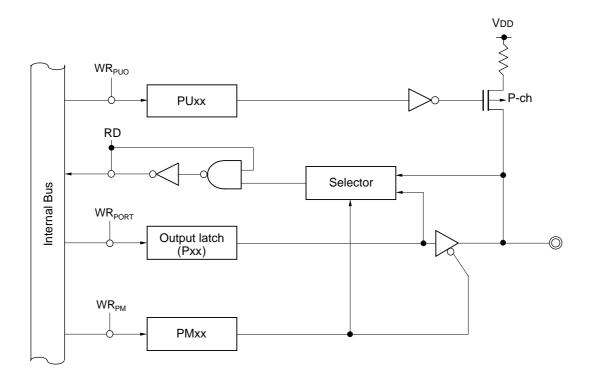

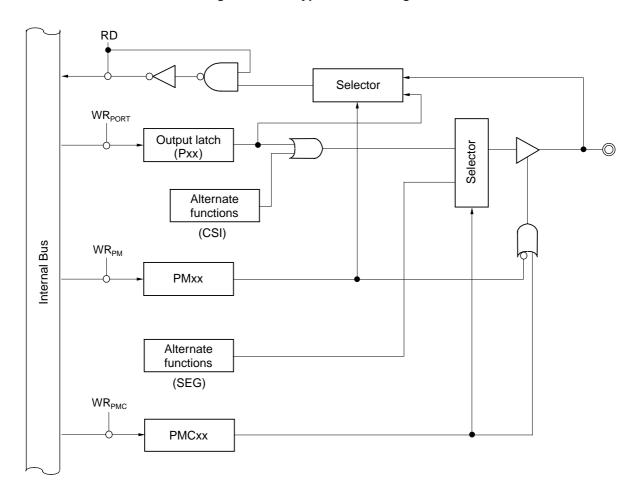

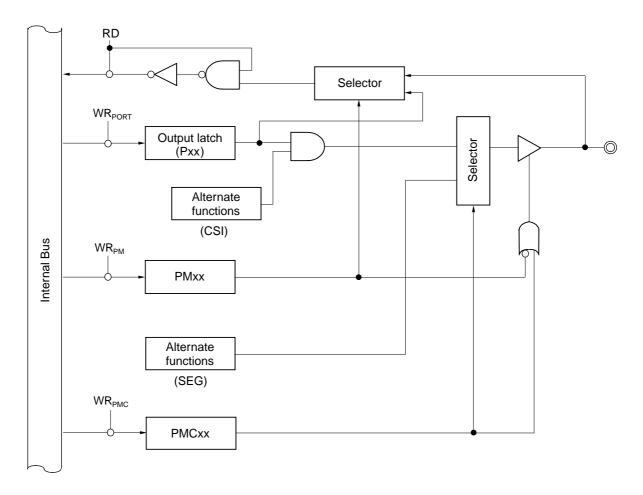

| Figure 14-2:                | Type A Block Diagram                                          |     |

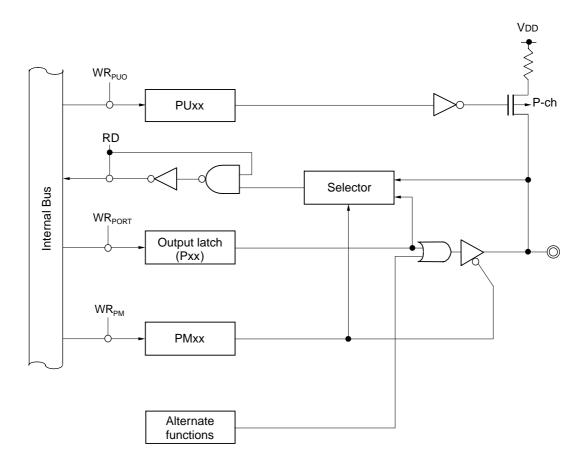

| Figure 14-3:                | Type B Block Diagram                                          |     |

| Figure 14-4:                | Type C Block Diagram                                          |     |

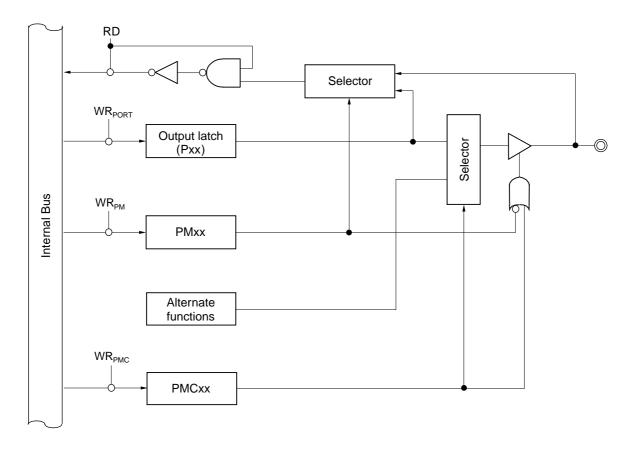

| Figure 14-5:                | Type D Block Diagram                                          |     |

| Figure 14-6:                | Type E Block Diagram                                          |     |

| Figure 14-7:                | Type F Block Diagram                                          |     |

| Figure 14-8:                | Type G Block Diagram                                          |     |

| Figure 14-9:                | Type H Block Diagram                                          |     |

| Figure 14-10:               | Type I Block Diagram                                          |     |

| Figure 14-11:               | Port 0 (P0)                                                   |     |

| Figure 14-12:               | Port 0 Mode Register (PM0)                                    |     |

| Figure 14-13:               | Port 0 Pull-up Resistor Option register (PU0)                 |     |

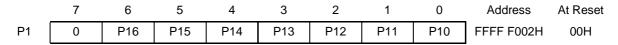

| Figure 14-14:               | Port 1 (P1)                                                   |     |

| Figure 14-15:               | Port 1 Mode Register (PM1)                                    |     |

| Figure 14-16:               | Port 1 Pull-up Resistor Option register (PU1)                 |     |

| Figure 14-17:               | Port 2 (P2)                                                   |     |

| Figure 14-18:               | Port 2 Mode Register (PM2)                                    |     |

| Figure 14-19: Figure 14-20: | Port 2 Pull-up Resistor Option register (PU2) Port 3 (P3)     |     |

| Figure 14-20.               | Port 3 Mode Register (PM3)                                    |     |

| Figure 14-21.               | Port 3 Pull-up Resistor Option register (PU3)                 |     |

| Figure 14-22:               | Port 4 (P4)                                                   |     |

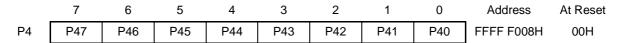

| Figure 14-24:               | Port 4 Mode Register (PM4)                                    |     |

| Figure 14-25:               | Port 4 Mode Control Register (PMC4)                           |     |

| Figure 14-26:               | Port 5 (P5)                                                   |     |

| Figure 14-27:               | Port 5 Mode Register (PM5)                                    |     |

| Figure 14-28:               | Port 5 Mode Control Register (PMC5)                           |     |

| Figure 14-29:               | Port 6 (P6)                                                   |     |

| Figure 14-30:               | Port 6 Mode Register (PM6)                                    |     |

| Figure 14-31:               | Port 6 Mode Control Register (PMC6)                           |     |

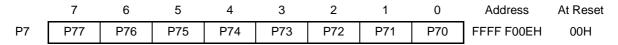

| Figure 14-32:               | Port 7 (P7)                                                   |     |

| Figure 14-33:               |                                                               | 456 |

| Figure 14-34:               | Port 8 Mode Register (PM8)                                    |     |

| Figure 14-35:               | Port 8 Pull-up Resistor Option register (PU8)                 |     |

| Figure 14-36:               | Port 9 (P9)                                                   |     |

| Figure 14-37:               | Port 9 Mode Register (PM9)                                    | 459 |

| Figure 14-38:               | Port 9 Mode Control Register (PMC9)                           | 459 |

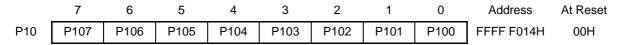

| Figure 14-39:               | Port 10 (P10)                                                 |     |

| Figure 14-40:               | Port 10 Mode Register (PM10)                                  |     |

| Figure 14-41:               | Port 10 Mode Control Register (PMC10)                         | 462 |

| Figure 14-42:               | Port 11 (P11)                                                 |     |

| Figure 14-43:               | Port 11 Mode Register (PM11)                                  |     |

| Figure 14-44:               | Port 11 Mode Control Register (PMC11)                         | 465 |

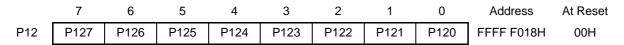

| Figure 14-45:               | Port 12 (P12)                                                 |     |

| Figure 14-46:               | Port 12 Mode Register (PM12)                                  | 467 |

| Figure 14-47:               | Port 12 Mode Control Register (PMC12)                         |     |

| Figure 14-48:               | Port 13 (P13)                                                 |     |

| Figure 14-49:               | Port 13 Mode Register (PM13)                                  |     |

| Figure 14-50:               | Port 13 Mode Control Register (PMC13)                         |     |

| Figure 14-51:               | Port 14 (P14)                                                 |     |

| Figure 14-52:               | Port 14 Mode Register (PM14)                                  |     |

| Figure 14-53:               | Port 14 Mode Control Register (PMC14)                         | 473 |

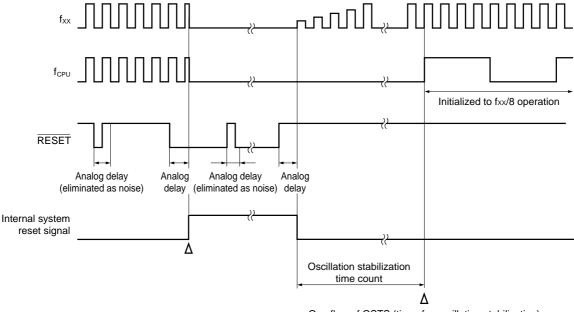

| Figure 15-1:  | Reset signal acknowledgment                                                  | 475 |

|---------------|------------------------------------------------------------------------------|-----|

| Figure 15-2:  | Reset at power-on                                                            |     |

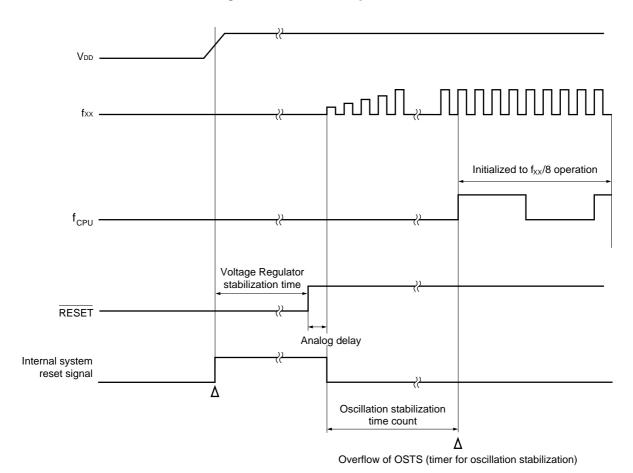

| Figure 16-1:  | Regulator                                                                    |     |

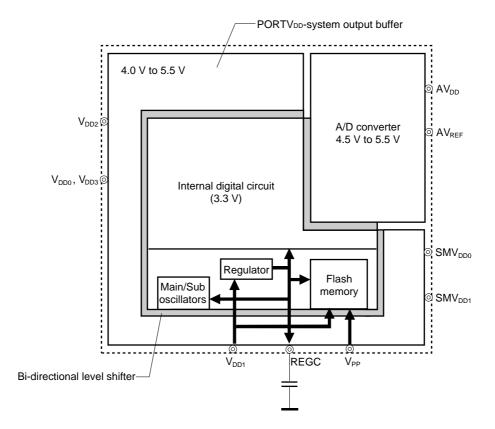

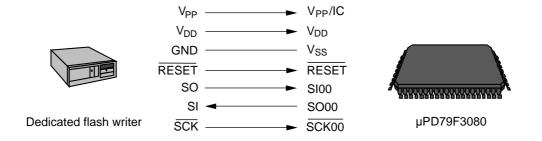

| Figure 17-1:  | Programming Environment in Conjunction with External Flash Writer            |     |

| Figure 17-2:  | Flash Writer Communication via CSI00                                         | 483 |

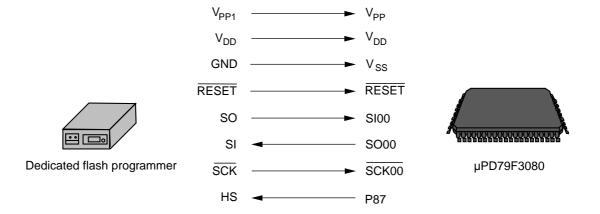

| Figure 17-3:  | Handshake-Supported CSI Communication                                        | 483 |

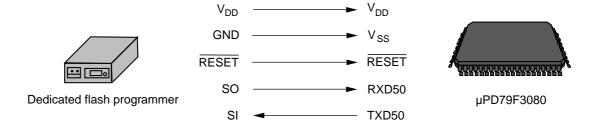

| Figure 17-4:  | Flash Writer Communication via UART50                                        | 484 |

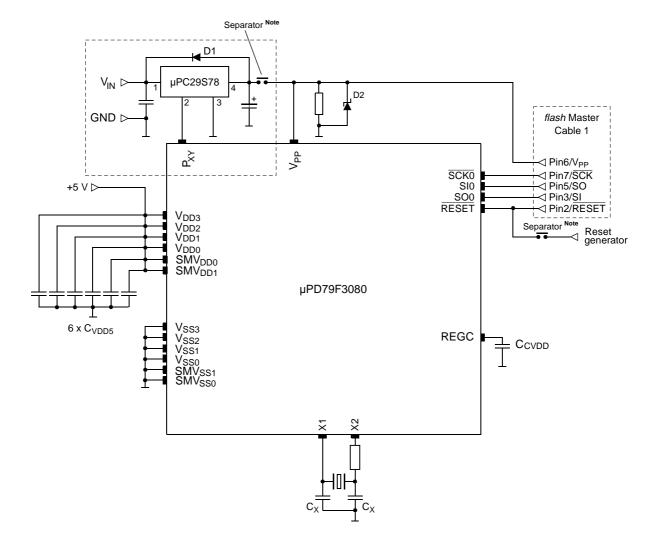

| Figure 17-5:  | Minimal Circuitry for Flash Selfprogramming via CSI00                        | 485 |

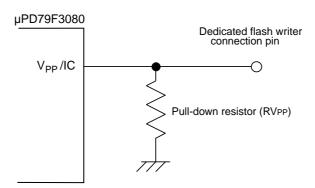

| Figure 17-6:  | Pin Handling of V <sub>PP</sub> pin                                          | 486 |

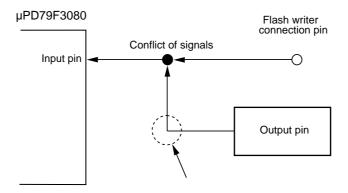

| Figure 17-7:  | Conflict between Flash Writer and Other Output Pin                           | 487 |

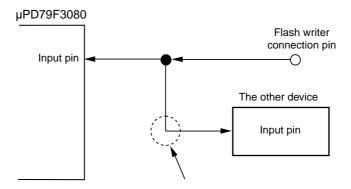

| Figure 17-8:  | Malfunction of Other Input Pins                                              | 488 |

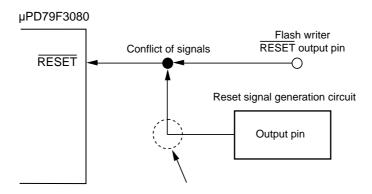

| Figure 17-9:  | Conflict between Flash Writer Reset Line and Reset Signal Generation Circuit | 489 |

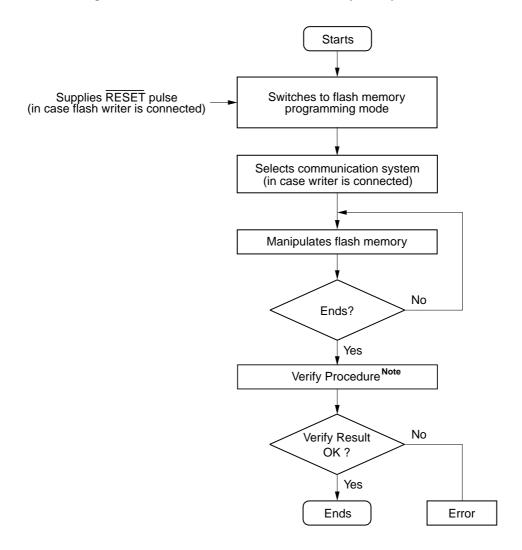

| Figure 17-10: | Flow Chart of Flash Memory Manipulation                                      | 490 |

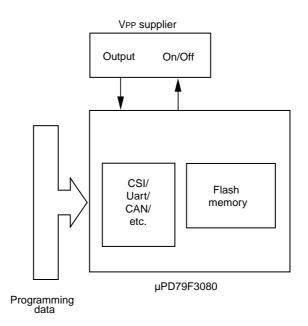

| Figure 17-11: | Configuration in Selfprogramming Mode                                        | 492 |

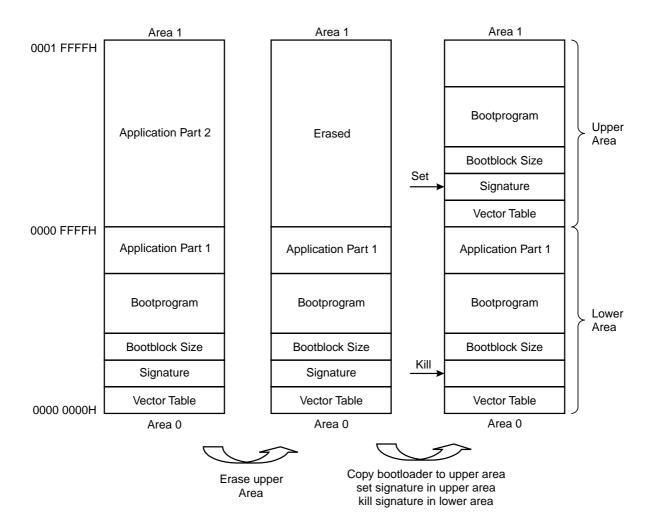

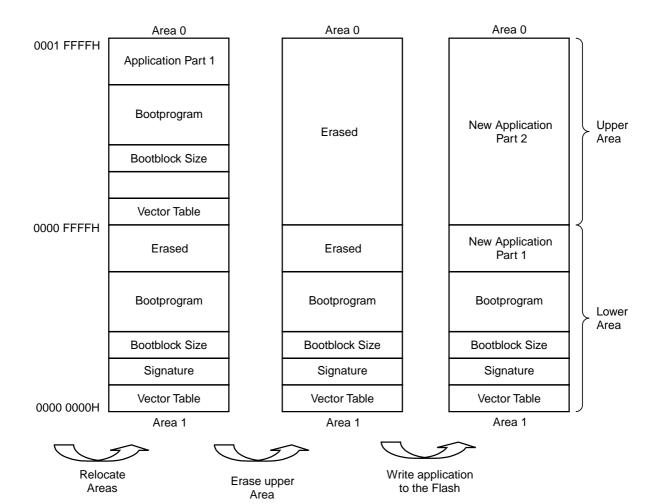

| Figure 17-12: | Secure Selfprogramming Flow (1/2)                                            | 494 |

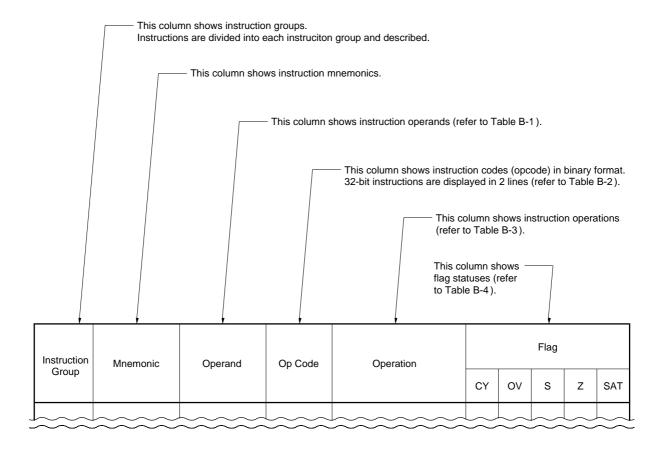

| Figure A-1:   | How to Read Instruction Set List                                             |     |

# **List of Tables**

| Table 2-1:  | Port pins                                                                       |     |

|-------------|---------------------------------------------------------------------------------|-----|

| Table 2-2:  | Non-port pins                                                                   |     |

| Table 2-3:  | Pin related to V850/DB1 status                                                  |     |

| Table 2-4:  | Types of Pin I/O Circuit and Connection of Unused Pin                           | 55  |

| Table 3-1:  | Program Registers                                                               |     |

| Table 3-2:  | System Register Numbers                                                         | 64  |

| Table 3-3:  | Interrupt/Exception Table                                                       | 72  |

| Table 3-4:  | Peripheral I/O Registers                                                        |     |

| Table 3-5:  | Non-Peripheral I/O Registers for DCAN1 Note 2                                   | 86  |

| Table 3-6:  | Non-Peripheral I/O Registers for DCAN0                                          | 96  |

| Table 4-1:  | Interrupt/Exception Sources                                                     | 110 |

| Table 4-2:  | Address and bit of each Interrupt Control Register                              | 127 |

| Table 4-3:  | Priorities of Interrupts and Exceptions                                         | 138 |

| Table 4-4:  | Interrupt Response Time                                                         | 140 |

| Table 5-1:  | Power Saving Modes Overview                                                     | 148 |

| Table 5-2:  | Operating States in Power Save Functions Mode                                   | 151 |

| Table 5-3:  | Operating States in HALT mode                                                   |     |

| Table 5-4:  | Operation after HALT mode release by interrupt request                          | 153 |

| Table 5-5:  | Operating States in WATCH Mode                                                  |     |

| Table 5-6:  | Operation after WATCH mode release by interrupt request                         |     |

| Table 5-7:  | Operating States in STOP Mode                                                   |     |

| Table 6-1:  | Timer G Configuration List                                                      |     |

| Table 6-2:  | Timer C Configuration List                                                      |     |

| Table 6-3:  | TOCn Output Control                                                             |     |

| Table 6-4:  | Timers 5n Configuration                                                         |     |

| Table 7-1:  | Configuration of Watch Timer                                                    |     |

| Table 7-2:  | Watch Timer (INTWT) Interval Times                                              |     |

| Table 7-3:  | Interval Timer (INTWTI) Interval Times                                          |     |

| Table 8-1:  | Watchdog Timer Configuration                                                    |     |

| Table 9-1:  | Generated Interrupts and Default Priorities                                     |     |

| Table 9-2:  | Transmission Status and Whether or Not Writing Is Enabled                       |     |

| Table 9-3:  | Reception Error Causes                                                          |     |

| Table 9-4:  | Baud Rate Generator Setting Data                                                |     |

| Table 9-5:  | Maximum and Minimum Allowable Baud Rate Error                                   |     |

| Table 10-1: | Mask Function                                                                   |     |

| Table 10-2: | Possible Reactions of the DCAN                                                  |     |

| Table 10-3: | Mask Operation Buffers                                                          |     |

| Table 10-4: | Interrupt Sources                                                               |     |

| Table 11-1: | A/D Converter Configuration                                                     |     |

| Table 11-2: | Register format of A/D Converter Control Register                               |     |

| Table 13-1: | Maximum Number of Display Pixels                                                |     |

| Table 13-2: | LCD Controller/Driver Configuration                                             |     |

| Table 13-3: | Frame Frequencies [Hz] (fx = 4 MHz)                                             |     |

| Table 13-4: | COM Signals                                                                     |     |

| Table 13-5: | LCD Drive Voltages 1/3 bias method                                              |     |

| Table 13-6: | Selection and Non-Selection Voltages (COM0 to COM2)                             |     |

| Table 13-7: | Selection and Non-Selection Voltages (COM0 to COM3)                             |     |