# **NEC Microcomputers, Inc.**

## **MULTI-PROTOCOL SERIAL CONTROLLER**

DESCRIPTION

The  $\mu$ PD7201 is a dual-channel multi-function peripheral controller designed to satisfy a wide variety of serial data communication requirements in microcomputer systems. Its basic function is a serial-to-parallel, parallel-to-serial converter/controller and within that role it is configurable by systems software so its "personality" can be optimized for a given serial data communications application.

The  $\mu$ PD7201 is capable of handling asynchronous and synchronous byte-oriented protocols such as IBM Bisync, and synchronous bit-oriented protocols such as HDLC and IBM SDLC. This versatile device can also be used to support virtually any other serial protocol for applications other than data communications.

The µPD7201 can generate and check CRC codes in any synchronous mode and can be programmed to check data integrity in various modes. The device also has facilities for modem controls in both channels. In applications where these controls are not needed, the modem controls can be used for general-purpose I/O.

#### **FEATURES**

•

- Two Fully Independent Duplex Serial Channels

- Four Independent DMA Channels for Send/Received Data for Both Serial Inputs/Outputs

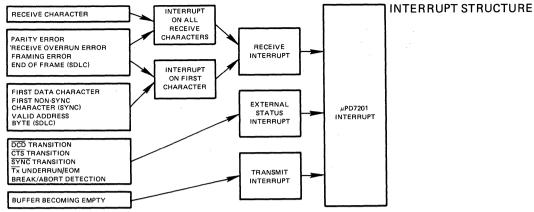

- Programmable Interrupt Vectors and Interrupt Priorities

- Modem Controls Signals .

- Variable, Software Programmable Data Rate, Up to 880K Baud at 3 MHz Clock

- Double Buffered Transmitter Data and Quadruply Buffered Received Data ٠ Programmable CRC Algorithm

- Selection of Interrupt, DMA or Polling Mode of Operation

- Asynchronous Operation: •

- .....

- Character Length: 5, 6, 7 or 8 Bits Stop Bits: 1, 1-1/2, 2 Transmission Speed: x1, x16, x32 or x64 Clock Frequency

- Parity: Odd, Even, or Disable \_

- Break Generation and Detection

- Interrupt on Parity, Overrun, or Framing Errors

- Monosync, Bisync, and External Sync Operations:

- Software Selectable Sync Characters

- Automatic Sync Insertion

- CRC Generation and Checking HDLC and SDLC Operations:

- - Abort Sequence Generation and Detection Automatic Zero Insertion and Detection

- Address Field Recognition CRC Generation and Checking

- I-Field Residue Handling

- N-Channel MOS Technology

- Single +5V Power Supply; Interface to Most Microprocessors Including 8080, 8085, 8086 .

- and Others.

- Single Phase TTL Clock

- Available in Plastic and Ceramic Dual-in-Line Packages

#### PIN CONFIGURATION

| CLK          | 1  | -0-  | 40 🛛 V <sub>CC</sub> |

|--------------|----|------|----------------------|

| RESET        | 2  |      | 39 CTSA              |

| DCDA         | 3  |      | 38 🗖 RTSA            |

| R×CB         | 4  |      | 37 🗖 TxDA            |

| DCDB         | 5  |      | 36 TxCA              |

| CTSB         | 6  |      | 35 RxCA              |

| TxCB         | 7  |      | 34 🗖 R×DA            |

| TxDB 🗖       | 8  |      | 33 SYNCA             |

| RxDB 🕻       | 9  | *    | 32 WAITA/DROR×A      |

| RTSB/SYNCB   | 10 | μPD  | 31 DTRA/HAO          |

| WAITB/DRQTxA | 11 | 7201 | 30 PRO/DRQT×B        |

| D7 🗖         | 12 |      | 29 🗖 PRI/DRQR×B      |

| D6 🗖         | 13 |      |                      |

| D5 🗖         | 14 |      | 27 🗖 INTA            |

| D4 🗖         | 15 |      | 26 DTRB/HAI          |

| D3 🗖         | 16 |      | 25 🗖 B/Ā             |

| D2 🗖         | 17 |      | 24 🗖 C/D             |

| D1 🖸         | 18 |      | 23 🗖 CS              |

| D0 🗖         | 19 |      | 22 🗖 RD              |

| ∨ss 🗖        | 20 |      | 21 🛛 WR              |

|              |    |      |                      |

# PIN DESCRIPTION

|       |                                | PIN                                                         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|--------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.   | SYMBOL                         | NAME                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12-19 | D <sub>0</sub> -D <sub>7</sub> | System Data Bus<br>(bidirectional,<br>3-state)              | The system data bus transfers data and commands between the processor and the $\mu\text{PD7201}$ . D_0 is the least significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25    | B/Ā                            | Channel A or B Select<br>(input, High selects<br>Channel B) | This input defines which channel is accessed during a data transfer between the processor and the $\mu PD7201$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24    | C/D                            | Control or Data Select<br>(input, High selects<br>Control)  | This input defines the type of information transfer performed between the processor and the $\mu$ PD7201. A High at this input during a processor write to or read from the $\mu$ PD7201 causes the information on the data bus to be interpreted as a command for the channel selected by B/Ā. A low at C/D means that the information on the data bus is data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 23    | CS                             | Chip Select (input,<br>active Low)                          | A low level at this input enables the $\mu$ PD7201 to accept command or data inputs from the processor during a write cycle, or to transmit data to the processor during a read cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1     | CLK                            | System Clock (input)                                        | The µPD7201 uses standard TTL clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22    | RD                             | Read (input active<br>Low)                                  | If $\overline{RD}$ is active, a memory or I/O read operation is in progress. $\overline{RD}$ is used with C/D, B/A and CS to transfer data from the $\mu$ PD7201 to the processor or the memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 21    | WR                             | Write (input, active<br>Low)                                | The $\overline{\text{WR}}$ signal is used to control the transfer of either command or data from the processor or the memory to the $\mu$ PD7201.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2     | RESET                          | Reset (input, active<br>Low)                                | A low $\overrightarrow{\text{RESET}}$ disables both receivers and transmitters, forces TxDA and TxDB marking, forces the modem controls high and disables all interrupts. The control registers must be rewritten after the $\mu$ PD7201 is reset and before data is transmitted or received. RESET must be active for a minimum of one complete CLK cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10,38 | RTSA, RTSB                     | Request to Send<br>(outputs, active Low)                    | When the $\overline{\text{RTS}}$ bit is set, the $\overline{\text{RTS}}$ output goes Low. When the $\overline{\text{RTS}}$ bit is reset in the Asynchronous mode, the output goes High after the transmitter is empty. In Synchronous modes, the $\overline{\text{RTS}}$ pin strictly follows the state of the $\overline{\text{RTS}}$ bit. Both pins can be used as general-purpose outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

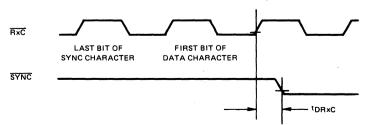

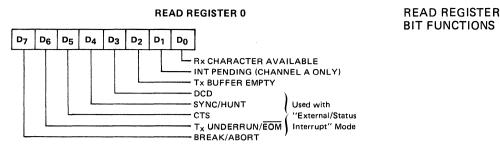

| 10,33 | SYNCA, SYNCB                   | Synchronization<br>(inputs/outputs, active<br>Low)          | These pins can act either as inputs or outputs. In the Asynchronous Receive mode, they are inputs similar to $\overline{CTS}$ and $\overline{DCD}$ . In this mode, the transitions on these lines affect the state of the Sync/Hunt status bits in Read Register 0. In the External Sync mode, these lines also act as inputs. When external synchronization is achieved, $\overline{SYNC}$ must be driven Low on the second rising edge of $\overline{RxC}$ after that rising edge of $\overline{RxC}$ on which the last bit of the sync character was received. In other words, after the sync pattern is detected, the external logic must wait for two full Receive Clock cycles to activate the $\overline{SYNC}$ input. Once $\overline{SYNC}$ is forced Low, it is wise to keep it Low until the processor informs the external sync logic that synchronization has been lost or a new message is about to start. Character assembly begins on the rising edge of $\overline{RxC}$ that immediately precedes the falling edge of $\overline{SYNC}$ in the External Sync mode. |

|       |                                |                                                             | In the Internal Synchronization mode (Monosync and Bisync), these pins act as outputs that are active during the part of the receive clock ( $RxC$ ) cycle in which sync characters are recognized. The sync condition is not latched, so these outputs are active each time a sync pattern is recognized, regardless of character boundaries.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 26,31 | DTRA, DTRB                     | Data Terminal Ready<br>(outputs, active Low)                | These outputs follow the state programmed into the DTR bit. They can also be programmed as general-purpose outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

.

## PIN DESCRIPTION (CONT.)

|                 | F                                | PIN                                                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|-----------------|----------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| NO.             | SYMBOL                           | NAME                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 27              | ĪNTĀ                             | Interrupt<br>Acknowledge (input,<br>active Low)              | This signal is generated by the processor and is sent to all peripheral devices. It serves to acknowledge the interrupt and to allow the highest priority interrupting device to put an 8-bit vector on the bus. INT and INTA are compatible with the fully nested option of the $\mu$ PD8259A-5.                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 29              | PRI                              | Priority In (input,<br>active Low)                           | These signals are daisy chained through the peripheral device controllers. The signal<br>on these lines is intact until a device with a pending interrupt request is found on<br>the chain. After that device, this signal holds off lower priority device interrupts.                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |

| 30              | PRO                              | Priority Out (output,<br>active Low)                         | A higher priority device can interrupt the processing of an interrupt from a lower priority device, provided the processor has interrupts enabled.                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |

|                 |                                  |                                                              | $\overline{\text{PRI}}$ is used with $\overline{\text{PRO}}$ to form a priority daisy chain when there is more than one interrupt-driven device. A Low on this line indicates that no other device of higher priority is being serviced by a processor interrupt service routine.                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|                 |                                  |                                                              | $\overrightarrow{PRO}$ is Low only if $\overrightarrow{PRI}$ is Low and the processor is not servicing an interrupt from the<br>$\mu$ PD7201. Thus, this signal blocks lower priority devices from interrupting while a<br>higher priority device is being serviced by its processor interrupt service routine.                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 11,29,<br>30,32 | DRQTxA, DRQTxB<br>DRQRxA, DRQRxB | DMA Request<br>(outputs, active High)                        | These signals are generated by the receiver or transmitter of Channel A and Channel B. These signals can be connected to an 8257 DMA Controller and are used for handshaking during DMA transfer.                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 26              | HAT                              | DMA Acknowledge<br>(input, active Low)                       | Typically, the HLDA signal driven from the processor is input to the $\overline{HAT}$ terminal of the highest priority µPD7201, and the $\overline{HAO}$ output of that µPD7201 is daisy chained to the $\overline{HAT}$ input of the lower priority µPD7201 and propagated down-                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| 31              | HAO                              | DMA Acknowledge<br>(output, active Low)                      | stream. HAT and HAO signals provide acknowledgement for the highest priority outstanding DMA request.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| 28              | INT                              | Interrupt Request<br>(output, open<br>collector, active Low) | When the $\mu PD7201$ is requesting an interrupt, it pulls $\overline{INT}$ low.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| 11,32           | WAITA, WAITB                     | (Outputs, open drain)                                        | Wait lines for both channels that synchronize the processor to the $\mu\text{PD7201}$ data rate. The reset state is open drain.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 6,39            | CTSA, CTSB                       | Clear to Send (inputs, active Low)                           | When programmed as Auto Enables, a Low on these inputs enables the respective transmitter. If not programmed as Auto Enables, these inputs may be programmed as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow-risetime inputs. The $\mu$ PD7201 detects pulses on these inputs and interrupts the processor on both logic level transitions. The Schmitt-trigger inputs do not guarantee a specified noise-level margin.                                          |  |  |  |  |  |  |  |  |  |

| 3,5             | DCDA, DCDB                       | Data Carrier Detect<br>(inputs, active Low)                  | These signals are similar to the $\overline{\text{CTS}}$ inputs, except they can be used as receiver enables.                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

| 9,34            | RxDA, RxDB                       | Receive Data (inputs, active High)                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 8,37            | TxDA, TxDB                       | Transmit Data<br>(outputs, active High)                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

| 4,35            | RxCA, RxCB                       | Receiver Clocks<br>(inputs)                                  | The Receiver Clocks may be 1, 16, 32, or 64 times the data rate in asynchronous modes. Receive data is sampled on the rising edge of $\overline{RxC}$ .                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| 7,36            | TxCA, TxCB                       | Transmitter Clocks<br>(inputs)                               | In asynchronous modes, the Transmitter Clocks may be 1, 16, 32, or 64 times the data rate. The multiplier for the transmitter and the receiver must be the same. Both $\overline{TxC}$ and $\overline{RxC}$ inputs are Schmitt-trigger buffered for relaxed rise- and fall-time requirements (no noise margin is specified). TxD changes on the falling edge of $\overline{TxC}$ . Note that $\overline{TxC}$ and $\overline{RxC}$ in Channel B are on a common pin, $\overline{RxCB}/\overline{TxCB}$ . |  |  |  |  |  |  |  |  |  |

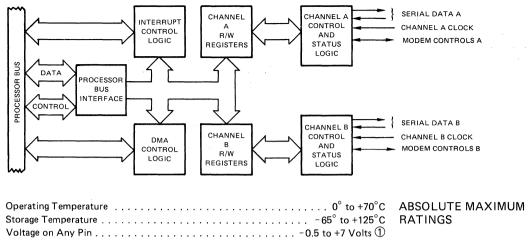

## **BLOCK DIAGRAM**

Note: 1) With respect to ground.

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## $T_a = 0^{\circ}C$ to +70°C; $V_{CC} = +5V \pm 10\%$

|                        | 0)/0000 | LI   | MITS                 |      | TEST                      |  |  |  |  |

|------------------------|---------|------|----------------------|------|---------------------------|--|--|--|--|

| PARAMETER              | SYMBOL  | MIN  | ΜΑΧ                  | UNIT | CONDITIONS                |  |  |  |  |

| Input Low Voltage      | VIL     | -0.5 | +0.8                 | V    |                           |  |  |  |  |

| Input High Voltage     | VIH     | +2.0 | V <sub>CC</sub> +0.5 | V    |                           |  |  |  |  |

| Output Low Voltage     | VOL     |      | +0.45                | V    | IOL = +2.0 mA             |  |  |  |  |

| Output High Voltage    | ∨он     | +2.4 |                      | V    | I <sub>OH</sub> = -200 μA |  |  |  |  |

| Input Leakage Current  | μL      |      | ±10                  | μA   | $V_{IN} = V_{CC}$ to $0V$ |  |  |  |  |

| Output Leakage Current | IOL     |      | ±10                  | μA   | VOUT = VCC to 0V          |  |  |  |  |

| VCC Supply Current     | Icc     |      | 180                  | mA   |                           |  |  |  |  |

DC CHARACTERISTICS

$T_a = 25^{\circ}C; V_{CC} = GND = 0V$

| PARAMETER                   | SYMBOL           | LIP | MITS | UNIT | TEST            |  |  |  |  |

|-----------------------------|------------------|-----|------|------|-----------------|--|--|--|--|

| FARAMETER                   | STIVIBUL         | MIN | MAX  |      | CONDITIONS      |  |  |  |  |

| Input Capacitance           | C <sub>IN</sub>  |     | 10   | pF   | fc = 1 MHz      |  |  |  |  |

| Output Capacitance          | COUT             |     | 15   | pF   | Unmeasured pins |  |  |  |  |

| Input/Output<br>Capacitance | C <sub>I/O</sub> |     | 20   | pF   | Returned to GND |  |  |  |  |

## CAPACITANCE

## AC CHARACTERISTICS $T_a = 0^{\circ}C$ to +70°C; $V_{CC} = +5V \pm 10\%$

| DADAA                            | 0.00                | LIN      | /ITS |      |  |

|----------------------------------|---------------------|----------|------|------|--|

| PARAMETER                        | SYMBOL              | MIN      | МАХ  | UNIT |  |

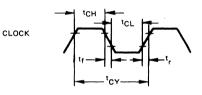

| Clock Cycle                      | tCY                 | 250      | 4000 | ns   |  |

| Clock High Width                 | tCH                 | 105      | 2000 | ns   |  |

| Clock Low Width                  | tCL                 | 105      | 2000 | ns   |  |

| Clock Rise and Fall Time         | t <sub>r</sub> , tf | 0        | 30   | ns   |  |

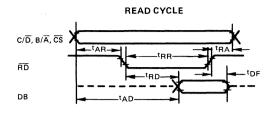

| Address Setup to RD              | tAR                 | 0        |      | ns   |  |

| Address Hold from RD             | <sup>t</sup> RA     | 0        |      | ns   |  |

| RD Pulse Width                   | tRR                 | 250      |      | ns   |  |

| Data Delay from Address          | tAD                 |          | 200  | ns   |  |

| Data Delay from RD               | tRD                 |          | 200  | ns   |  |

| Output Float Delay               | tDF                 | 10       | 100  | ns   |  |

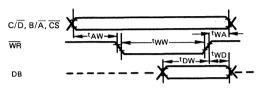

| Address Setup to WR              | tAW                 | 0        |      | ns   |  |

| Address Hold from WR             | twA                 | 0        |      | ns   |  |

| WR Pulse Width                   | tww                 | 250      |      | ns   |  |

| Data Setup to WR                 | tDW                 |          | 150  | ns   |  |

| Data Hold from WR                | twp                 | 0        |      | ns   |  |

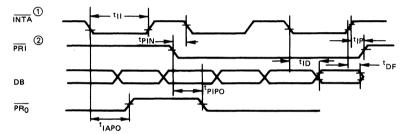

| PRO Delay from INTA              | tiapo               | <u> </u> | 200  | ns   |  |

| PRI Setup to INTA                | tPIN                | 0        |      | ns   |  |

| PRI Hold from INTA               | tip                 | 0        |      | ns   |  |

| INTA Pulse Width                 | til                 | 250      |      | ns   |  |

| PRO Delay from PRI               | tPIPO               |          | 100  | ns   |  |

| Data Delay from INTA             | tID                 |          | 200  | ns   |  |

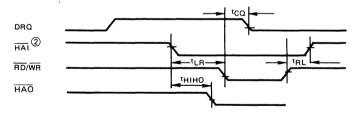

| Request Hold from RD/WR          | tCO                 |          | 150  | ns   |  |

| HAI Setup to RD/WR               | tLR                 | 300      |      | ns   |  |

| HAI Hold from RD/WR              | tRL                 | 0        |      | ns   |  |

| HAO Delay from HAI               | thiho               |          | 100  | ns   |  |

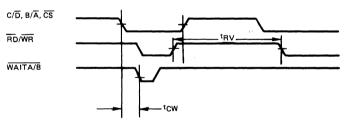

| Recovery Time Between Controls   | tRV                 | 300      |      | ns   |  |

| WAIT Delay from Address          | tCW                 |          | 120  | ns   |  |

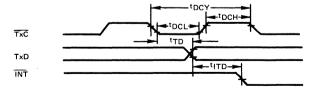

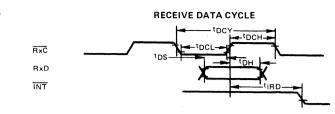

| Data Clock Cycle                 | tDCY                | 400      |      | ns   |  |

| Data Clock Low Width             | tDCL                | 180      |      | ns   |  |

| Data Clock High Width            | <sup>t</sup> DCH    | 180      |      | ns   |  |

| Tx Data Delay                    | tтр                 |          | 300  | ns   |  |

| Data Set up to RxC               | tDS                 | 0        |      | ns   |  |

| Data Hold from RxC               | tDH                 | 140      |      | ns   |  |

| INT Delay Time from TxC          | ЧТD                 |          | 4~6  | tCY  |  |

| INT Delay Time from RxC          | tIRD                |          | 7~11 | tCY  |  |

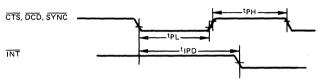

| Low Pulse Width                  | tPL                 | 200      |      | ns   |  |

| High Pulse Width                 | tPH                 | 200      |      | ns   |  |

| External INT from CST, DCD, SYNC | tIPD                |          | 500  | ns   |  |

| Delay from RxC to SYNC           | tDRxC               |          | 100  | ns   |  |

## TIMING WAVEFORMS

INTA CYCLE

TRANSMIT DATA CYCLE

Notes: (1) INTA signal acts as RD signal. (2) PRI and HAI signals act as CS signal.

# μ PD7201

## TIMING WAVEFORMS (CONT.)

READ/WRITE CYCLE (SOFTWARE BLOCK TRANSFER MODE)

SYNC PULSE GENERATION (EXTERNAL SYNC MODE)

9

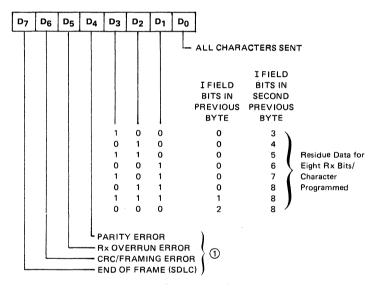

READ REGISTER 11

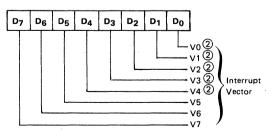

#### **READ REGISTER 2**

Notes:

①

Used with Special Receive Condition Mode.

②

Variable if "Status Affects Vector" is programmed.

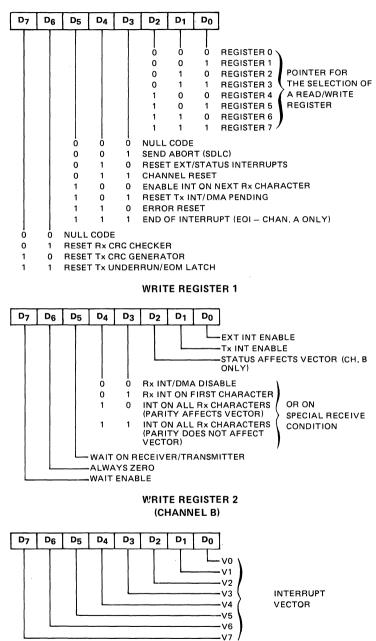

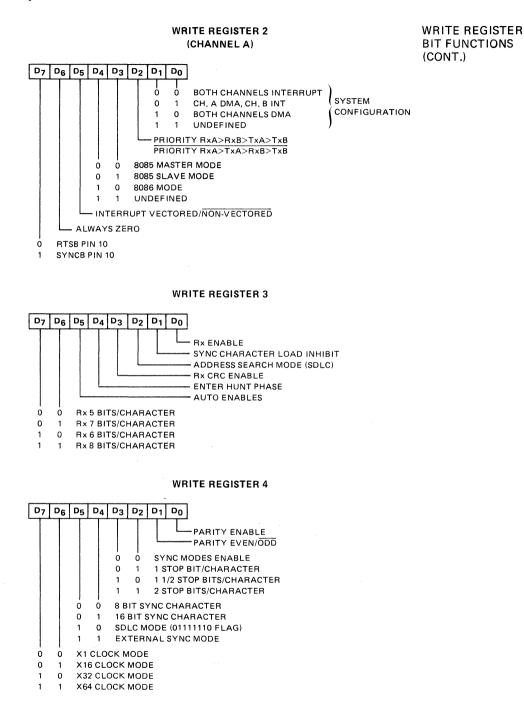

#### WRITE REGISTER BIT FUNCTIONS

WRITE REGISTER 0

9

Note: (1) For SDLC it must be programmed to "01111110" for flag recognition.

|     |     |     | ITS | PRIN | MODE         |        | CONTENTS ON DATA BUS DRIVEN BY THE $\mu$ PD7201 AT |    |          |           |                         |    |                | AT EACH INTA SEQUENCE |                |        |    |                |        |      |                |    |    |    |     |      |    |    |                |

|-----|-----|-----|-----|------|--------------|--------|----------------------------------------------------|----|----------|-----------|-------------------------|----|----------------|-----------------------|----------------|--------|----|----------------|--------|------|----------------|----|----|----|-----|------|----|----|----------------|

| 1 1 | V C | :н. | . A |      |              |        |                                                    |    | lst Îl   | NTA       | •                       |    |                |                       | 2nd INTA       |        |    |                |        |      | 3rd INTA (*)   |    |    |    |     |      |    |    |                |

| D5  | D   | 94  | D3  |      |              | D7     | D <sub>6</sub>                                     | D5 | D4       | D3        | D2                      | D1 | D <sub>0</sub> | D7                    | D6             | D5     | D4 | D3             | D      | 2 D1 | D <sub>0</sub> | D7 | D6 | D5 | D4  | D3   | D2 | D1 | D <sub>0</sub> |

| ø   | ;   | x   | x   | ×    | Non-vectored |        | High-Z                                             |    |          |           | High-Z                  |    |                |                       |                | High-Z |    |                |        |      |                |    |    |    |     |      |    |    |                |

| 1   | (   | ø   | ø   | ø    | 8085 Master  | 1      | 1                                                  | ø  | (Ca<br>Ø | all)<br>1 | 1                       | ø  | 1              | V7                    | V <sub>6</sub> | V5     | ∨4 | V <sub>3</sub> | v      | 2 V1 | V <sub>0</sub> | ø  | ø  | ø  | ø   | ø    | ø  | ø  | ø              |

| 1   | (   | ø   | Ø   | 1    | 8085 Master  | 1      | 1                                                  | Ø  | ø        | 1         | 1                       | Ø  | 1              |                       |                |        | Hi | gh-Z           | 2      |      |                |    |    |    | Hig | ıh-Z |    |    |                |

| 1   | (   | ø   | 1   | Ø    | 8085 Slave   |        |                                                    |    | Hig      | h-Z       |                         |    |                | ٧7                    | V6             | V5     | V4 | V <sub>3</sub> | v      | 2 V· | Vo             | ø  | Ø  | Ø  | Ø   | Ø    | Ø  | Ø  | Ø              |

| 1   | (   | Ø   | 1   | 1    | 8085 Slave   |        |                                                    |    | Hig      | h-Z       |                         |    |                | High-Z                |                |        |    |                | High-Z |      |                |    |    |    |     |      |    |    |                |

| 1   |     | 1   | Ø   | Ø    | 8086         | High-Z |                                                    |    |          |           | V7 V6 V5 V4 V3 V2 V1 V0 |    |                |                       |                | 1 V0   |    |                |        |      |                |    |    |    |     |      |    |    |                |

| 1   |     | 1   | Ø   | 1    | 8086         |        |                                                    |    | Hig      | h-Z       |                         |    |                |                       |                |        | Hi | gh-Z           | 2      |      |                |    |    |    |     |      |    |    |                |

(\*) 3rd INTA is 8085 Mode