# MOS INTEGRATED CIRCUIT $\mu PD75028(A)$

## **4-BIT SINGLE-CHIP MICROCOMPUTER**

The information in this document is subject to change without notice.

The uPD75028(A) belongs to the NEC CMOS 4-bit single chip microcomputer 75% series which enables data processing matching an 8-bit microcomputer.

The uPD75028(A) is a powerful and high cost performance product which contains high function such as A/D converter and serial bus interface (SBI) adopting the NEC standard format in addition to Ohigh-speed operation (minimum instruction execution time by CPU: 0.95 us).

uPD75P036 which contains PROM instead of uPD75028(A) ROM is also provided for evaluation during system development or for small production.

#### Features

- o High reliability as compared with uPD75028

- o Fast execution time (@4.19 MHz)

- · High speed cycle: 0.95 us

- · Low voltage cycles: 1.91 us and 15.3 us

- o Power-reducing operation

- With system clock operating at 32.768 kHz (execution time: 122 us)

- o A/D converter

- · 8-channel, 8-bit

- o Low-voltage operation possible ( $V_{\rm DD}$ =2.7 to 6.0V)

- o Four timers

- One of them can be used as PWM output, 16-bit counter for an integrating A/D converter, etc.

- o NEC standard serial bus interface

- · SBI mode\_

- o Very low-power clock operation: 5 uA TYP. (at 3V in HALT mode)

- o 43 I/O lines

- With mask-option or software-selectable pull-up/pull-down resistors

- o OTP version: uPD75P036 ( $V_{DD} = 2.7$  to 6.0 V)

## Applications

Car electronics, etc.

## Ordering Information

| Ordering Code         | Package                   | Quality Grade |

|-----------------------|---------------------------|---------------|

| uPD75028CW(A)-xxx     | 64-pin plastic Shrink DIP | Special       |

| uPD75028GC(A)-xxx-AB8 | 64-pin plastic QFP        | Special       |

Remarks: xxx is ROM code number.

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

# Difference between uPD75028(A) and uPD75028

| Product                     | uPD75028(A)  | uPD75028     |  |

|-----------------------------|--------------|--------------|--|

| Quality grade               | Special      | Standard     |  |

| Operation temperature range | -40 to +85°C | -40 to +70°C |  |

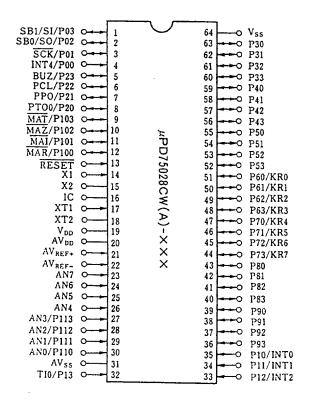

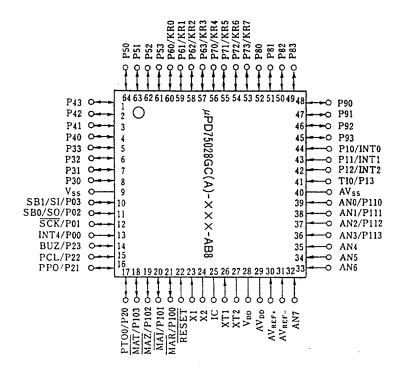

# Pin Configuration (Top View)

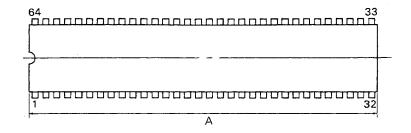

# o 64-pin plastic shrink DIP

IC: Internally connected. (Connect the pin to  $V_{\mbox{DD}}$ )

#### Pin names

```

P00-03

: Port0

P10-13

: Portl

P20-23

: Port2

P30-33

: Port3

P40-43

: Port4

P50-53

: Port5

: Port6

P60-63

P70-73

: Port7

P80-83

: Port8

P90-93

: Port9

P100-103

: Port10

P110-113 : Port11

KR0-7

: Key Return

SCK

: Serial Clock

SI

: Serial Input

so

: Serial Output

SB0, 1

: Serial Bus 0, 1

RESET

: Reset Input

TIO

: Timer Input 0

PT00

: Programmable Timer Output 0

BUZ

: Buzzer Clock

PCL

: Programmable Clock

INTO, 1, 4 : External Vectored Interrupt 0, 1, 4

: External Test Input 2

X1, 2

: Main System Clock Oscillation 1, 2

XT1, 2

: Subsystem Clock Oscillation 1, 2

MAR

: Reference Integration Control

MAI

: Integration Control

MFT A/D

MAZ

: Autozero Control

mode

MAT

: External Comparate Timing Input

PPO

: Programmable Pulse Output...MFT timer mode

ANO-7

: Analog Input 0-7

: Analog Reference (+)

AV REF+

AVREF-

: Analog Reference (-)

AV_{DD}

: Analog V<sub>DD</sub>

AVSS

: Analog V<sub>SS</sub>

V<sub>DD</sub>

: Positive Power Supply

v<sub>ss</sub>

: Ground

```

Remarks: MFT: Multifunction timer

TTV

# Function Outline (1/2)

| Item                                                                                                                                                                                                                                   |                                                                                                                                                                                                                 |                                                                                                                                                          | Function                                                               |                                                                        |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|--|

| Number of instructions                                                                                                                                                                                                                 | 41                                                                                                                                                                                                              | <del></del>                                                                                                                                              |                                                                        |                                                                        |  |  |  |  |

| Instruction execution time                                                                                                                                                                                                             | operation)                                                                                                                                                                                                      | ·                                                                                                                                                        | k is selected: 0.95, 1.91, is selected: 122 us (during                 | •                                                                      |  |  |  |  |

| On-chip memory                                                                                                                                                                                                                         | Program memo                                                                                                                                                                                                    | ry (ROM):                                                                                                                                                | 8064 x 8 bits                                                          |                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                        | Data memory                                                                                                                                                                                                     | Data memory (RAM): 512 x 4 bits                                                                                                                          |                                                                        |                                                                        |  |  |  |  |

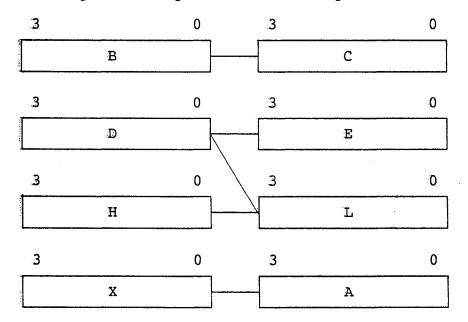

| General purpose register                                                                                                                                                                                                               | 1                                                                                                                                                                                                               | • During 4-bit operation: 8 (X, A, B, C, D, E, H, L) • During 8-bit operation: 4 (XA, BC, DE, HL)                                                        |                                                                        |                                                                        |  |  |  |  |

| Accumulator                                                                                                                                                                                                                            | Bit accumu  4-bit accu  8-bit accu                                                                                                                                                                              | mulator (A)                                                                                                                                              | )                                                                      |                                                                        |  |  |  |  |

| Instruction set                                                                                                                                                                                                                        | Various bit manipulation Efficient 4-bit data handling instruction 8-bit data transfer instructions GETI instruction which can convert any 2-byte or 3-byte instruction into a 1-byte instruction for execution |                                                                                                                                                          |                                                                        |                                                                        |  |  |  |  |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 | 12 lines                                                                                                                                                 | Input pins                                                             | Pull-up resistor can be applied to 27 lines and                        |  |  |  |  |

| I/O line                                                                                                                                                                                                                               | 48 lines                                                                                                                                                                                                        | 24 lines                                                                                                                                                 | CMOS I/O pins<br>(can be LED driving: 4)                               | pull-down resistor can<br>be applied to 4 lines b<br>means of software |  |  |  |  |

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 | 12 lines                                                                                                                                                 | Middle-voltage N-ch<br>open drain input/output<br>(can be LED driving) | Pull-up resistor can be applied to 12 lines by means of mask option    |  |  |  |  |

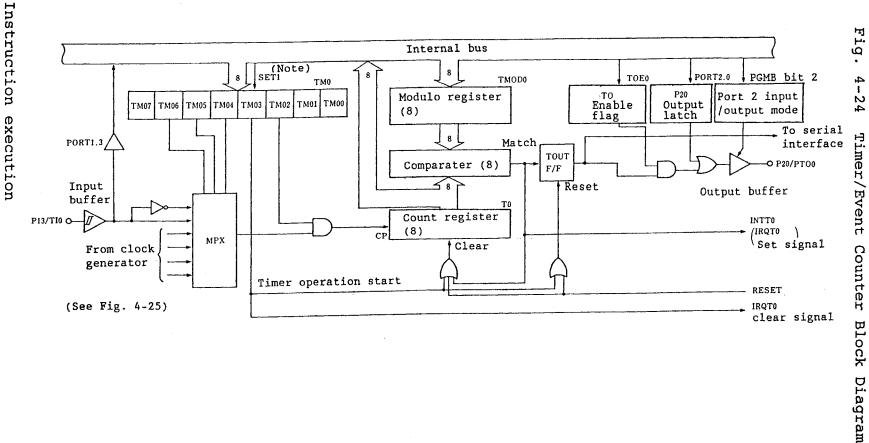

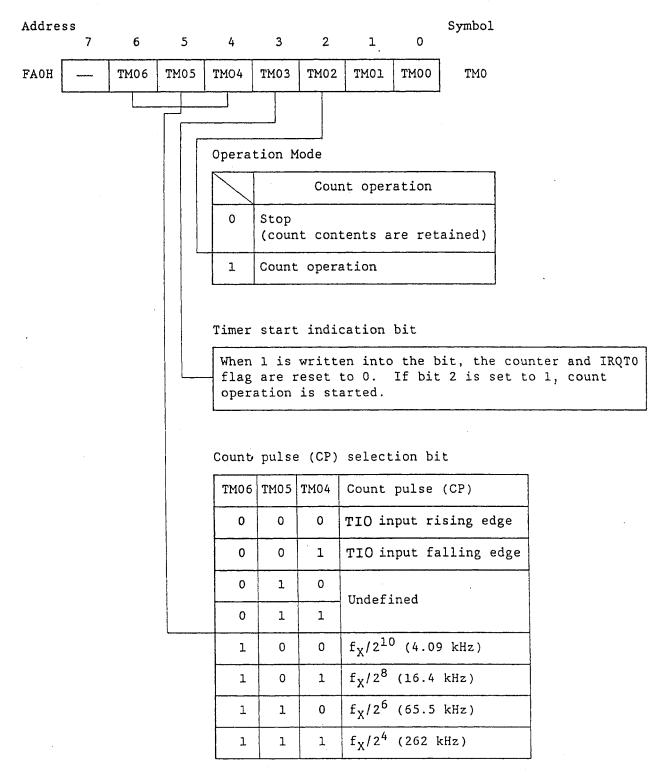

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 | • Four                                                                                                                                                   | imer/event counter stages of clock sources t count can be made         |                                                                        |  |  |  |  |

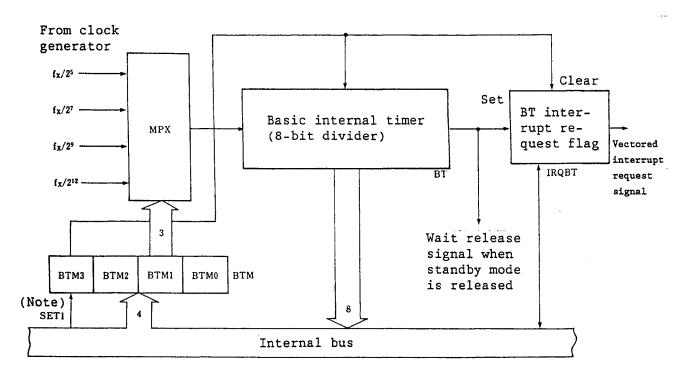

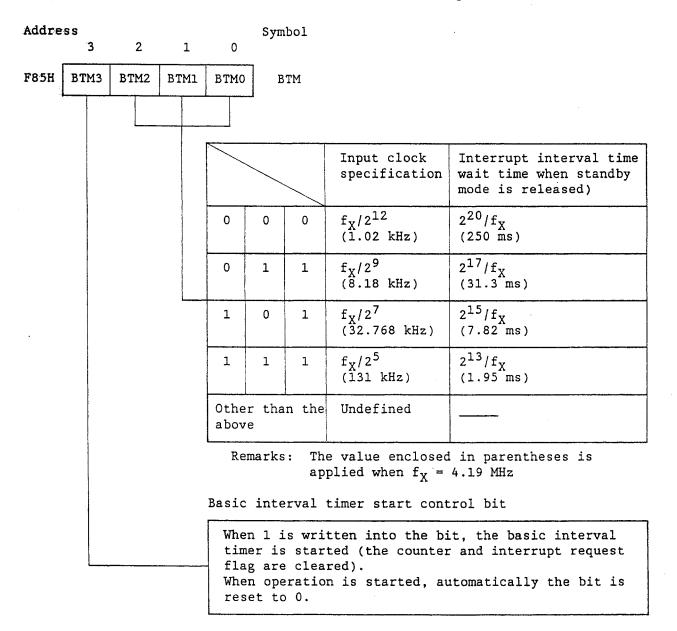

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 | 8-bit basic interval timer     Reference time generation: 1.95ms, 7.82ms, 31.3ms 250ms     (during 4.19MHz operation)     Applicable as a watchdog timer |                                                                        |                                                                        |  |  |  |  |

| • Watch timer  • 0.5-second timer interval generation • Count clock source : Main system clock and subsystem clock can be che • Watch rapid feed mode (3.9-ms time interval generation) • Buzzer output is enabled (2kHz, 4kHz, 32kHz) |                                                                                                                                                                                                                 |                                                                                                                                                          |                                                                        |                                                                        |  |  |  |  |

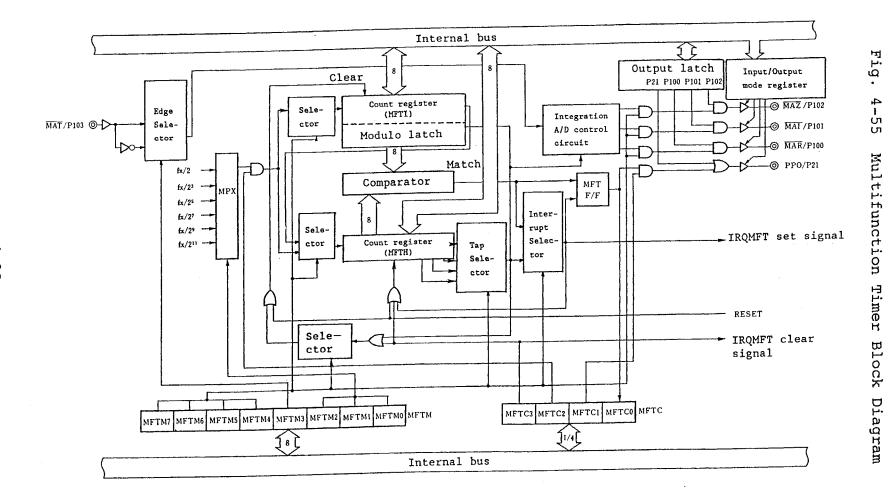

|                                                                                                                                                                                                                                        |                                                                                                                                                                                                                 | Multifunction timer     8-bit timer     PWM output     16-bit free running timer     16-bit integration A/D converter counter                            |                                                                        |                                                                        |  |  |  |  |

# Function Outline (2/2)

| Item                    | Function                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

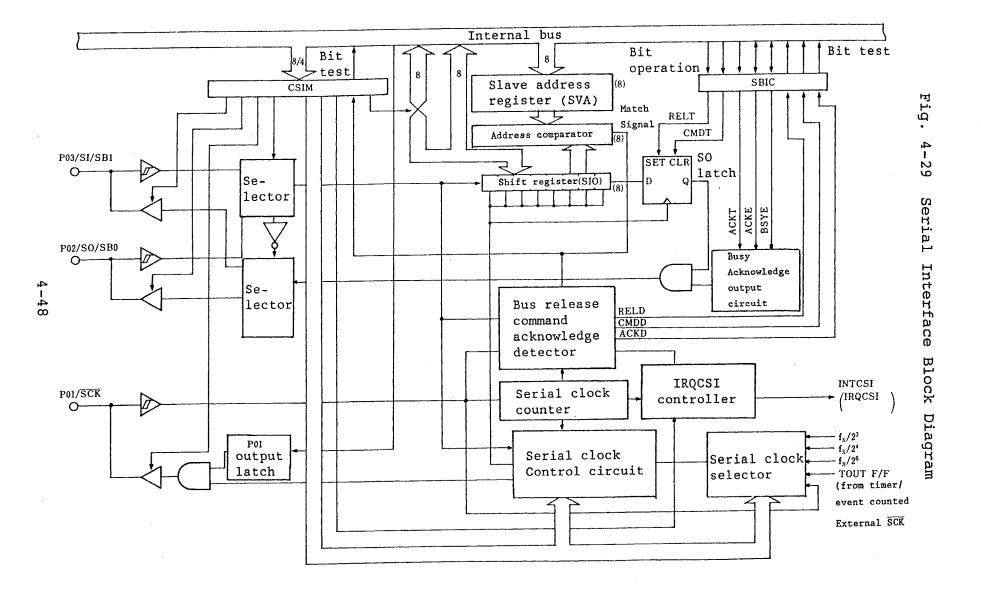

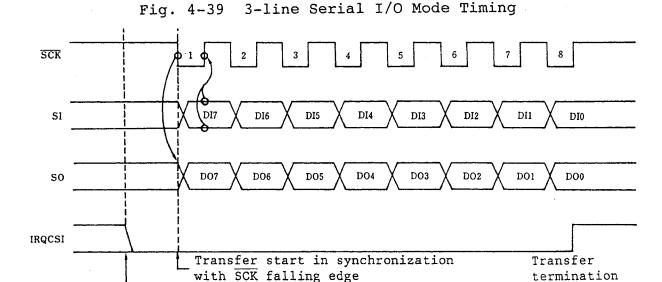

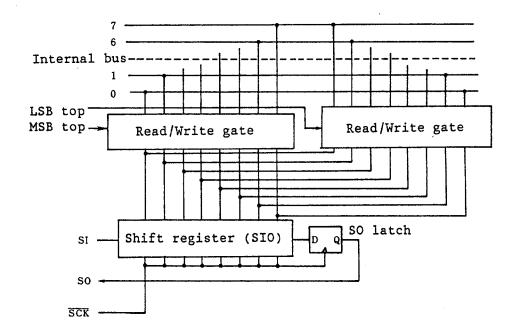

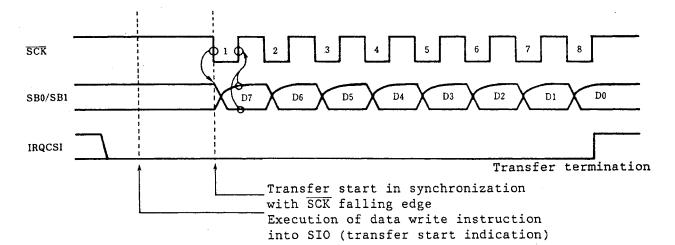

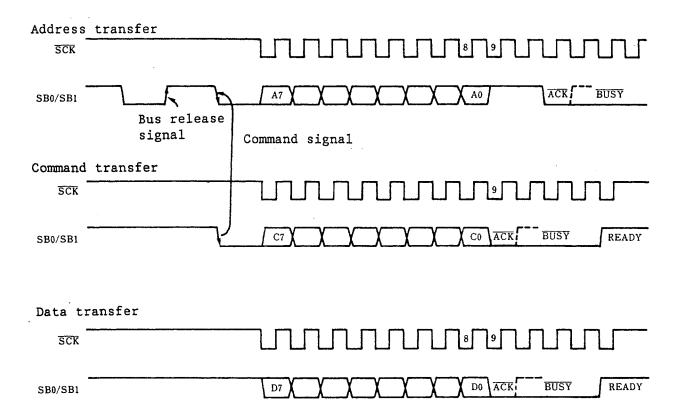

| 8-bit serial interface  | • Can cover the following three modes • 3-line serial I/O mode MSB first/LSB first can be selected • 2-line serial I/O mode • SBI mode                                                                                                                   |  |  |  |  |

| Bit sequential buffer   | Special bit manipulation memory: 16 bits  • Appropriate for remote control application                                                                                                                                                                   |  |  |  |  |

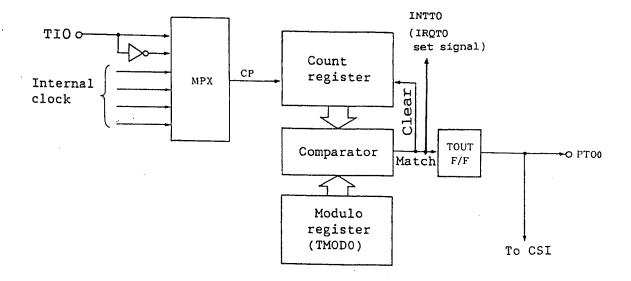

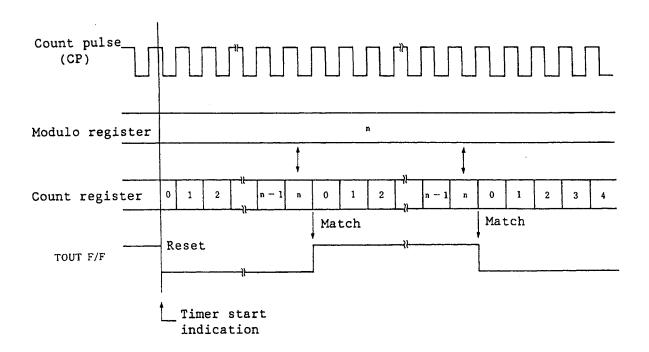

|                         | Timer/event counter output (PTOO): Square wave output of any frequency                                                                                                                                                                                   |  |  |  |  |

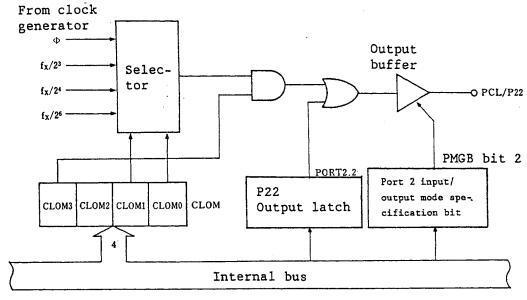

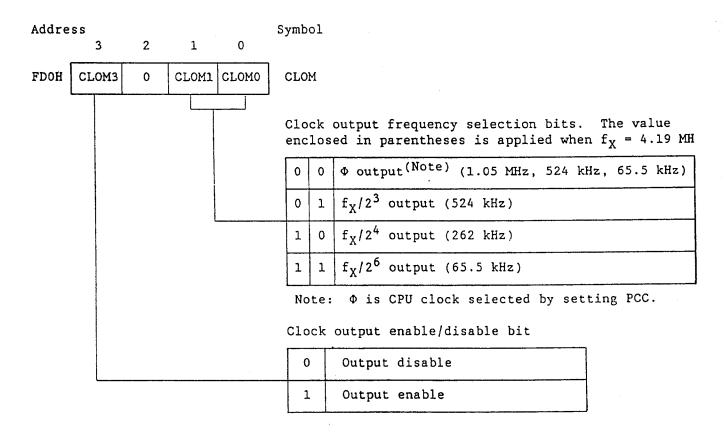

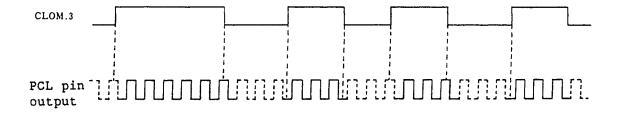

| Clock output function   | Clock output (PCL): $\phi$ , $f_{\chi}/2^3$ , $f_{\chi}/2^4$ , $f_{\chi}/2^6$ (4.19MHz during main system clock operation)                                                                                                                               |  |  |  |  |

|                         | Buzzer output (BUZ): 2kHz, 4kHz 32kHz (4.19MHz during main system clock operation or 32.768kHz subsystem clock operation)                                                                                                                                |  |  |  |  |

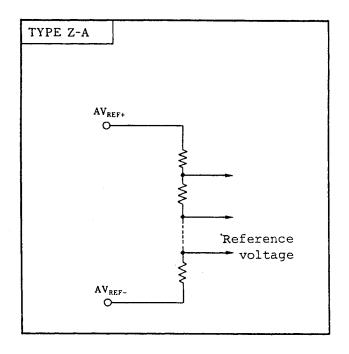

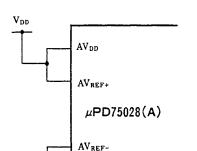

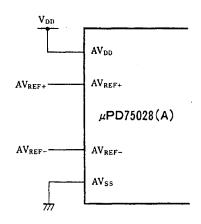

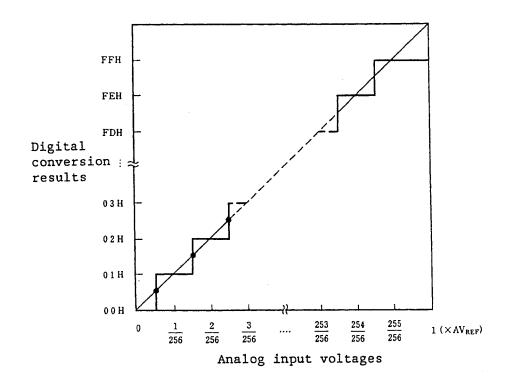

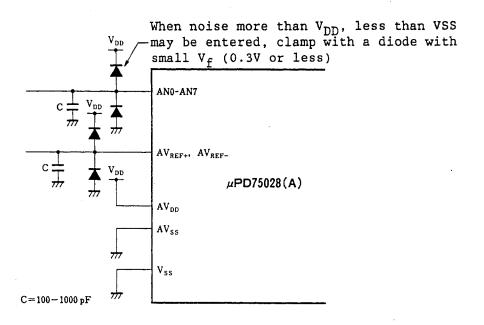

| A/D converter           | 8-bit resolution A/D converter (successive approximation): 8 channels • Can operate at low voltage: $V_{DD}^{-2.7-6.0V}$ • Reference voltage can be set as desired in the range of $AV_{REF+}$ , $AV_{REF-}$ . 2.5V<( $AV_{REF+}$ )-( $AV_{REF-}$ )<6.0V |  |  |  |  |

| Vector interrupt        | External: 3 Internal: 4                                                                                                                                                                                                                                  |  |  |  |  |

| Test input              | External: 1 Internal: 1                                                                                                                                                                                                                                  |  |  |  |  |

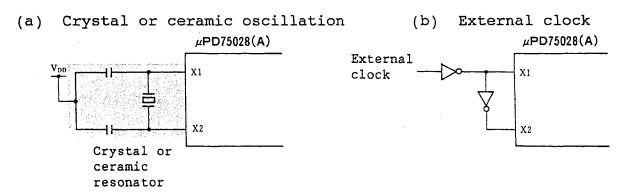

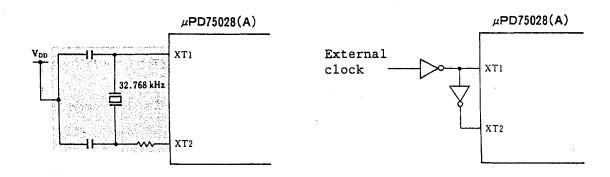

| System clock oscillator | Ceramic or crystal oscillator for main system clock oscillation     Crystal oscillator for subsystem clock oscillation                                                                                                                                   |  |  |  |  |

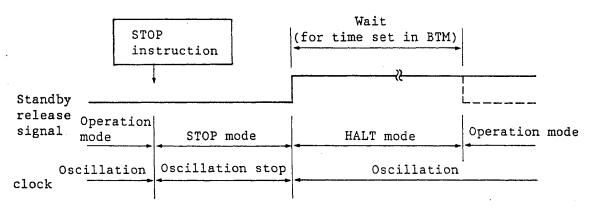

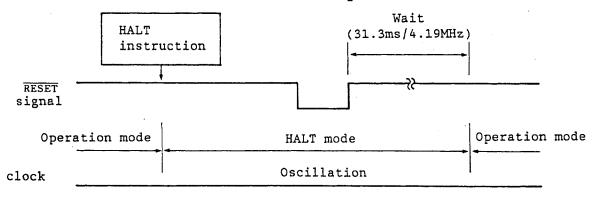

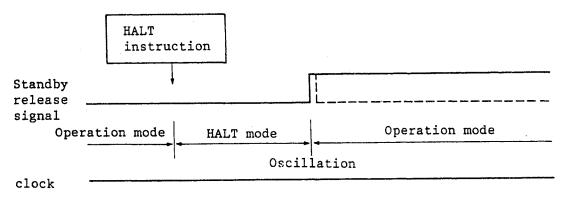

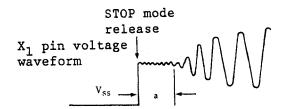

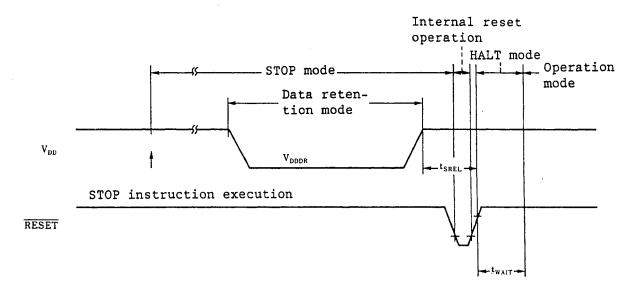

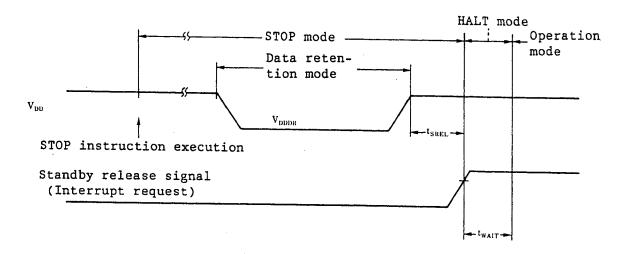

| Standby function        | STOP mode: Stops main system clock oscillation.     HALT mode: Continues system clock oscillation. (Stops CPU clock supply)                                                                                                                              |  |  |  |  |

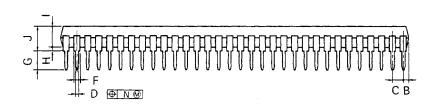

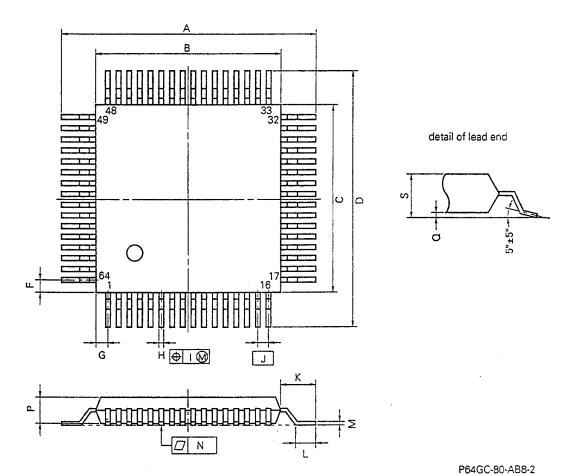

| Package                 | • 64-pin plastic shrunk DIP (750mil) • 64-pin plastic QFP (14 x 14mm)                                                                                                                                                                                    |  |  |  |  |

## CONTENTS

|      |                                                    | <u>Paqe</u> |

|------|----------------------------------------------------|-------------|

| 1. P | IN FUNCTION                                        | 1-1         |

| 1.1  | Port Pins                                          | 1-1         |

| 1.2  | Pins Other than Port Pins                          | 1-3         |

| 1.3  | Pin Input/Output Circuits                          | 1-5         |

| 1.4  | Mask Option Selection                              | 1-7         |

| 2. u | PD75028 ARCHITECTURE AND MEMORY MAP                | 2-1         |

| 2.1  | Data Memory Bank Configuration and Addressing Mode | 2-1         |

| 2.2  | Memory Mapped I/O                                  | 2-7         |

| 3. I | NTERNAL CPU FUNCTION                               | 3-1         |

| 3.1  | Program Counter (PC)                               | 3-1         |

| 3.2  | Program Memory (ROM)                               | 3-2         |

| 3.3  | Data Memory (RAM)                                  | 3-4         |

| 3.4  | General Purpose Registers                          | 3-7         |

| 3.5  | Accumulators                                       | 3-9         |

| 3.6  | Stack Pointer (SP)                                 | 3-10        |

| 3.7  | Program Status Word (PSW)                          | 3-12        |

| 3.8  | Bank Selection Register (BS)                       | 3-17        |

| 4. P | ERIPHERAL HARDWARE FUNCTION                        | 4-1         |

| 4.1  | Digital Input/Output Ports                         | 4-1         |

| 4.2  | Clock Generator                                    | 4-16        |

| 4.3  | Clock Output Circuit                               | 4-27        |

| 4.4  | Basic Interval Timer                               | 4-30        |

|    |       |                                             | <u>Page</u>     |

|----|-------|---------------------------------------------|-----------------|

|    | 4.5   | Watch Timer                                 | 4-34            |

|    | 4.6   | Timer/Event Counter                         | 4-38            |

|    | 4.7   | Serial Interface                            | 4-46            |

|    | 4.8   | A/D Converter                               | 4-83            |

|    | 4.9   | Multifunction Timer (MFT)                   | 4-92            |

|    | 4.10  | Bit Sequential Buffer                       | 4-116           |

| 5  | . IN  | TERRUPT FUNCTION                            | 5-1             |

|    | 5.1   | Interrupt Control Circuit Configuration     | 5-2             |

|    | 5.2   | Interrupt Control Circuit Hardware          | 5-4             |

|    | 5.3   | Interrupt Sequence                          | 5-12            |

|    | 5.4   | Multiple Interrupt Processing Control       | 5-13            |

|    | 5.5   | Vector Address Sharing Interrupt Processing | 5-15            |

| 6  | . Si  | ANDBY FUNCTION                              | 6-1             |

|    | 6.1   | Standby Mode Setting and Operation State    | 6-1             |

|    | 6.2   | Standby Mode Release                        | 6-2             |

|    | 6.3   | Operation after Standby Mode is Released    | 6-5             |

| 7  | . RI  | ESET FUNCTION                               | 7-1             |

| 8  | . 11  | STRUCTION SET                               | 8-1             |

|    | 8.1   | uPD75028(A) Featuring Instruction           | 8-1             |

|    | 8.2   | Instruction Set and Operation               | 8-5             |

| 9  | . E   | LECTRICAL CHARACTERISTICS                   | 9-1             |

| 1  | 0. P  | ACKAGE INFORMATION                          | 10-1            |

| 1  | 1. R  | ECOMMENDED CONDITIONS FOR SOLDERING         | 11-1            |

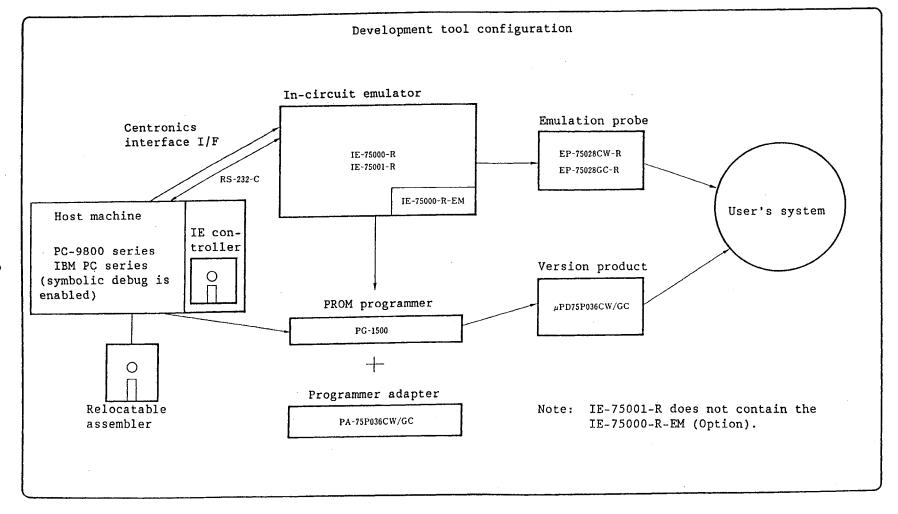

| 70 | מאשמם | TY DEVELOPMENT TOOLS                        | λ <sub></sub> 1 |

### 1. PIN FUNCTION

## 1.1 Port Pins

| Pin name            | 1/0 | Dual<br>function<br>pin | Function                                                                                                                                                                 | 8-<br>bit<br>I/0 | When reset                                                  | Input/output<br>circuit type<br>(Note 1) |

|---------------------|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------|------------------------------------------|

| P00                 | 1   | INT4                    | 4-bit input port (PORTO).                                                                                                                                                |                  |                                                             | В                                        |

| P01                 | 1/0 | SCK                     | Internal pull-up resistor can be specified for                                                                                                                           | x                | Input                                                       | F - A                                    |

| P02                 | 1/0 | SO/SB0                  | PO1-PO3 in 3-bit units by software.                                                                                                                                      |                  |                                                             | F - B                                    |

| P03                 | 1/0 | SI/SB1                  |                                                                                                                                                                          |                  |                                                             | M - C                                    |

| P10                 |     | INTO                    | With noise removing                                                                                                                                                      | g                |                                                             |                                          |

| P11                 | ı   | INT1                    | function                                                                                                                                                                 | -                |                                                             | D 0                                      |

| P12                 |     | INT2                    | 4-bit input port (PORTI). Internal pull-up resistor                                                                                                                      | x                | Input                                                       | B - C                                    |

| P13                 |     | T10                     | can be specified in 4-bit units by software.                                                                                                                             |                  |                                                             |                                          |

| . P20               |     | PTOO                    | 4-bit input/output port                                                                                                                                                  |                  |                                                             |                                          |

| P21                 | 1/0 | PP0                     | (PORT2).<br>Internal pull-up resistor                                                                                                                                    | x                | Input                                                       | E - B                                    |

| P22                 |     | PCL                     | can be specified 4-bit units by software.                                                                                                                                |                  |                                                             | !<br>                                    |

| P23                 |     | BUZ                     |                                                                                                                                                                          |                  |                                                             |                                          |

| P30(Note 2)         |     | -                       | Programmable 4-bit input/                                                                                                                                                |                  |                                                             |                                          |

| P31(Note 2)         | 1/0 | -                       | output port (PORT3). Input or output mode can                                                                                                                            |                  | 7                                                           | E - B                                    |

| P32(Note 2)         |     | -                       | be set bit-wise. Internal pull-up resistor                                                                                                                               | x                | Input                                                       | L - D                                    |

| P33(Note 2)         |     | -                       | can be specified in 4-bit units by software.                                                                                                                             |                  |                                                             |                                          |

| P40-P43<br>(Note 2) | 1/0 | -                       | N-ch open drain 4-bit<br>input/output port (PORT4).<br>Internal pull-up resistor<br>can be contained bit-wise<br>(mask option). 10-V voltage<br>10-V voltage during open |                  | High (when pull-up resistor is contained) or high impedance | M                                        |

| P50-P53<br>(Note 2  | 1/0 | _                       | N-ch open drain 4-bit input/output port (PORT5). Internal pull-up resistor can be contained bit-wise (mask option).  10-V voltage during open drain.                     | •                | High (when pull-up resistor is contained) or high impedance | 1                                        |

Note 1: o denotes Schmitt trigger input.

Note 2: LED can be directly driven.

# 1.1 Port Pins (Continued)

| Pin name    | 1/0 | Dual<br>function<br>pin | Function                                                                                                  | 8-<br>bit<br>I/O | When reset             | Input/output<br>circuit type<br>(Note 1) |

|-------------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------|------------------|------------------------|------------------------------------------|

| P60         |     | KRO                     | Programmable 4-bit input/                                                                                 |                  |                        |                                          |

| P61         | 1/0 | KR1                     | output port (PORT6). Input or output mode can be                                                          |                  | <b>.</b>               |                                          |

| P62         | 1/0 | KR2                     | specified bit-wise.<br>Internal pull-up resistor                                                          |                  | Input                  | F - A                                    |

| P63         |     | KR3                     | can be specified in 4-bit units by software.                                                              | 0                |                        |                                          |

| P70         |     | KR4                     | 4-bit input/output port                                                                                   |                  |                        |                                          |

| P71         |     | KR5                     | (PORT7).<br>Internal pull-up resistor                                                                     |                  | Input                  | F - A                                    |

| P72         | 1/0 | KR6                     | can be specified 4-bit units by software.                                                                 | 0                |                        |                                          |

| P73         |     | KR7                     |                                                                                                           |                  |                        |                                          |

| P80-P83     | 1/0 | **                      | 4-bit input/output port (PORT8). Internal pull-up resistor can be specified in 4-bit units by software.   | ×                | Input                  | E - B                                    |

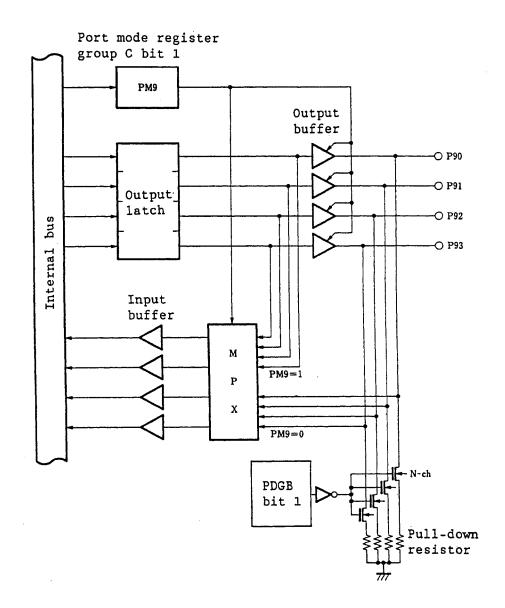

| P90-P93     | 1/0 | -                       | 4-bit input/output port (PORT9). Internal pull-down resistor can be specified in 4-bit units by software. |                  | Input                  | E - D                                    |

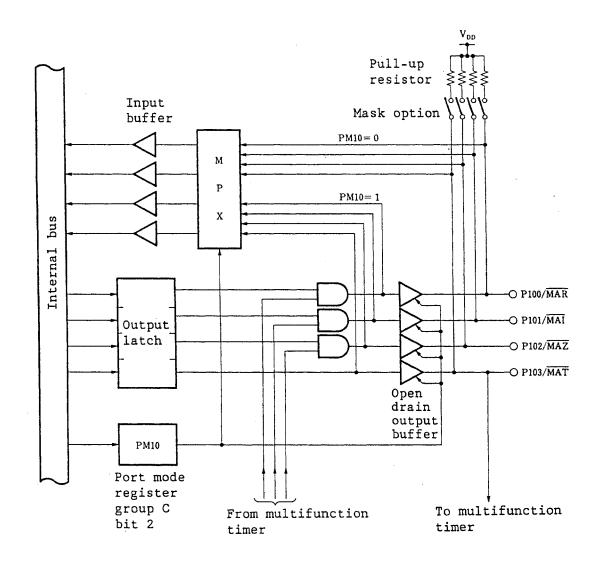

| P100(Note2) |     | MAR                     | N-ch open drain 4-bit input/                                                                              |                  | High (when             |                                          |

| P101(Note2) | 1   | MAI                     | output port (PORT10). Internal pull-up resistor                                                           |                  | pull-up<br>resistor is |                                          |

| P102(Note2) | 1/0 | MAŽ                     | can be contained bit-wise (mask option).                                                                  |                  | contained)<br>or high  | M                                        |

| P103(Note2) |     | MAT                     | 10-V voltage during open drain.                                                                           |                  | impedance              |                                          |

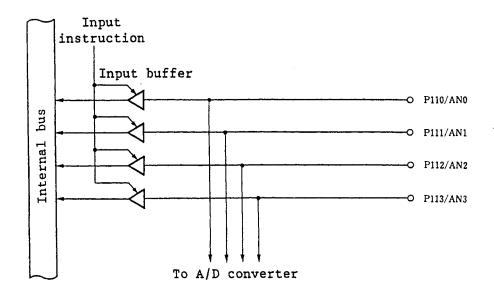

| P110        |     | ANO                     | 4-bit input port (PORT11).                                                                                | x                |                        |                                          |

| P111        | 1_  | AN1                     |                                                                                                           |                  |                        |                                          |

| P112        | I   | AN2                     |                                                                                                           |                  | Input                  | Y - A                                    |

| P113        | 1   | AN3                     |                                                                                                           |                  |                        |                                          |

Note 1: o denotes Schmitt trigger input.

Note 2: LED can be directly driven.

## 1.2 Pins Other Than Port Pins

| Pin name | 1/0 | Dual<br>function<br>pin | Function                                                                                                  |                                              |                     | When<br>reset | Input/output<br>circuit type<br>(Note 1) |

|----------|-----|-------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|---------------|------------------------------------------|

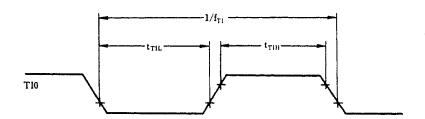

| TIO      | I   | P13                     | External even                                                                                             |                                              | input to timer/     |               | B - c                                    |

| PT00     | 1/0 | P20                     | Timer/event co                                                                                            | ounter                                       | output.             | Input         | E - B                                    |

| PCL      | 1/0 | P22                     | Clock output.                                                                                             |                                              |                     | Input         | E - B                                    |

| BUZ      | 1/0 | P23                     | Any desired for buzzer or sys                                                                             | -                                            |                     | Input         | E - B                                    |

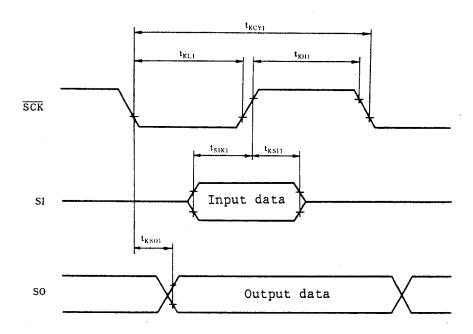

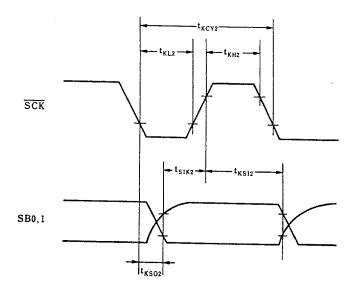

| SCK      | 1/0 | P01                     | Serial clock                                                                                              | input/o                                      | utput.              | Input         | P- A                                     |

| SO/SB0   | 1/0 | P02                     | Serial data of<br>Serial bus in                                                                           | •                                            | put.                | Input         | F - B                                    |

| SI/SB1   | 1/0 | P03                     | Serial data in                                                                                            | •                                            | Input               | M - c         |                                          |

| INT4     | I   | P00                     | Edge-detected vectored interrupt input (both rising edge detection and falling edge detection are valid). |                                              |                     |               | 8                                        |

| INTO     | ı   | P10                     | Edge-detected vectored inte                                                                               | rrupt                                        | Clocked             |               | B - c                                    |

| INT1     | 1   | P11                     | input (detect<br>edge can be<br>selected).                                                                | 10n                                          | Asynchronous        |               |                                          |

| INT2     | I   | P12                     | Edge-detected<br>testable inpu<br>(rising edge<br>detection).                                             |                                              | Asynchronous        |               | B - c                                    |

| KRO-KR3  | 1/0 | P60-P63                 | Parallel fall input.                                                                                      | ing edg                                      | ge detect testable  | Input         | F - A                                    |

| KR4-KR7  | 1/0 | P70-P73                 | Parallel fall input.                                                                                      | Parallel falling edge detect testable input. |                     |               | F - A                                    |

| MAR      | 1/0 | P100                    | Reverse integration signal output.                                                                        |                                              | (Note 2)            | -             |                                          |

| MAI      | 1/0 | P101                    | During MFT integration A/D                                                                                | Integr                                       | ration signal       | (Note 2)      | -                                        |

| MAZ      | 1/0 | P102                    | converter<br>mode                                                                                         | Auto 2                                       | zero signal output. | (Note 2)      | -                                        |

| MAT      | 1/0 | P103                    |                                                                                                           | Compan                                       | rator input.        | (Note 2)      | -                                        |

Note 1: o denotes Schmitt trigger input

Note 2: High (when pull-up resistor is contained) or high impedance.

Remarks: MFT: Multifunction timer

# 1.2 Pins Other Than Port Pins (Continued)

| Pin name            | 1/0 | Dual<br>function<br>pin | Function                                                                                                                                                                   |                                                                                                                                           | When<br>reset | Input/output<br>circuit type<br>(Note 1) |

|---------------------|-----|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|

| PPO                 | 1/0 | P21                     | During MFT<br>timer mode                                                                                                                                                   | Timer pulse output.                                                                                                                       | Input         | E - B                                    |

| ANO-AN3             | _   | P110-P113               |                                                                                                                                                                            |                                                                                                                                           | -             | Y - A                                    |

| AN4-AN7             | I   | _                       |                                                                                                                                                                            | 8-bit analog input.                                                                                                                       | Input         | Y                                        |

| AV <sub>REF+</sub>  | I   | -                       | A/D<br>converter<br>dedicated                                                                                                                                              | Reference voltage input (AV <sub>DD</sub> side).                                                                                          |               | Z - A                                    |

| AV <sub>REF</sub> - | I   | -                       | pins                                                                                                                                                                       | Reference voltage input (AV <sub>SS</sub> side).                                                                                          |               | Z - A                                    |

| AV <sub>DD</sub>    | ı   | -                       |                                                                                                                                                                            | Operation voltage input                                                                                                                   |               | _                                        |

| AVSS                |     |                         |                                                                                                                                                                            | Reference GND input.                                                                                                                      |               | _                                        |

| X1, X2              | I   | -                       | system cloc<br>external cl                                                                                                                                                 | ceramic connection pins for main<br>k oscillation. To supply<br>ock, input it to XT1 and its<br>ase to X2. X1 can be used as a<br>(test). | <del></del>   | _                                        |

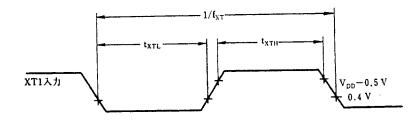

| XT1, XT2            | I   | -                       | Crystal connection pins for subsystem clock oscillation. To supply external clock, input it to XT1 and its inverted phase to XT2. XT1 can be used as a 1-bit input (test). |                                                                                                                                           |               | _                                        |

| RESET               | I   | -                       | System reset input.                                                                                                                                                        |                                                                                                                                           |               | B                                        |

| IC                  | -   | -                       | Internally Connected. Connect to V <sub>DD</sub>                                                                                                                           |                                                                                                                                           |               | _                                        |

| V <sub>DD</sub>     | -   | -                       | Positive power supply.                                                                                                                                                     |                                                                                                                                           |               | -                                        |

| v <sub>ss</sub>     | -   | -                       | GND potenti                                                                                                                                                                | al.                                                                                                                                       |               | -                                        |

Note 1: o denotes Schmitt trigger input.

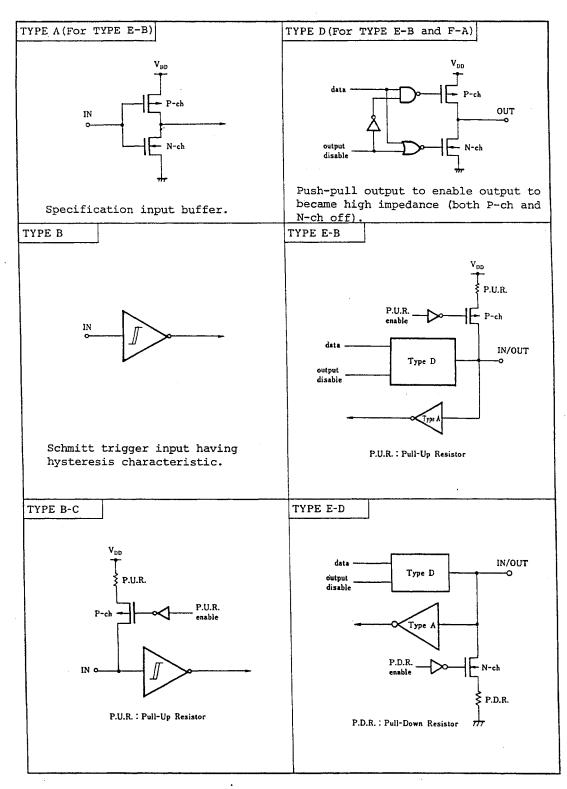

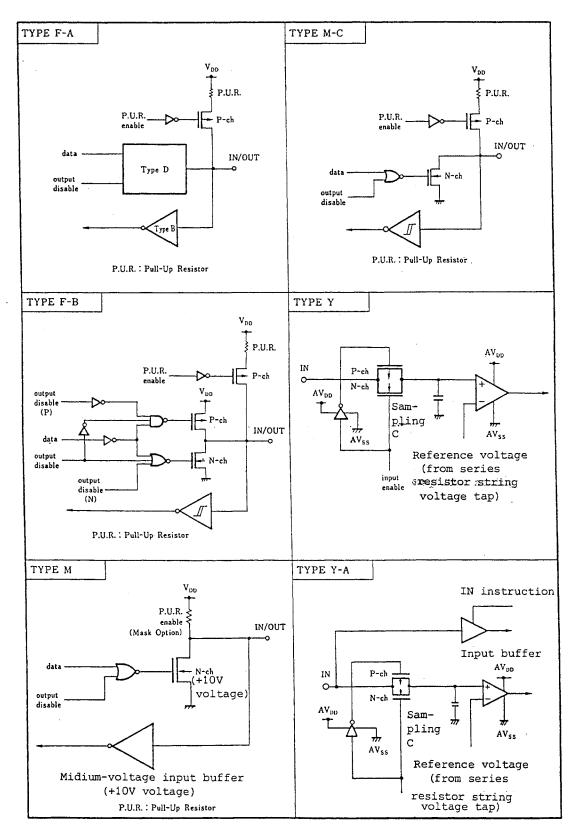

## 1.3 Pin Input/Output Circuits

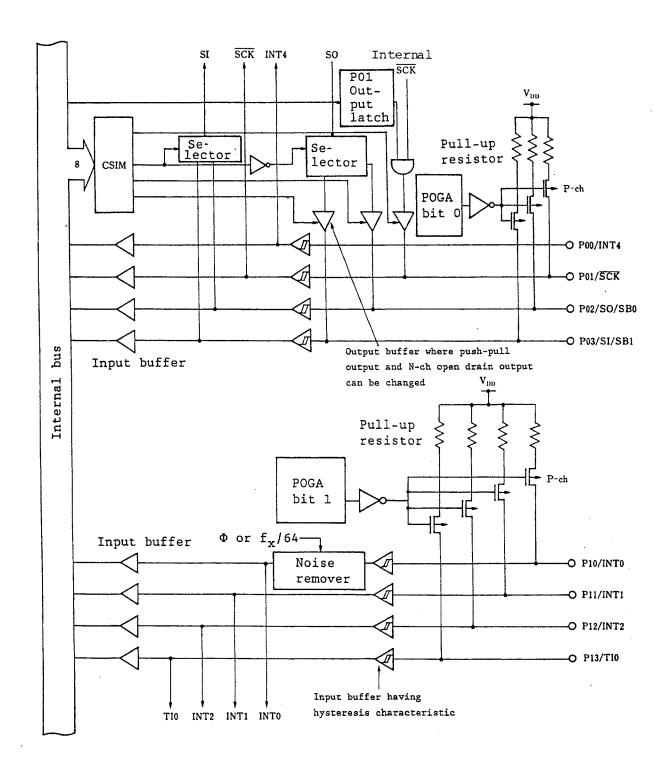

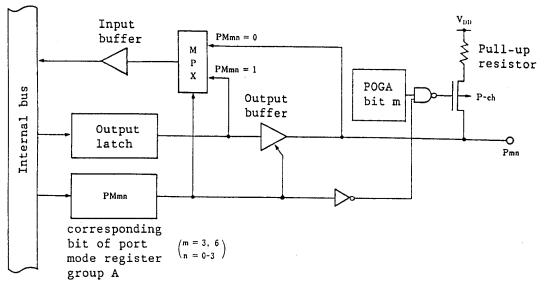

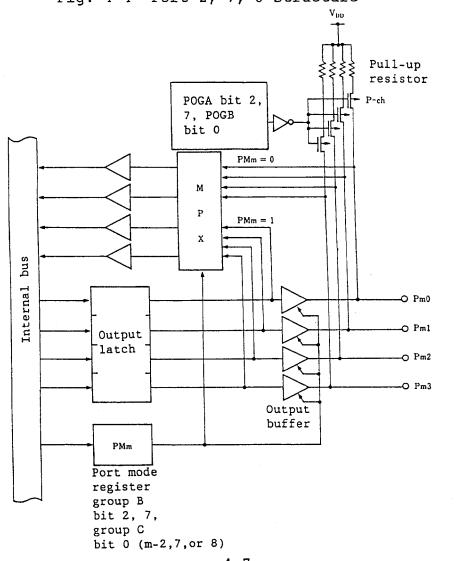

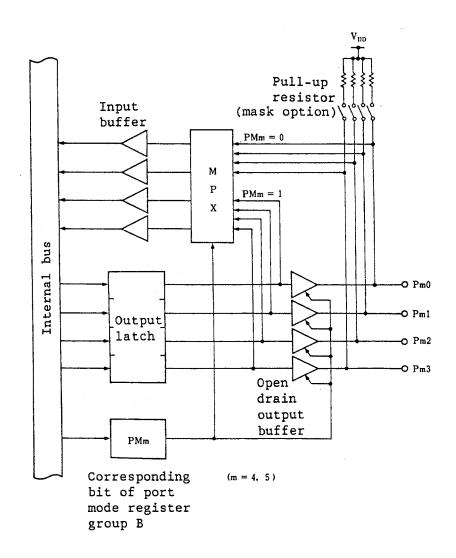

The pin input/output circuits of the uPD75028(A) are shown schematically.

# 1.4 Mask Option Selection

The pins contain mask option, as listed below:

| Pin function                      | · | Mas                                              | k op | tion                                                    |

|-----------------------------------|---|--------------------------------------------------|------|---------------------------------------------------------|

| P40-P43,<br>P50-P53,<br>P100-P103 | 1 | Pull-up resistor (can be specified bit-wise)     | 2    | No pull-up resistor (can be specified bit-wise)         |

| XT1, XT2                          | 1 | Feedback resistor (when subsystem clock is used) | 2    | No feedback resistor (when subsystem clock is not used) |

#### 2. uPD75028(A) ARCHITECTURE AND MEMORY MAP

The uPD75028(A) architecture features are as follows:

- (a) Bank configuration of data memory

- (b) Memory mapped-I/O

General description of these features is given.

#### 2.1 Data Memory Bank Configuration and Addressing Mode

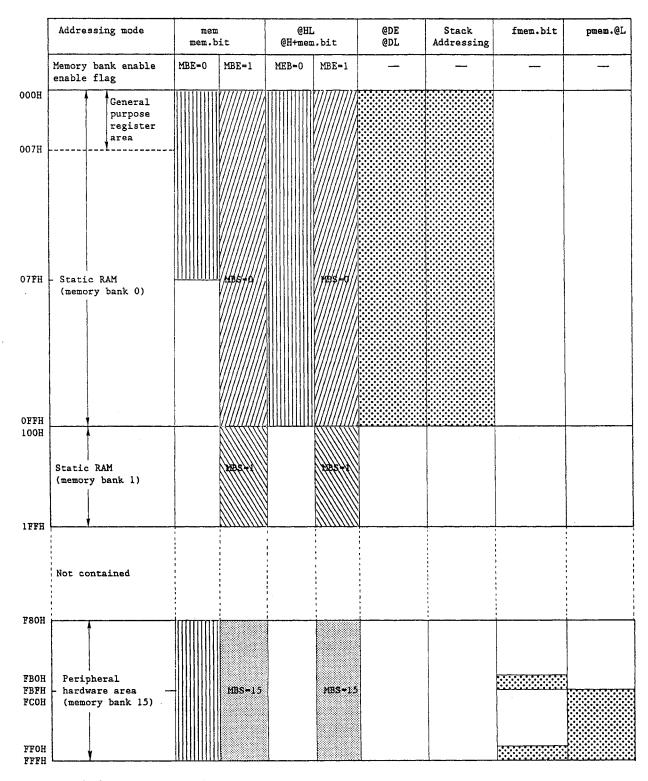

The uPD75028(A) contains 512-word x 4-bit static RAM at addresses 000H-1FFH of data memory space and peripheral hardware such as input/output ports and timers at addresses F80H-FFFH, as shown in Fig. 2-1. To address the data memory space of 12-bit addresses, the low-order eight bits of an address are specified directly or indirectly by an instruction and the high-order four bits are specified according to memory bank (MB). (Memory bank configuration)

Memory bank enable flag (MBE) and memory bank selection register (MBS) are contained for memory bank (MB) specification and enable addressing as shown in Figs. 2-1 and 2-2 and Table 2-1. (MBS is used to select a memory bank and 0, 1, or 15 can be set. MBE is a flag to determine whether or not the memory bank selected in MBS is validated. MBE is automatically saved and restored during interrupt processing or subroutine processing, thus can be set as desired by the interrupt service routine or subroutine.)

For addressing the data memory space, normally MBE is set to 1 and static RAM of the memory bank specified in MBS is operated; efficient programming is enabled by using MBE = 0 mode and MBE = 1 mode each properly in program processing.

|              | Applicable program processing                                                                                       |

|--------------|---------------------------------------------------------------------------------------------------------------------|

| MBE = 0 mode | o Interrupt processing o Repetition of internal hardware operation and static RAM operation o Subroutine processing |

| MBE = 1 mode | o Normal program processing                                                                                         |

### MBE and MBS are set as shown below:

Example: SET1 MBE ; MBE - 1

CLR1 MBE ; MBE - 0

SEL MB0 ; MBS - 0

SEL MB1 ; MBS - 1

SEL MB15 ; MBS - 15

Fig. 2-1 Data Memory Configuration and Addressing Range for each Addressing Mode

Table 2-1 Addressing Mode

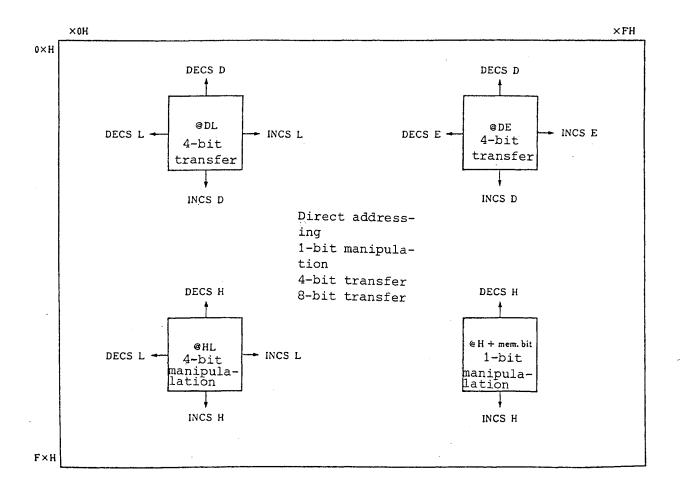

| Addressing mode                     | Identifier | Specified address                                                                                                                                                                                      |  |  |  |  |  |  |

|-------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1-bit direct<br>addressing          | mem.bit    | Bit of address indicated by MB and mem. The bit position is indicated by bit.  - When MBE = 0, MB = 0 when mem = 00H-7FH  MB = 15 when mem = 80H-FFH  - When MBE = 1, MB = MBS                         |  |  |  |  |  |  |

| 4-bit direct<br>addressing          |            | Address indicated by MB and mem.  - When MBE = 0, \{ MB = 0 \text{ when mem} = 00H-7FH \\ \{ MB = 15 \text{ when mem} = 80H-FFH \\ \}  - When MBE = 1, MB = MBS                                        |  |  |  |  |  |  |

| 8-bit direct<br>addressing          | mem        | Address indicated by MB and mem (mem is an even address).<br>- When MBE = 0, $MB = 0$ when mem = 00H-7FH $MB = 15$ when mem = 80H-FFH - When MBE = 1, MB = MBS                                         |  |  |  |  |  |  |

| .4-bit register indirect addressing | @HL        | Address indicated by MB, HL.  MB = MBE·MBS                                                                                                                                                             |  |  |  |  |  |  |

| addressing                          | @DE        | Memory bank 0 address indicated by DE.                                                                                                                                                                 |  |  |  |  |  |  |

|                                     | @DL        | Memory bank 0 address indicated by DL.                                                                                                                                                                 |  |  |  |  |  |  |

| 8-bit register indirect addressing  | @HL        | Address indicated by MB and HL (L register contains an even number).  BM = MBE·MBS                                                                                                                     |  |  |  |  |  |  |

| Bit manipula-<br>tion addressing    | fmem.bit   | Bit of address indicated by fmem. The bit position is indicated by bit.  fmem = FBOH=FBFH (hardware related to interrupts)  FFOH-FFFH (I/O port)                                                       |  |  |  |  |  |  |

|                                     | pmem. @L   | Bit of address indicated by the high-order 10 bits of pmem and the high-order two bits of the L register. The bit position is indicated by the low-order two bits of the L register.  pmem = FCOH-FFFH |  |  |  |  |  |  |

|                                     | @H+mem.bit | Bit indicated by MB, H, and the low-order four bit of mem. The bit position is indicated by bit.  MB = MBE·MBS                                                                                         |  |  |  |  |  |  |

| Stack addressing                    | 5          | Memory bank 0 address indicated by SP.                                                                                                                                                                 |  |  |  |  |  |  |

As listed in Table 2-1, direct or indirect addressing is enabled for each of 1-bit data, 4-bit data, and 8-bit data on uPD75028(A) data memory operation; very efficient and easy-to-understand programs can be prepared.

Example 1: Transfer 8-bit data at port 4, 5 to address 20H, 21H.

CLR1 MBE ; MBE — 0

IN XA, PORT4 ; XA — Port 5, 4

MOV 20H, XA ; (21H, 20H) — XA

Example 2: Set P33 if P02 is 0.

SKT PORT0.2 ; Skip if port 0 bit 2 is 1

SET1 PORT3.3 ; Set port 3 bit 3

Example 3: Output different value to port 6 depending on the P10 state.

SKF PORT1.0 ; Skip if port 1 bit 0 is 0

MOV A, #1010B ; A — 1010B (string effect)

MOV A, #0101B ; A — 0101B (string effect)

SEL MB15 ; or CLR1 MBE

OUT PORT6, A ; Port 6 — A

Fig. 2-2 Static RAM Address Update Method

#### 2.2 Memory Mapped I/O

The uPD75028(A) adopts memory mapped I/O where peripheral hard-ware device such as input/output ports and timers are mapped in data memory space addresses F80H-FFFH, as shown in Fig. 2-1. Thus, special instructions to control the peripheral hardware are not provided; the peripheral hardware is controlled by memory operation instructions. (Some hardware control mnemonics for the user easily understand programs are provided.)

Table 2-2 lists the addressing mode that can be used for peripheral hardware operation.

Table 2-2 Addressing Mode Applicable at Peripheral Hardware Operation

|                       | Applicable addressing mode                                                                                | Applicable hardware                                            |

|-----------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

|                       | Direct addressing mem.bit by setting MBE = 0 or (MBE = 1 and MBS = 15)                                    | All hardware devices where 1-bit manipulation can be performed |

| 1-bit<br>manipulation | Direct addressing fmem.bit regardless of MBE or MBS.                                                      | ISTO, MBE<br>IExxx, IRQxxx, PORTn.x                            |

|                       | Indirect addressing pmem.@L regardless of MBE or MBS.                                                     | BSBn.x<br>PORTn.x                                              |

| 4-bit                 | Direct addressing mem by setting MBE = 0 or (MBE = 1 and MBS = 15)                                        | All hardware devices where 4-bit manipulation can be performed |

| manipulation          | Register indirect addressing @HL by setting (MBE = 1 and MBS = 15)                                        | can be performed                                               |

| 8-bit                 | Direct addressing mem by setting MBE = 0 or (MBE = 1 and MBS = 15). mem is an even address.               | All hardware devices where 8-bit manipulation can be performed |

| manipulation          | Register indirect addressing @HL by setting MBE = 1 and MBS = 15. The L register contains an even number. |                                                                |

Fig. 2-3 shows uPD75028(A) I/O map.

The columns of Fig. 2-3 have the following meanings.

- . Symbol: Name indicating the internal hardware address. It can be described in the instruction operand field.

- . R/W: Indicates whether or not the hardware device can be read/written.

R/W: Read and write are enabled

R: Read only

W: Write only

- . Number of bits that can be manipulated: Indicates the number of bits that can be processed to operate the hardware device.

- o: Operation in the bit units specified under the column (1, 4, or 8 bits) can be performed.

- $\triangle$ : Only some bits can be manipulated. See Remarks for the bits that can be manipulated.

- -: Operation in the bit units specified under the column (1, 4, or 8 bits) cannot be performed.

- . Bit manipulation addressing: Indicates the bit manipulation addressing applicable to the hardware device where 1-bit manipulation is performed.

Fig. 2-3 uPD75028(A) I/O Map (1/4)

| Address      | Hardware name (symbol)                           | R/W |       | of bit<br>manipu |       | Bit mani-<br>pulation | Remarks                                  |  |  |

|--------------|--------------------------------------------------|-----|-------|------------------|-------|-----------------------|------------------------------------------|--|--|

|              | b3 b2 b1 b0                                      |     | l-bit | 4-bit            | 8-bit | addressing            |                                          |  |  |

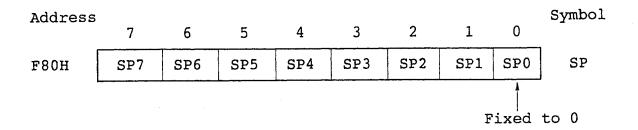

| F80H         | Stack pointer (SP)                               | R/W | •     | •                | 0     |                       | Bit 0 is fixed to 0.                     |  |  |

| P85H         | Basic interval timer mode register (BTM)         | W   | Δ     | 0                | -     | mem.bit               | Only bit 3 can be manipu lated bit-wise. |  |  |

| F86H         | Basic interval timer (BT)                        | R   | _     | -                | 0     |                       |                                          |  |  |

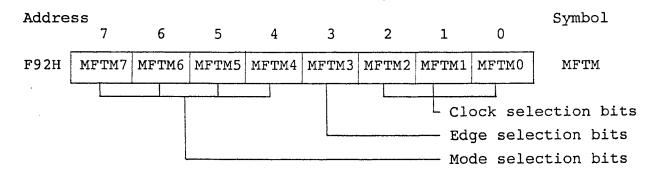

| F92H         | Multifunction timer mode register (MFTM)         | w   | -     | _                | 0     |                       |                                          |  |  |

| F98H         | Watch mode register (WM)                         | R/W | Δ     | -                | _     | mem.bit               | Only bit 3 can be tested bit-wise.       |  |  |

|              | •                                                | W   | -     | -                | 0     |                       |                                          |  |  |

| F9AH         | Multifunction timer con-<br>trol register (MFTC) | R/W | 0     | ٥                | -     | mem.bit               | (Note 1)                                 |  |  |

| F9CH         | Multifunction timer count register L (MFTL)      | R/W | -     | -                | 0     |                       |                                          |  |  |

| F9EH         | Multifunction timer<br>count register H (MFTH)   | R/W | -     | -                | o     |                       |                                          |  |  |

| FAOH         | Timer/event counter 0                            | W   | Δ     | -                |       | mem.bit               | Only bit 3 can be manipulated bit-wise.  |  |  |

|              | mode register (TMO)                              |     | -     | -                | •     |                       |                                          |  |  |

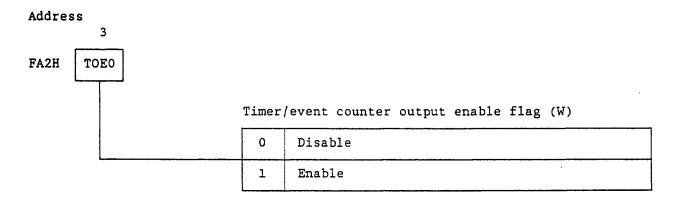

| FA2H         | (Note2)<br>TOE0                                  | w   | 0     | -                | _     | mem.bit               |                                          |  |  |

| <b>ГА</b> 4Н | Timer/event counter 0 count register (TO)        |     | -     | -                | 0     |                       |                                          |  |  |

| FA6H         | Timer/event counter 0 modulo register (TMODO)    | W   | -     | -                | o     |                       |                                          |  |  |

Note 1: Bit 3 (W): In read mode, 0 is read.

Bit 2, 1 (R/W)

Bit 0 (R): In write mode, written data becomes invalid.

2: TOE0: Timer/event counter 0 output enable flag (W)

Fig. 2-3 uPD75028(A) I/O Map (2/4)

| Address | Hard                                                                                           | ware n            | ame (s        | ymbol)    | R/W |       | of bit<br>manipu | -     | Bit mani-<br>pulation | Remarks                                        |  |  |   |

|---------|------------------------------------------------------------------------------------------------|-------------------|---------------|-----------|-----|-------|------------------|-------|-----------------------|------------------------------------------------|--|--|---|

|         | b3   b2                                                                                        |                   | ъ1            | ъ0        |     | l-bit | 4-bit            | 8-bit | addressing            |                                                |  |  |   |

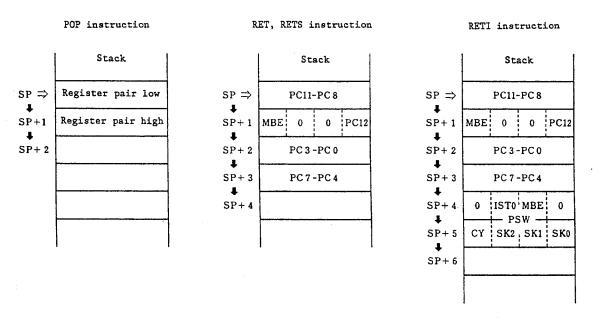

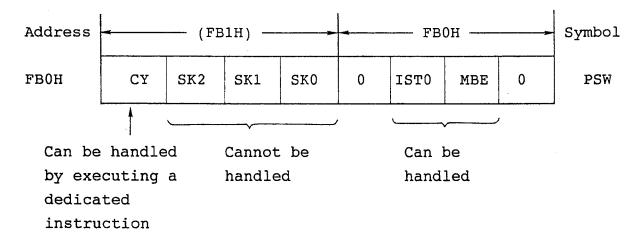

| FBOH    | 0                                                                                              | IST0              | MBE           | 0         | R/W | -     | o                |       |                       | Only bits 2 and 1 can be manipulated bit-wise. |  |  |   |

|         | Progra                                                                                         | m stat            | us word       | i (PSW)   | R   | -     | -                | 0     |                       |                                                |  |  | - |

| FB2H    | IME                                                                                            |                   |               |           | -   | -     | -                | -     | fmem.bit              | Operation by executing EI/DI instruction.      |  |  |   |

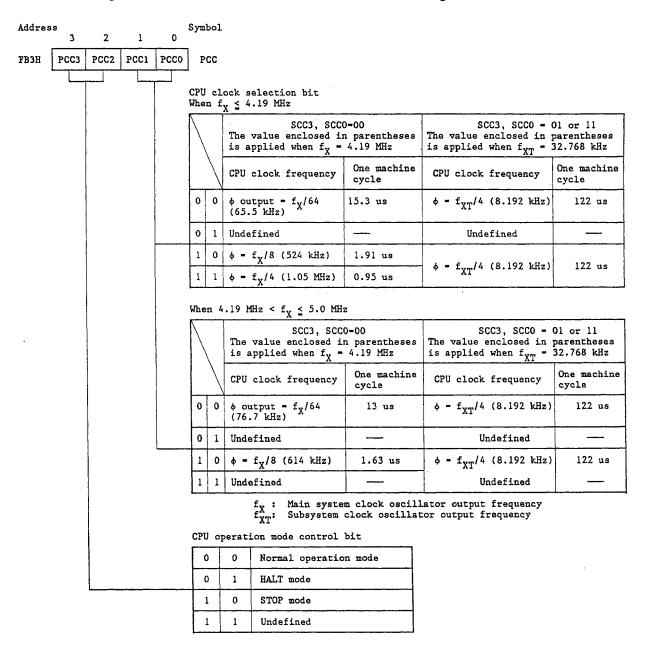

| FB3H    |                                                                                                | sor cl            | ock cor<br>C) | ntrol     | W   | -     | 0                | -     |                       |                                                |  |  |   |

| FB4H    | INTO u                                                                                         | ode re            | gister        | (IMO)     | W   | -     | 0                |       |                       | Bit 2 is fixed to 0.                           |  |  |   |

| FB5H    | INT1 u                                                                                         | ode re            | gister        | (IM1)     | W   | -     | 0                | _     |                       | Bits 3 to 1 are fixed to 0.                    |  |  |   |

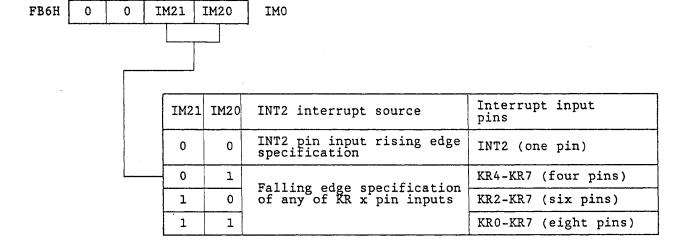

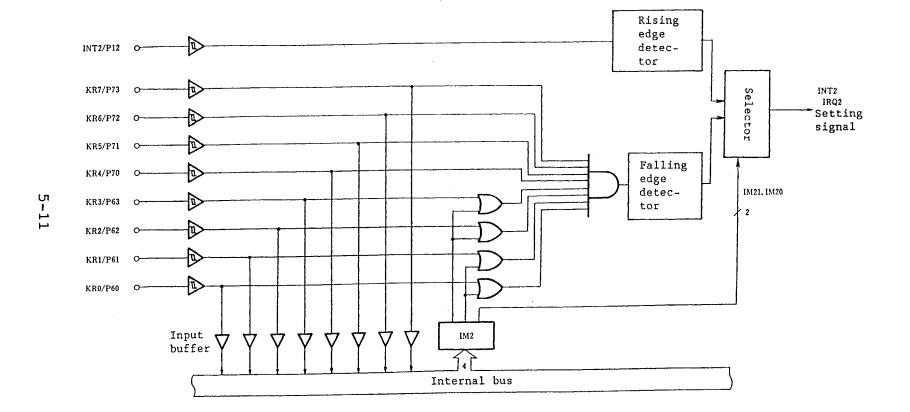

| FB6H    | INT2 mode register (IM2)                                                                       |                   |               |           | W   | -     | 0                |       |                       | Bits 3 and 2 are fixed to 0.                   |  |  |   |

| FB7H    |                                                                                                | a clock<br>er (SC | contro        | <b>ol</b> | น   | 0     | _                | _     |                       | Bits 2 and 1 are fixed to 0.                   |  |  |   |

| FB8H    | IE4                                                                                            | IRQ4              | IEBT          | IRQBT     | R/W | 0     | 0                | -     |                       |                                                |  |  |   |

| FBAH    |                                                                                                |                   | IEW           | IRQW      | R/W | 0     | 0                |       |                       |                                                |  |  |   |

| рввн    |                                                                                                |                   | LEMFT         | IRQMFT    | R/W | 0     | 0                | -     |                       |                                                |  |  |   |

| FBCH    |                                                                                                |                   | 1ETO          | IRQTO     | R/W | 0     | 0                |       | fmem.bit              |                                                |  |  |   |

| FBDH    |                                                                                                |                   | IECSI         | IRQCSI    | R/W | 0     | 0                | -     |                       |                                                |  |  |   |

| FBEH    | IE1                                                                                            | IRQ1              | IEO           | IRQO      | R/W | 0     | 0                |       |                       |                                                |  |  |   |

| FBFH    |                                                                                                |                   | IE2           | IRQ2      | R/W | 0     | 0                | Ī -   |                       |                                                |  |  |   |

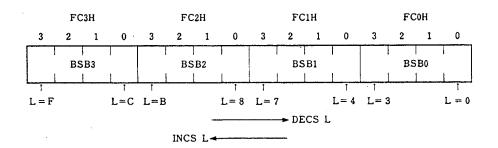

| FCOH    | Rit s                                                                                          | equenti           | al buf        | fer O     | R/W |       |                  | 1     |                       |                                                |  |  |   |

|         | Bit sequential buffer 0 (BSB0)  Bit sequential buffer 1 (BSB1)  Bit sequential buffer 2 (BSB2) |                   |               |           |     |       |                  |       |                       |                                                |  |  |   |

| FC1H    |                                                                                                |                   |               |           |     | 0     | 0                |       | mem.bit               |                                                |  |  |   |

| FC2H    |                                                                                                |                   |               |           |     | 0     | 0                |       | pmem.@L               |                                                |  |  |   |

| FC3H    | Bit s<br>(BSB3                                                                                 |                   | Lal buf       | fer 3     | R/W | 0     | 0                | 0     |                       |                                                |  |  |   |

Remarks 1: IExxx is an interrupt enable flag.

2: IRQxxx is an interrupt request flag.

Fig. 2-3 uPD75028(A) I/O Map (3/4)

| Address | Hardware name (symbol)                          |        |        |                  | R/W |          | of bit |       | Bit mani-<br>pulation | Remarks                                       |

|---------|-------------------------------------------------|--------|--------|------------------|-----|----------|--------|-------|-----------------------|-----------------------------------------------|

|         | ъ3                                              | b2     | ъ1     | ъ0               |     | l-bit    | 4-bit  | 8-bit | addressing            |                                               |

| FDOH    | Clock o                                         |        |        |                  | W   | -        | 0      | -     |                       |                                               |

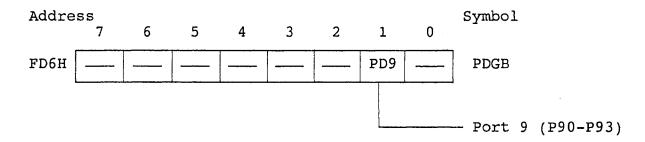

| FD6H    | Pull-do<br>ficatio<br>(PDGB)                    |        |        |                  | w   | -        | -      | o     |                       |                                               |

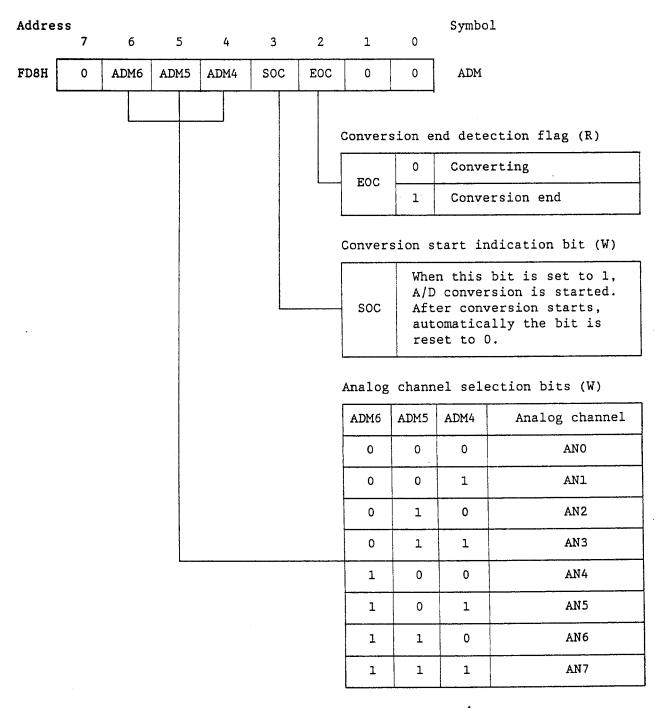

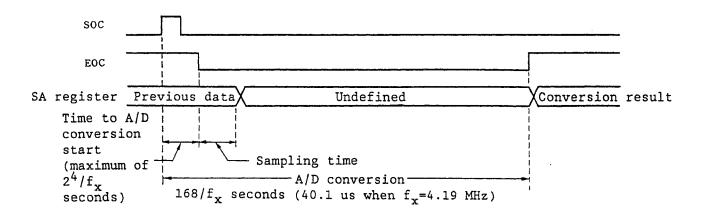

| FD8H    | soc                                             | EOC    |        |                  | R/W | Δ        | -      | 0     | mem.bit               | EOC R<br>SOC W                                |

|         | A/D cor<br>registe                              |        |        |                  | W   | -        | -      |       |                       |                                               |

| FDAH    | SA regi                                         | Lster  | (SA)   |                  | R   | -        | -      | 0     |                       |                                               |

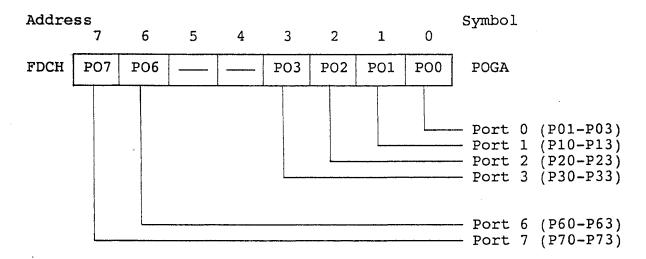

| FDCH    | Pull-up<br>fication<br>(POGA)                   |        |        |                  | W   | <u>-</u> | _      | o     |                       |                                               |

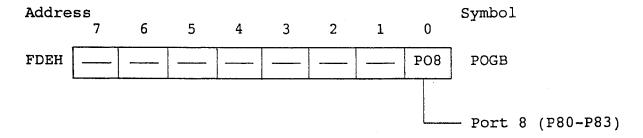

| .FDEH   | Pull-up<br>fication<br>(POGB)                   |        |        | peci-<br>group B | W   | -        | -      | 0     |                       |                                               |

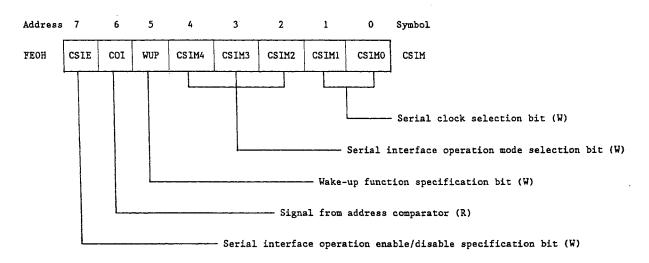

| FEOH    |                                                 |        |        |                  |     | _        | _      |       |                       |                                               |

|         | Serial<br>regist                                |        |        | ode              | R/W | Δ        | 0      | 0     | mem.bit               | Only bits 3 to 1 can be manipulated bit-wise. |

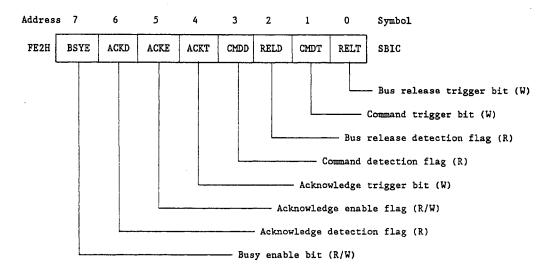

| FE2H    | SBI control register (SBIC)                     |        |        |                  |     | 0        | -      | -     | mem.bit               | All bits can be manipulated bit-wise.         |

| FE4H    | Serial<br>(SIO)                                 | I/O s  | hift r | egister          | R/W | -        | -      | 0     |                       |                                               |

| FE6H    | Slave (SVA)                                     | addres | s regi | ster             | W   | _        | -      | 0     |                       |                                               |

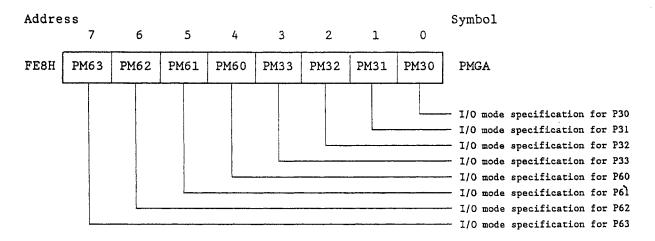

| PE8H    | PM33                                            | PM32   | PM31   | PM30             |     |          |        |       |                       |                                               |

|         | Port m<br>A (PMG                                |        | gister | group            | W   | -        | -      | 0     |                       |                                               |

|         | PM63                                            | PM62   | PM61   | PM60             |     |          |        |       |                       |                                               |

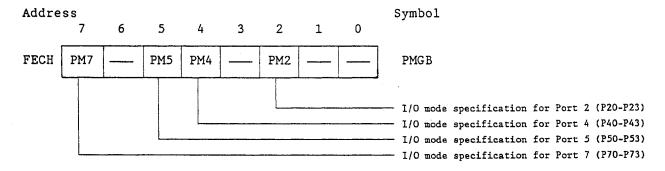

| FECH    | PM2                                             |        |        |                  |     |          |        |       |                       |                                               |

|         | Port mode register group B (PMGB)               |        |        | W                | -   | -        | 0      |       |                       |                                               |

| PERU    | PM7                                             |        | PM5    | PM4              | -   |          | -      |       | +                     |                                               |

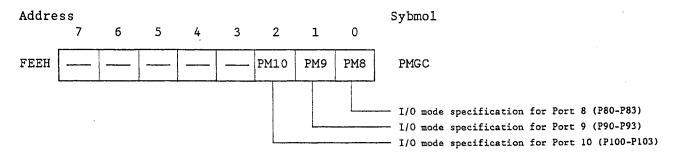

| FEEH    | PM10 PM9 PM8  Port mode register group C (PMGC) |        |        |                  |     | -        | -      | 0     |                       |                                               |

Fig. 2-3 uPD75028(A) I/O Map (4/4)

| Address        | Hardw  | ame (s | symbol) | R/W      |         | of bit<br>manipu |       | Bit mani-<br>pulation | Remarks             |   |

|----------------|--------|--------|---------|----------|---------|------------------|-------|-----------------------|---------------------|---|

|                | ъ3     | ъ2     | ъ1      | ъ0       |         | l-bit            | 4-bit | 8-bit                 | addressing          |   |

| FFOH           | Port 0 |        |         | (PORTO)  | R       | 0                | 0     |                       |                     |   |

| PF1H           | Port 1 |        |         | (PORT1)  | R       | 0                | 0     | _                     |                     |   |

| FF2H           | Port 2 |        |         | (PORT2)  | R/W     | 0                | o     |                       |                     |   |

| FF3H           | Port 3 |        |         | (PORT3)  | R/W     | 0                | 0     | _                     |                     |   |

| FF4H           | Port 4 |        |         | (PORT4)  | R/W     | 0                | 0     |                       |                     |   |

| FF5H           | Port 5 |        |         | (PORT5)  | R/W     | 0                | o     |                       |                     | · |

| (Note)<br>FF6H | KR3    | KR2    | KR1     | KRO      | R/W     |                  |       |                       | fmem.bit<br>pmem.@L |   |

| rron           | Port 6 |        |         | (PORT6)  | K/W     | 0                | o     | _                     |                     |   |

| (Note)<br>FF7H | KR7    | KR6    | KR5     | KR4      | D /11   |                  |       | •                     |                     |   |

| FF/R           | Port 7 |        | (PORT7) | R/W      | 0       | 0                |       |                       |                     |   |

| .FF8H          | Port 8 |        |         | (PORT8)  | 72 / 72 | o                | 0     |                       |                     |   |

| FF9H           | Port 9 |        |         | (PORT9)  | R/W     | ٥                | ٥     | -                     |                     |   |

| FFAH           |        |        |         | (PORT10) | R/W     | 0                | 0     |                       |                     |   |

| FFBH           | Port 1 | 1      |         | (PORT11) | R       | 0                | ٥     | -                     |                     |   |

Note: KR0-KR7 can be read only. Specify PORT6 or PORT7 during 4-bit parallel input.

#### 3. INTERNAL CPU FUNCTION

## 3.1 Program Counter (PC) · · · 13 bits

The program counter (PC) is a 13-bit binary counter which retains program memory address information.

Fig. 3-1 Program Counter Format

| 1 |      |      |      |     |     |     |     |     |     |     |     |     |     |    |

|---|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

|   | PC12 | PC11 | PC10 | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | PC |

| 1 |      |      | l    |     |     | Ţ   |     | l   | ĺ   | ŀ   | 1   | [ . |     |    |

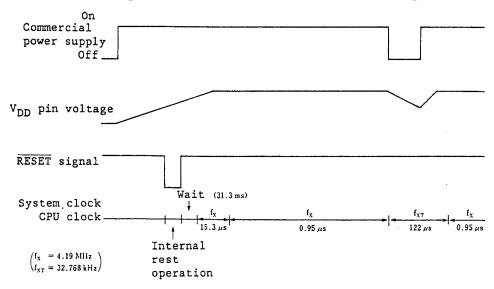

When the  $\overline{\text{RESET}}$  signal is generated, the low-order five bits of program memory address 0000H are set in PC12-PC8 and the contents of address 0001H are set in PC7-PC0 for initialization.

#### 3.2 Program Memory (ROM) · · · 8064 words x 8 bits

The program memory is 8064-word x 8-bit mask programmable ROM which stores programs, table data, etc.

The program memory is addressed by the program counter. Table data can be referenced by executing a table look-up instruction (MOVT).

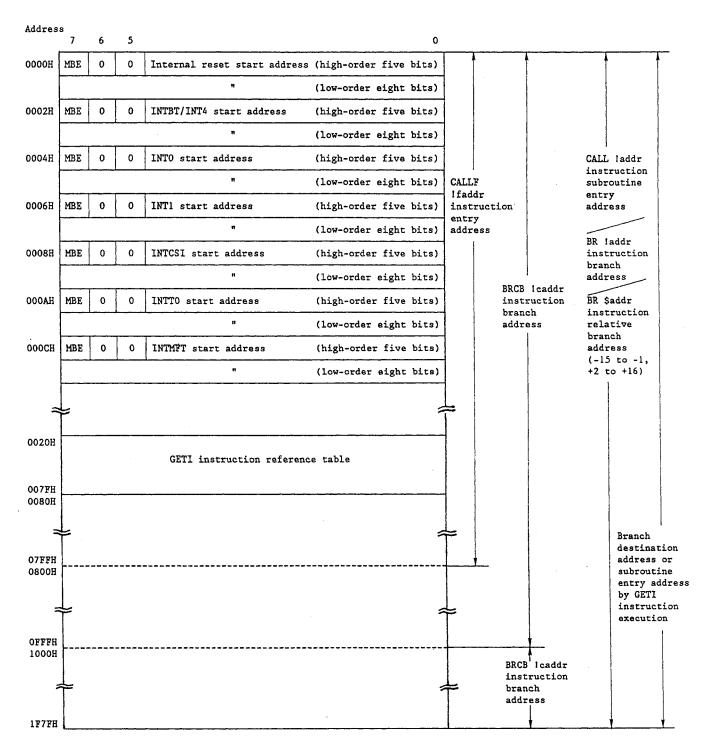

Fig. 3-2 shows the branch-possible address range when a branch instruction or subroutine call instruction is executed. Relative branch instruction (BR \$addr) enables a branch to address [PC contents -15 to -1, +2 to +16] independently of block boundaries.

Program memory addresses are 0000H-1F7FH; the following addresses are specially assigned: (Every area except for 0000H or 0001H can be used as normal program memory.)

#### • Addresses 0000H-0001H

Vector table into which the program start address and MBE setup value are written when the  $\overline{\text{RESET}}$  signal is generated. Reset start is enabled at any desired address.

#### Addresses 0002H-000DH

Vector table into which the program start address and MBE setup value are written when a vectored interrupt occurs. Interrupt processing can be started at any desired address.

Addresses 0020H-007FH

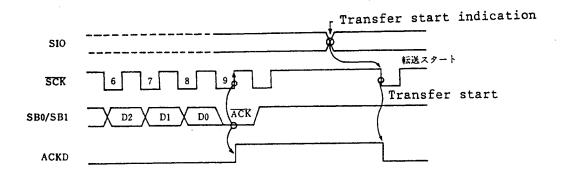

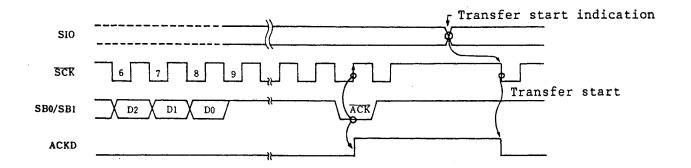

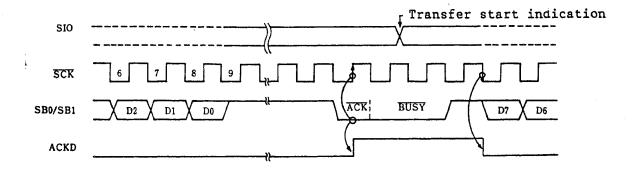

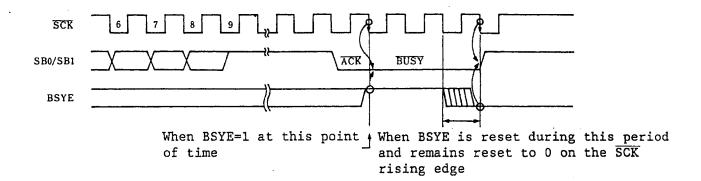

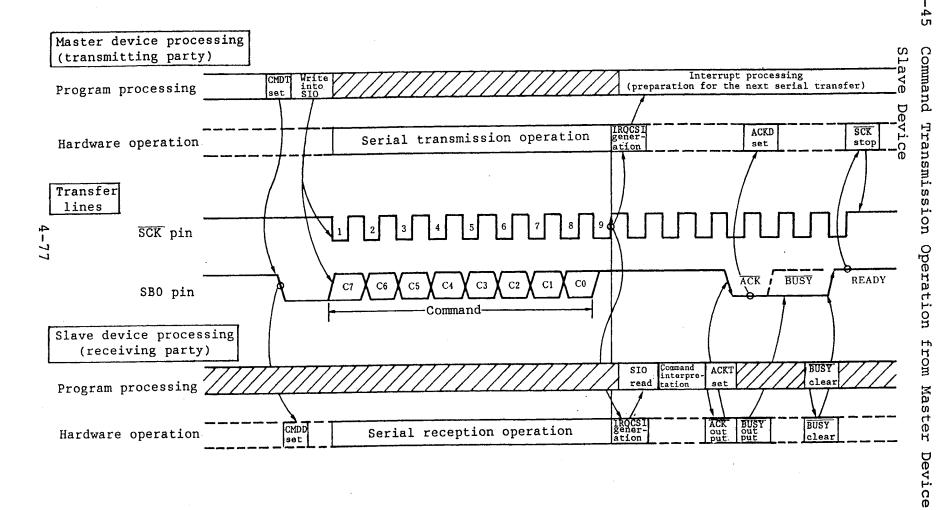

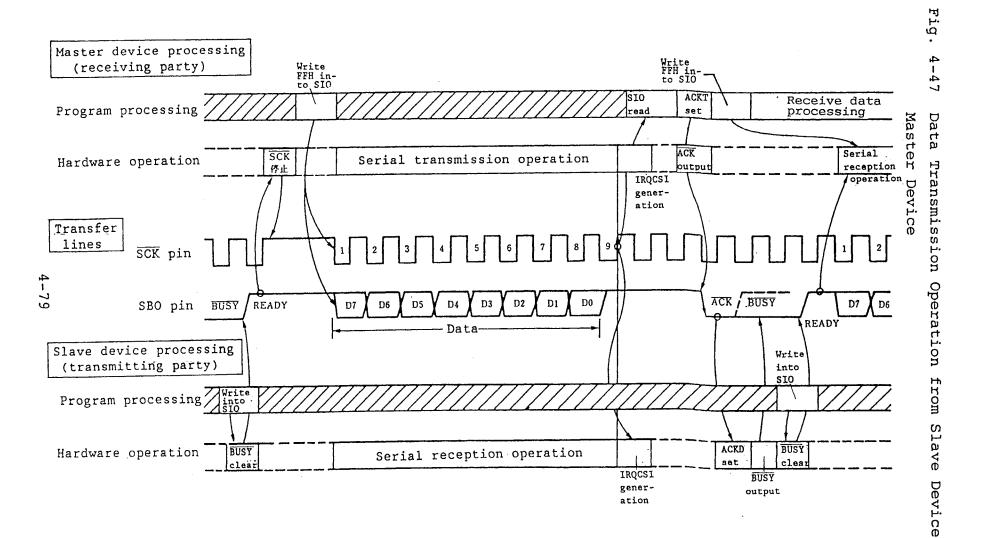

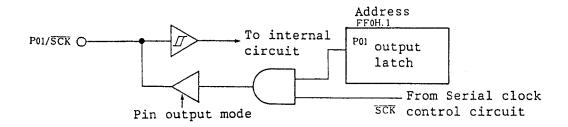

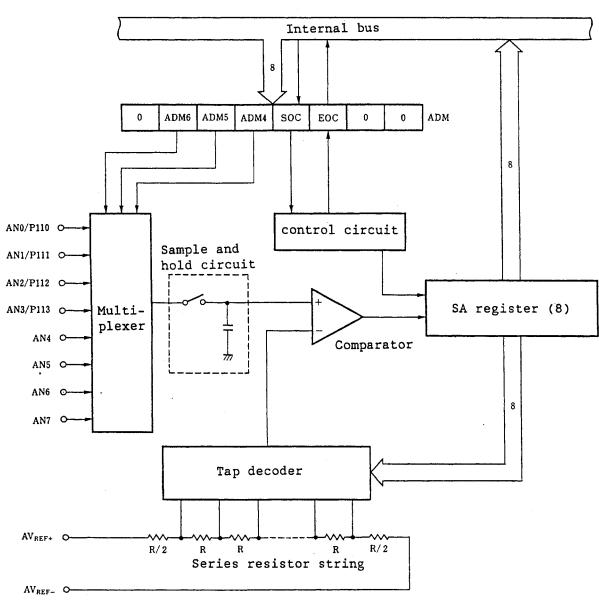

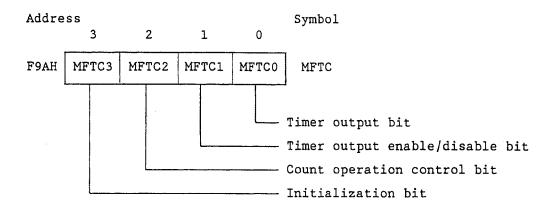

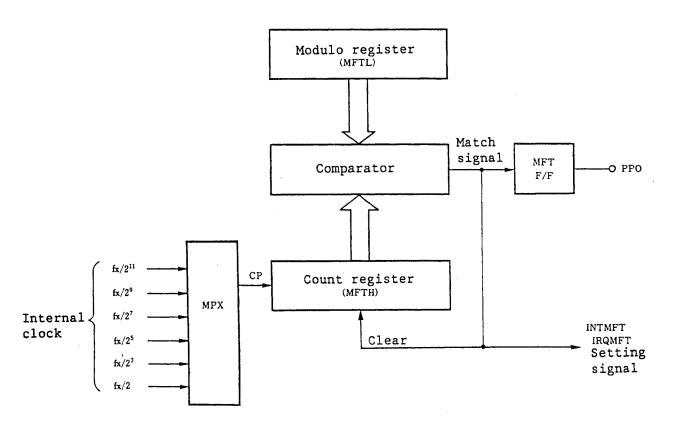

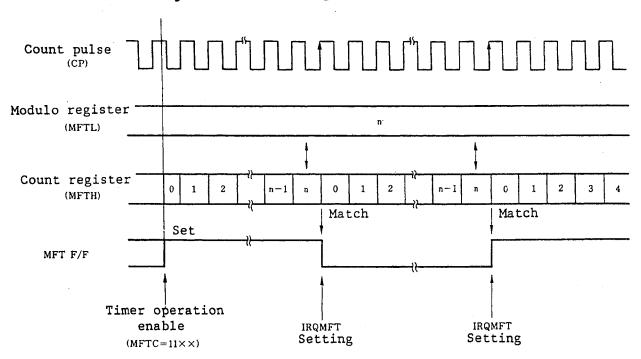

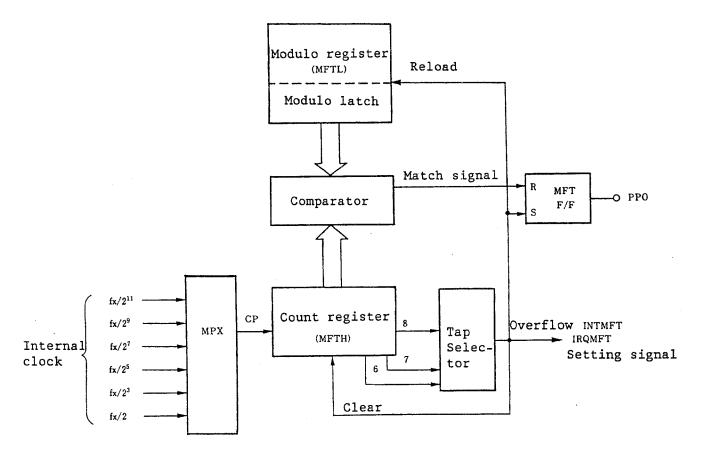

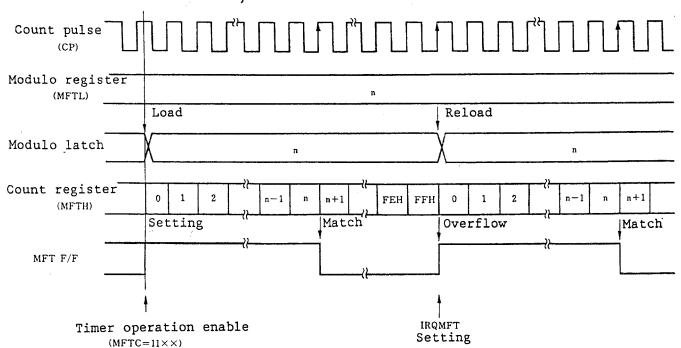

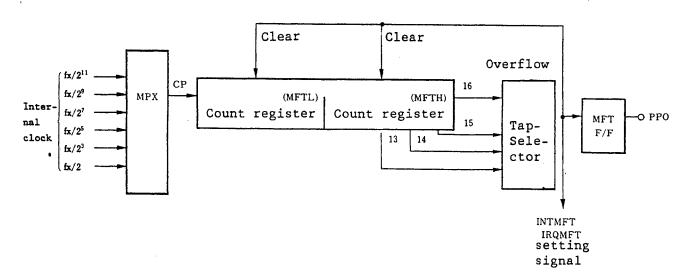

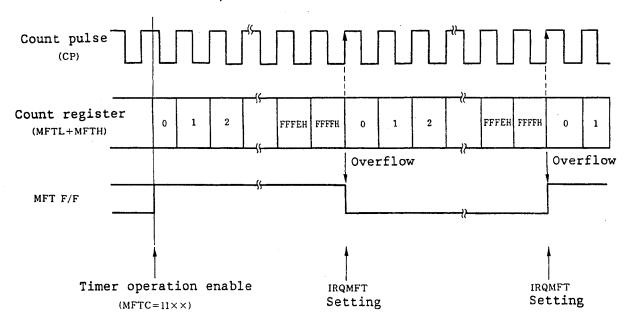

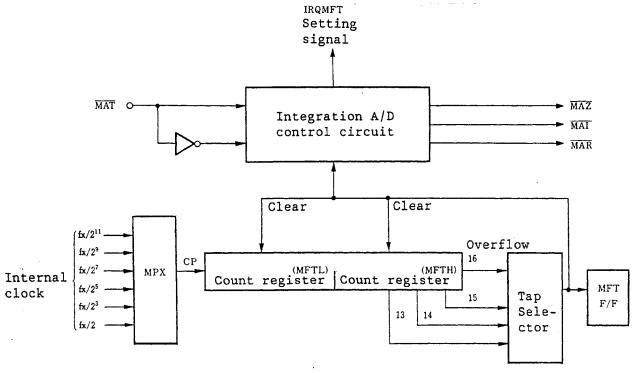

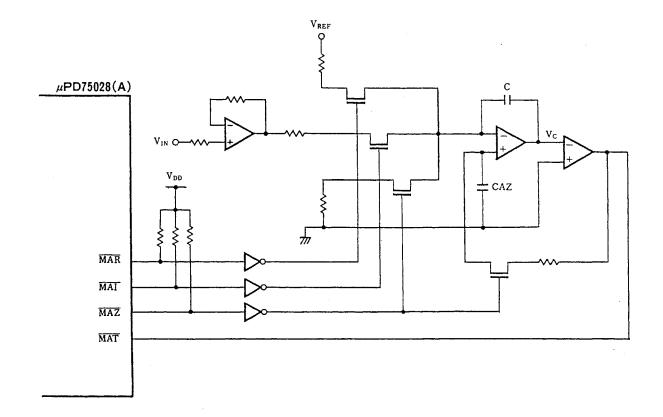

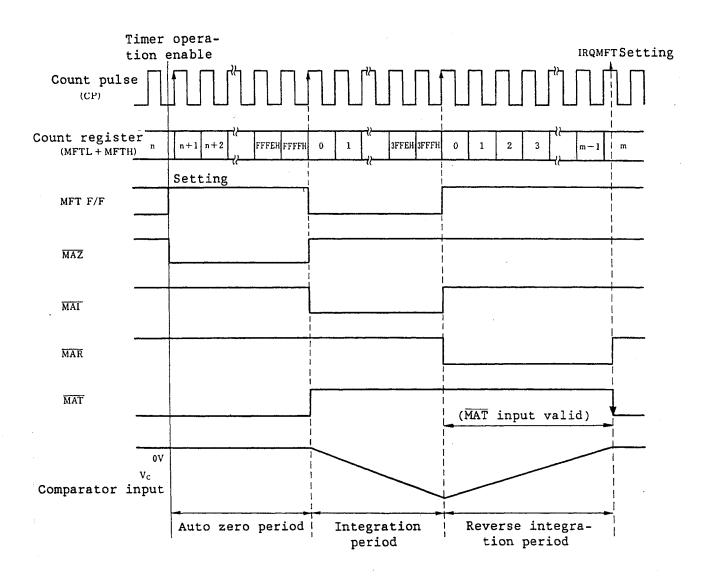

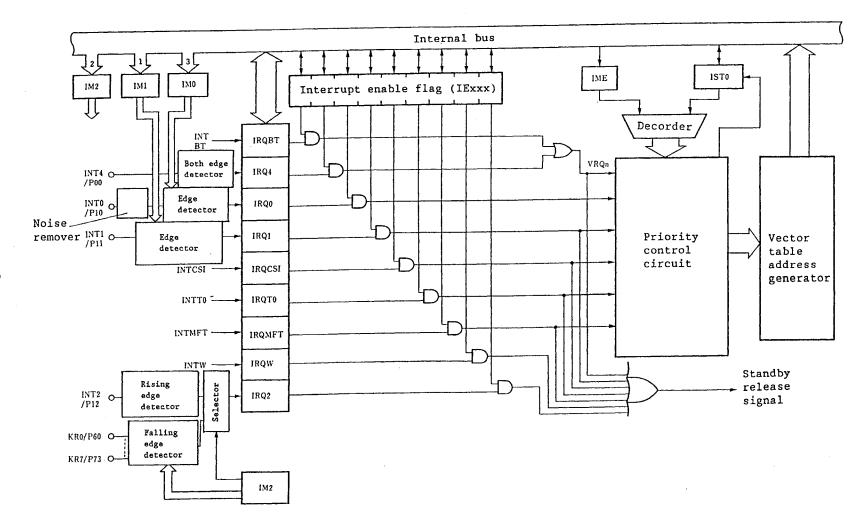

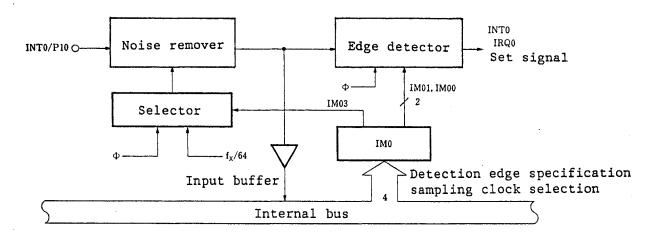

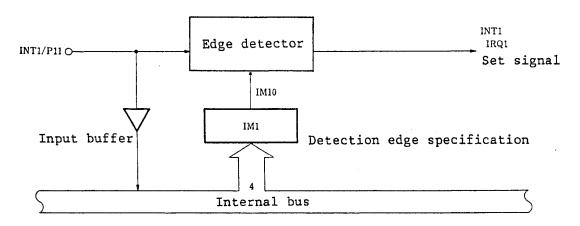

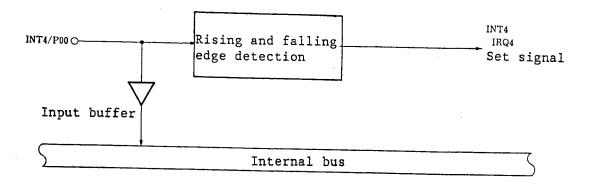

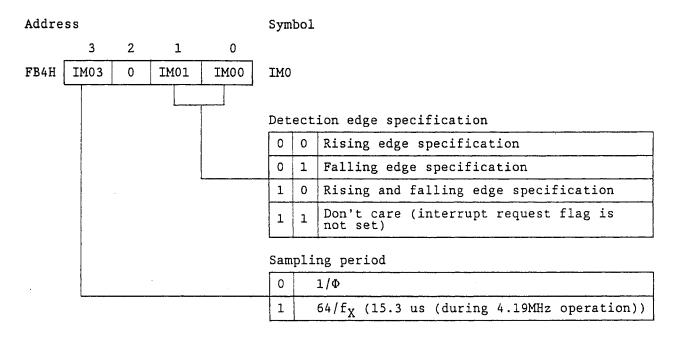

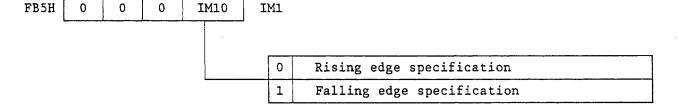

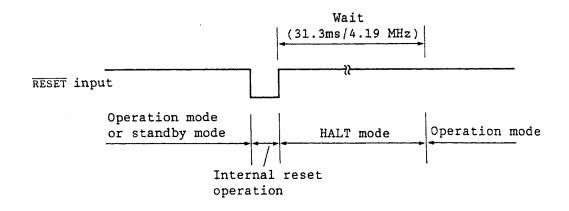

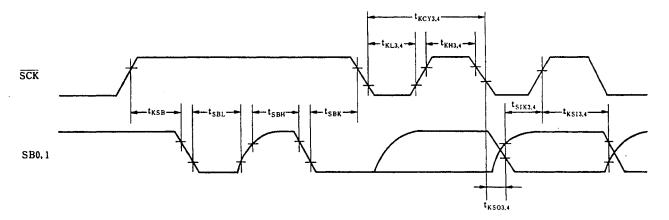

Table area referenced by executing GETI instruction(Note).