The instructions for the uPD7502 and uPD7503 are a subset of the uPD7500 SET A instructions.

6.1 Operand Format and Description

Operands are coded in the operand field of an instruction according to the format prescribed. For details of the operand format, refer to the assembler specifications.

| addr                    | 11-bit immediate data or label (uPD7502)<br>12-bit immediate data or label (uPD7503)                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| caddr                   | 11-bit immediate data or label                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| addr1<br>addr2<br>addr3 | 3, 4, 5, 6, BH, CH, EH, FH immediate data or label<br>3-bit immediate data or label (uPD7502)<br>4-bit immediate data or label (uPD7503)<br>0, 1, 4, 5, 6 immediate data or label |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| taddr1<br>taddr2        | OCOH to OCFH immediate data or label<br>ODOH to OFFH immediate data or label                                                                                                      | ć                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| mem                     | 7-bit immediate data or label (uPD7502)<br>8-bit immediate data or label (uPD7503)                                                                                                | M.Data:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| byte<br>n4<br>n3        | 8-bit immediate data or label<br>4-bit immediate data or label<br>3-bit immediate data or label                                                                                   | n and a second s |

| bit                     | 2-bit immediate data or label                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| pr                      | DL, DE, HL-, HL+, HL                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 |  | 2 | L | e | 9 | e | n | ď |

|---|--|---|---|---|---|---|---|---|

|---|--|---|---|---|---|---|---|---|

Α: Accumulator D register D: E register Ε: H register Н: L register L: Register pair (DE) DE: Register pair (DL) DL: Register pair (HL) HL: Register pair (DE, HL-, HL+, HL, DL) pr: SP: Stack pointer Program counter PC: Bit n of the program counter PCn: Carry flag C: PSW: Program status word Shift register \$10: MOD: Modulo register CT: Count register Immediate data for byte n4 or n3 In: Immediate data for addr, caddr, addr2, taddr1, or Pn: taddr2 Immediate data for bit Bn: Immediate data for mem, addrl, addr3, or addr4 Dn: Immediate data for pr Rn: Data addressed by xx (xx): Hexadecimal data xxH:

## 6.3 Instruction Execution Time

The instructions provided for the uPD7502 and uPD7503 are one or two byte long. One-byte instructions are executed in one machine cycle, and 2-byte instructions are executed in two machine cycles, with some exceptions. One machine cycle is equal to one cycle for system clock é. When the RC oscillation frequency or CL1 input frequency is 200 kHz (when the operating voltage is 5 V), one machine cycle is 10 us.

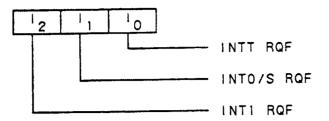

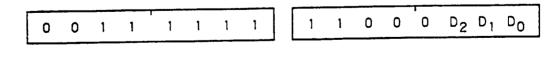

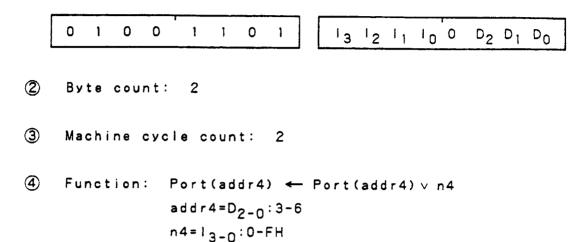

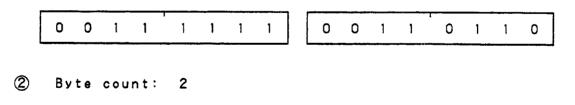

When the skip condition for an instruction having the skip function is established, a skip takes place during one machine cycle, irrespective of whether the instruction to be skipped is a 1-byte or 2-byte instruction. In this case, the instruction execution time is one machine cycle longer than that required when no skip is performed. 6.4 Explanation of Instructions The instructions are explained in terms of: Instruction code (binary)  $\bigcirc$ Byte count 2 (3) Machine cycle count (4) Function Example (5) 6 Note 6.4.1 Load/store instructions LAI n4 (Load A with Immediate) 0 0 0 1 13 2 1 10 Instruction code:  $\bigcirc$ Byte count: 1 2 Machine cycle count: 1 3 Function: A ← n4 n4=1<sub>3-0</sub>:0-FH **(4)** Four-bit immediate data n4 is loaded into the accumulator. The instruction has a string effect. When the same instruction is coded more than once successively, the second and subsequent instructions are processed as NOPs.

(5) Example: Subroutines that add 1, 2, and 3 to the data at address Z in binary notation

```

ZAD1:LAI 1;(1)

ZAD2:LAI 2;(2)

ZAD3:LAI 3;(3)

LHLI Z

ASC

NOP

XAM HL

RT

```

(1) When ZAD1 is called

The value 1 is loaded into the accumulator by LAI 1, and the subsequent instructions (2) and (3) change to NOP, and 1 is added to the data at data memory address Z in binary.

(2) When ZAD2 is called

The value 2 is loaded into the accumulator by LAI 2, and instruction (3) changes to NOP, and 2 is added to the data at data memory address Z in binary.

(3) When ZAD3 is called

The value 3 is loaded into the accumulator by LAI 3, and 3 is added to the data at data memory address Z in binary. LDI n4 (Load D with Immediate)

Instruction code:

|     | 0 0 1 1 1 1 0 0 0 1 0 3 2 1 0                                                                                           |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     |                                                                                                                         |  |  |  |  |  |

| 2   | Byte count: 2                                                                                                           |  |  |  |  |  |

| 3   | Machine cycle count: 2                                                                                                  |  |  |  |  |  |

| 4   | Function: D <del>&lt;-</del> n4 n4=l <sub>3-0</sub> :0-FH<br>Four-bit immediate data n4 is loaded to<br>the D register. |  |  |  |  |  |

| LEI | n4 (Load E with Immediate)                                                                                              |  |  |  |  |  |

| 1   | Instruction code:                                                                                                       |  |  |  |  |  |

|     | 0 0 1 1 1 1 0 0 0 0 0 13 12 11 10                                                                                       |  |  |  |  |  |

| 2   | Byte count: 2                                                                                                           |  |  |  |  |  |

| 3   | Machine cycle count: 2                                                                                                  |  |  |  |  |  |

| 4   | Function: E ← n4 n4=1 <sub>3-0</sub> :0-FH<br>Four-bit immediate data n4 is loaded to<br>the E register.                |  |  |  |  |  |

C. Mary

LHI n4 (Load H with immediate)

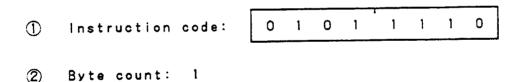

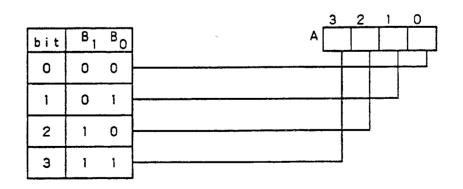

$\bigcirc$ Instruction code: 0 0 1 1 13 12 11 10 0 0 1 1 1 1 1 0 (2) Byte count: 2 (3) Machine cycle count: 2 ④ Function: H ← n4 n4=1<sub>3-0</sub>:0-FH Four-bit immediate data n4 is loaded in the H register. LLI n4 (Load L with Immediate) Instruction code: 0 0 1 1 0 0 13 12 11 10 1 1 1 0 0 1 2 Byte count: 2 3 Machine cycle count: 2 4 Function: L 🖛 n4 n4=1<sub>3-0</sub>:0-FH Four-bit immediate data n4 is loaded to the L register. LAM pr (Load A with Memory) 0 1 0 R<sub>4</sub> 0 0 R<sub>1</sub> R<sub>0</sub>  $\bigcirc$ Instruction code: 2 Byte count: 1

3 Machine cycle count: 1 or 2 (when a skip is made)

## (4) Function: A ← (pr)

When pr=HL+: skip if L=O When pr=HL-: skip if L=FH

| pr  | <sup>R</sup> 4 | R <sub>1</sub> | Ro |

|-----|----------------|----------------|----|

| DL  | 0              | 0              | 0  |

| DE  | 0              | 0              | 1  |

| HL- | 1              | 0              | 0  |

| HL+ | 1              | 0              | 1  |

| нι  | 1              | 1              | 0  |

The contents of the data memory location addressed by a register pair are loaded into the accumulator. If HL+ is specified for pr, the L register is incremented after data loading. If the result is O, the following instruction is skipped. If HL- is specified for pr, the the L register is decremented after data loading. If the result is FH, the following instruction is skipped.

6 Note: LAM HL-, LAM HL+, and LAM HL can be coded as LDS, LIS, and L, respectively (each having no operand).

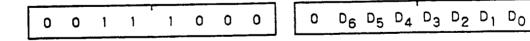

LADR mem (Load A Direct): uPD7502

(1) Instruction code:

② Byte count: 2

.

(3) Machine cycle count: 2

(

| 4    | Function:   | A ← (mem) mem=D <sub>7-0</sub> :00H-7FH    |

|------|-------------|--------------------------------------------|

|      |             | The contents of the data memory location   |

|      |             | addressed by 7-bit immediate data mem are  |

|      |             | loaded into the accumulator.               |

| 5    | Example:    | The data at memory address 6FH is loaded   |

|      |             | into the accumulator.                      |

|      |             | LADR 6FH:A ← (6FH)                         |

| LADR | mem (Load / | A Direct): uPD7503                         |

| 1    | Instruction | n code:                                    |

|      | 0 0 1       | $D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$          |

|      |             |                                            |

| 2    | Byte count  | : 2                                        |

| 3    | Machine cy  | cle count: 2                               |

| 4    | Function:   | A ← (mem) mem=D <sub>7-0</sub> :00H-DFH    |

|      |             | The contents of the data memory location   |

|      |             | addressed by 8-bit immediate data mem are  |

|      |             | loaded into the accumulator.               |

| LDEI | byte (Load  | DE with Immediate)                         |

| 1    | Instructio  | n code:                                    |

|      | 0 1 0       | 0 1 1 1 1 1 7 6 5 4 3 2 1 0                |

| •    | _           |                                            |

| 2    | Byte count  | : 2                                        |

| 3    | Machine cy  | cle count: 2                               |

| 4    | Function:   | DE - byte byte=1 <sub>7-0</sub> :00H-FFH   |

|      |             | Eight-bit immediate data byte is loaded to |

|      |             | register pair DE.                          |

LHLI byte (Load HL with Immediate)

1 Instruction code:

| Byte count: 2<br>Machine cycle count: 2<br>Function: HL ← byte byte=1 <sub>7-0</sub> :00H-FFH<br>Eight-bit immediate data byte is load<br>register pair HL. This instruction h<br>string effect. When more than one LH<br>LHLT instruction is coded successivel<br>the second and subsequent instruction |        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Function: HL - byte byte=1 <sub>7-0</sub> :00H-FFH<br>Eight-bit immediate data byte is load<br>register pair HL. This instruction h<br>string effect. When more than one LH<br>LHLT instruction is coded successivel                                                                                     |        |

| Eight-bit immediate data byte is load<br>register pair HL. This instruction h<br>string effect. When more than one LH<br>LHLT instruction is coded successive!                                                                                                                                           |        |

| register pair HL. This instruction h<br>string effect. When more than one LH<br>LHLT instruction is coded successive!                                                                                                                                                                                    |        |

| string effect. When more than one LH<br>LHLT instruction is coded successive!                                                                                                                                                                                                                            | ed to  |

| LHLT instruction is coded successivel                                                                                                                                                                                                                                                                    | as a   |

|                                                                                                                                                                                                                                                                                                          | ill or |

|                                                                                                                                                                                                                                                                                                          | у,     |

| the second and subsequent institution                                                                                                                                                                                                                                                                    |        |

| processed as NOP instructions.                                                                                                                                                                                                                                                                           |        |

|                                                                                                                                                                                                                                                                                                          |        |

| Example:                                                                                                                                                                                                                                                                                                 |        |

| LDHLI: LHLI 12H ; *                                                                                                                                                                                                                                                                                      |        |

| LHLI 34H ;SKIP *                                                                                                                                                                                                                                                                                         |        |

| LHLI 56H ;SKIP SKIP *<br>LHLI 78H ;SKIP SKIP SKIP *                                                                                                                                                                                                                                                      |        |

|                                                                                                                                                                                                                                                                                                          |        |

|                                                                                                                                                                                                                                                                                                          |        |

| ; RESULT HL=12H;34H;56H;76H;5AH                                                                                                                                                                                                                                                                          |        |

| LHLTB: LHLT TABL1 ; *                                                                                                                                                                                                                                                                                    |        |

| LHLT TABL2 : SKIP *                                                                                                                                                                                                                                                                                      |        |

| LHLT TABL3 ;SKIP SKIP *                                                                                                                                                                                                                                                                                  |        |

| LHLT TABL4 ; SKIP SKIP SKIP *                                                                                                                                                                                                                                                                            |        |

| LHLI OO ; SKIP SKIP SKIP SKIP                                                                                                                                                                                                                                                                            |        |

| ; RESULT HL=8CH,4BH,2AH,19H                                                                                                                                                                                                                                                                              |        |

| ORG OCOH                                                                                                                                                                                                                                                                                                 |        |

| TABL1: DB 8CH<br>TABL2: DB 4BH                                                                                                                                                                                                                                                                           |        |

| TABLE: DB CAH                                                                                                                                                                                                                                                                                            |        |

| TABL4: DB 19H                                                                                                                                                                                                                                                                                            |        |

| ;                                                                                                                                                                                                                                                                                                        |        |

is sie in mun

Caution: \* is an entry address. The value to be loaded in register pair HL varies depending on the entry address.

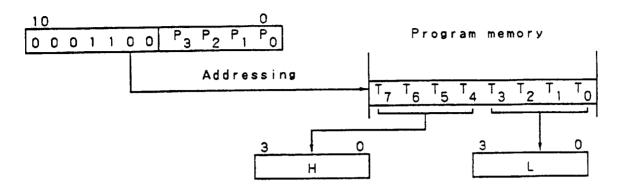

LHLT taddr1 (Load HL with Table data): uPD7502

| 1 | Instruction code: $1  1  0  0  P_3  P_2  P_1  P_0$                                                                                             |

|---|------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Byte count: 1                                                                                                                                  |

| 3 | Machine cycle count: 2                                                                                                                         |

| 4 | Function: HL $\leftarrow$ ROM (0001100P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> )<br>taddr1=0,CH,P <sub>3-0</sub> :0C0H-0CFH |

The high-order four bits of the table data  $(T_{7-0})$  in the program memory location addressed by 4-bit immediate data  $(P_{3-0})$ (the value of the high-order four bits of the address is fixed to OCH) are loaded to the H register, and the low-order four bits of the table data are loaded in the L register. This instruction has a string effect. When more than one LHLI or LHLT instruction is coded successively, the second and subsequent instructions are processed as NOP instructions.

The program counter is not affected by the execution of this instruction. An area at addresses OCOH to OCFH is allocated to the table area for the LHLT instruction. Before the LHLT instruction is executed, table data must be programmed with an assembler pseudo instruction in the table area. Only values ranging from OCOH to OCFH can be coded as taddr1.

(5) Example: Subroutines that load table data to register pair HL

| TCAL1:<br>TCAL2:<br>TCAL3: | LHLT<br>LHLT<br>LHLT<br>LHLI<br>RT | TABL1<br>TABL2<br>TABL3<br>00 | ; (1)<br>; (2)<br>; (3)<br>; (4) |

|----------------------------|------------------------------------|-------------------------------|----------------------------------|

|                            | •                                  |                               |                                  |

|                            | ORG                                | осон                          |                                  |

| TABL1:<br>TABL2:<br>TABL3: | DB<br>DB<br>DB                     | 8CH<br>4BH<br>2AH             | :LHLT TABLE AREA                 |

(1) When TCAL1 is called

The H register is loaded with eight, the L register is loaded with CH, and the following instructions (2), (3), and (4) change to NOPs, then TCAL1 returns to the calling program.

(2) When TCAL2 is called

The H register is loaded with four, the L register is loaded with BH, and the following instructions (3) and (4) change to NOPs, then TCAL2 returns to the calling program. (3) When TCAL3 is called

The H register is loaded with two, the L register is loaded with AH, and the following instruction (4) changes to NOP, then TCAL3 returns to the calling program.

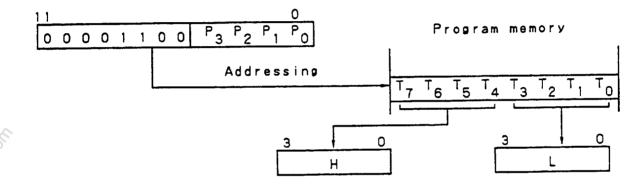

LHLT taddr1 (Load HL with Table data): uPD7503

| 1 | Instruction code: 1 1 0 0 P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub>                                                                                                                                                                                                                                              |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Byte count: 1                                                                                                                                                                                                                                                                                                                      |

| 3 | Machine cycle count: 2                                                                                                                                                                                                                                                                                                             |

| 4 | Function: HL $\leftarrow$ ROM (00001100P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> )<br>taddr1=0,CH,P <sub>3-0</sub> :0C0H-0CFH                                                                                                                                                                                    |

|   | The high-order four bits of table data<br>(T <sub>7-O</sub> ) at the program memory location<br>addressed by 4-bit immediate data (P <sub>3-O</sub> )<br>(the higher bits of the address are fixed<br>to OCH) are loaded to the H register, and<br>the low-order four bits of the table data<br>are loaded to the L register. This |

|   | instruction has a string effect. When ar                                                                                                                                                                                                                                                                                           |

processed as NOPs.

n an LHLI or LHLT instruction is coded more than once successively, the second and subsequent LHLI or LHLT instructions are

The program counter is not affected by this instruction. An area at addresses OCOH to OCFH is allocated to the table area for the LHLT instruction. Before an LHLT instruction is executed, table data must be programmed in this area with an assembler pseudo instruction.

Only values ranging from OCOH to OCFH can be coded as taddr1.

3 Machine cycle count: 2

4 Function: A  $\leftarrow$  ROM(PC<sub>10-6</sub>,0,C,A)<sub>H</sub> (HL)  $\leftarrow$  ROM(PC<sub>10-6</sub>,0,C,A)<sub>L</sub> The high-order four bits of the table data  $(T_{7-0})$  at a program memory location are loaded to the accumulator, and the low-order four bits of the table data are loaded in the data memory location addressed by register pair HL. The program memory location of the table data is addressed by the high-order five bits  $(PC_{10-6})$  of the program counter, the carry flag (C), and the contents of the accumulator (A) (bit 5 of the ROM address is always O).

Before LAMT is executed, necessary table data must be programmed with an assembler pseudo instruction.

The program counter is not affected by the LAMT instruction.

The table area for this instruction can be placed in any current page (indicated by  $PC_{10-6}$  when the LAMP instruction is executed). Note that when the LAMT instruction is used at the last address of a page ( $PC_{5-0}=3FH$ ), the high-order bits ( $P_{10-6}$ ) of an address for table reference indicates the next page.

LAMTL (Load A and Memory with Table data): uPD7503 only

(1) Instruction code:

|   | 0 0 1 1 1 1 1 1 0 0 1 1 0 1 0 0                                                                                                                                                     |  |  |  |  |  |  |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 2 | Byte count: 2                                                                                                                                                                       |  |  |  |  |  |  |

| 3 | Machine cycle count: 3                                                                                                                                                              |  |  |  |  |  |  |

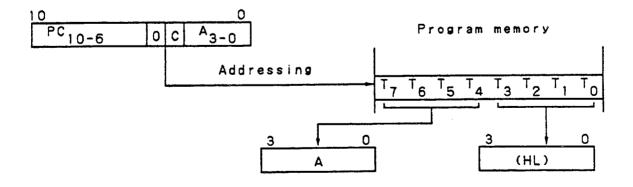

| 4 | Function: A $\leftarrow$ ROM(PC <sub>11-8</sub> , A <sub>3-0</sub> , (HL) <sub>3-0</sub> )H<br>(HL) $\leftarrow$ ROM(PC <sub>11-8</sub> , A <sub>3-0</sub> , (HL) <sub>3-0</sub> )L |  |  |  |  |  |  |

|   | The high-order four bits of the table                                                                                                                                               |  |  |  |  |  |  |

the high-order four bits of the table data  $(T_{7-0})$  at a program memory location is loaded to the accumulator, and the low-order 4 bits are loaded to a data memory location addressed by register pair HL. The location of the table data is addressed by the contents of the data memory location addressed by the high-order four bits (PC<sub>11-8</sub>) of the program counter, accumulator contents  $(A_{3-0})$ , and register pair HL.

Before the LAMTL instruction is executed, necessary table data must be programmed with an assembler pseudo instruction.

The program counter is not affected by the LAMTL instruction. Note that if the LAMTL instruction is executed with  $PC_{7-0}$ = address FFH, the value of  $PC_{11-8}$ when the LAMTL instruction is executed plus one is used to address the table area.

TAD (Transfer A to D)

1 Instruction code:

0 0 1 0 1 0 1 0 1 0 0.1 1 1 1 1 2 Byte count: 2 3 Machine cycle count: 2 **(4**) Function: D - A The contents of the accumulator are transferred to the D register.

TAE (Transfer A to E)  $\bigcirc$ Instruction code: 1 1 1 0 1 0 0 0 1 0 1 0 1 0 0 1 (2) Byte count: 2 3 Machine cycle count: 2 Function: E 🖛 A 4 The contents of the accumulator are transferred to the E register. TAH (Transfer A to H) (1)Instruction code: 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 2 Byte count: 2 Machine cycle count: 2 3 Function: H 🖛 A 4 The contents of the accumulator are transferred to the H register. TAL (Transfer A to L)  $\bigcirc$ Instruction code: 0 1 1 1 1 0 1 0 0 1 1 0 1 0 0 1

② Byte count: 2

③ Machine cycle count: 2

④ Function: L ← A The contents of the accumulator are transferred to the L register.

TDA (Transfer D to A)

(1) Instruction code:

0 1 1 -1 0 1 0 1 1 1 1 0 0 1 1 0 2 Byte count: 2 3 Machine cycle count: 2 Function: A 🔶 D **(4)** The contents of the D register are transferred to the accumulator. TEA (Transfer E to A)  $\bigcirc$ Instruction code: 1 0 0 0 1 0 1 1 0 1 1 1 С 0 1 1 2 Byte count: 2 Machine cycle count: 2 3 Function: A 🖛 E 4 The contents of the E register are transferred to the accumulator.

THA (Transfer H to A)  $\bigcirc$ Instruction code: 1 0 1 1 0 0 1 1 1 1 1 0 1 0 1 1 2 Byte count: 2 3 Machine cycle count: 2 **(4**) Function: A ← H The contents of the H register are transferred to the accumulator. TLA (Transfer L to A)  $\bigcirc$ Instruction code: ٥ 0 0 0 1 1 1 1 1 0 1 1 1 0 1 1 2 Byte count: 2 3 Machine cycle count: 2 **(4)** Function: A 🔶 L The contents of the L register are transferred to the accumulator. XAD (Exchange A with D) 1Instruction code: 0 1 0 0 1 0 1 0 2 Byte count: 1 3 Machine cycle count: 1

(4) Function:  $A \leftrightarrow D$ The contents of the accumulator and D register are exchanged. XAE (Exchange A with E)  $\bigcirc$ Instruction code: 0 1 0 0 1 0 1 1 (2) Byte count: 1 (3) Machine cycle count: 1 (4) Function:  $A \leftrightarrow E$ The contents of the accumulator and E register are exchanged. XAH (Exchange A with H)  $\bigcirc$ Instruction code: 0 1 1 1 1 0 0 1 ② Byte count: 1 (3) Machine cycle count: 1 (4) Function: A ↔ H The contents of the accumulator and H register are exchanged. XAL (Exchange A with L) Instruction code: 0 1 1 0 1 1 1 1 ② Byte count: 1 3 Machine cycle count: 1

④ Function: A ↔ L The contents of the accumulator and L register are exchanged.

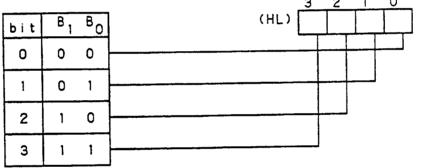

XAM pr (Exchange A with Memory)

| 1 | Instruction | code: | 0 | 1 | 0 | R <sub>4</sub> | 0 | 1 | R <sub>1</sub> | RO |

|---|-------------|-------|---|---|---|----------------|---|---|----------------|----|

|   |             |       |   |   |   |                |   |   |                |    |

② Byte count: 1

(3) Machine cycle count: 1/2 (when a skip is made)

④ Function: A ↔ (pr) pr=DL,DE,HL-,HL+,HL When pr=HL+: Skip if L=0 When pr=HL-: Skip if L=FH

| pr  | R <sub>4</sub> | R1 | R <sub>O</sub> |

|-----|----------------|----|----------------|

| DL  | 0              | 0  | 0              |

| DE  | 0              | 0  | 1              |

| HL- | 1              | 0  | 0              |

| HL+ | 1              | 0  | 1              |

| HL  | 1              | 1  | 0              |

The contents of the accumulator and the contents of the data memory location addressed by a register pair are exchanged. When HL+ is specified for pr, the data is exchanged, then the L register is incremented by one. When the L register content becomes 0, the succeeding instruction is skipped. When HL- is specified for pr, the data is exchanged, then the L register is decremented by one. When the L register content becomes FH, the succeeding instruction is skipped. (6) Note: XAM HL-, XAM HL+, and XAM HL can be written as XDS, XIS, and X, respectively (each having no operands).

XADR mem (Exchange A with Memory Direct): uPD7502

() Instruction code:

0 0 1 1 1 0 0 1 0 D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub>

② Byte count: 2

3 Machine cycle count: 2

- ④ Function: A ↔ (mem) mem=D<sub>6-0</sub>:00H-7FH The contents of the accumulator and the contents of the data memory location addressed by 7-bit immediate data mem are exchanged.

- ⑤ Example: The contents of a data memory location at address 2FH are transferred to address 10H. LADR 2FH ;A ← (2FH) XADR 10H ;A ← (10H)

$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$

XADR mem (Exchange A with Memory Direct): uPD7503

1 Instruction code:

0 0 1 1 1 0 0 1

- ② Byte count: 2

- 3 Machine cycle count: 2

④ Function: A → (mem) mem=D<sub>7-0</sub>:00H-DFH The contents of the accumulator and the contents of the data memory location addressed by 8-bit immediate data mem are exchanged.

XHDR mem (Exchange H with Memory Direct): uPD7502

Instruction code:

Contraction of the second

|      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2    | Byte count: 2                                                                                                                                                                                   |

| 3    | Machine cycle count: 2                                                                                                                                                                          |

| 4    | Function: H ←→ (mem) mem=D <sub>6-0</sub> :00H-7FH<br>The contents of the H register and the<br>contents of the data memory location<br>addressed by 7-bit immediate data mem are<br>exchanged. |

| XHDR | (mem (Exchange H with Memory Direct): uPD7503                                                                                                                                                   |

| 1    | Instruction code:                                                                                                                                                                               |

|      | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                            |

| 2    | Byte count: 2                                                                                                                                                                                   |

| 3    | Machine cycle count: 2                                                                                                                                                                          |

| 4    | Function: H ↔ (mem) mem=D <sub>7-0</sub> :00H-DFH<br>The contents of the H register and the<br>contents of the data memory location<br>addressed by 8-bit immediate data mem are                |

|      | exchanged.                                                                                                                                                                                      |

XLDR mem (Exchange L with Memory Direct): uPD7502  $\bigcirc$ Instruction code: 0 D<sub>6</sub> D<sub>5</sub> D<sub>4</sub> D<sub>3</sub> D<sub>2</sub> D<sub>1</sub> D<sub>0</sub> 0 0 1 1 0 1 1 1 ② Byte count: 2 3 Machine cycle count: 2 (4) Function:  $L \iff (mem) mem=D_{6-0}:00H-7FH$ The contents of the L register and the contents of the data memory location addressed by 7-bit immediate data mem are exchanged. XLDR mem (Exchange L with Memory Direct): uPD7503  $\bigcirc$ Instruction code:  $\mathsf{D}_7 \hspace{0.1in} \mathsf{D}_6 \hspace{0.1in} \mathsf{D}_5 \hspace{0.1in} \mathsf{D}_4 \hspace{0.1in} \mathsf{D}_3 \hspace{0.1in} \mathsf{D}_2 \hspace{0.1in} \mathsf{D}_1 \hspace{0.1in} \mathsf{D}_0$ 0 0 1 1 1 0 1 1 ② Byte count: 2 3 Machine cycle count: 2 **(4)** Function:  $L \iff (mem) mem=D_{7-0}:00H-DFH$ The contents of the L register and the contents of the data memory location addressed by 8-bit immediate data mem are exchanged.

6.4.2 Operation instructions

AISC n4 (Add Immediate to A, Skip if Carry)

0 0 0 0 13 12 11 10 Instruction code:  $\bigcirc$ Byte count: 1 2 (3) Machine cycle: 1/2 (when a skip is made) ④ Function: A ↔ A+n4;Skip if carry. n4=1<sub>3-0</sub>:0-FH Four-bit immediate data n4 is added to the accumulator in binary. When a carry is produced, a skip is performed. The carry flag is not affected. Note: When n4 = 0, an NOP instruction is executed. 6 ASC (Add Memory to A, Skip if Carry) 0 1 1 1 0 1 1 1 Instruction code:  $\bigcirc$ Byte count: 1 2 Machine cycle count: 1/2 (when a skip is made) 3 Function: A ← A+(HL);Skip if carry. 4 The contents of the data memory location addressed by register pair HL are added to the accumulator in binary. When a carry is produced as a result of the addition, a skip is performed. The carry flag is not affected.

ACSC (Add Memory to A with Carry, Skip if Carry)

| 1   | Instruction code: 0 1 1 1 1 1 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | Byte count: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | Machine cycle: 1/2 (when a skip is made)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4   | Function: A,C ← A+(HL)+C;Skip if carry.<br>The contents of the data memory location<br>addressed by register pair HL are added<br>to the accumulator in binary (including<br>carry flag). When a carry is produced as<br>a result of the addition, the carry flag<br>is set and a skip is made. When no carry<br>is produced, the carry flag is reset, and<br>if the following instruction is an AISC<br>instruction, the skip condition for the<br>AISC instruction is inhibited. (A skip<br>is performed when a carry is produced.) |

|     | Only the AISC instruction is affected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EXL | (Exclusive-Or Logic A and Memory)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1   | Instruction code: 0 1 1 1 1 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | Byte count: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3   | Machine cycle count: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4   | Function: A ← A ← (HL)<br>The contents of the accumulator are<br>exclusive-ORed with the contents of the<br>data memory location addressed by<br>register pair HL, then the result is                                                                                                                                                                                                                                                                                                                                                 |

stored in the accumulator.

ANL (And Logic A and Memory)

Instruction code: (1)0 0 0 1 1 0 1 1 1 1 1 1 0 0 1 1 Byte count: 2 2 Machine cycle count: 2 3  $A \leftarrow A \land (HL)$ Function: 4 The contents of the accumulator are ANDed with the contents of the data memory location addressed by the register pair HL, then the result is stored in the .accumulator. ORL (Or Logic A and Memory) Instruction code:  $\bigcirc$ 1 0 1 1 0 1 .0 1 1 1 1 1 1 0 0 1 Byte count: 2 2 Machine cycle count: 2 3  $A \leftarrow A \lor (HL)$ Function: **(4)** The contents of the accumulator are ORed with the contents of the data memory location addressed by register pair HL, then the result is stored in the accumulator.

6.4.3 Accumulator manipulation instruction

| СМА | (Complement A)                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------|

| 1   | Instruction code: 0 1 1 1 1 1 1 1                                                                          |

| 2   | Byte count: 1                                                                                              |

| 3   | Machine cycle count: 1                                                                                     |

| 4   | Function: A - A<br>One's complement of the accumulator<br>contents is obtained. (Each bit is<br>inverted.) |

| 5   | Example: When A=5<br>3 2 1 0                                                                               |

|     | Before execution 0101 A                                                                                    |

|     | After execution 1010 A                                                                                     |

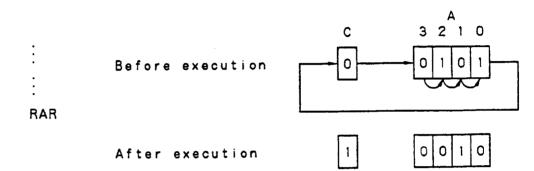

| RAR | (Rotate A Right)                                                                                           |

| 1   | Instruction code:                                                                                          |

|     | 0 0 1 1 1 1 1 1 1 1 0 0 1 1                                                                                |

| 2   | Byte count: 2                                                                                              |

| 3   | Machine cycle count: 2                                                                                     |

(4) Function:  $A_{n-1} \leftarrow A_n$  (n=1-3)  $C \leftarrow A_0$   $A_3 \leftarrow C$ The contents of the accumulator, including the carry flag, are rotated one bit to the right.

(5) Example:

6.4.4 Carry flag manipulation instructions

RC (Reset Carry)

① Instruction code:

② Byte count: 1

3 Machine cycle count: 1

④ Function: C ← 0 The carry flag is reset.

SC (Set Carry)

(1) Instruction code:

② Byte count: 1

|       | 3    | Machine cycle count: 1                                                                                     |

|-------|------|------------------------------------------------------------------------------------------------------------|

|       | 4    | Function: C <del>&lt; 1</del><br>The carry flag is set.                                                    |

| 6.4.5 | Incr | ement/decrement instructions                                                                               |

|       | IES  | (Increment E, Skip if E=O)                                                                                 |

|       | 1    | Instruction code: 0 1 0 0 1 0 0 1                                                                          |

|       | 2    | Byte count: 1                                                                                              |

|       | 3    | Machine cycle count: 1/2 (when a skip is made)                                                             |

|       | 4    | Function: E — E+1;Skip if E=0<br>The E register is incremented. When the<br>result is E=0, a skip is made. |

|       | ILS  | (Increment L, Skip if L=0)                                                                                 |

|       | 1    | Instruction code: 0 1 0 1 1 0 0 1                                                                          |

|       | 2    | Byte count: 1                                                                                              |

|       | 3    | Machine cycle count: 1/2 (when a skip is made)                                                             |

|       | 4    | Function: L — L+1;Skip if L=0<br>The L register is incremented. When the<br>result is L=0, a skip is made. |

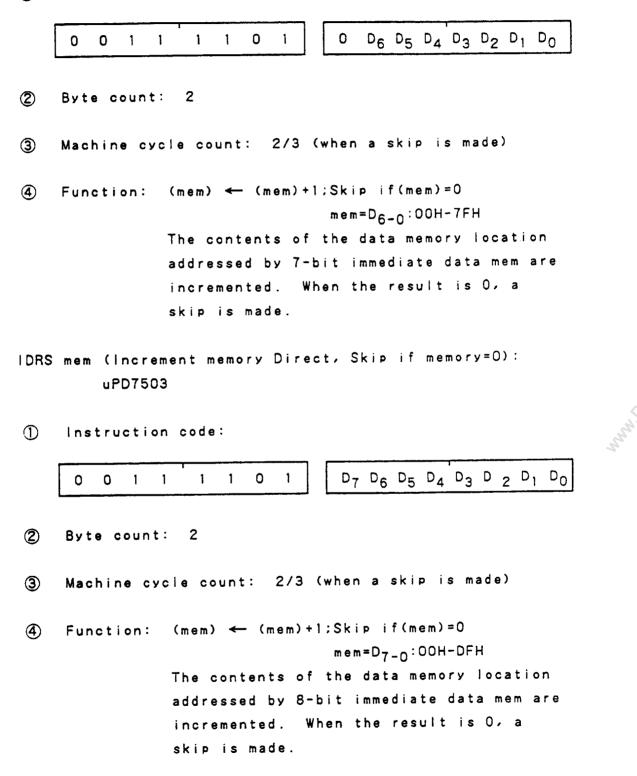

IDRS mem (Increment memory Direct, Skip if memory=0): uPD7502

(1) Instruction code:

DES (Decrement E, Skip if E=FH) Instruction code: 0 1 0  $\bigcirc$ 0 0 1 0 0 2 Byte count: 1 3 Machine cycle count: 1/2 (when a skip is made) 4 Function: E ← E-1:Skip if E=FH The E register is decremented, and when the decrement results in E=FH, a skip is made. DLS (Decrement L, Skip if L=FH) Instruction code: 0 1 0 1 1 0 0 0 2 Byte count: 1 Machine cycle count: 1/2 (when a skip is made) 3 4 Function: L ← L-1:Skip if L=FH The L register is decremented. When the decrement results in L=FH, a skip is made.

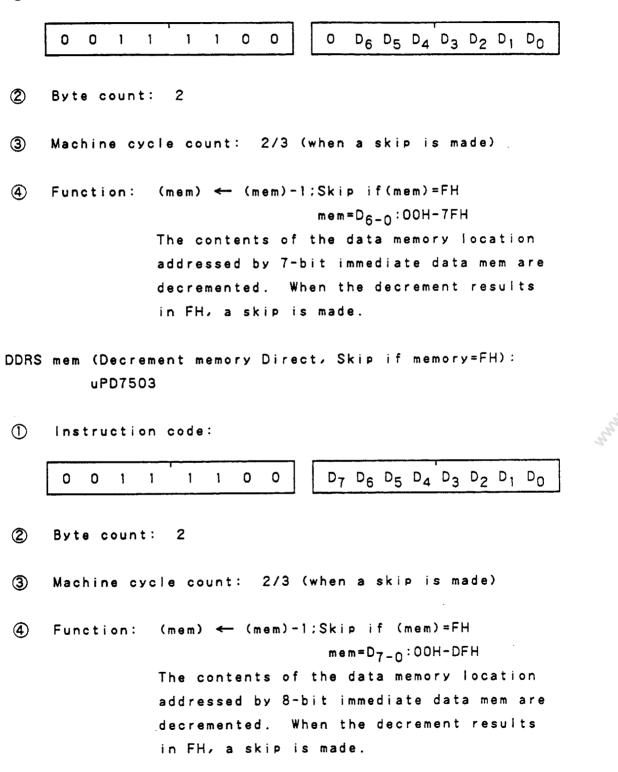

DDRS mem (Decrement memory Direct, SKip if Memory=FH): uPD7502

() Instruction code:

6.4.6 Memory bit manipulation instructions

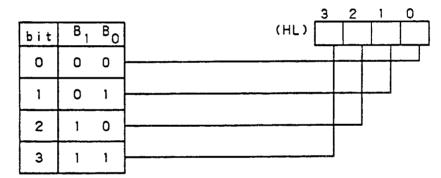

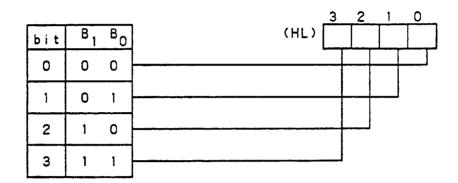

RMB bit (Reset Memory Bit)

Instruction code: 0 1 1 0 1 0 B<sub>1</sub> B<sub>0</sub>

Byte count: 1

Machine cycle count: 1

Function: (HL)bit ← 0 bit=B<sub>1-0</sub>:0-3 A particular bit at the data memory location addressed by register pair HL is reset. The bit to be reset is specified by 2-bit immediate data bit.

The bits other than the specified bit are left unchanged.

0 1

0

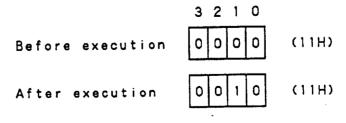

(5) Example: Bit 2 at data memory address 10H is reset.

LHLI 10H RMB 2  $;(10H)_2 \leftarrow 0$ 3 2 1 0 Before execution 0 1 1 1 (10)

After execution

(10н)

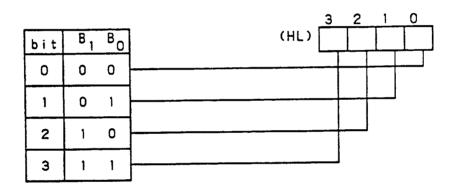

SMB bit (Set Memory Bit)

Instruction code: 0 1 1 0 1 1 B<sub>1</sub> B<sub>0</sub>

Byte count: 1

Machine cycle count: 1

Function: (HL)bit ← 1 bit=B<sub>1-0</sub>:0-3

A particular bit at the data memory location addressed by register pair HL is set. The bit to be set is specified by 2-bit immediate data bit.

The bits other than the specified bit are left unchanged.

5 Example: Bit 1 at data memory address 11H is set.

LHLI 11H SMB 1 ;(11H)<sub>1</sub> ← 1

```

6.4.7 Jump instructions

```

JMP addr (Jump): uPD7502  $\bigcirc$ Instruction code: 0 0 1 0 0 P<sub>10</sub> P<sub>9</sub> P<sub>8</sub> P<sub>7</sub> P<sub>6</sub> P<sub>5</sub> P<sub>4</sub> P<sub>3</sub> P<sub>2</sub> P<sub>1</sub> P<sub>0</sub> (2) Byte count: 2 (3) Machine cycle count: 2 Function:  $PC_{10-0} \leftarrow P_{10-0}$  addr= $P_{10-0}$ :000H-7FFH 4 A jump is made to the address indicated by 11-bit immediate data addr. JMP addr (Jump): uPD7503  $\bigcirc$ Instruction code: 1 0 P<sub>11</sub> P<sub>10</sub> P<sub>9</sub> P<sub>8</sub> P<sub>7</sub> P<sub>6</sub> P<sub>5</sub> P<sub>4</sub> P<sub>3</sub> P<sub>2</sub> P<sub>1</sub> P<sub>0</sub> 0 0 (2) Byte count: 2 3 Machine cycle count: 2 Function:  $PC_{11-0} \leftarrow P_{11-0}$  addr= $P_{11-0}$ :000H-FFFH 4 A jump is made to the address indicated by 12-bit immediate data addr. JCP addr (Jump in the Current Page): uPD7502 1 0 P5 P4 P3 P2 P1 P0 (1) Instruction code: (2) Byte count: 1

(3) Machine cycle count: 1

(4) Function:  $PC_{5-0} \leftarrow P_{5-0}$  addr= $PC_{10-6}$ ,  $P_{5-0}$ :000H-7FFH A jump is made. The destination address is obtained by replacing the low-order six bits of the program counter ( $PC_{5-0}$ ) with 6-bit immediate data  $P_{5-0}$ . The high-order five bits of the program counter ( $PC_{10-6}$ ) are not affected.

A value different from the current contents of  $PC_{1D-6}$  cannot be coded for addr.

(5) Example:

| ROM | Address |      |   |           |

|-----|---------|------|---|-----------|

| 108 |         |      |   |           |

| 109 | JCP     | 13BH | : | NON ERROR |

| 10A |         |      |   |           |

| ÷   |         |      |   |           |

| 13B |         |      |   |           |

| 13C | JCP     | 150H | ; | ERROR     |

| ÷   |         |      |   |           |

| 1FF | JCP     | 230H | ; | NON ERROR |

| 200 |         |      |   |           |

|     |         |      |   |           |

(6) Note: The PC contents indicates the address next to the JCP instruction while a JCP instruction is being executed. For example, when a JCP instruction is executed at 1FFH, the PC indicates 200H, and so a jump to address 230H is allowed.

N.ON

JCP addr (Jump in the Current Page): uPD7503

- 1 Instruction code: 1 0  $P_5 P_4 P_3 P_2 P_1 P_0$ 2 Byte count: 1 3 Machine cycle count: 1 4 Function:  $PC_{5-0} \leftarrow P_{5-0}$  addr= $PC_{11-6} P_{5-0}$ :000H-FFFH

- A jump is made to an address obtained by replacing the low-order six bits of the program counter ( $PC_{5-0}$ ) with 6-bit immediate data  $P_{5-0}$ . The high-order six bits of the program counter ( $PC_{11-6}$ ) are not affected.

1

A value different from the current contents of  $PC_{11-6}$  cannot be coded for addr.

JAM addr2 (Jump with A and Memory): uPD7502

(1) Instruction code:

0 0 1 1 1 1 1

$0 0 0 1 0 P_2 P_1 P_0$

- 2 Byte count: 2

- (3) Machine cycle count: 2

- 4 Function:  $PC_{10-8} \leftarrow P_{2-0}$ ,  $PC_{7-4} \leftarrow A_{3-0}$ ,  $PC_{3-0} \leftarrow (HL)$  addr $2=P_{2-0}:0-7$

The high-order three bit  $(PC_{10-8})$  of the program counter are replaced by 3-bit immediate data addr2, the intermediate four bits  $(PC_{7-4})$  are replaced by the accumulator contents, and the low-order four bits  $(PC_{3-0})$  are replaced by the contents of the data memory location addressed by register pair HL. A jump to the resultant address is then made. This means that the jump destination varies within the 256-address space depending on the accumulator and data memory contents.

JAM addr2 (Jump with A and Memory): uPD7503

(1) Instruction code:

|   | $0 0 1 1 1 1 1 1 0 0 0 1 P_3 P_2 P_1 P_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Byte count: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3 | Machine cycle count: 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4 | Function: $PC_{11-8} \leftarrow P_{3-0}$ , $PC_{7-4} \leftarrow A_{3-0}$ ,<br>$PC_{3-0} \leftarrow (HL)$ addr $2=P_{3-0}:0-FH$<br>The high-order four bits of the program<br>counter ( $PC_{11-8}$ ) are replaced with 4-bit<br>immediate data addr2, the intermediate<br>four bits of the program counter ( $PC_{7-4}$ )<br>are replaced with the accumulator<br>contents, and the low-order four bits<br>( $PC_{3-0}$ ) are replaced with the contents of<br>the data memory location addressed by<br>register pair HL. A jump to the<br>resultant address is then made. This<br>means that the jump destination varies<br>within the 256-address space depending on |

the accumulator and data memory contents.

6.4.8 Subroutine stack control instructions

CALL caddr (Call Subroutine): uPD7502

1 Instruction code:

| 0 0 1 1 0 P <sub>10</sub> P <sub>9</sub> P <sub>8</sub> P <sub>7</sub> P <sub>6</sub> P <sub>5</sub> P <sub>4</sub> P <sub>3</sub> P <sub>2</sub> P <sub>1</sub> P <sub>0</sub> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

- 2 Byte count: 2

- 3 Machine cycle count: 2

- (4) Function:  $(SP-1) \leftarrow PC_{7-4}$ ,  $(SP-2) \leftarrow PC_{3-0}$ ,  $(SP-3) \leftarrow PSW$ ,  $(SP-4) \leftarrow 0$ ,  $PC_{10-8}$  $PC_{10-0} \leftarrow P_{10-0}$ ,  $SP \leftarrow SP-4$  $caddr=P_{10-0}$ :000H-7FFH

The contents of the program counter (return address) and PSW are saved in the data memory location (stack) addressed by the stack pointer (SP), then a jump is made to the address indicated by 11-bit immediate data caddr.

CALL caddr (Call Subroutine): uPD7503

① Instruction code:

0 0 1 1 0 P<sub>10</sub> P<sub>9</sub> P<sub>8</sub>

P7 P6 P5 P4 P3 P2 P1 P0

- ② Byte count: 2

- 3 Machine cycle count: 2

(4) Function: (SP-1)  $\leftarrow PC_{7-4}$ , (SP-2)  $\leftarrow PC_{3-0}$ , (SP-3)  $\leftarrow PSW$ , (SP-4)  $\leftarrow PC_{11-8}$ ,  $PC_{11-0} \leftarrow 0, P_{10-0}$ , SP  $\leftarrow$  SP-4 caddr=P<sub>10-0</sub>:000H-7FFH

> The contents of the program counter (return address) and PSW are saved in the data memory location (stack) addressed by the stack pointer (SP), then a jump is made to the address indicated by 11-bit immediate data caddr.

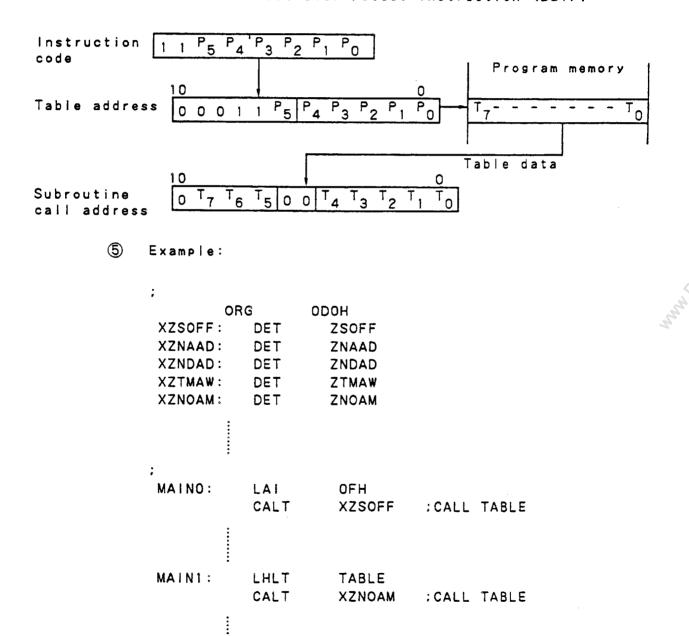

CALT taddr2 (Call Table): uPD7502

1 1 P<sub>5</sub> P<sub>4</sub> P<sub>3</sub> P<sub>2</sub> P<sub>1</sub> P<sub>0</sub> (1) Instruction code: 2 Byte count: 1 3 Machine cycle count: 2 Function: (SP-1)  $\leftarrow PC_{7-4}$ , (SP-2)  $\leftarrow PC_{3-0}$ , 4  $(SP-3) \leftarrow PSW, (SP-4) \leftarrow 0, PC_{10-8}$  $PC_{9-7,4-0} \leftarrow ROM(00011P_5P_4P_3P_2P_1P_0)$  $PC_{11,10,6,5} \leftarrow 0$ SP ← SP-4 taddr2=00011P5P4P3P2P1P0:0D0H-0FFH The contents of the program counter (return address) and PSW are saved in the data memory location (stack) addressed by the stack pointer (SP), 8-bit table data  $(T_{7-0})$  at the table address  $(00011P_5P_4P_3P_2P_1P_0)$  specified in the instruction is loaded into the program counter in form of  $0T_7T_6T_500T_4T_3T_2T_1T_0$ , then a jump is made.

Be sure to code a table address in the operand of the CALT instruction.

The table area for the CALT instruction is assigned to addresses ODOH to OFFH. Before the CALT instruction is executed, data for the subroutine call address must be programmed in this address with an assembler pseudo instruction (DET).

CALT taddr2 (Cali Table): uPD7503

made.

$\bigcirc$

3

1 1 P5 P4 P3 P2 P1 P0 Instruction code: (2) Byte count: 1 Machine cycle count: 2 (4) Function: (SP-1)  $\leftarrow PC_{7-4}$ , (SP-2)  $\leftarrow PC_{3-0}$ ,  $(SP-3) \leftarrow PSW, (SP-4) \leftarrow PC_{11-8}$  $PC_{9-7,4-0} \leftarrow ROM(000011P_5P_4P_3P_2P_1P_0)$ PC<sub>11,10,6,5</sub> ← 0 SP ← SP-4  $taddr2=000011P_5P_4P_3P_2P_1P_0:0D0H-0FFH$ The contents of the program counter (return address) and PSW are saved in the data memory location (stack) addressed by the stack pointer (SP), 8-bit table data  $(T_{7-0})$  at the table address  $(000011P_5P_4P_3$  $P_2P_1P_0$ ) specified in the instruction is loaded into the program counter in form of  $OOT_7T_6T_5OOT_4T_3T_2T_1T_0$ , then a jump is

> Be sure to code a table address in the operand of the CALT instruction.

The table area for the CALT instruction is assigned to addresses ODOH to OFFH. Before the CALT instruction is executed, the subroutine call address data must be programmed in this area with an assembler pseudo instruction (DET).

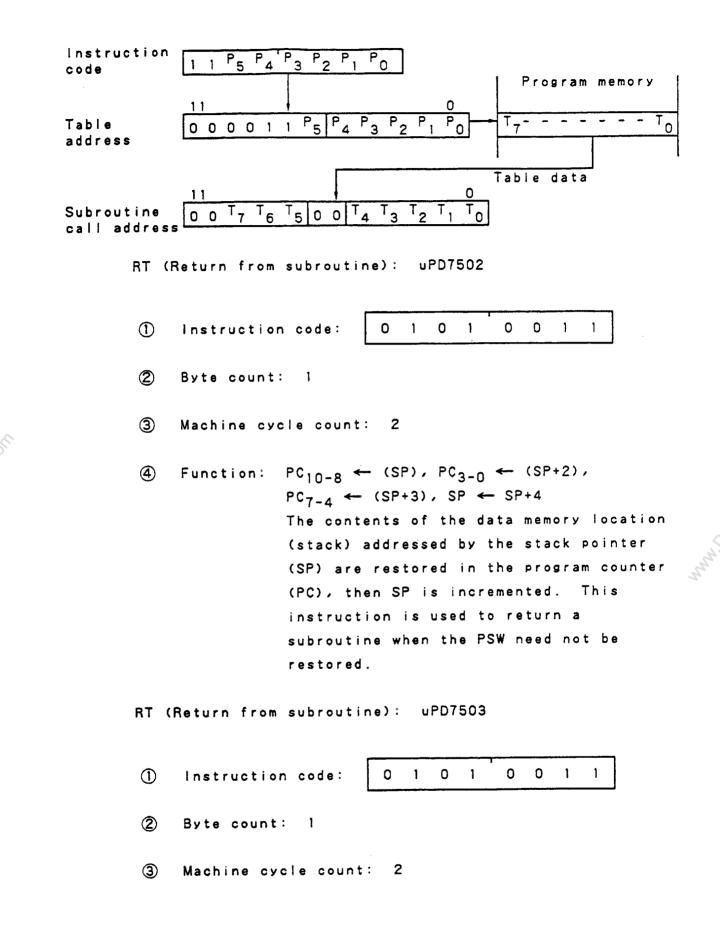

(4) Function:  $PC_{11-8} \leftarrow (SP)$ ,  $PC_{3-0} \leftarrow (SP+2)$ ,  $PC_{7-4} \leftarrow (SP+3)$ ,  $SP \leftarrow SP+4$ The contents of the data memory location (stack) addressed by the stack pointer (SP) are restored in the program counter (PC), then SP is incremented.

(6) Note: PSW is not restored.

RTS (Return from Subroutine, then Skip): uPD7502

① Instruction code:

(2) Byte count: 1

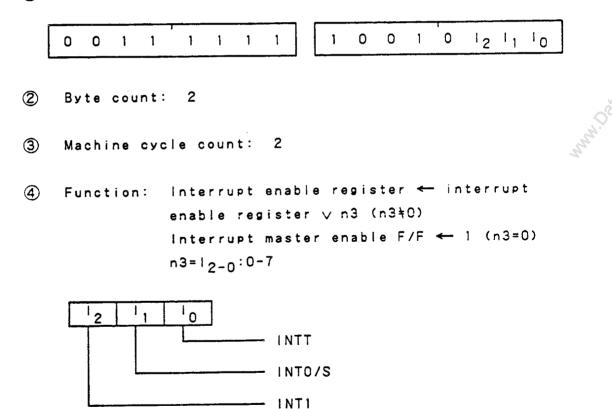

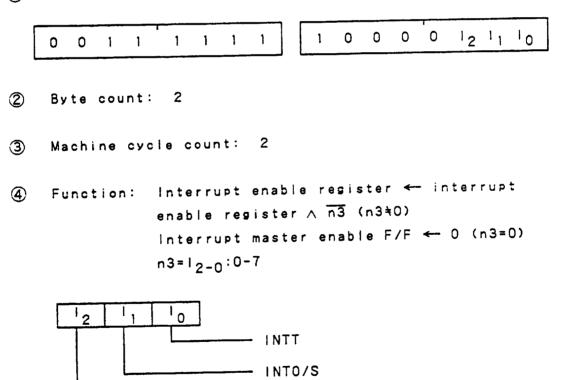

(3) Machine cycle count: 3