# mos integrated circuit $\mu$ PD754144, 754244

#### **4-BIT SINGLE-CHIP MICROCONTROLLERS**

#### DESCRIPTION

NE

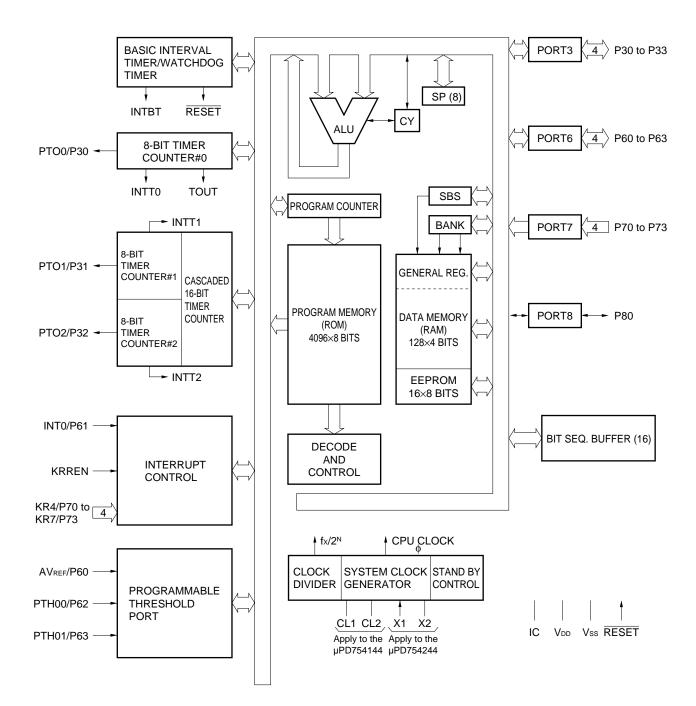

The  $\mu$ PD754244 is a 4-bit single-chip microcontroller which incorporates the EEPROM<sup>TM</sup> for key-less entry application.

It incorporates a  $16 \times 8$ -bit EEPROM, a 4-Kbyte mask ROM to store software, a  $128 \times 4$ -bit RAM to store the processing data, a processing CPU, and a carrier generator which easily outputs waveforms for infrared remote controller.

The details of functions are described in the following user's manual. Be sure to read it before designing.

#### $\mu$ PD754144, 754244 User's Manual: U10676E

#### FEATURES

- On-chip EEPROM:  $16 \times 8$  bits (mapped to the data memory)

- On-chip key return reset function for key-less entry

- System clock oscillation circuit

- μPD754144: RC oscillator (external resistor and capacitor)

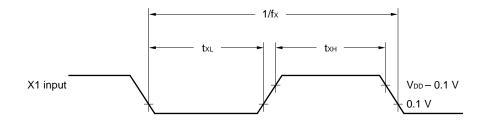

- μPD754244: Crystal/ceramic oscillator

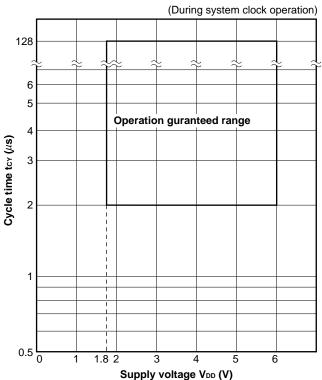

- Low-voltage operation: VDD = 1.8 to 6.0 V

- Timer function (4 channels)

- Basic interval timer/watchdog timer: 1 channel

- 8-bit timer counter : 3 channels

- On-chip memory

- Program memory (ROM) 4096 × 8 bits

- Data memory (static RAM) 128 × 4 bits

- Instruction execution time variable function suited for power saving.

- μPD754144:

- 4, 8, 16, 64  $\mu$ s (at fcc = 1.0-MHz operation)

- μPD754244:

0.95, 1.91, 3.81, 15.3 μs (at fx = 4.19-MHz operation)

0.67, 1.33, 2.67, 10.7 μs (at fx = 6.0-MHz operation)

#### APPLICATIONS

Automotive appliances such as key-less entry, compact data carrier, etc.

Unless contextually excluded, references in this data sheet to the  $\mu$ PD754244 (crystal/ceramic oscillation: fx) mean the  $\mu$ PD754144.

The  $\mu$ PD754144 and  $\mu$ PD754244 differ in the notation of their RC oscillation: whenever fx (RC oscillation notation for  $\mu$ PD754244) is described, fcc should be substituted for the  $\mu$ PD754144.

The information in this document is subject to change without notice.

#### **ORDERING INFORMATION**

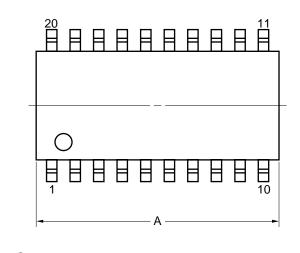

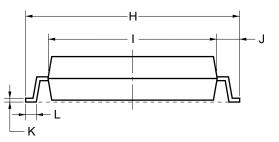

| Part Number              | Package                                            |

|--------------------------|----------------------------------------------------|

| μPD754144GS-xxx-BA5      | 20-pin plastic SOP (300 mil, 1.27-mm pitch)        |

| $\mu$ PD754144GS-xxx-GJG | 20-pin plastic shrink SOP (300 mil, 0.65-mm pitch) |

| μPD754244GS-xxx-BA5      | 20-pin plastic SOP (300 mil, 1.27-mm pitch)        |

| μPD754244GS-xxx-GJG      | 20-pin plastic shrink SOP (300 mil, 0.65-mm pitch) |

Remark xxx indicates ROM code suffix.

#### **Functional Outline**

| P                             | arameter          |                                                                                                                             | μPD754144                                                            | μPD754244                                                                                                                                         |  |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction execution time    |                   | <ul> <li>4, 8, 16, 64 μs</li> <li>(at fcc = 1.0-MHz operation)</li> </ul>                                                   |                                                                      | <ul> <li>0.95, 1.91, 3.81, 15.3 μs<br/>(at fx = 4.19-MHz operation)</li> <li>0.67, 1.33, 2.67, 10.7 μs<br/>(at fx = 6.0-MHz operation)</li> </ul> |  |

| On-chip                       | Mask ROM          | 4096 >                                                                                                                      | < 8 bits (0000H-0FFFH)                                               |                                                                                                                                                   |  |

| memory                        | RAM               | 128 ×                                                                                                                       | 4 bits (000H-07FH)                                                   |                                                                                                                                                   |  |

|                               | EEPROM            | 16 × 8                                                                                                                      | bits (400H-41FH)                                                     |                                                                                                                                                   |  |

| System clock                  | oscillator        |                                                                                                                             | cillator<br>nal resistor and capacitor)                              | Crystal/ceramic oscillator                                                                                                                        |  |

| General-purpo                 | ose register      |                                                                                                                             | t operation: $8 \times 4$ banks<br>t operation: $4 \times 4$ banks   |                                                                                                                                                   |  |

| Input/output                  | CMOS input        | 4                                                                                                                           | On-chip pull-up resistor can be s                                    | pecified by mask option.                                                                                                                          |  |

| port                          | CMOS input/output | 9                                                                                                                           | 9 On-chip pull-up resistor connection can be specified by means of s |                                                                                                                                                   |  |

|                               | Total             | 13                                                                                                                          |                                                                      |                                                                                                                                                   |  |

| Start-up time                 | after reset       | 56/fcc                                                                                                                      |                                                                      | 2 <sup>17</sup> /fx, 2 <sup>15</sup> /fx (selected by mask option)                                                                                |  |

| Stand-by mod                  | e release time    | 2 <sup>9</sup> /fcc                                                                                                         |                                                                      | 2 <sup>20</sup> /fx, 2 <sup>17</sup> /fx, 2 <sup>15</sup> /fx, 2 <sup>13</sup> /fx                                                                |  |

|                               |                   |                                                                                                                             |                                                                      | (selected by the setting of BTM)                                                                                                                  |  |

| Timer                         |                   | 4 char                                                                                                                      |                                                                      |                                                                                                                                                   |  |

|                               |                   |                                                                                                                             | t timer counter<br>b be used as 16-bit timer counter)                | : 3 channels                                                                                                                                      |  |

|                               |                   | Basic interval/watchdog timer                                                                                               |                                                                      | : 1 channel                                                                                                                                       |  |

| Bit sequential                | buffer            | 16 bits                                                                                                                     |                                                                      |                                                                                                                                                   |  |

| Vectored inter                | rupt              | External: 1, Internal: 5                                                                                                    |                                                                      |                                                                                                                                                   |  |

| Test input                    |                   | External: 1 (key return reset function available)                                                                           |                                                                      |                                                                                                                                                   |  |

| Standby function              |                   | STOP/HALT mode                                                                                                              |                                                                      |                                                                                                                                                   |  |

| Operating ambient temperature |                   | $T_{A} = -40$ to +85 °C                                                                                                     |                                                                      |                                                                                                                                                   |  |

| Operating sup                 |                   | V <sub>DD</sub> = 1.8 to 6.0 V                                                                                              |                                                                      |                                                                                                                                                   |  |

| Package                       |                   | <ul> <li>20-pin plastic SOP (300 mil, 1.27-mm pitch)</li> <li>20-pin plastic shrink SOP (300 mil, 0.65-mm pitch)</li> </ul> |                                                                      |                                                                                                                                                   |  |

#### CONTENTS

| 1.  | PIN CONFIGURATION (TOP VIEW)6                                                                                                                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.  | BLOCK DIAGRAM                                                                                                                                                                                                                           |

| 3.  | PIN FUNCTION93.1 Port Pins93.2 Non-port Pins103.3 Pin Input/Output Circuits113.4 Recommended Connection of Unused Pins12                                                                                                                |

| 4.  | SWITCHING FUNCTION BETWEEN MK I MODE AND MK II MODE       13         4.1 Difference between Mk I and Mk II Modes       13         4.2 Setting Method of Stack Bank Select Register (SBS)       14                                       |

| 5.  | MEMORY CONFIGURATION15                                                                                                                                                                                                                  |

| 6.  | EEPROM                                                                                                                                                                                                                                  |

| 7.  | PERIPHERAL HARDWARE FUNCTIONS197.1 Digital Input/Output Ports197.2 Clock Generator197.3 Basic Interval Timer/Watchdog Timer227.4 Timer Counter237.5 Programmable Threshold Port (Analog Input Port)277.6 Bit Sequential Buffer16 Bits28 |

| 8.  | INTERRUPT FUNCTION AND TEST FUNCTION                                                                                                                                                                                                    |

| 9.  | STANDBY FUNCTION                                                                                                                                                                                                                        |

| 10. | RESET FUNCTION       32         10.1 Configuration and Operation Status of RESET Function       32         10.2 Watchdog Flag (WDF), Key Return Flag (KRF)       36                                                                     |

| 11. | MASK OPTION                                                                                                                                                                                                                             |

| 12. | INSTRUCTION SETS                                                                                                                                                                                                                        |

| 13. | ELECTRICAL SPECIFICATIONS                                                                                                                                                                                                               |

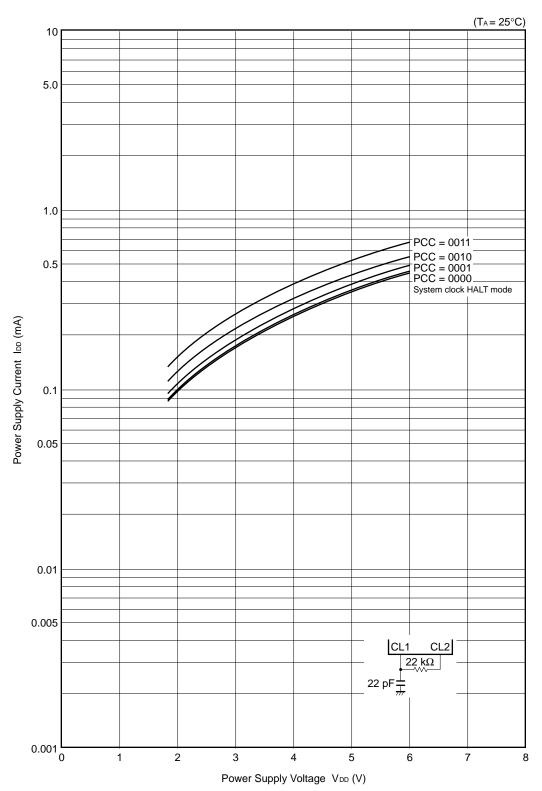

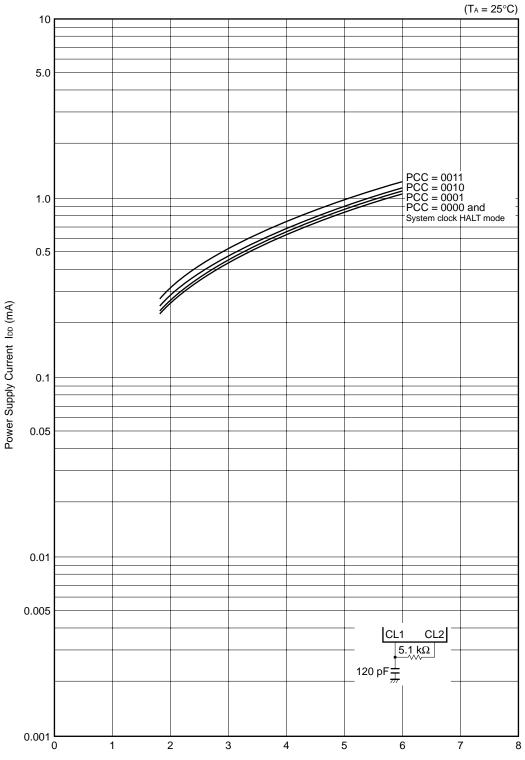

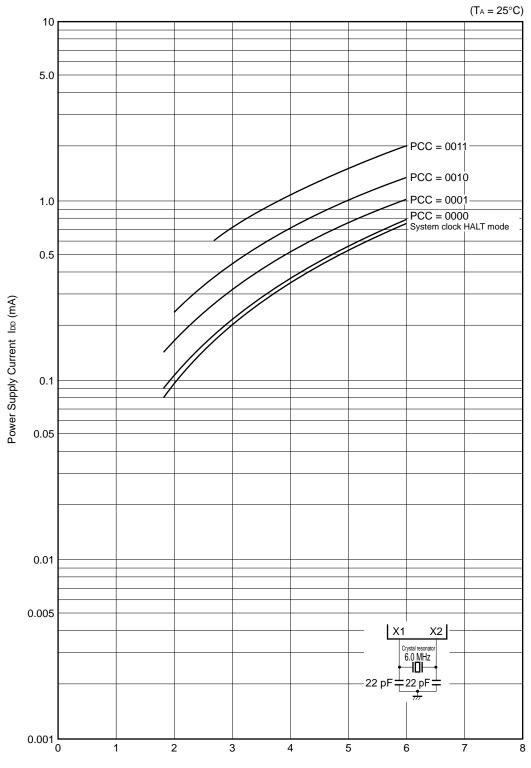

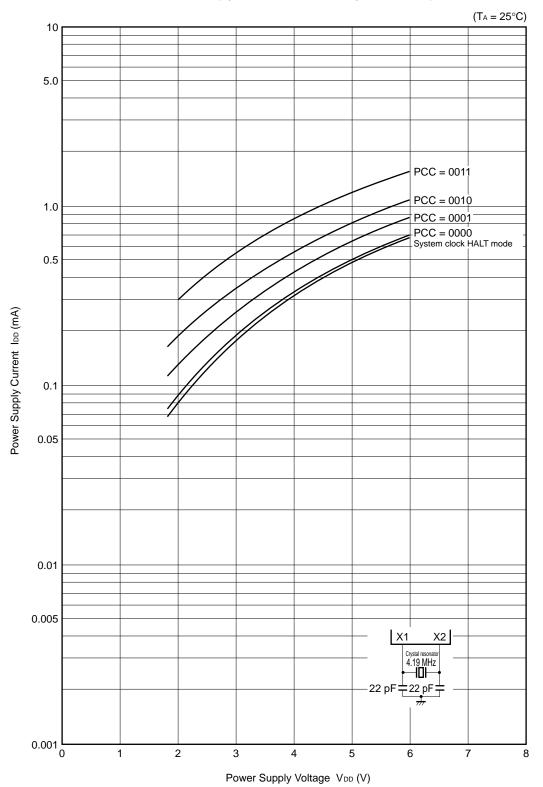

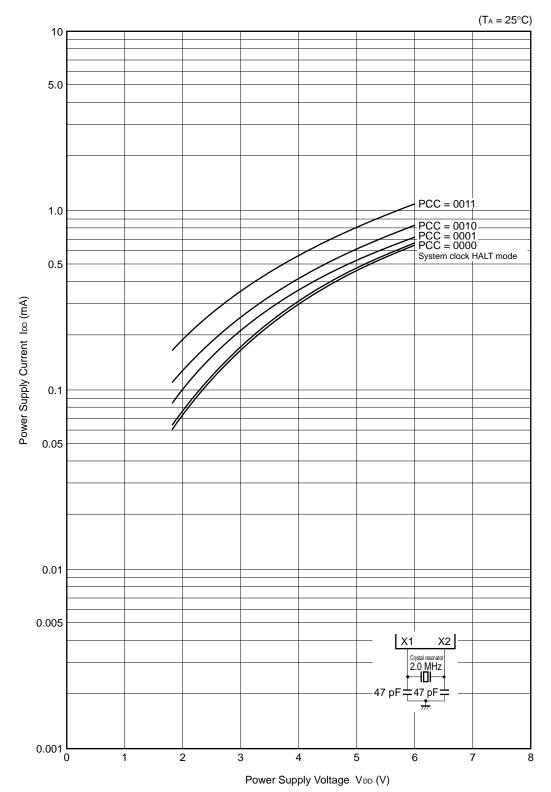

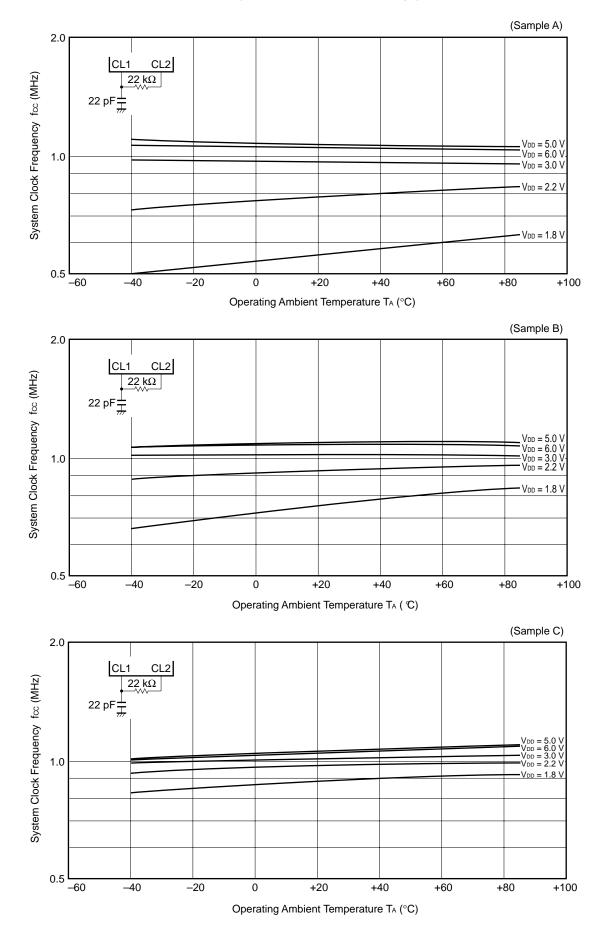

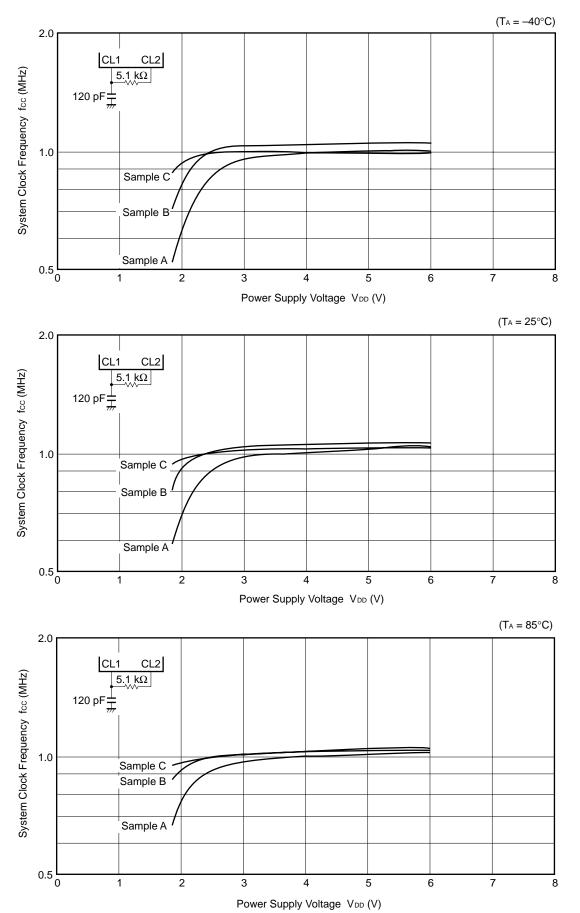

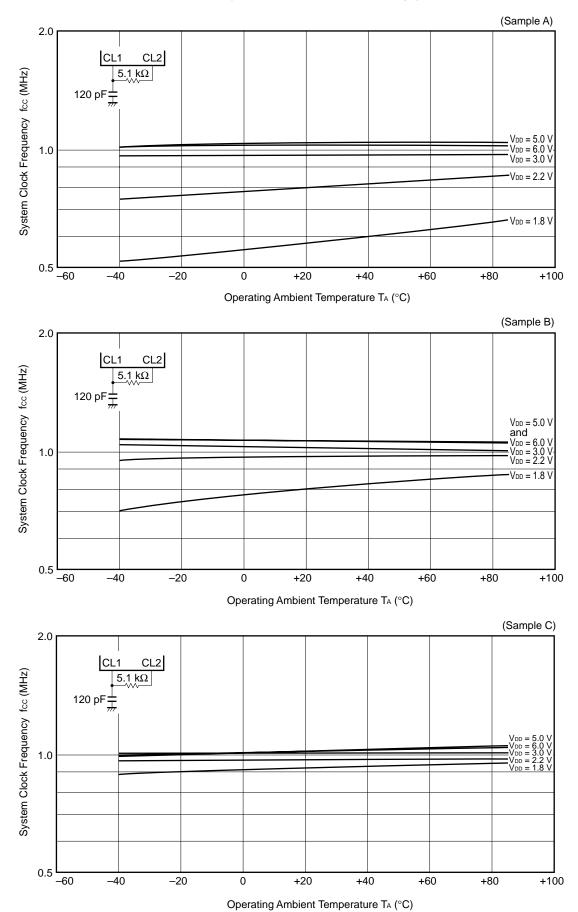

| 14. | CHARACTERISTICS CURVES (REFERENCE VALUES)                                                                                                                                                                                               |

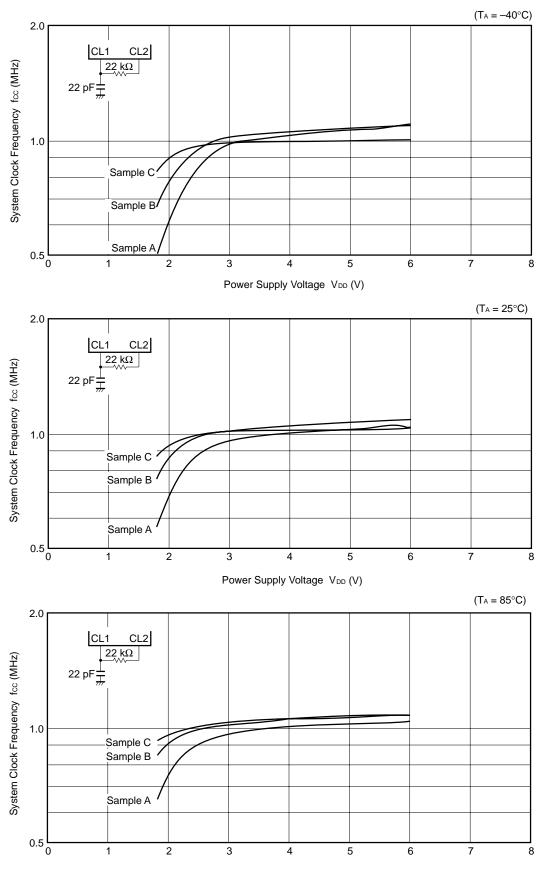

| 15. RC OSCILLATION FREQUENCY CHARACTERISTICS EXAMPLES (REFERENCE VALUES) 7     |

|--------------------------------------------------------------------------------|

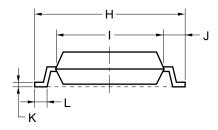

| 16. PACKAGE DRAWINGS                                                           |

| 17. RECOMMENDED SOLDERING CONDITIONS                                           |

| APPENDIX A. COMPARISON OF FUNCTIONS AMONG $\mu$ PD754144, 754244, AND 75F42648 |

| APPENDIX B. DEVELOPMENT TOOLS8                                                 |

| APPENDIX C. RELATED DOCUMENTS8                                                 |

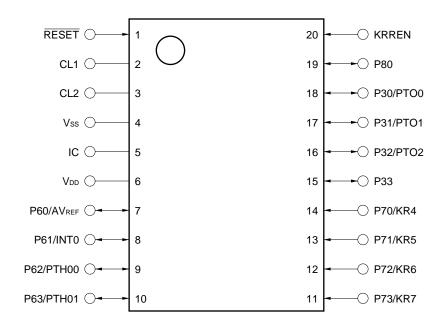

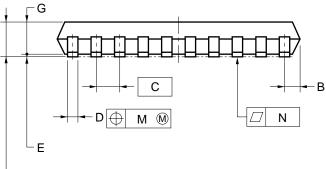

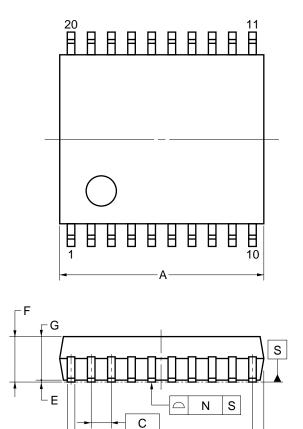

#### 1. PIN CONFIGURATION (TOP VIEW)

- μPD754144

- 20-pin Plastic SOP (300 mil, 1.27-mm pitch) μPD754144GS-xxx-BA5

- 20-pin Plastic Shrink SOP (300 mil, 0.65-mm pitch) μPD754144GS-×××-GJG

IC: Internally Connected (Connect to VDD directly)

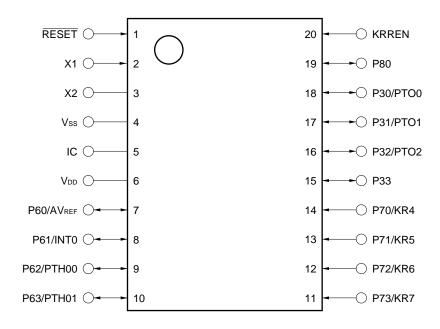

- μPD754244

- 20-pin Plastic SOP (300 mil, 1.27-mm pitch) μPD754244GS-xxx-BA5

- 20-pin Plastic Shrink SOP (300 mil, 0.65-mm pitch) μPD754244GS-×××-GJG

IC: Internally Connected (Connect to VDD directly)

#### **Pin Identification**

| AVREF       | : Analog reference              | P70 to P73      | : Port 7                                            |

|-------------|---------------------------------|-----------------|-----------------------------------------------------|

| CL1 and CL2 | : System clock (RC)             | P80             | : Port 8                                            |

| IC          | : Internally connected          | PTH00 and PTH01 | : Programmable threshold port analog inputs 0 and 1 |

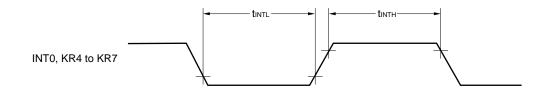

| INT0        | : External vectored interrupt 0 | PTO0 to PTO2    | : Programmable timer outputs 0 to 2                 |

| KR4 to KR7  | : Key returns 4 to 7            | RESET           | : Reset                                             |

| KRREN       | : Key return reset enable       | Vdd             | : Positive power supply                             |

| P30 to P33  | : Port 3                        | Vss             | : Ground                                            |

| P60 to P63  | : Port 6                        | X1 and X2       | : System clock (crystal/ceramic)                    |

|             |                                 |                 |                                                     |

#### 2. BLOCK DIAGRAM

#### 3. PIN FUNCTION

#### 3.1 Port Pins

| Pin Name | Input/Output | Alternate<br>Function | Function                                                                                                 | 8-bit<br>I/O | After Reset | I/O Circuit<br>TYPE Note 1 |

|----------|--------------|-----------------------|----------------------------------------------------------------------------------------------------------|--------------|-------------|----------------------------|

| P30      | Input/Output | PTO0                  | Programmable 4-bit input/output port                                                                     | -            | Input       | E-B                        |

| P31      |              | PTO1                  | (PORT3).<br>This port can be specified input/output bit-                                                 |              |             |                            |

| P32      |              | PTO2                  | wise.                                                                                                    |              |             |                            |

| P33      |              | _                     | On-chip pull-up resistor connection can be specified by software in 4-bit units.                         |              |             |                            |

| P60      | Input/Output | AVREF                 | Programmable 4-bit input/output port (PORT6).                                                            | -            | Input       | Ē-A                        |

| P61      |              | INT0                  | This port can be specified input/output bit-<br>wise.                                                    |              |             |                            |

| P62      |              | PTH00                 | On-chip pull-up resistor can be specified by                                                             |              |             |                            |

| P63      |              | PTH01                 | - software in 4-bit units <sup>Note2</sup> .<br>Noise eliminator can be selected with P61/INT0.          |              |             |                            |

| P70      | Input        | KR4                   | 4-bit input port (PORT7).                                                                                | -            | Input       | B-A                        |

| P71      |              | KR5                   | On-chip pull-up resistor can be specified by software bit-wise.                                          |              |             |                            |

| P72      |              | KR6                   |                                                                                                          |              |             |                            |

| P73      | 1            | KR7                   |                                                                                                          |              |             |                            |

| P80      | Input/Output | -                     | 1-bit input/output port (PORT8).<br>On-chip pull-up resistor connection can be<br>specified by software. | _            | Input       | Ē-A                        |

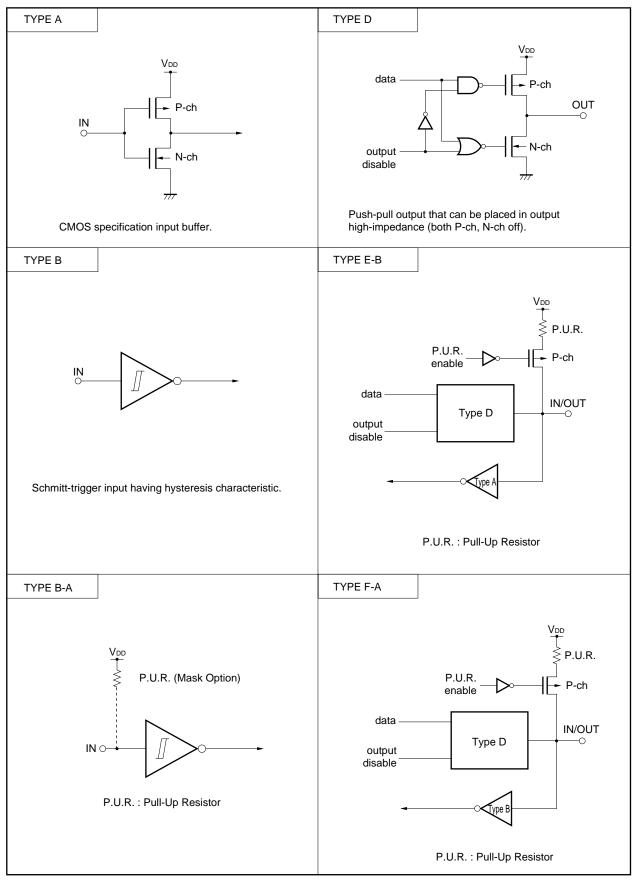

**Notes 1.** Circled characters indicate the Schmitt-trigger input.

2. Do not specify an on-chip pull-up resistor connection when using the programmable threshold port.

#### 3.2 Non-port Pins

| Pin Name   | Input/Output | Alternate<br>Function | Function                                                                                                                                                                                    | After Reset | I/O Circuit<br>TYPE <sup>Note</sup> |

|------------|--------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|

| PTO0       | Output       | P30                   | Timer counter output pins                                                                                                                                                                   | Input       | E-B                                 |

| PTO1       |              | P31                   |                                                                                                                                                                                             |             |                                     |

| PTO2       |              | P32                   |                                                                                                                                                                                             |             |                                     |

| INTO       | Input        | P61                   | Edge detection vectored<br>interrupt input pinNoise elimination<br>circuit can be<br>selected.(detected edge can be<br>selected)selected.Noise elimination circuit<br>can be selected.input | Input       | Ē-A                                 |

| KR4 to KR7 | Input        | P70 to P73            | Falling edge detection testable input pins                                                                                                                                                  | Input       | B-A                                 |

| PTH00      | Input        | P62                   | Threshold voltage-variable 2-bit analog input p                                                                                                                                             | ns Input    | (F)-A                               |

| PTH01      |              | P63                   |                                                                                                                                                                                             |             |                                     |

| KRREN      | Input        | _                     | Key return reset enable pin<br>The reset signal is generated at the falling edge<br>of KRn while KRREN is high in STOP mode.                                                                | Input       | B                                   |

| AVREF      | Input        | P60                   | Reference voltage input pin                                                                                                                                                                 | Input       | Ē-A                                 |

| CL1        | -            | _                     | Incorporated in the $\mu$ PD754144 only RC (for system clock oscillation) connection pin                                                                                                    | _           | -                                   |

| CL2        | -            |                       | External clock cannot be input.                                                                                                                                                             |             |                                     |

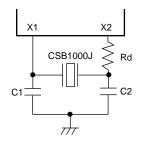

| X1         | Input        | _                     | Incorporated in the µPD754244 only<br>Crystal/ceramic resonator (for system clock<br>oscillation) connection pin                                                                            | -           | _                                   |

| Х2         | _            |                       | When inputting the external clock, input the external clock to pin X1 and input the inverted phase of the external clock to pin X2.                                                         |             |                                     |

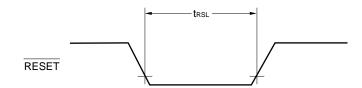

| RESET      | Input        | _                     | System reset input pin (low-level active)                                                                                                                                                   | -           | B-A                                 |

|            |              |                       | Pull-up resistor can be incorporated (mask option                                                                                                                                           | ).          |                                     |

| IC         | -            | _                     | Internally Connected Connect directly to $V_{DD}$ .                                                                                                                                         | -           | -                                   |

| Vdd        | -            | -                     | Positive supply pin                                                                                                                                                                         | -           | -                                   |

| Vss        |              | _                     | Ground potential                                                                                                                                                                            | -           | _                                   |

**Note** Circled characters indicate the Schmitt-trigger input.

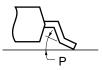

#### 3.3 Pin Input/Output Circuits

The  $\mu$ PD754244 pin input/output circuits are shown schematically.

#### 3.4 Recommended Connection of Unused Pins

| Pin       | Recommended Connecting Method                                                                                                                                                                                                                                                        |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P30/PTO0  | Input state : Independently connect to Vss or VDD via a resistor.                                                                                                                                                                                                                    |  |  |

| P31/PTO1  | Output state: Leave open.                                                                                                                                                                                                                                                            |  |  |

| P32/PTO2  |                                                                                                                                                                                                                                                                                      |  |  |

| P33       |                                                                                                                                                                                                                                                                                      |  |  |

| P60/AVREF |                                                                                                                                                                                                                                                                                      |  |  |

| P61/INT0  |                                                                                                                                                                                                                                                                                      |  |  |

| P62/PTH00 |                                                                                                                                                                                                                                                                                      |  |  |

| P63/PTH01 |                                                                                                                                                                                                                                                                                      |  |  |

| P70/KR4   | Connect to Vbb.                                                                                                                                                                                                                                                                      |  |  |

| P71/KR5   |                                                                                                                                                                                                                                                                                      |  |  |

| P72/KR6   |                                                                                                                                                                                                                                                                                      |  |  |

| P73/KR7   |                                                                                                                                                                                                                                                                                      |  |  |

| P80       | Input state : Independently connect to Vss or Vbb via a resistor.                                                                                                                                                                                                                    |  |  |

|           | Output state: Leave open.                                                                                                                                                                                                                                                            |  |  |

| KRREN     | When this pin is connected to VDD, internal reset signal is gener-<br>ated at the falling edge of the KRn pin in the STOP mode.<br>When this pin is connected to Vss, internal reset signal is not<br>generated even if the falling edge of KRn pin is detected in the<br>STOP mode. |  |  |

| IC        | Connect directly to VDD.                                                                                                                                                                                                                                                             |  |  |

#### Table 3-1. List of Recommended Connection of Unused Pins

#### 4. SWITCHING FUNCTION BETWEEN MK I MODE AND MK II MODE

#### 4.1 Difference between Mk I and Mk II Modes

The  $\mu$ PD754244 75XL CPU has the following two modes: Mk I and Mk II, either of which can be selected. The mode can be switched by the bit 3 of the Stack Bank Select register (SBS).

- Mk I mode: Instructions are compatible with the 75X series. Can be used in the 75XL CPU with a ROM capacity of up to 16 Kbytes.

- Mk II mode: Incompatible with 75X series. Can be used in all the 75XL CPU's including those products whose ROM capacity is more than 16 Kbytes.

|                                                      | Mk I Mode        | Mk II Mode       |

|------------------------------------------------------|------------------|------------------|

| Number of stack bytes<br>for subroutine instructions | 2 bytes          | 3 bytes          |

| BRA laddr1 instruction<br>CALLA laddr1 instruction   | Not available    | Available        |

| CALL laddr instruction                               | 3 machine cycles | 4 machine cycles |

| CALLF Ifaddr instruction                             | 2 machine cycles | 3 machine cycles |

#### Table 4-1. Differences between Mk I Mode and Mk II Mode

Caution The Mk II mode supports a program area exceeding 16 Kbytes for the 75X and 75XL Series. Therefore, this mode is effective for enhancing software compatibility with products that have a program area of more than 16 Kbytes.

With regard to the number of stack bytes during execution of subroutine call instructions, the usable area increases by 1 byte per stack compared to the Mk I mode when the Mk II mode is selected.

However, when the CALL !addr and CALLF !faddr instructions are used, the machine cycle becomes longer by 1 machine cycle. Therefore, if more emphasis is placed on RAM use efficiency and processing performance than on software compatibility, the Mk I mode should be used.

#### 4.2 Setting Method of Stack Bank Select Register (SBS)

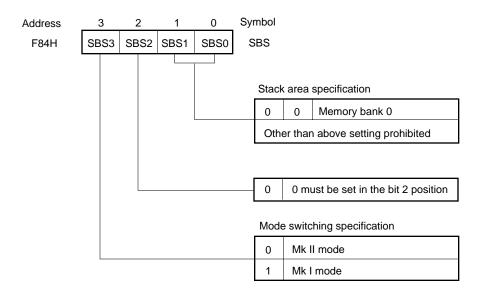

Switching between the Mk I mode and Mk II mode can be done by the SBS. Figure 4-1 shows the format. The SBS is set by a 4-bit memory manipulation instruction.

When using the Mk I mode, the SBS must be initialized to 1000B at the beginning of a program. When using the Mk II mode, it must be initialized to 0000B.

Figure 4-1. Stack Bank Select Register Format

Caution Because SBS. 3 is set to "1" after a RESET signal is generated, the CPU operates in the Mk I mode. When executing an instruction in the Mk II mode, set SBS. 3 to "0" to select the Mk II mode.

#### 5. MEMORY CONFIGURATION

- Program memory (ROM) ••• 4096 x 8 bits

- Addresses 0000H and 0001H

Vector table wherein the program start address and the values set for the RBE and MBE at the time a  $\overline{\text{RESET}}$  signal is generated are written. Reset and start are possible at an arbitrary address.

• Addresses 0002H to 000FH

Vector table wherein the program start address and values set for the RBE and MBE by the vectored interrupts are written. Interrupt service can be started at an arbitrary address.

- Addresses 0020H to 007FH Table area referenced by the GETI instruction<sup>Note</sup>.

- **Note** The GETI instruction realizes a 1-byte instruction on behalf of an arbitrary 2-byte instruction, 3-byte instruction, or two 1-byte instructions. It is used to decrease the program steps.

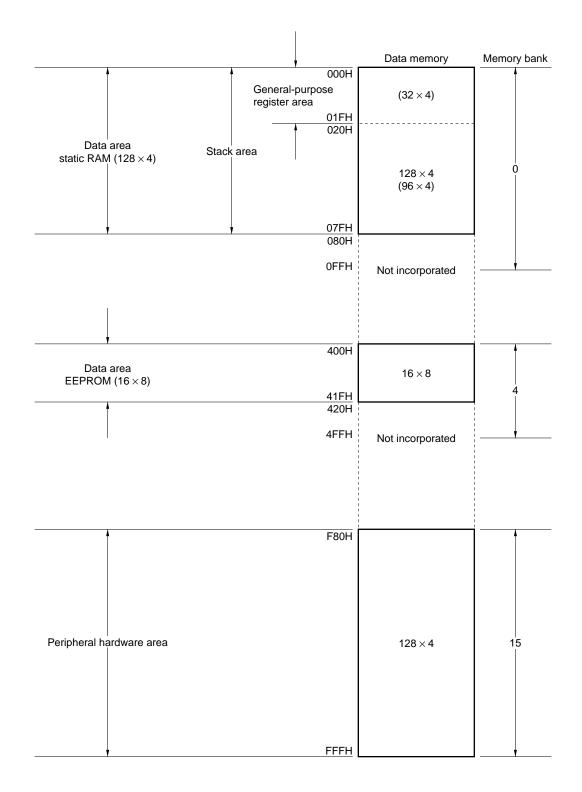

#### • Data memory

| ٠ | Data area                |                                       |

|---|--------------------------|---------------------------------------|

|   | Static RAM               | ••• 128 words x 4 bits (000H to 07FH) |

|   | EEPROM                   | ••• 16 words x 8 bits (400H to 41FH)  |

| • | Peripheral hardware area | ••• 128 words x 4 bits (F80H to FFFH) |

| Address | 7      | 6   | 5 | 4     |                              | 0                   |             |                              |           |

|---------|--------|-----|---|-------|------------------------------|---------------------|-------------|------------------------------|-----------|

| 0000H   | MBE    | RBE | 0 | 0     | Internal reset start address | (high-order 4 bits) |             | · ·                          |           |

| 0001H   |        | 1   | 1 |       | Internal reset start address | (low-order 8 bits)  |             |                              |           |

| 0002H   | MBE    | RBE | 0 | 0     | INTBT start address          | (high-order 4 bits) | CALLF !fado | Ir instruction               |           |

| 0003H   |        | 1   | 1 |       | INTBT start address          | (low-order 8 bits)  | entry a     | ddress                       |           |

| 0004H   | MBE    | RBE | 0 | 0     | INT0 start address           | (high-order 4 bits) |             |                              |           |

| 0005H   |        |     |   |       | INT0 start address           | (low-order 8 bits)  |             |                              |           |

| 0006H   |        |     |   |       |                              |                     |             |                              |           |

| 0007H   |        |     |   |       |                              |                     |             |                              |           |

| 0008H   |        |     |   |       |                              |                     |             | Branch ac                    |           |

| 0009H   |        |     |   |       |                              |                     |             | BR !:<br>BRCB<br>BR B        | !caddr    |

| 000AH   | MBE    | RBE | 0 | 0     | INTT0 start address          | (high-order 4 bits) |             | BR B<br>BR B<br>BRA !a       | CXA       |

| 000BH   |        |     |   |       | INTT0 start address          | (low-order 8 bits)  |             | CALL<br>CALLA !              | !addr     |

| 000CH   | MBE    | RBE | 0 | 0     | INTT1/INTT2 start address    | (high-order 4 bits) |             | instruc                      | ctions    |

| 000DH   |        | 1   | 1 | 1     | INTT1/INTT2 start address    | (low-order 8 bits)  |             | GETI Bra                     | anch/call |

| 000EH   | MBE    | RBE | 0 | 0     | INTEE start address          | (high-order 4 bits) |             | Addre                        |           |

| 000FH   |        | 1   |   |       | INTEE start address          | (low-order 8 bits)  |             | BR \$addr i                  |           |

|         |        |     |   |       |                              |                     |             | relative brar<br>(−15 to −1, |           |

|         | Ĩ      |     |   |       |                              |                     | Ē           |                              |           |

| 0020H   |        |     |   |       |                              |                     |             |                              |           |

| 007FH   |        |     |   | GET i | nstruction reference table   |                     |             |                              |           |

| 0080H   |        |     |   |       |                              |                     |             |                              |           |

| (       | L<br>T |     |   |       |                              | 2                   | Ļ           |                              |           |

| 07FFH   |        |     |   |       |                              |                     |             | ,                            |           |

| 0800H   |        |     |   |       |                              | -                   |             |                              |           |

|         | Ĩ      |     |   |       |                              |                     | Ē           |                              |           |

| 0FFFH   |        |     |   |       |                              |                     |             |                              |           |

#### Figure 5-1. Program Memory Map

Note Can be used in the MkII mode only.

**Remark** In addition to the above, a branch can be made to an address with the low-order 8-bits only of the PC changed by means of a BR PCDE or BR PCXA instruction.

Figure 5-2. Data Memory Map

#### 6. EEPROM

The  $\mu$ PD754244 incorporates 16 words × 8 bit EEPROM (Electrically Erasable PROM) as well as static RAM (128 words × 4 bit) as a data memory.

The EEPROM incorporated into the  $\mu$ PD754244 has the following features.

- (1) Written data is retained if power is turned off.

- (2) 8-bit data manipulation (auto-erase/auto-write) is available by memory manipulation instruction as well as for static RAM. However available instructions are restricted.

- (3) It can reduce loads of software because the auto-erase and/or auto-write operation is performed by hardware.

- (4) Write operation control using the interrupt request

- The interrupt request is generated under following conditions.

- Terminates write operation

- Write status flag

It is possible to check whether enables or disables write operation by bit manipulation instructions.

#### 7. PERIPHERAL HARDWARE FUNCTIONS

#### 7.1 Digital Input/Output Ports

The following two types of I/O ports are provided.

CMOS input (Port 7) : 4

CMOS I/O (Ports 3, 6, 8) : 9

Total : 13

#### Table 7-1. Types and Features of Digital Ports

| Port Name | Function    | Operation and Features                               | Remarks                                                      |

|-----------|-------------|------------------------------------------------------|--------------------------------------------------------------|

| PORT3     | 4-bit I/O   | Can be set to input or output mode bit-wise.         | Also used as PTO0 to PTO2 pins.                              |

| PORT6     |             |                                                      | Also used as AV $_{\text{REF}}$ INT0, PTH00, and PTH01 pins. |

| PORT7     | 4-bit input | 4-bit input only port                                | Also used as KR4 to KR7 pins.                                |

|           |             | On-chip pull-up resistor connection can be specified |                                                              |

|           |             | by mask option bit-wise.                             |                                                              |

| PORT8     | 1-bit I/O   | Can be set to input or output mode bit wise.         | _                                                            |

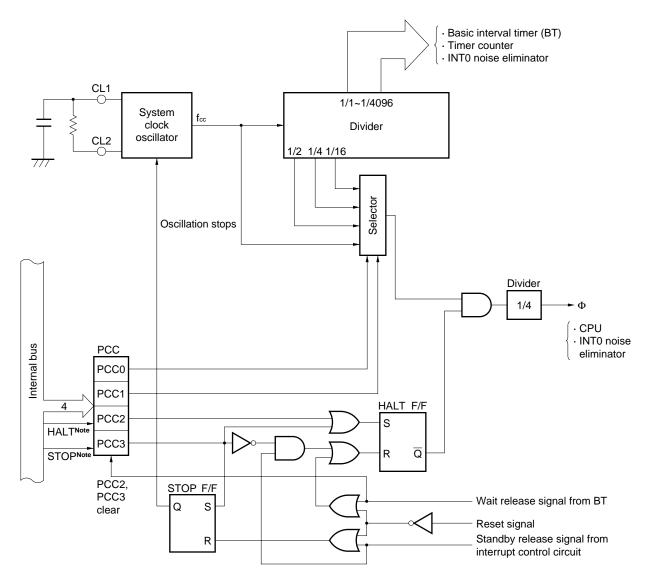

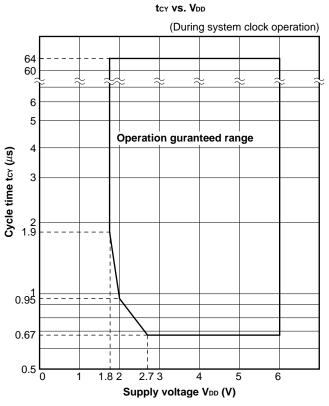

#### 7.2 Clock Generator

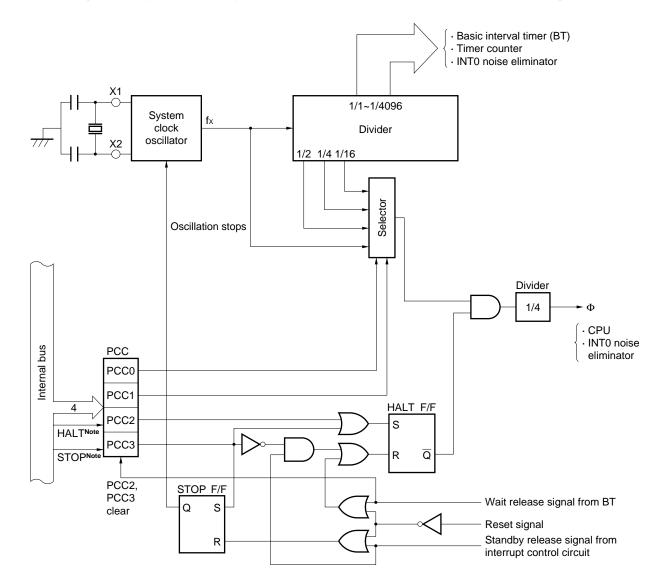

The clock generator provides the clock signals to the CPU and peripheral hardware. Its configuration is shown in Figures 7-1 and 7-2.

The operation of the clock generator is set with the processor clock control register (PCC). The instruction execution time can be changed.

#### • μPD754144

- 4, 8, 16, 64  $\mu$ s (when the system clock fcc operates at 1.0 MHz)

- μPD754244

- 0.95, 1.91, 3.81, 15.3  $\mu s$  (when the system clock fx operates at 4.19 MHz)

- 0.67, 1.33, 2.67, 10.7  $\mu$ s (when the system clock fx operates at 6.0 MHz)

#### Figure 7-1. µPD754144 (RC Oscillation) Clock Generator Block Diagram

Remarks 1. fcc: System clock frequency

- **2.**  $\Phi$  = CPU clock

- 3. PCC: Processor Clock Control Register

- 4. One clock cycle (tcr) of the CPU clock is equal to one machine cycle of the instruction.

Figure 7-2. µPD754244 (Crystal/Ceramic Oscillation) Clock Generator Block Diagram

Note Instruction execution

Remarks 1. fx: System clock frequency

- **2.**  $\Phi$  = CPU clock

- 3. PCC: Processor Clock Control Register

- 4. One clock cycle (tcr) of the CPU clock is equal to one machine cycle of the instruction.

### NEC

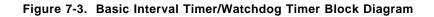

#### 7.3 Basic Interval Timer/Watchdog Timer

The basic interval timer/watchdog timer has the following functions.

- (a) Interval timer operation to generate a reference time interrupt

- (b) Watchdog timer operation to detect a runaway of program and reset the CPU

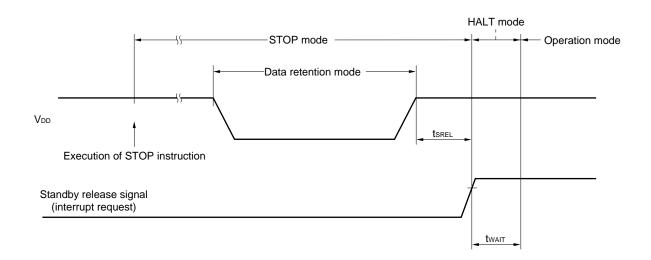

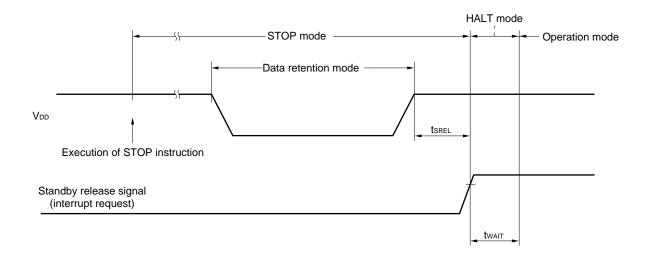

- (c) Selects and counts the wait time when the standby mode is released ( $\mu$ PD754244 only)<sup>Note 1</sup>

- (d) Reads the contents of counting

- **Notes 1.** In the  $\mu$ PD754144 (RC oscillation), the wait time cannot be specified when the standby mode is released. The oscillation stabilization wait time is negligible in the  $\mu$ PD754144 and this device returns to the normal operation mode after counting 2<sup>9</sup>/fcc (512  $\mu$ s: @ fcc = 1.0-MHz operation). In the  $\mu$ PD754244 (crystal/ceramic oscillation), on the other hand, the wait time can be specified when the standby mode is released.

- **2.** Instruction execution.

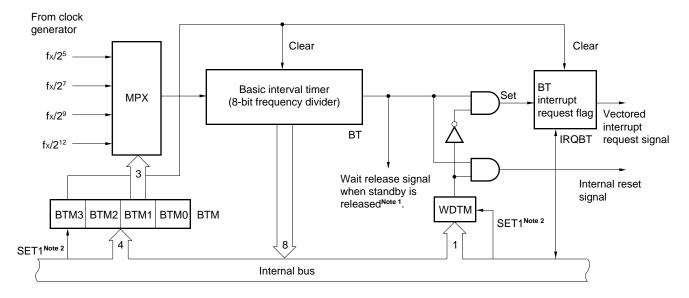

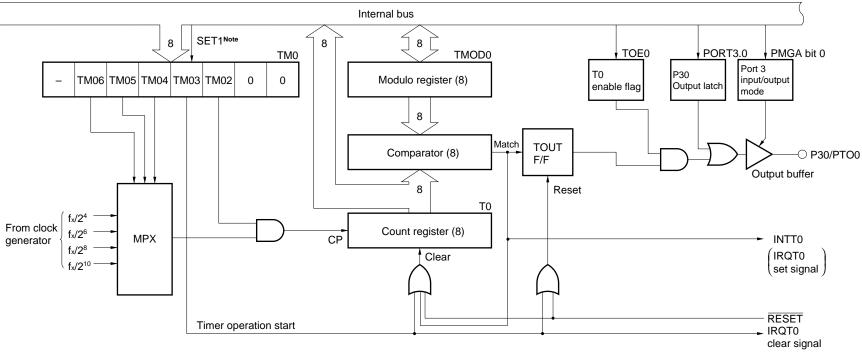

#### 7.4 Timer Counter

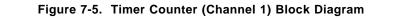

The  $\mu$ PD754244 incorporates three channels of timer counters. Its configuration is shown in Figures 7-4 to 7-6.

The timer counter has the following functions.

- (a) Programmable interval timer operation

- (b) Square wave output of any frequency to PTO0-PTO2 pins

- (c) Count value read function

The timer counter can operate in the following four modes as set by the mode register.

| Table 7-2. | Mode Lis | st |

|------------|----------|----|

|------------|----------|----|

| Mode                      | Channel 0 | Channel 1 | Channel 2 | TM11 | TM10 | TM21 | TM20 |

|---------------------------|-----------|-----------|-----------|------|------|------|------|

| 8-bit timer counter mode  | 0         | 0         | 0         | 0    | 0    | 0    | 0    |

| PWM pulse generator mode  | ×         | ×         | 0         | 0    | 0    | 0    | 1    |

| 16-bit timer counter mode | ×         | (         | C         | 1    | 0    | 1    | 0    |

| Carrier generator mode    | ×         | (         | С         | 0    | 0    | 1    | 1    |

Remark O: Available

$\times$  : Not available

NEC

**Note** Instruction execution

Caution When setting data to TM0, be sure to set bits 0 and 1 to 0.

**Note** Instruction execution

ZEO

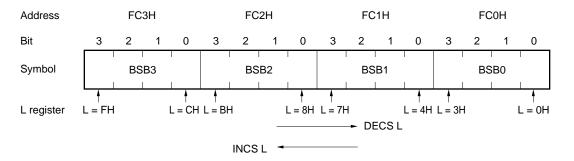

#### Internal bus <u>]</u>8] <u>∫</u>8<u></u>] ] 8 [ SETNote 8 TMOD2 TC2 TM2 TMODH PORT3.2 PMGA bit 2 High-level period setting modulo register (8) Port 3 TM26 TM25 TM24 TM23 TM22 TM21 TM20 Modulo register (8) TOE2 REMC NRZB NRZ Output 0 input/output latch 787 787 mode Reload Decoder MPX (8) Selector 18 L O P32/PTO2 Match Output buffer TOUT Comparator (8) F/F \_\_\_\_8 <sup>¯</sup> Selector fx Reset Timer counter (channel 1) f<sub>x</sub>/2 Τ2 clock input From clock Overflow fx/24 Count register (8) MPX generator CP f<sub>x</sub>/2<sup>6</sup> Clear Carrier generator mode f<sub>x</sub>/2<sup>8</sup> f<sub>x</sub>/2<sup>10</sup> INTT2 (IRQT2 16-bit timer counter mode set signal - IRQT2 clear signal Timer operation start RESET Timer counter (channel 1) clear signal (When 16-bit timer mode) Timer counter (channel 1) match signal Timer counter (channel 1) match signal (When 16-bit timer counter mode) (When Carrier generator mode)

Figure 7-6. Timer Counter (Channel 2) Block Diagram

**Note** Instruction execution

Caution When setting data to TC2, be sure to set bit 7 to 0.

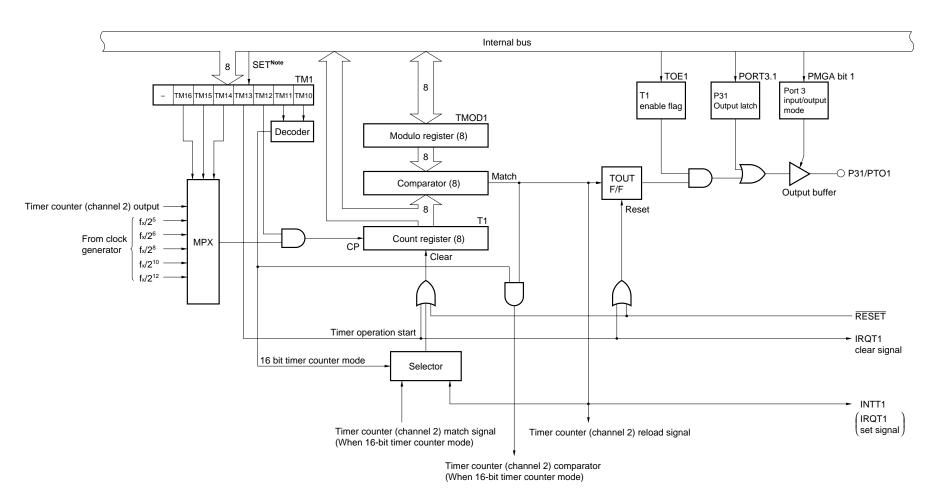

#### 7.5 Programmable Threshold Port (Analog Input Port)

The  $\mu$ PD754244 provides analog input pins (PTH00, PTH01) whose threshold voltage (reference voltage) is selectable within sixteen steps. The following operations can be performed with these analog input pins.

- (1) Comparator operation

- (2) 4-bit resolution A/D converter operation (controlled by software)

## Caution Do not specify an on-chip pull-up resistor connection for Port 6 when using the programmable threshold port.

Figure 7-7. Programmable Threshold Port Block Diagram

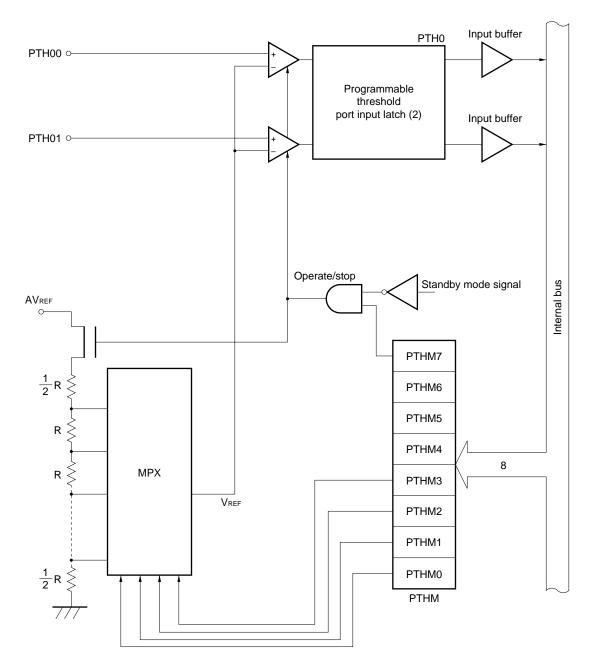

#### 7.6 Bit Sequential Buffer ...... 16 Bits

The bit sequential buffer (BSB) is a special data memory for bit manipulation and the bit manipulation can be easily performed by changing the address specification and bit specification in sequence, therefore it is useful when processing large data bit-wise.

#### Figure 7-8. Bit Sequential Buffer Format

Remarks 1. In the pmem.@L addressing, the specified bit moves corresponding to the L register.

2. In the pmem. @L addressing, the BSB can be manipulated regardless of MBE/MSB specification.

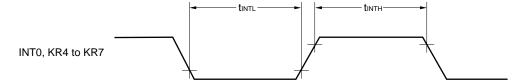

#### 8. INTERRUPT FUNCTION AND TEST FUNCTION

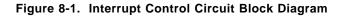

Figure 8-1 shows the interrupt control circuit. Each hardware device is mapped in the data memory space.

The interrupt control circuit of the  $\mu$ PD754244 has the following functions.

#### (1) Interrupt function

- Vectored interrupt function for hardware control, enabling/disabling the interrupt acknowledgement by the interrupt enable flag (IExxx) and interrupt master enable flag (IME).

- Can set any interrupt start address.

- Multiple interrupts wherein the order of priority can be specified by the interrupt priority select register (IPS).

- Test function of interrupt request flag (IRQ×××). An interrupt generated can be checked by software.

- Release the standby mode. A release interrupt can be selected by the interrupt enable flag.

#### (2) Test function

- Test request flag (IRQ2) generation can be checked by software.

- Release the standby mode. The test source to be released can be selected by the test enable flag.

Notes 1. Noise eliminator (Standby release is disable when noise eliminator is selected.)

2. The INT2 pin is not provided. Interrupt request flag (IRQ2) is set at the KRn pin falling edge when IM20 = 1 and IM21 = 0.

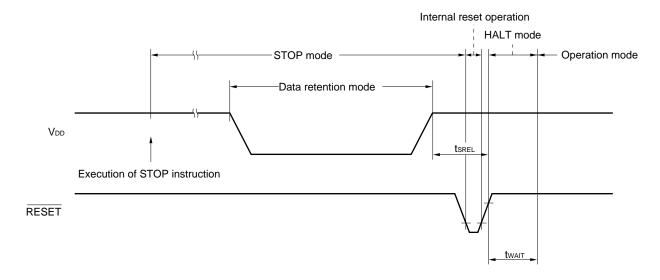

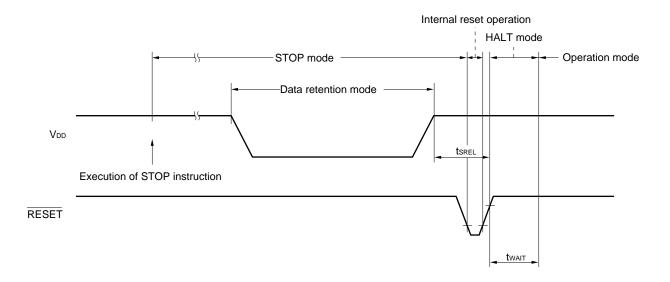

#### 9. STANDBY FUNCTION

In order to reduce power dissipation while a program is in a standby mode, two types of standby modes (STOP mode and HALT mode) are provided for the  $\mu$ PD754244.

| Item Mode                 |                                         | STOP Mode                                                                                                                                                                                                                           | HALT Mode                                                                                                                  |  |

|---------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Set instruction           |                                         | STOP instruction                                                                                                                                                                                                                    | HALT instruction                                                                                                           |  |

| Operation<br>status       | Clock generator                         | Operation stops.                                                                                                                                                                                                                    | Only the CPU clock $\Phi$ halts (oscillation continues).                                                                   |  |

|                           | Basic interval timer/<br>watchdog timer | Operation stops.                                                                                                                                                                                                                    | Operable<br>BT mode: The IRQBT is set in the basic<br>time interval.<br>WT mode: Reset is generated by the<br>BT overflow. |  |

|                           | Timer                                   | Operation stops.                                                                                                                                                                                                                    | Operable.                                                                                                                  |  |

| External interrupt<br>CPU |                                         | INT0 is not operable. <sup>Note</sup><br>INT2 is operable during KRn falling period only.                                                                                                                                           |                                                                                                                            |  |

|                           |                                         | The operation stops.                                                                                                                                                                                                                |                                                                                                                            |  |

| Release signal            |                                         | <ul> <li>Reset signal</li> <li>Interrupt request signal sent from<br/>interrupt enabled peripheral hardware</li> <li>System reset signal (key return reset)<br/>generated by KRn falling edge when the<br/>KRREN pin = 1</li> </ul> | <ul> <li>Reset signal</li> <li>Interrupt request signal sent from<br/>interrupt enabled peripheral hardware</li> </ul>     |  |

#### Table 9-1. Operation Status in Standby Mode

**Note** Can operate only when the noise eliminator is not used (IM02 = 1) by bit 2 of the edge detection mode register (IM0).

#### **10. RESET FUNCTION**

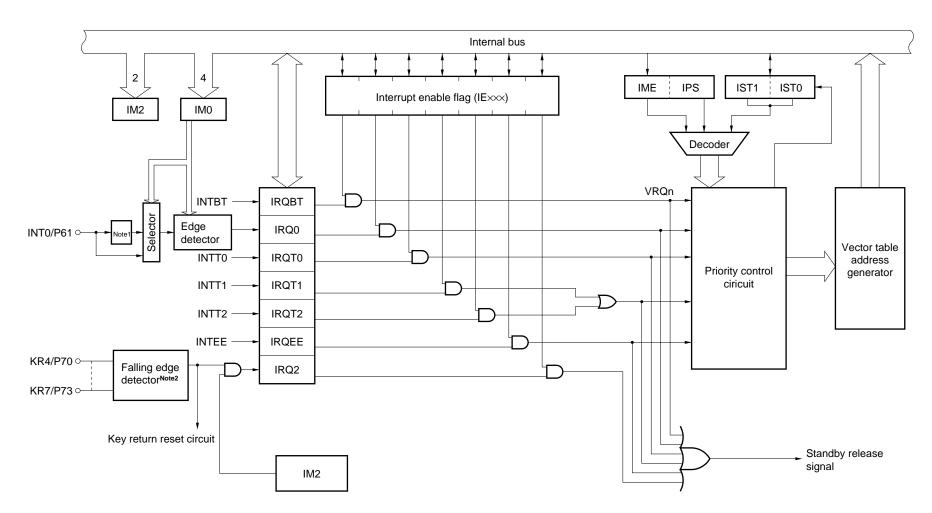

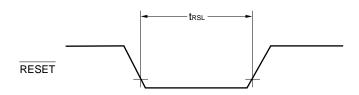

#### 10.1 Configuration and Operation Status of RESET Function

There are three kinds of reset input: the external reset signal (RESET), the reset signal sent from the basic interval/watchdog timer, and the reset signal generated by a falling edge signal from KRn in the STOP mode. When any of these reset signals is input, an internal reset signal is generated. The configuration is shown in Figure 10-1.

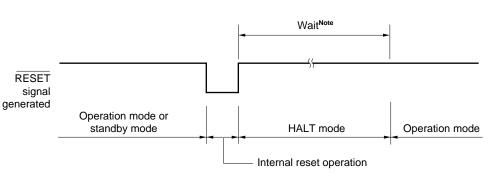

Each hardware is initialized by the  $\overrightarrow{\text{RESET}}$  signal generation as listed in Table 10-1. Figure 10-2 shows the timing chart of the reset operation.

Figure 10-2. Reset Operation by RESET Signal Generation

$2^{17}$ /fx (21.8 ms : @ 6.0-MHz operation, 31.3 ms: @ 4.19-MHz operation)  $2^{15}$ /fx (5.46 ms : @ 6.0-MHz operation, 7.81 ms: @ 4.19-MHz operation)

**Note** In the  $\mu$ PD754144, the wait time is fixed to 56/fcc (56 $\mu$ s: @ 1.0-MHz operation). In the  $\mu$ PD754244, the wait time can be selected from the following two time settings by means of the mask option.

|                      | Hardware                                           | RESET signal generation<br>in the standby mode                                          | RESET signal generation                                                                 |  |

|----------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Program counter (PC) |                                                    | Sets the low-order 4 bits of                                                            | Sets the low-order 4 bits of                                                            |  |

|                      |                                                    | program memory's address                                                                | program memory's address                                                                |  |

|                      |                                                    | 0000H to the PC11-PC8 and the contents of address 0001H to                              | 0000H to the PC11-PC8 and the                                                           |  |

|                      |                                                    | the PC7-PC0.                                                                            | contents of address 0001H to the PC7-PC0.                                               |  |

| PSW (                | Carry flag (CY)                                    | Held                                                                                    | Undefined                                                                               |  |

| :                    | Skip flag (SK0 to SK2)                             | 0                                                                                       | 0                                                                                       |  |

| 1                    | nterrupt status flag (IST0, IST1)                  | 0                                                                                       | 0                                                                                       |  |

| I                    | Bank enable flag (MBE, RBE)                        | Sets the bit 6 of program<br>memory's address 0000H to<br>the RBE and bit 7 to the MBE. | Sets the bit 6 of program<br>memory's address 0000H to<br>the RBE and bit 7 to the MBE. |  |

| Stack poir           | nter (SP)                                          | Undefined                                                                               | Undefined                                                                               |  |

| Stack ban            | k select register (SBS)                            | 1000B                                                                                   | 1000B                                                                                   |  |

| Data mem             | ory (RAM)                                          | Held                                                                                    | Undefined                                                                               |  |

| Data mem             | ory (EEPROM)                                       | Held <sup>Note 1</sup>                                                                  | Held <sup>Note 2</sup>                                                                  |  |

| EEPROM               | write control register (EWC)                       | 0                                                                                       | 0                                                                                       |  |

| General-p            | urpose register (X, A, H, L, D, E, B, C)           | Held                                                                                    | Undefined                                                                               |  |

| Bank sele            | ct register (MBS, RBS)                             | 0, 0                                                                                    | 0, 0                                                                                    |  |

| Basic interv         | val Counter (BT)                                   | Undefined                                                                               | Undefined                                                                               |  |

| timer/watch          | dog Mode register (BTM)                            | 0                                                                                       | 0                                                                                       |  |

| timer                | Watchdog timer enable flag (WDTM)                  | 0                                                                                       | 0                                                                                       |  |

| Timer cou            | nter Counter (T0)                                  | 0                                                                                       | 0                                                                                       |  |

| (channel C           | ) Modulo register (TMOD0)                          | FFH                                                                                     | FFH                                                                                     |  |

|                      | Mode register (TM0)                                | 0                                                                                       | 0                                                                                       |  |

|                      | TOE0, TOUT F/F                                     | 0, 0                                                                                    | 0, 0                                                                                    |  |

| Timer cou            | nter Counter (T1)                                  | 0                                                                                       | 0                                                                                       |  |

| (channel 1           | ) Modulo register (TMOD1)                          | FFH                                                                                     | FFH                                                                                     |  |

|                      | Mode register (TM1)                                | 0                                                                                       | 0                                                                                       |  |

|                      | TOE1, TOUT F/F                                     | 0, 0                                                                                    | 0, 0                                                                                    |  |

| Timer cou            | nter Counter (T2)                                  | 0                                                                                       | 0                                                                                       |  |

| (channel 2           | 2) Modulo register (TMOD2)                         | FFH                                                                                     | FFH                                                                                     |  |

|                      | High-level period setting modulo register (TMOD2H) | FFH                                                                                     | FFH                                                                                     |  |

|                      | Mode register (TM2)                                | 0                                                                                       | 0                                                                                       |  |

|                      | TOE2, TOUT F/F                                     | 0, 0                                                                                    | 0, 0                                                                                    |  |

|                      | REMC, NRZ, NRZB                                    | 0, 0, 0                                                                                 | 0, 0, 0                                                                                 |  |

#### Table 10-1. Hardware Status After Reset (1/3)

**Notes 1.** Undefined if STOP mode is entered during an EEPROM write operation. Also undefined if HALT mode is entered during a write operation and a RESET signal is input during a write operation.

2. If a RESET signal is input during an EEPROM write operation, the data at that address is undefined.

|                                                  | Hardware                                    | RESET signal generation in the standby mode | RESET signal generation in operation |  |

|--------------------------------------------------|---------------------------------------------|---------------------------------------------|--------------------------------------|--|

| Programmable threshold port mode register (PTHM) |                                             | 00H                                         | 00H                                  |  |

| Clock generator                                  | Processor clock control register (PCC)      | 0                                           | 0                                    |  |

| Interrupt                                        | Interrupt request flag (IRQ×××)             | Reset (0)                                   | Reset (0)                            |  |

| function                                         | Interrupt enable flag (IE×××)               | 0                                           | 0                                    |  |

|                                                  | Interrupt priority selection register (IPS) | 0                                           | 0                                    |  |

|                                                  | INT0, 2 mode registers (IM0, IM2)           | 0, 0                                        | 0, 0                                 |  |

| Digital port                                     | Output buffer                               | Off                                         | Off                                  |  |

|                                                  | Output latch                                | Cleared (0)                                 | Cleared (0)                          |  |

|                                                  | I/O mode registers (PMGA, C)                | 0                                           | 0                                    |  |

|                                                  | Pull-up resistor setting register (POGA, B) | 0                                           | 0                                    |  |

| Bit sequential buffer (BSB0-BSB3)                |                                             | Held                                        | Undefined                            |  |

#### Table 10-1. Hardware Status After Reset (2/3)

#### Table 10-1. Hardware Status After Reset (3/3)

| Hardware              | RESET signal<br>generation by key<br>return reset | RESET signal<br>generation in the<br>standby mode | RESET signal<br>generation by WDT<br>during operation | RESET signal<br>generation during<br>operation |

|-----------------------|---------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|------------------------------------------------|

| Watchdog flag (WDF)   | Hold the previous status                          | 0                                                 | 1                                                     | 0                                              |

| Key return flag (KRF) | 1                                                 | 0                                                 | Hold the previous status                              | 0                                              |

#### 10.2 Watchdog Flag (WDF), Key Return Flag (KRF)

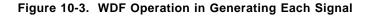

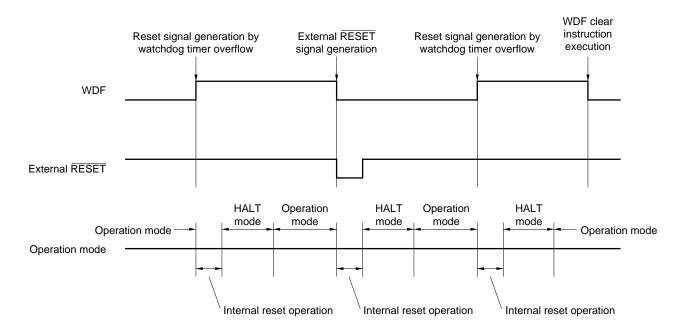

The WDF is cleared by a watchdog timer overflow signal, and the KRF is set by a reset signal generated by the KRn pins. As a result, by checking the contents of WDF and KRF, it is possible to know what kind of reset signal is generated.

As the WDF and KRF are cleared only by external signal or instruction execution, if once these flags are set, they are not cleared until an external signal is generated or a clear instruction is executed. Check and clear the contents of WDF and KRF after reset start operation by executing SKTCLR instruction and so on.

Table 10-2 lists the contents of WDF and KRF corresponding to each signal. Figure 10-3 shows the WDF operation in generating each signal, and Figure 10-4 shows the KRF operation in generating each signal.

| Hardware              | External RESET signal generation | Reset signal<br>generation by watch-<br>dog timer overflow | Reset signal<br>generation by the<br>KRn input | WDF clear<br>instruction<br>execution | KRF clear<br>instruction<br>execution |

|-----------------------|----------------------------------|------------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| Watchdog flag (WDF)   | 0                                | 1                                                          | Hold                                           | 0                                     | Hold                                  |

| Key return flag (KRF) | 0                                | Hold                                                       | 1                                              | Hold                                  | 0                                     |

Table 10-2. WDF and KRF Contents Correspond to Each Signal

Figure 10-4. KRF Operation in Generating Each Signal

# 11. MASK OPTION

The  $\mu$ PD754244 has the following mask options:

Mask option of P70/KR4 to P73/KR7

On-chip pull-up resistor connection can be specified for these pins.

- (1) Do not connect an on-chip pull-up resistor

- (2) Connect the 100-k $\Omega$  (typ.) pull-up resistor bit-wise

- Mask option of RESET pin

On-chip pull-up resistor connection can be specified for this pin.

- (1) Do not connect an on-chip pull-up resistor

- (2) Connect the 100-k $\Omega$  (typ.) pull-up resistor

• Standby function mask option ( $\mu$ PD754244 only) <sup>Note</sup>

The wait time when the  $\overline{\text{RESET}}$  signal is input can be selected.

- (1) 2<sup>17</sup>/fX (21.8 ms: @ fx = 6.0-MHz operation, 31.3 ms: @ fx = 4.19-MHz operation)

- (2)  $2^{15}$ /fX (5.46 ms: @ fx = 6.0-MHz operation, 7.81 ms: @ fx = 4.19-MHz operation)

- **Note** This mask option is not provided for the  $\mu$ PD754144, and its wait time is fixed to 56/fcc (56  $\mu$ s: @ fcc = 1.0-MHz operation).

#### **12. INSTRUCTION SETS**

#### (1) Expression formats and description methods of operands

The operand is described in the operand column of each instruction in accordance with the description method for the operand expression format of the instruction. For details, refer to "RA75X ASSEMBLER PACKAGE USERS' MANUAL — LANGUAGE (EEU-1367)". If there are several elements, one of them is selected. Capital letters and the + and – symbols are key words and are described as they are. For immediate data, appropriate numbers and labels are described.

Instead of the labels such as mem, fmem, pmem, and bit, the symbols of the registers can be described. However, there are restrictions in the labels that can be described for fmem and pmem. For details, refer to " $\mu$ PD754144, 754244 user's manual (U10676E)".

| Expression<br>format | Description method                                   |

|----------------------|------------------------------------------------------|

| reg                  | X, A, B, C, D, E, H, L                               |

| reg1                 | X, B, C, D, E, H, L                                  |

| rp                   | XA, BC, DE, HL                                       |

| rp1                  | BC, DE, HL                                           |

| rp2                  | BC, DE                                               |

| rp'                  | XA, BC, DE, HL, XA', BC', DE', HL'                   |

| rp'1                 | BC, DE, HL, XA', BC', DE', HL'                       |

| rpa                  | HL, HL+, HL–, DE, DL                                 |

| rpa1                 | DE, DL                                               |

| n4                   | 4-bit immediate data or label                        |

| n8                   | 8-bit immediate data or label                        |

| mem                  | 8-bit immediate data or label <sup>Note</sup>        |

| bit                  | 2-bit immediate data or label                        |

| fmem                 | FB0H-FBFH, FF0H-FFFH immediate data or label         |

| pmem                 | FC0H-FFFH immediate data or label                    |

| addr                 | 000H-FFFH immediate data or label                    |

| addr1                | 000H-FFFH immediate data or label                    |

| caddr                | 12-bit immediate data or label                       |

| faddr                | 11-bit immediate data or label                       |

| taddr                | 20H-7FH immediate data (where bit $0 = 0$ ) or label |

| PORTn                | PORT3, 6, 7, 8                                       |

| IE×××                | IEBT, IET0-IET2, IE0, IE2, IEEE                      |

| RBn                  | RB0-RB3                                              |

| MBn                  | MB0, MB4, MB15                                       |

Note mem can be only used for even address in 8-bit data processing.

| ) | Legend | in explanation of operation                    |

|---|--------|------------------------------------------------|

|   | А      | : A register, 4-bit accumulator                |

|   | В      | : B register                                   |

|   | С      | : C register                                   |

|   | D      | : D register                                   |

|   | Е      | : E register                                   |

|   | Н      | : H register                                   |

|   | L      | : L register                                   |

|   | Х      | : X register                                   |

|   | XA     | : XA register pair; 8-bit accumulator          |

|   | BC     | : BC register pair                             |

|   | DE     | : DE register pair                             |

|   | HL     | : HL register pair                             |

|   | XA'    | : XA' extended register pair                   |

|   | BC'    | : BC' extended register pair                   |

|   | DE'    | : DE' extended register pair                   |

|   | HL'    | : HL' extended register pair                   |

|   | PC     | : Program counter                              |

|   | SP     | : Stack pointer                                |

|   | CY     | : Carry flag, bit accumulator                  |

|   | PSW    | : Program status word                          |

|   | MBE    | : Memory bank enable flag                      |

|   | RBE    | : Register bank enable flag                    |

|   | PORTn  | : Port n (n = 3, 6, 7, 8)                      |

|   | IME    | : Interrupt master enable flag                 |

|   | IPS    | : Interrupt priority selection register        |

|   | IE×××  | : Interrupt enable flag                        |

|   | RBS    | : Register bank selection register             |

|   | MBS    | : Memory bank selection register               |

|   | PCC    | : Processor clock control register             |

|   |        | : Separation between address and bit           |

|   | (××)   | : The contents addressed by $\times\!\!\times$ |

|   | ××Н    | : Hexadecimal data                             |

|   |        |                                                |

#### (3) Explanation of symbols under addressing area column

| *1  | MB = MBE•MBS<br>(MBS = 0, 4, 15)                                                                 |                           |

|-----|--------------------------------------------------------------------------------------------------|---------------------------|

| *2  | MB = 0                                                                                           |                           |

| *3  | MBE = 0 : MB = 0 (000H to 07FH)<br>MB = 15 (F80H to FFFH)<br>MBE = 1 : MB = MBS (MBS = 0, 4, 15) | Data memory addressing    |