## **NEC** Microcomputers, Inc.

## **DIGITAL SIGNAL PROCESSOR**

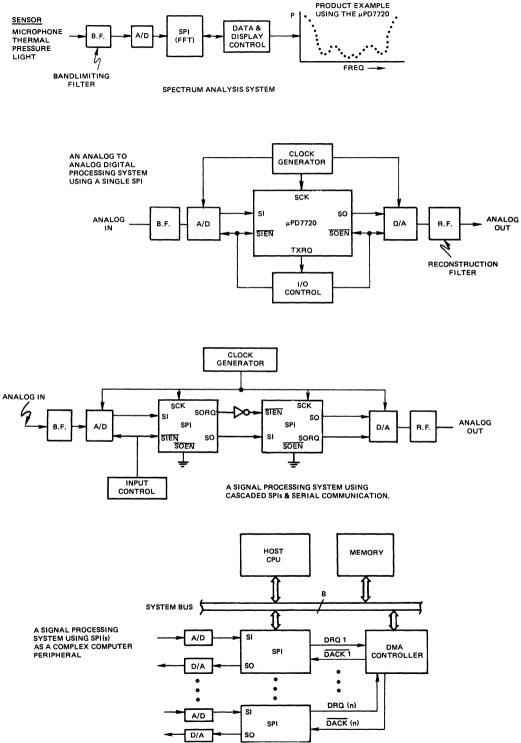

DESCRIPTION The NEC μPD7720 Signal Processing Interface (SPI) is an advanced architecture microcomputer optimized for signal processing algorithms. Its speed and flexibility allow the SPI to efficiently implement signal processing functions in a wide range of environments and applications.

The NEC SPI is the state of the art in signal processing today, and for the future.

####

- Digital Filtering

- Fast Fourier Transforms (FFT)

- Dual-Tone Multi-Frequency (DTMF) Transmitters/Receivers

- High Speed Data Modems

- Equalizers

- Adaptive Control

- Sonar/Radar Image Processing

- Numerical Processing

| PERFORMANCE<br>BENCHMARKS | <ul> <li>Second Order Digital Filter (BiQuad)</li> <li>SINE/COS of Angles</li> <li>μ/A LAW to Linear Conversion</li> <li>FFT: 32 Point Complex</li> </ul> | 2.25 μs<br>5.25 μs<br>0.50 μs<br>0.7 ms |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                           | 64 Point Complex                                                                                                                                          | 1.6 ms                                  |

### FEATURES • Fast Instruction Execution - 250 ns

- 16 Bit Data Word

- Multi-Operation Instructions for Optimizing Program Execution

- Large Memory Capacities

| — Program ROM | 512 x 23 Bits |

|---------------|---------------|

|               |               |

| - | Coefficient ROM | 510 x 13 Bits |

|---|-----------------|---------------|

|   |                 |               |

- Data RAM 128 x 16 Bits

- Fast (250 ns) 16 x 16-31 Bit Multiplier

- Dual Accumulators

- Four Level Subroutine Stack for Program Efficiency

- Multiple I/O Capabilities

- Serial

- Parallel

- DMA

- Compatible with Most Microprocessors, Including:

- μPD8080

- μPD8085

- μPD8086

- μPD780 (Z80<sup>TM\*</sup>)

- Power Supply +5V

- Technology NMOS

- Package 28 Pin Dip

<sup>\*</sup>Z80 is a trademark of Zilog Corporation.

|       | -  |                  |           |

|-------|----|------------------|-----------|

| NC    | 1  | -0               | 28 VCC    |

| DACK  | 2  |                  | 27 🗖 A0   |

| DRQ 🗖 | 3  |                  | 26 🗖 टड   |

| P0 🗖  | 4  |                  | 25 🗖 RD   |

| P1 🗖  | 5  |                  | 24 🗖 WR   |

| ₽o□   | 6  |                  | 23 SORO   |

| ₽1□   | 7  | μ <b>PD7720D</b> | 22 🗖 SO   |

| D2    | 8  |                  | 21 🗖 SI   |

| D3    | 9  |                  | 20 SOEN   |

| D₄I   | 10 |                  | 19 🗖 SIEN |

| D5    | 11 |                  | 18 🗖 SCK  |

| D6 🗆  | 12 |                  | 17 🛛 INT  |

| D7 🗖  | 13 |                  | 16 🗖 RST  |

| GND 🗖 | 14 |                  | 15 CLK    |

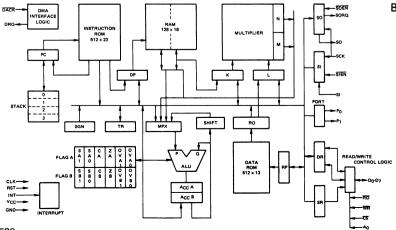

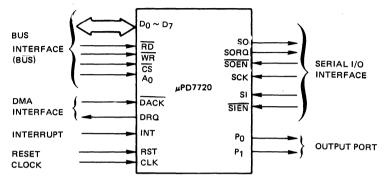

Fabricated in high speed NMOS, the µPD7720 SPI is a complete 16-bit microcomputer FUNCTIONAL DESCRIPTION on a single chip. ROM space is provided for program and coefficient storage, while the on-chip RAM may be used for temporary data, coefficients and results. Computational power is provided by a 16-bit Arithmetic/Logic Unit (ALU) and a separate 16 x 16 bit fully parallel multiplier. This combination allows the implementation of a "sum of products" operation in a single 250 nsec instruction cycle. In addition, each arithmetic instruction provides for a number of data movement operations to further increase throughput. Two serial I/O ports are provided for interfacing to codecs and other serially-oriented devices while a parallel port provides both data and status information to conventional  $\mu P$  for more sophisticated applications. Handshaking signals, including DMA controls, allow the SPI to act as a sophisticated programmable peripheral as well as a stand alone microcomputer.

Memory is divided into three types, Program ROM, Data ROM, and Data RAM. The 512 x 23 bit words of Program ROM are addressed by a 9-bit Program Counter which can be modified by an external reset, interrupt, call, jump, or return instruction.

The Data ROM is organized in  $512 \times 13$  bit words and is also addressed through a 9-bit ROM pointer (RP Reg.) which may be modified as part of an arithmetic instruction so that the next value is available for the next instruction. The Data ROM is ideal for storing the necessary coefficients, conversion tables and other constants for all your processing needs.

The Data RAM is 128 x 16 bit words and is addressed through a 7-bit Data Pointer (DP Reg.). The DP has extensive addressing features that operate simultaneously with arithmetic instructions so that no added time is taken for addressing or address modification.

### PIN CONFIGURATION

### MEMORY

**BLOCK DIAGRAM**

I

### PIN IDENTIFICATION

| PIN  | NAME                           | 1/0          | FUNCTION                                                                                                                                                                                                            |

|------|--------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | NC                             | 1            | No Connection.                                                                                                                                                                                                      |

| 2    | DACK                           | 1            | DMA Request Acknowledge. Indicates to the $\mu$ PD7720 that the Data Bus is ready for a DMA transfer. ( $\overline{DACK} = \overline{CS} \bullet A_0 = 0$ )                                                         |

| 3    | DRQ                            | 0            | DMA Request signals that the $\mu$ PD7720 is requesting a data transfer on the Data Bus.                                                                                                                            |

| 4,5  | P0, P1                         | 0            | $P_0$ , $P_1$ are general purpose output control lines.                                                                                                                                                             |

| 6-13 | D <sub>0</sub> -D <sub>7</sub> | 1/O Tristate | Port for data transfer between the Data Register or Status Register and Data Bus.                                                                                                                                   |

| 14   | GND                            |              |                                                                                                                                                                                                                     |

| 15   | CLK                            | I            | Single phase Master Clock input.                                                                                                                                                                                    |

| 16   | RST                            | I            | Reset initializes the $\mu$ PD7720 internal logic and sets the PC to 0.                                                                                                                                             |

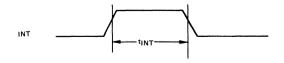

| 17   | INT                            | I            | Interrupt. A low to high transition on this pin<br>will (if interrupts are enabled by the program)<br>execute a call instruction to location 100H.                                                                  |

| 18   | SCK                            | I            | Serial Data Input/Output Clock. A serial data<br>bit is transferred when this pin is high.                                                                                                                          |

| 19   | SIEN                           | I            | Serial Input Enable. This line enables the shift clock to the Serial Input Register.                                                                                                                                |

| 20   | SOEN                           | I            | Serial Output Enable. This pin enables the shift clock to the Serial Output Register.                                                                                                                               |

| 21   | SI                             | I            | Serial Data Input. This pin inputs 8 or 16 bit<br>serial data words from an external device such<br>as an A/D converter.                                                                                            |

| 22   | SO                             | 0            | Serial Data Output. This pin outputs 8 or 16<br>bit data words to an external device such as an<br>D/A converter.                                                                                                   |

| 23   | SORQ                           | 0            | Serial Data Output Request. Specifies to an<br>external device that the Serial Data Register<br>has been loaded and is ready for output.<br>SORQ is reset when the entire 8 or 16 bit<br>word has been transferred. |

| 24   | WR                             | 1            | Write Control Signal writes the contents of data bus into the Data Register.                                                                                                                                        |

| 25   | RD                             | 1            | Read Control Signal. Enables an output to the Data Port from the Data or Status Register.                                                                                                                           |

| 26   | <del>cs</del>                  | I            | Chip Select. Enables data transfer with Data or Status Port with $\overline{\text{RD}}$ or $\overline{\text{WR}}$ .                                                                                                 |

| 27   | A <sub>0</sub>                 | I            | Selects Data Register for Read/Write (low) or Status Register for read (high).                                                                                                                                      |

| 28   | Vcc                            |              | +5V Power                                                                                                                                                                                                           |

## μ PD7720

### General

One of the unique features of the SPI's architecture is its arithmetic facilities. With a separate multipler, ALU, and multiple internal data paths, the SPI is capable of carrying out a multiply, an add, or other arithmetic operation, and move data between internal registers in a single instruction cycle.

### ALU

The ALU is a 16-bit 2's complement unit capable of executing 16 distinct operations on virtually any of the SPI's internal registers, thus giving the SPI both speed and versatility for efficient data management.

### Accumulators (ACCA/ACCB)

Associated with the ALU are a pair of 16-bit accumulators, each with its own set of flags, which are updated at the end of each arithmetic instruction (except NOP). In addition to Zero Result, Sign Carry, and Overflow Flags, the SPI incorporates auxilliary Overflow and Sign Flags (SA1, SB1, OVA1, OVB1). These flags enable the detection of an overflow condition and maintain the correct sign after as many as 3 successive additions or subtractions.

| FLAG A | SA1 | SA0 | СА | ZA | OVA1 | OVA0 |

|--------|-----|-----|----|----|------|------|

| FLAG B | SB1 | SB0 | СВ | ZB | OVB1 | OVB0 |

### ACC A/B FLAG REGISTERS

### Sign Register (SGN)

When OVA1 (or OVB1) is set, the SA1 (or SB1) bit will hold the corrected sign of the overflow. The SGN Register will use SA1 (SB1) to automatically generate saturation constants 7FFFH(+) or 8000H(-) to permit efficient limiting of a calculated valve.

### Multiplier

Thirty-one bit results are developed by a 16 x 16 bit 2's complement multiplier in 250 ns. The result is automatically latched in 2-16-bit registers M&N (LSB in N is zero) at the end of each instruction cycle. The ability to have a new product available and to be able to use it in each instruction cycle, provides significant advantages in maximizing processing speed for real time signal processing.

### Stack

The SPI contains a 4-level program stack for efficient program usage and interrupt handling.

### Interrupt

A single level interrupt is supported by the SPI. Upon sensing a high level on the INT terminal, a subroutine call to location 100H is executed. The EI bit of the status register is automatically reset to 0 thus disabling the interrupt facilities until reenabled under program control.

### ARITHMETIC CAPABILITIES

### INPUT/OUTPUT General

The NEC SPI has 3 communication ports; 2 serial and one 8-bit parallel, each with their own control lines for interface handshaking. The parallel port also includes DMA control lines (DRQ and DACK) for high speed data transfer and reduced processor overhead. A general purpose 2 bit output (see Figure 1) port, rounds out a full complement of interface capability.

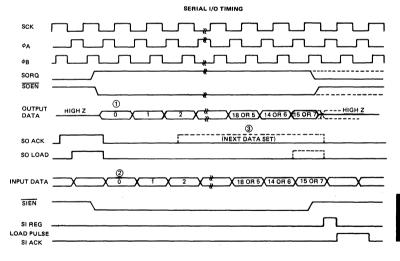

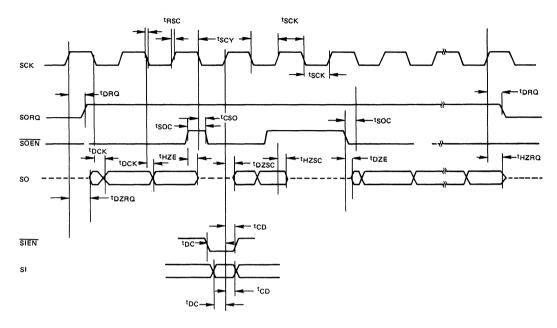

### Serial I/O

Two shift registers (SI, SO) that are software-configurable to 8 or 16 bits and are externally clocked (SCK) provide simple interface between the SPI and serial peripherals such as, A/D and D/A converters, codecs, or other SPIs.

1 Data clocked out on falling edge of SCK.

② Data clocked in on rising edge of SCK.

3 Broken line denotes consecutive sending of next data.

# PARALLEL I/O The 8-bit parallel I/O port may be used for transferring data or reading the SPI's status. Data transfer is handled through a 16-bit Data Register (DR) that is software-configurable for double or single byte data transfers. The port is ideally suited for operating with 8080, 8085 and 8086 processor buses and may be used with other processors and computer systems.

| CS     | A <sub>0</sub> | WR  | RD                                                     | OPERATION                                                              |

|--------|----------------|-----|--------------------------------------------------------|------------------------------------------------------------------------|

| 1<br>X | x ð<br>x       | × 1 | $\left\{ \begin{array}{c} x \\ 1 \end{array} \right\}$ | { No effect on internal operation. D₀-D⁊ are at high impedance levels. |

| 0      | 0              | 0   | 1                                                      | Data from D0-D7 is latched to DR ()                                    |

| 0      | 0              | 1   | 0                                                      | Contents of DR are output to D0-D7 (1)                                 |

| 0      | 1              | 0   | 1                                                      | lilegal                                                                |

| 0      | 1              | 1   | 0                                                      | Eight MSBs of SR are output to D0-D7                                   |

| 0      | x              | 0   | 0                                                      | Illegal                                                                |

### PARALLEL R/W OPERATION

① Eight MSBs or 8 LSBs of data register (DR) are used depending on DR status bit (DRS).

The condition of  $\overrightarrow{DACK} = 0$  is equivalent to  $A_0 = \overrightarrow{CS} = 0$ .

### Status Register (SR)

MSB

LSB

|     |      |      |     |     |     |     |     |    |   |   |   | _   |   |    |    |  |

|-----|------|------|-----|-----|-----|-----|-----|----|---|---|---|-----|---|----|----|--|

| RQM | USF1 | USFO | DRS | DMA | DRC | soc | SIC | EI | 0 | 0 | 0 | ° O | 0 | P1 | PO |  |

|     |      | L    | ·   |     |     |     |     |    |   |   | _ | _   | - |    |    |  |

The status register is a 16-bit register in which the 8 most significant bits may be read by the system's MPU for the latest I/O and processing status.

| RQM (Request for Master):                        | A read or write from DR to IDB sets RQM = 1. An<br>Ext read (write) resets RQM = 0.                                 |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| USF1 — (User Flag 1):)<br>USF0 — (User Flag 0):) | General purpose flags which may be read by an external processor for user defined signalling                        |

| DRS – (DR Status):                               | For 16 bit DR transfers (DRC = 0) DRS = 1 after<br>first 8 bits have been transferred, DRS = 0 after all<br>16 bits |

| DMA (DMA Enable):                                | DMA = 0 (Non DMA transfer mode)<br>DMA = 1 (DMA transfer mode)                                                      |

| DRC – (DR Control):                              | DRC = 0 (16 bit mode), DRC = 1 (8 bit mode)                                                                         |

| SOC - (SO Control):                              | SOC = 0 (16 bit mode), $SOC = 1$ (8 bit mode)                                                                       |

| SIC – (SI Control):                              | SIC = 0 (16 bit mode), SIC = 1 (8 bit mode)                                                                         |

| EI – (Enable Interrupt):                         | EI = 0 (interrupts disabled), EI = 1 (interrupts enabled)                                                           |

| PO/P1 (Ports 0 and 1):                           | PO and P1 directly control the state of output pins PO and P1                                                       |

## INSTRUCTIONS T

The SPI has 3 types of instructions all of which are one word, 23 bits long and execute in 250 ns.

|    | 22 21 | 20 19        | 18 17 | 16 15 | 14          | 13 12    | 11 10 9            | 8                     | 7 | 65  | 4 | 3 | 2  | 1 | 0 |

|----|-------|--------------|-------|-------|-------------|----------|--------------------|-----------------------|---|-----|---|---|----|---|---|

| OP | 00    | P-<br>SELECT | A     | LU    | A<br>S<br>L | DPL      | DP <sub>H</sub> ⋅M | R<br>P<br>D<br>C<br>B |   | SRC |   |   | DS | т |   |

| RT | 01    |              |       |       | Sa          | ime as O | P instruction      | 1                     |   |     |   |   |    |   |   |

### A) Arithmetic/Move-Return (OP = 00/RT = 01)

There are two instructions of this type, both of which are capable of executing all ALU functions listed in Table 2 on the value specified by the ALU input (i.e., P select field see Table 1).

| Table 1. OP, RT | т | able | 1. | OP, | RT |

|-----------------|---|------|----|-----|----|

|-----------------|---|------|----|-----|----|

|          | P-Select Field                  |                    |

|----------|---------------------------------|--------------------|

| Mnemonic | D <sub>20</sub> D <sub>19</sub> | ALU Input          |

| RAM      | 0 0                             | RAM                |

| IDB      | 0 1                             | *Internal Data Bus |

| м        | 1 0                             | M Register         |

| N        | . 1 1                           | N Register         |

\*Any value on the on-chip data bus. Value may be selected from any of registers listed in Table 7 source register selections.

## μPD7720

| Table | 2. | OP, | RT |

|-------|----|-----|----|

|-------|----|-----|----|

| Flags | Affected |

|-------|----------|

|          |     | ALU | Field |     |                                    | Flag A | SA1 | SA0 | CA | ZA | OVA1 | OVA0 |

|----------|-----|-----|-------|-----|------------------------------------|--------|-----|-----|----|----|------|------|

| Mnemonic | D18 | D17 | D16   | D15 | ALU Function                       | Flag B | SB1 | SB0 | СВ | ZB | OVB1 | OVB0 |

| NOP      | 0   | 0   | 0     | 0   | No Operation                       |        | -   | -   | -  |    | -    | -    |

| OR       | 0   | 0   | 0     | 1   | OR                                 |        | ø   | \$  | \$ | ø  | ø    | ø    |

| AND      | 0   | 0   | 1     | 0   | AND                                |        | ø   | \$  | \$ | ø  | ø    | ø    |

| XOR      | 0   | 0   | 1     | 1   | Exclusive OR                       |        | ø   | \$  | \$ | ø  | ø    | ø    |

| SUB      | 0   | 1   | 0     | 0   | Subtract                           |        | \$  | \$  | \$ | \$ | \$   | ø    |

| ADD      | 0   | 1   | 0     | 1   | ADD                                |        | \$, | \$  | \$ | \$ | \$   | \$   |

| SBB      | 0   | 1   | 1     | 0   | Subtract with<br>Borrow            |        | \$  | \$  | \$ | ¢  | \$   | \$   |

| ADC      | 0   | 1   | 1     | 1   | Add with Carry                     |        | \$  | \$  | \$ | \$ | \$   | \$   |

| DEC      | 1   | 0   | 0     | 0   | Decrement ACC                      |        | \$  | \$  | \$ | \$ | \$   | \$   |

| INC      | 1   | 0   | 0     | 1   | Increment ACC                      |        | \$  | \$  | \$ | \$ | \$   | \$   |

| СМР      | 1   | 0   | 1     | 0   | Complement ACC<br>(1's Complement) |        | \$  | \$  | \$ | ø  | ø    | ø    |

| SHR1     | 1   | 0   | 1     | 1   | 1-bit R-Shift                      |        | \$  | \$  | ÷∳ | ø  | ø    | ø    |

| SHL1     | 1   | 1   | 0     | 0   | 1-bit L-Shift                      |        | \$  | \$  | \$ | ø  | ø    | ø    |

| SHL2     | 1   | 1   | 0     | 1   | 2-bit L-Shift                      |        | ø   | \$  | \$ | ø  | ø    | ø    |

| SHL4     | 1   | 1   | 1     | 0   | 4-bit L-Shift                      |        | ø   | \$  | \$ | ø  | ø    | ø    |

| хснд     | 1   | 1   | 1     | 1   | 8-bit Exchange                     |        | ø   | \$  | \$ | ø  | ø    | ø    |

Affected by result

No affect

Reset

Table 3. OP, RT

|          | ASL Field |                   |

|----------|-----------|-------------------|

| Mnemonic | D14       | ACC Selection     |

| ACCA     | 0         | A <sub>CC</sub> A |

| ACCB     | 1         | A <sub>CC</sub> B |

### Table 4. OP, RT

|          | DPL             | Field |               |

|----------|-----------------|-------|---------------|

| Mnemonic | D <sub>13</sub> | D12   | DP3-DP0       |

| DPNOP    | 0               | 0     | No Operation  |

| DPINC    | 0               | 1     | Increment DPL |

| DPDEC    | 1               | 0     | Decrement DPL |

| DPCLR    | 1               | 1     | Clear DPL     |

Table 5. OP, RT

|          | DP              | <sub>1</sub> -M Fi | eld |                  | ;                                        |    |  |  |  |  |  |  |  |  |  |

|----------|-----------------|--------------------|-----|------------------|------------------------------------------|----|--|--|--|--|--|--|--|--|--|

| Mnemonic | D <sub>11</sub> | D10                | Dg  | Exclusive OR     |                                          |    |  |  |  |  |  |  |  |  |  |

| MO       | 0               | 0                  | 0   | (DP <sub>6</sub> | DP <sub>5</sub> DP <sub>4</sub> ) ¥ (0 0 | 0) |  |  |  |  |  |  |  |  |  |

| M1       | 0               | 0                  | 1   | DP6              | $DP_5 DP_4 \neq (0 0)$                   | 1) |  |  |  |  |  |  |  |  |  |

| M2       | 0               | 1                  | 0   | DP <sub>6</sub>  | DP <sub>5</sub> •DP <sub>4</sub> ¥ (0 1  | 0) |  |  |  |  |  |  |  |  |  |

| M3       | 0               | 1                  | 1   | DP <sub>6</sub>  | DP <sub>5</sub> DP <sub>4</sub> ¥ (0 1   | 1) |  |  |  |  |  |  |  |  |  |

| M4       | 1               | 0                  | 0   | DP <sub>6</sub>  | DP <sub>5</sub> DP <sub>4</sub> ¥ (1 0   | 0) |  |  |  |  |  |  |  |  |  |

| M5       | 1               | 0                  | 1   | DP <sub>6</sub>  | $DP_5 DP_4 \neq (1 0)$                   | 1) |  |  |  |  |  |  |  |  |  |

| M6       | 1               | 1                  | 0   | DP6              | DP <sub>5</sub> DP <sub>4</sub> ¥ (1 1   | 0) |  |  |  |  |  |  |  |  |  |

| M7       | 1               | 1                  | 1   | DP6              | DP <sub>5</sub> DP <sub>4</sub> ¥ (1 1   | 1  |  |  |  |  |  |  |  |  |  |

2) 22

| Table 6. | OP,RT |

|----------|-------|

|----------|-------|

|          | RPDCR          |              |

|----------|----------------|--------------|

| Mnemonic | D <sub>8</sub> | Operation    |

| RPNOP    | 0              | No Operation |

| RPDEC    | 1              | Decrement RP |

Besides the arithmetic functions these instructions can also modify (1) the RAM Data Pointer DP, (2) the Data ROM Pointer RP, and (3) move data along the on-chip data bus from a source register to a destination register (the possible source and destination registers are listed in Tables 7 and 8 respectively). The difference in the two instructions of this type is that one executes a subroutine or interrupt return at the end of the instruction cycle while the other does not.

|          |    | SRC | Field | d  |                       |

|----------|----|-----|-------|----|-----------------------|

| Mnemonic | D7 | D6  | D5    | D4 | Specified Register    |

| NON      | 0  | 0   | 0     | 0. | NO Register           |

| А        | 0  | 0   | 0     | 1  | ACC A (Accumulator A) |

| В        | 0  | 0   | 1     | 0  | ACC B (Accumulator B) |

| TR       | 0  | 0   | 1     | 1  | TR Temporary Register |

| DP       | 0  | 1   | 0     | 0  | DP Data Pointer       |

| RP       | 0  | 1   | 0     | 1  | RP ROM Pointer        |

| RO       | 0  | 1   | 1     | 0  | RO ROM Output Data    |

| SGN      | 0  | 1   | 1     | 1  | SGN Sign Register     |

| DR       | 1  | 0   | 0     | 0  | DR Data Register      |

| DRNF     | 1  | 0   | 0     | 1  | DR Data No Flag ①     |

| SR       | 1  | 0   | 1     | 0  | SR Status             |

| SIM      | 1  | 0   | 1     | 1  | SI Serial in MSB (2)  |

| SIL      | 1  | 1   | 0     | 0  | SI Serial in LSB ③    |

| к        | 1  | .1  | 0     | 1  | K Register            |

| L        | 1  | 1   | 1     | 0  | L Register            |

| MEM      | 1  | 1   | 1     | 1  | RAM                   |

| Table 7. | OP, I | RT |

|----------|-------|----|

|----------|-------|----|

1 DR to IDB RQM not set. IN DMA DRQ not set.

② First bit in goes to MSB, last bit to LSB.

③ First bit in goes to LSB, last bit to MSB (bit reversed).

Table 7 - List of Registers Specified by the Source Field (SRC)

|          |    | DST            | Field | d              |                                              |  |  |  |  |  |  |  |

|----------|----|----------------|-------|----------------|----------------------------------------------|--|--|--|--|--|--|--|

| Mnemonic | D3 | D <sub>2</sub> | D1    | D <sub>0</sub> | Specified Register                           |  |  |  |  |  |  |  |

| @NON     | 0  | 0              | 0     | 0              | NO Register                                  |  |  |  |  |  |  |  |

| @A       | 0  | Ò              | 0     | 1              | ACC A (Accumulator A)                        |  |  |  |  |  |  |  |

| @B       | 0  | 0              | 1     | 0              | ACC B (Accumulator B)                        |  |  |  |  |  |  |  |

| @TR      | 0  | 0              | 1     | 1              | TR Temporary Register                        |  |  |  |  |  |  |  |

| @DP      | 0  | 1              | 0     | 0              | DP Data Pointer                              |  |  |  |  |  |  |  |

| @RP      | 0  | 1              | 0     | 1              | RP ROM Pointer                               |  |  |  |  |  |  |  |

| @DR      | 0  | 1              | 1     | 0              | DR Data Register                             |  |  |  |  |  |  |  |

| @SR      | 0  | 1              | 1     | 1              | SR Status Register                           |  |  |  |  |  |  |  |

| @SOL     | 1  | 0              | 0     | 0              | SO Serial Out LSB ①                          |  |  |  |  |  |  |  |

| @SOM     | 1  | 0              | 0     | 1              | SO Serial Out MSB ②                          |  |  |  |  |  |  |  |

| @K       | 1  | 0              | 1     | 0              | K (Mult)                                     |  |  |  |  |  |  |  |

| @KLR     | 1  | 0              | 1     | 1              | $IDB \rightarrow K ROM \rightarrow L$ ③      |  |  |  |  |  |  |  |

| @KLM     | 1  | 1              | 0     | 0              | Hi RAM $\rightarrow$ K IDB $\rightarrow$ L ④ |  |  |  |  |  |  |  |

| @L       | 1  | 1              | 0     | 1              | L (Mult)                                     |  |  |  |  |  |  |  |

| @NON     | 1  | 1              | 1     | 0              | NO Register                                  |  |  |  |  |  |  |  |

| @MEM     | 1  | 1              | 1     | 1              | RAM                                          |  |  |  |  |  |  |  |

Table 8. OP, RT, LDI

1 LSB is first bit out.

② MSB is first bit out.

③ Internal data bus to K and ROM to L register.

④ Contents of RAM address specified by DP<sub>6</sub> = 1 (i.e., 1, DP<sub>5</sub>, DP<sub>4</sub>, DP<sub>0</sub>) is placed in K register. IDB is placed in L.

Table 8 - List of Registers Specified by the Destination Field (DST)

### B) Jump/Call/Branch

| 22 | 21     | 20 | 19  | 18 | 17 | 16 | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7 | 6 | 5 | 4 | Ş | 2 | 1 | 0 |  |

|----|--------|----|-----|----|----|----|-----|----|----|----|----|----|---|----|---|---|---|---|---|---|---|---|--|

| 1( | )<br>) | Е  | RCH | 1  |    |    | CND |    |    |    |    |    | ٢ | ١A |   |   |   |   |   |   | / | 7 |  |

### JP Instruction Field Specifications

Three types of execution address modification instructions are accommodated by the processor and are listed in Table 9. All of the instructions, if unconditional or the specified condition is true, take their next program execution address from the Next Address field (NA), otherwise PC = PC + 1.

### Table 9. Branch Field Selections (BRCH)

| 20 | 19 | 18 | Instruction      |

|----|----|----|------------------|

| 1  | 0  | 0  | Uncondition jump |

| 1  | 0  | 1  | Subroutine call  |

| 0  | 1  | 0  | Condition jump   |

For the conditional jump instruction, the condition field specifies the jump condition. Table 10 lists all the instruction mnemonics of the J/C/B OP codes.

The SPI offers all the execution modification instructions necessary for efficient, data, I/O and arithmetic control.

| Mnemonic | D <sub>20</sub> | D19 | D <sub>18</sub> | D17 | D16 | D15 | D14 | D13 | Conditions    |

|----------|-----------------|-----|-----------------|-----|-----|-----|-----|-----|---------------|

| JMP      | 1.              | 0   | 0               | 0   | 0   | 0   | 0   | 0   | No Condition  |

| CALL     | 1               | 0   | 1               | 0   | 0   | • 0 | 0   | 0   | No Condition  |

| JNCA     | 0               | 1   | 0               | 0   | 0   | 0   | 0   | 0   | CA = 0        |

| JCA      | 0               | 1   | 0               | 0   | 0   | 0   | 0   | 1   | CA = 1        |

| JNCB     | 0               | 1   | 0               | 0   | 0   | 0   | 1   | 0   | CB = 0        |

| JCB      | 0               | 1   | 0               | 0   | 0   | 0   | 1   | 1   | CB = 1        |

| JNZA     | 0               | 1   | 0               | 0   | 0   | 1   | 0   | 0   | ZA = 0        |

| JZA      | 0               | 1   | 0               | 0   | 0   | 1   | 0   | 1   | ZA = 1        |

| JNZB     | 0               | 1   | 0               | 0   | 0   | 1   | 1   | 0   | ZB = 0        |

| JZB      | 0               | 1   | 0               | 0   | 0   | 1   | 1   | 1   | ZB = 1        |

| JNOVA0   | 0               | 1   | 0               | 0   | 1   | 0   | 0   | 0   | OVA0 = 0      |

| JOVA0    | 0               | 1   | 0               | 0   | 1   | 0   | 0   | 1   | OVA0 = 1      |

| JNOVB0   | 0               | 1   | 0               | 0   | 1   | 0   | 1   | 0   | OVB0 = 0      |

| JOVB0    | 0               | 1   | 0               | 0   | 1   | 0   | 1   | 1   | OVB0 = 1      |

| JNOVA1   | 0               | 1   | 0               | 0   | 1   | 1   | 0   | 0   | OVA1 = 0      |

| JOVA1    | 0               | 1   | 0               | 0   | 1   | 1   | 0   | 1   | 0VA1 = 1      |

| JNOVB1   | 0               | 1   | 0               | 0   | 1   | 1   | 1   | 0   | OVB1 = 0      |

| JOVB1    | 0               | 1   | 0               | 0   | 1   | 1   | 1   | 1   | OVB1 = 1      |

| JNSA0    | 0               | 1   | 0               | 1   | 0   | 0   | 0   | 0   | SA0 = 0       |

| JSA0     | 0               | 1   | 0               | 1   | 0   | 0   | 0   | 1   | SA0 = 1       |

| JNSB0    | 0               | 1   | 0               | 1   | 0   | 0   | 1   | 0   | SB0 = 0       |

| JSB0     | 0               | 1   | 0               | 1   | 0   | 0   | 1   | 1   | SB0 = 1       |

| JNSA1    | 0               | 1   | 0               | 1   | 0   | 1   | 0   | 0   | SA1 = 0       |

| JSA1     | 0               | 1   | 0               | 1   | 0   | 1   | 0   | 1   | SA1 = 1       |

| JNSB1    | 0               | 1   | 0               | 1   | 0   | 1   | 1   | 0   | SB1 = 0       |

| JSB1     | 0               | 1   | 0               | 1   | 0   | 1   | 1   | 1   | SB1 = 1       |

| JDPL0    | 0               | 1   | 0               | 1   | 1   | 0   | 0   | 0   | DPL = 0       |

| JDPLF    | 0               | 1   | 0               | 1   | 1   | 0   | 0   | 1   | DPL = F (HEX) |

| JNSIAK   | 0               | 1   | 0               | 1   | 1   | 0   | 1   | 0   | SI ACK = 0    |

| JSIAK    | 0               | 1   | 0               | 1   | 1   | -0  | 1   | 1   | SI ACK = 1    |

| JNSOAK   | 0               | 1   | 0               | 1   | 1   | 1   | 0   | 0   | SO ACK = 0    |

| JSOAK    | 0               | 1   | 0               | 1   | 1   | 1   | 0   | 1   | SO ACK = 1    |

| JNRQM    | 0               | 1   | 0               | 1   | 1   | 1   | 1   | 0   | RQM = 0       |

| JRQM     | 0               | 1   | 0               | 1   | 1   | 1   | 1   | 1   | RQM = 1       |

Table 10. Condition Field Specifications

\*BRCH or CND values not in this table are prohibited.

## **µPD7720**

### C) Load Data (LDI)

| 22 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|----|---|

| 11    |    |    |    |    |    |    |    | ł  | 2  |    |    |   |   |   |   |   | / |   | D | sт |   |

The Load Data instruction will take the 16-bit value contained in the Immediate Data field (ID) and place it in the location specified by the Destination field (DST) (see Table 8).

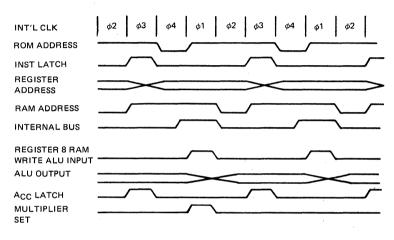

INSTRUCTION EXECUTION TIMING

|          | Voltage (V <sub>CC</sub> Pin)                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| RATINGS* | Voltage, Any Input $\ldots$ Voltage, Any Input $\ldots$ Voltage, Any Input $\ldots$ Voltage, Any Input $\ldots$                           |

|          | Voltage, Any Output                                                                                                                       |

|          | Operating Temperature $\dots \dots \dots$ |

|          | Storage Temperature                                                                                                                       |

Note: 1 With respect to GND.

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent : damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*T<sub>a</sub> = 25°C

### DC CHARACTERISTICS

$T_a = -10 \sim +70^{\circ}$  C,  $V_{CC} = +5V \pm 5\%$

| PARAMETER            | SYMBOL          | MIN  | түр | MAX                  | UNIT | CONDITION                 |

|----------------------|-----------------|------|-----|----------------------|------|---------------------------|

| Input Low Voltage    | VIL             | -0.5 |     | 0.8                  | v    |                           |

| Input High Voltage   | VIH             | 2.0  |     | V <sub>CC</sub> +0.5 | v    |                           |

| CLK Low Voltage      | V <sub>øL</sub> | -0.5 |     | 0.45                 | v    |                           |

| CLK High Voltage     | V <sub>ØH</sub> | 3.5  |     | Vcc +0.5             | v    |                           |

| Output Low Voltage   | VOL             |      |     | 0.45                 | V    | IOL = 2.0 mA              |

| Output High Voltage  | ∨он             | 2.4  |     |                      | V    | I <sub>OH</sub> = -400 μA |

| Input Load Current   | LIL             |      |     | -10                  | μA   | VIN = 0V                  |

| Input Load Current   | LIH             |      |     | 10                   | μA   | VIN = VCC                 |

| Output Float Leakage | LOL             |      |     | -10                  | μA   | VOUT = VCC                |

| Output Float Leakage | LOH             |      |     | 10                   | μA   | V <sub>OUT</sub> = 0.47V  |

| Power Supply Current | Icc             |      | 200 | 280                  | mA   |                           |

| CAPACI | TANCE |

|--------|-------|

|--------|-------|

| PARAMETER                     | SYMBOL | MIN | TYP | MAX | UNIT | CONDITION              |

|-------------------------------|--------|-----|-----|-----|------|------------------------|

| CLK, SCK Input<br>Capacitance | Cφ     |     |     | 20  | pF   |                        |

| Input Pin Capacitance         | CIN    |     | ·   | 10  | ρF   | f <sub>c</sub> = 1 MHz |

| Output Pin Capacitance        | COUT   |     |     | 20  | рF   |                        |

## μPD7720

$T_a = -10 \sim +70^{\circ}$ C,  $V_{CC} = +5V \pm 5\%$

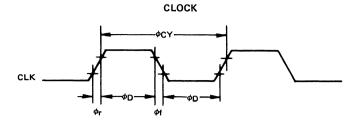

| PARAMETER                             | SYMBOL             | MIN | ТҮР | MAX  | UNIT | CONDITION               |

|---------------------------------------|--------------------|-----|-----|------|------|-------------------------|

| CLK Cycle Time                        | ΦCY                | 125 |     | 2000 | ns   |                         |

| CLK Pulse Width                       | φD                 | 50  |     |      | ns   |                         |

| CLK Rise Time                         | ¢R                 |     |     | 20   | ns   |                         |

| CLK Fall Time                         | ΦF                 |     |     | 20   | ns   |                         |

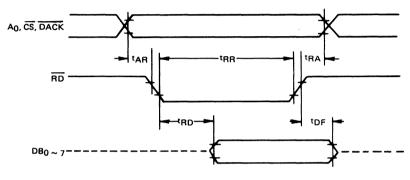

| Address Setup Time for RD             | <sup>t</sup> AR    | 0   |     |      | ns   |                         |

| Address Hold Time for RD              | <sup>t</sup> RA    | 0   |     |      | ns   |                         |

| RD Pulse Width                        | t <sub>RR</sub>    | 200 |     |      | ns   |                         |

| Data Delay from RD                    | tRD                |     |     | 150  | ns   | C <sub>L</sub> = 100 pF |

| Read to Data Floating                 | tDF                | 20  |     | 100  | ns   | CL = 100 pF             |

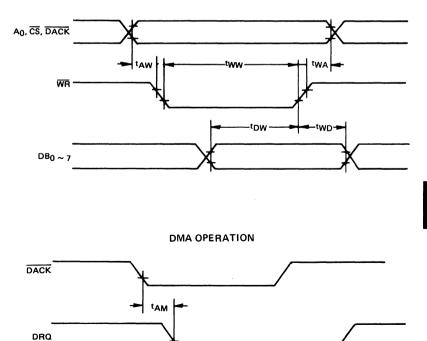

| Address Setup Time for WR             | tAW                | 0   |     |      | ns   |                         |

| Address Hold Time for WR              | tWA                | 0   |     |      | ns   |                         |

| WR Pulse Width                        | tww                | 200 |     |      | ns   |                         |

| Data Setup Time for WR                | tDW                | 150 |     |      | ns   |                         |

| Data Hold Time for WR                 | twd                | 0   |     |      | ns   |                         |

| DRQ Delay                             | <sup>t</sup> AM    |     |     | 150  | ns   | CL = 100 pF             |

| SCK Cycle Time                        | tSCY               | 480 |     | DC   | ns   |                         |

| SCK Pulse Width                       | <sup>t</sup> SCK   | 230 |     |      | ns   |                         |

| SCK Rise/Fall Time                    | tRSC               |     |     | 20   | ns   |                         |

| SORQ Delay                            | t DRQ              | 30  |     | 150  | ns   | CL = 100 pF             |

| SOEN Setup Time                       | tsoc               | 50  |     |      | ns   |                         |

| SOEN Hold Time                        | tCSO               | 10  |     |      | ns   |                         |

| SO Delay                              | <sup>t</sup> DCK   |     |     | 150  | ns   |                         |

| SO Delay from SORQ                    | <sup>t</sup> DZRQ  | *   |     |      |      |                         |

| SO Delay from SCK                     | tDZSC              | *   |     |      |      |                         |

| SO Delay from SOEN                    | <sup>t</sup> DZE   | *   |     |      |      |                         |

| SOEN to SO Floating                   | tHZE               | *   |     |      |      |                         |

| SCK to SO Floating                    | tHZSC              | *   |     |      |      |                         |

| SORO to SO Floating                   | tHZRO              | *   |     |      |      |                         |

| SIEN, SI Setup Time                   | tDC                | 50  |     |      | ns   |                         |

| SIEN, SI Hold Time                    | <sup>t</sup> CD    | 20  |     |      | ns   |                         |

| P <sub>0</sub> , P <sub>1</sub> Delay | tDP                |     |     | 300  | ns   |                         |

| RST Pulse Width                       | <sup>t</sup> RST   | 4   |     |      | ØCY  |                         |

| INT Pulse Width                       | • <sup>t</sup> INT | 8   |     |      | ΦCΥ  |                         |

\*To be specified

### AC CHARACTERISTICS

WRITE OPERATION

РОЯТ ОUТРИТ СLК Ро, Р1

## μPD7720

7720DS-12-80-CAT