# **NEC Microcomputers, Inc.**

# **16 BIT MICROPROCESSOR**

DESCRIPTION

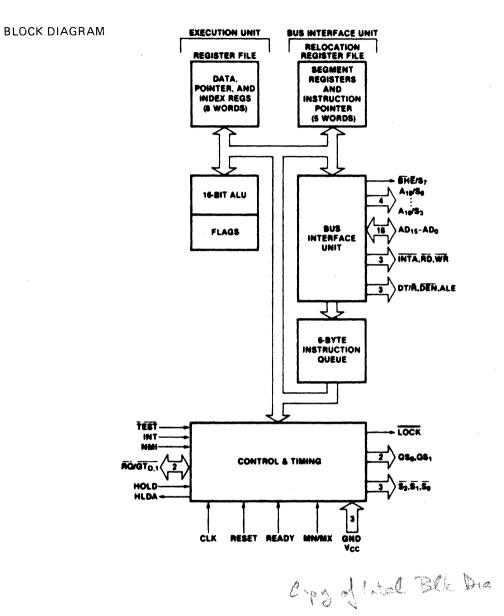

The  $\mu$ PD8086 is a 16-bit microprocessor that has both 8-bit and 16-bit attributes. It has a 16-bit wide physical path to memory for high performance. Its architecture allows higher throughput than the 5 MHz  $\mu$ PD8085A-2.

- FEATURES Can Directly Address 1 Megabyte of Memory

- Fourteen 16-Bit Registers with Symmetrical Operations

- Bit, Byte, Word, and Block Operations

- 8 and 16-Bit Signed and Unsigned Arithmetic Operations in Binary or Decimal

- Multiply and Divide Instructions

- 24 Operand Addressing Modes

- Assembly Language Compatible with the μPD8080/8085

- Complete Family of Components for Design Flexibility

#### PIN CONFIGURATION GND d 1 40 D Vcc AD14 d 2 39 h AD15 3 A16/S3 38 AD13 4 37 🗖 A17/S4 AD12 AD11 5 36 A18/S5 35 A19/S6 AD10 C 6 34 BHE/ST AD9 C 7 33 MN/MX 32 RD 31 HOLD 8 AD8 AD7 C 9 AD6 10 (RO/GTO) **µ**PD8086 AD5 11 30 (RQ/GT1) CPU AD4 12 29 (LOCK) AD3 13 28 (S2) AD2 C 14 27 (\$1) DEN AD1 С (50) 15 26 AD0 (QS0) 25 16 NMI (QS1) 17 24 TEST INTR 18 23 CLK B READY 19 22 21 B RESET GND 20

| NO.                 | SYMBOL                                | NAME                             | FUNCTION                                                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------------|---------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2-16, 39            | AD0-AD15                              | Address/Data Bus                 | Multiplexed address (T <sub>1</sub> ) and data (T <sub>2</sub> , T <sub>3</sub> , T <sub>W</sub> , T <sub>4</sub> ) bus.<br>8-bit paripherals tied to the lower 8 bits, use A0 to condition<br>chip select functions. These lines are tri-state during interrupt<br>acknowledge and hold states. |  |  |  |  |

| -17                 | NMI                                   | Non-Maskable<br>Interrupt        | This is an edge triggered input causing a type Z interrupt. A<br>look-up table is used by the processor for vectoring<br>information.                                                                                                                                                            |  |  |  |  |

| 18                  | INTR                                  | Interrupt Request                | A level triggered input sampled on the last clock cycle of<br>each instruction. Vectoring is via an interrupt look-up table.<br>INTR can mask in software by resetting the interrupt enable<br>bit.                                                                                              |  |  |  |  |

| 19                  | CLK                                   | Clock                            | The clock input is a 1/3 duty cycle input basic timing for the processor and bus controller.                                                                                                                                                                                                     |  |  |  |  |

| 21                  | RESET                                 | Reset                            | This active high signal must be high for 4 clock cycles. When<br>it returns low, the processor restarts execution.                                                                                                                                                                               |  |  |  |  |

| 22                  | READY                                 | Ready                            | An acknowledgement from memory or I/O that data will be transferred. Synchronization is done by the µPD8284 clock generator.                                                                                                                                                                     |  |  |  |  |

| 23                  | TEST                                  | Test                             | This input is examined by the "WAIT" instruction, and if<br>low, execution continues. Otherwise the processor waits in an<br>"Idle" state. Synchronized by the processor on the leading<br>edge of CLK.                                                                                          |  |  |  |  |

| 24                  | INTA                                  | Interrupt<br>Acknowledge         | This is a read strobe for reading vectoring information. During T <sub>2</sub> , T <sub>3</sub> , and T <sub>W</sub> of each interrupt acknowledge cycle it is low.                                                                                                                              |  |  |  |  |

| 25                  | ALE                                   | Address Latch Enable             | This is used in conjunction with the $\mu$ PD8282/8283 latches to latch the address, during T <sub>1</sub> of any bus cycle.                                                                                                                                                                     |  |  |  |  |

| 26                  | DEN                                   | Data Enable                      | This is the output enable for the µPD8282/8287 transceivers.<br>It is active low during each memory and I/O access and<br>INTA cycles.                                                                                                                                                           |  |  |  |  |

| 27                  | DT/R                                  | Data Transmit/Receive            | Used to control the direction of data flow through the transceivers.                                                                                                                                                                                                                             |  |  |  |  |

| 28                  | м/іо                                  | Memory/IO Status                 | This is used to separate memory access from I/O access.                                                                                                                                                                                                                                          |  |  |  |  |

| 29                  | WR                                    | Write                            | Depending on the state of the $M/\overline{10}$ line, the processor is either writing to I/O or memory.                                                                                                                                                                                          |  |  |  |  |

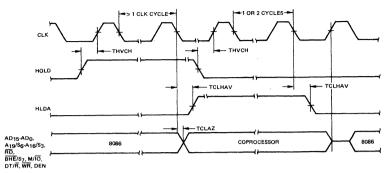

| 30                  | HLDA                                  | Hold Acknowledge                 | A response to the HOLD input, causing the processor to<br>tri-state the local bus. The bus return active one cycle after<br>HOLD goes back low.                                                                                                                                                  |  |  |  |  |

| 31                  | HOLD                                  | Hold                             | When another device requests the local bus, driving HOLD high, will cause the $\mu PD8086$ to issue a HLDA.                                                                                                                                                                                      |  |  |  |  |

| 32                  | RĎ                                    | Read                             | Depending on the state of the M/IO line, the processor is reading from either memory or I/O.                                                                                                                                                                                                     |  |  |  |  |

| 33                  | MN/MX                                 | Minimum/Maximum                  | This input is to tell the processor which mode it is to be used<br>in. This effects some of the pin descriptions.                                                                                                                                                                                |  |  |  |  |

| 34                  | BHE/S7                                | Bus/High Enable                  | This is used in conjunction with the most significant half of<br>the data bus. Peripheral devices on this half of the bus use<br>BHE to condition chip select functions.                                                                                                                         |  |  |  |  |

| 35-38               | A16-A19                               | Most Significant<br>Address Bits | The four most significant address bits for memory opera-<br>tions, Low during I/O operations.                                                                                                                                                                                                    |  |  |  |  |

| 26, 27, 28<br>34-38 | S0-S7                                 | Status Outputs                   | These are the status outputs from the processor. They are used by the $\mu$ PD8288 to generate bus control signals.                                                                                                                                                                              |  |  |  |  |

| 24, 25              | <b>QS<sub>1</sub>, QS<sub>0</sub></b> | Que Status                       | Used to track the internal $\mu$ PD8086 instruction que.                                                                                                                                                                                                                                         |  |  |  |  |

| 29                  | LOCK                                  | Lock                             | This output is set by the "LOCK" instruction to prevent<br>other system bus masters from gaining control.                                                                                                                                                                                        |  |  |  |  |

| 30, 31              | RO/GTO<br>RO/GT1                      | Request/Grant                    | Other local bus masters can force the processor to rebase the local bus at the end of the current bus cycle.                                                                                                                                                                                     |  |  |  |  |

#### PIN IDENTIFICATION

| Operating Temperature                     | ABSOLUTE MAXIMUM |

|-------------------------------------------|------------------|

| Storage Temperature                       | RATINGS*         |

| Voltage on Any Pin with Respect to Ground |                  |

| Power Dissipation                         |                  |

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$T_a = 25^{\circ}C$

|                                                                      |                 |      |                       |          | TEST                           | DC CHARACTERISTICS |

|----------------------------------------------------------------------|-----------------|------|-----------------------|----------|--------------------------------|--------------------|

| PARAMETER                                                            | SYMBOL          | MIN  | MAX                   | UNITS    | CONDITIONS                     |                    |

| Input Low Voltage                                                    | VIL             | -0.5 | +0.8                  | v        |                                |                    |

| Input High Voltage                                                   | ∨ін             | 2.0  | V <sub>CC</sub> + 0.5 | v        |                                |                    |

| Output Low Voltage                                                   | VOL             |      | 0.45                  | v        | I <sub>OL</sub> = 2.0 mA       |                    |

| Output High Voltage                                                  | ∨он             | 2.4  |                       | v        | I <sub>OH</sub> = -400 μA      |                    |

| Power Supply Current<br>µPD8086/<br>µPD8086-2                        | ICC             |      | 340<br>350            | mA<br>mA | T <sub>a</sub> = 25°C          |                    |

| Input Leakage Current                                                | ILI             |      | ±10                   | μA       | 0V < VIN < VCC                 |                    |

| Output Leakage Current                                               | <sup>I</sup> LO |      | ±10                   | μA       | $0.45V \le V_{OUT} \le V_{CC}$ |                    |

| Clock Input Low Voltage                                              | VCL             | -0.5 | +0.6                  | v        |                                |                    |

| Clock Input High Voltage                                             | Vсн.            | 3.9  | VCC + 1.0             | v        |                                |                    |

| Capacitance of Input Buffer<br>(All input except<br>AD0-AD15, RQ/GT) | CIN             |      | 15                    | pF       | fc = 1 MHz                     |                    |

| Capacitance of I/O Buffer<br>(AD0-AD15, RQ/GT)                       | C10             |      | 15                    | pF       | fc = 1 MHz                     | ].                 |

$T_a = 0^{\circ}C$  to  $70^{\circ}C$ ;  $V_{CC} = 5V \pm 10\%$

#### $\mu$ PD8086: T<sub>a</sub> = 0°C to 70°<u>C</u>; V<sub>CC</sub> = 5V ± 10%

#### AC CHARACTERISTICS

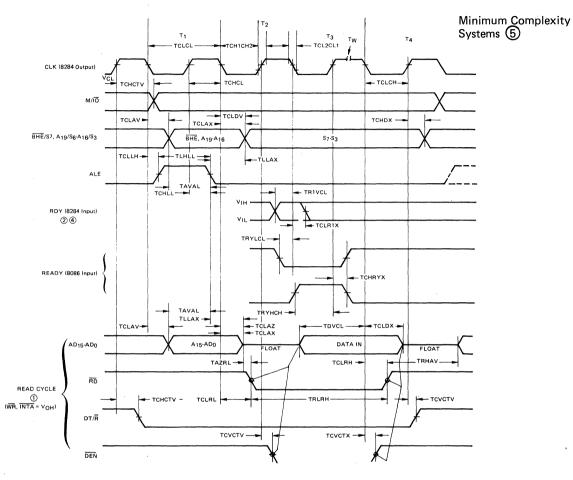

MINIMUM COMPLEXITY SYSTEM

|                                    |         | TIMING          | REQUIR | EMENTS            |         |       |                  |

|------------------------------------|---------|-----------------|--------|-------------------|---------|-------|------------------|

|                                    |         | μ <b>PD8086</b> |        | µPD8086-2 (Prelim | ninary) |       | TEST             |

| PARAMETER                          | SYMBOL  | MIN             | MAX    | MIN               | MAX     | UNITS | CONDITIONS       |

| CLK Cycle Period – µPD8086         | TCLCL   | 200             | 500    | 125               | 500     | ns    |                  |

| CLK Low Time                       | TCLCH   | (2/3 TCLCL) -15 |        | (2/3 TCLCL) -15   |         | ns    |                  |

| CLK High Time                      | TCHCL   | (1/3 TCLCL) +2  |        | (1/3 TCLCL) +2    |         | ns    |                  |

| CLK Rise Time                      | TCH1CH2 |                 | 10     |                   | 10      | ns    | From 1.0V to 3.5 |

| CLK Fall Time                      | TCL2CL1 |                 | 10     |                   | 10      | ns    | From 3.5V to 1.0 |

| Data In Setup Time                 | TDVCL   | 30              |        | 20                |         | ns    |                  |

| Data In Hold Time                  | TCLDX   | 10              |        | 10                |         | ns    |                  |

| RDY Setup Time into µPD8284<br>① ② | TRIVCL  | 35              |        | 35                |         | ns    |                  |

| RDY Hold Time into µPD8284<br>① ②  | TCLR1X  | 0               |        | 0                 |         | ns    |                  |

| READY Setup Time into #PD8086      | TRYHCH  | (2/3 TCLCL) -15 |        | (2/3 TCLCL) -15   |         | ns    |                  |

| READY Hold Time into µPD8086       | TCHRYX  | 30              |        | 20                |         | ns    |                  |

| READY Inactive to CLK              | TRYLCL  | -8              |        | 8                 |         | ns    |                  |

| HOLD Setup Time                    | тнусн   | 35              |        | 20                |         | ns    |                  |

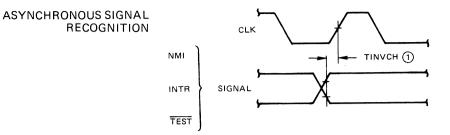

| INTR, NMI, TEST Setup Time         | TINVCH  | 30              |        | 15                |         | ns    |                  |

#### TIMING RESPONSES

|                                    |        | TIM             | ING RE | SPONSES          |         |       |                     |

|------------------------------------|--------|-----------------|--------|------------------|---------|-------|---------------------|

|                                    |        | μ <b>PD8086</b> |        | μPD8086-2 (Preli | minary) |       | TEST                |

| PARAMETER                          | SYMBOL | MIN             | MAX    | MIN              | MAX     | UNITS | CONDITIONS          |

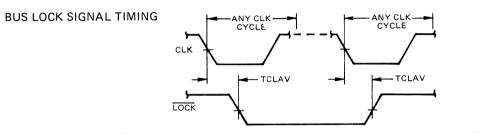

| Address Valid Delay                | TCLAV  | 10              | 110    | 10               | 60      |       |                     |

| Address Hold Time                  | TCLAX  | 10              |        | 10               |         | ns    |                     |

| Address Float Delay                | TCLAZ  | TCLAX           | 80     | TCLAX            | 50      | ns    |                     |

| ALE Width                          | TLHLL  | TCLCH-20        |        | TCLCH-10         |         | ns    |                     |

| ALE Active Delay                   | TCLLH  |                 | 80     |                  | 50      | ns    |                     |

| ALE Inactive Delay                 | TCHLL  |                 | 85     |                  | 55      | ns    |                     |

| Address Hold Time to ALE Inactive  | TLLAX  | TCHCL-10        |        | TCHCL-10         |         | ns    |                     |

| Data Valid Delay                   | TCLDV  | 10              | 110    | 10               | 60      | ns    | CL = 20-100 pF for  |

| Data Hold Time                     | TCHDX  | 10              | 1      | 10               |         | ns    | all µPD8086 Outputs |

| Data Hold Time After WR            | TWHDX  | TCLCH-30        |        | TCLCH-30         |         | ns    | µPD8086 self-load)  |

| Control Active Delay 1             | TCVCTV | 10              | 110    | 10               | 70      | ns    |                     |

| Control Active Delay 2             | тснсту | 10              | 110    | 10               | 60      | ns    |                     |

| Control Active Delay               | TCVCTX | 10              | 110    | 10               | 70      | ns    |                     |

| Address Float to READ Active       | TAZRL  | 0               |        | 0                |         | ns    |                     |

| RD Active Delay                    | TCLRL  | 10              | 165    | 10               | 100     | ns    |                     |

| RD Inactive Delay                  | TCLRH  | 10              | 150    | 10               | 80      | ns    |                     |

| RD Inactive to Next Address Active | TRHAV  | TCLCL-45        |        | TCLCL-40         |         | ns    |                     |

| HLDA Valid Delay                   | TCLHAV | 10              | 160    | 10               | 100     | ns    |                     |

| RD Width                           | TRLRH  | 2TCLCL-75       |        | 2TCLCL-50        |         | ns    |                     |

| WR Width                           | TWLWH  | 2TCLCL-60       |        | 2TCLCL-40        |         | ns    |                     |

| Address Vaild to ALE Low           | TAVAL  | TCLCH-60        |        | TCLCH-40         | T       | ns    |                     |

NOTES:

① Signal at µPD8284 shown for reference only.

② Setup requirement for asynchronous signal only to guarantee recognition at next CLK.

③ Applies only to T2 state. (8 ns into T3)

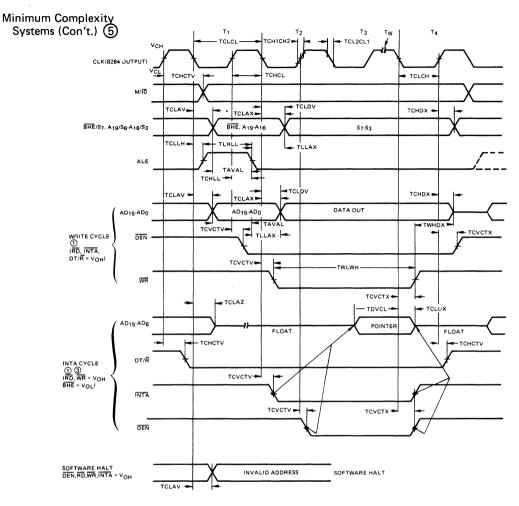

#### TIMING WAVEFORMS

#### **TIMING WAVEFORMS**

- NOTES: (1) All signals switch between V<sub>OH</sub> and V<sub>OL</sub> unless otherwise specified.

- (2) RDY is sampled near the end of T<sub>2</sub>, T<sub>3</sub>, T<sub>W</sub> to determine if T<sub>W</sub> machines states are to be inserted.

- 3 Two INTA cycles run back-to-back. The μPD8086 local ADDR/Data Bus is floating during both INTA cycles. Control signals shown for second INTA cycle.

- (4) Signals at  $\mu$ PD8284 are shown for reference only.

- (5) All timing measurements are made at 1.5V unless otherwise noted.

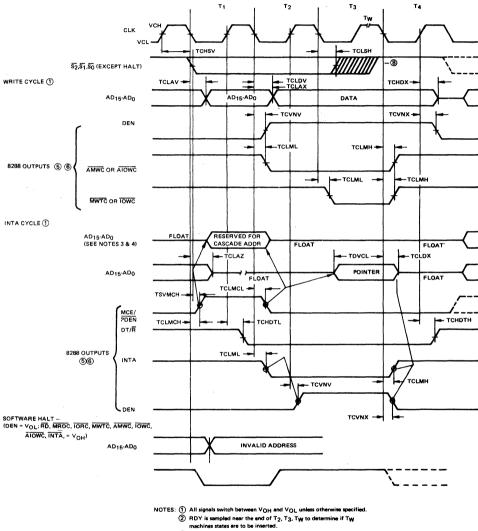

#### TIMING WITH µPB8288 BUS CONTROLLER

| •                                                 |         | TIMIN           | IG REQ | UIREMENTS         |        |       |                   |

|---------------------------------------------------|---------|-----------------|--------|-------------------|--------|-------|-------------------|

| ,                                                 |         | μ <b>PD8086</b> |        | µPD8086-2 (Prelim | inary) |       | TEST              |

| PARAMETER                                         | SYMBOL  | MIN             | MAX    | MIN               | MAX    | UNITS | CONDITIONS        |

| CLK Cycle Period - µPD8086                        | TCLCL   | 200             | 500    | 125               | 500    | ns    |                   |

| CLK Low Time                                      | TCLCH   | (2/3 TCLCL) -15 |        | (2/3 TCLCL) -15   |        | ns    |                   |

| CLK High Time                                     | TCHCL   | (1/3 TCLCL) +2  |        | (1/3 TCLCL) +2    |        | ns    |                   |

| CLK Rise Time                                     | TCH1CH2 |                 | 10     |                   | 10     | ns    | From 1.0V to 3.5V |

| CLN Fall Time                                     | TCL2CL1 |                 | 10     |                   | 10     | ns    | From 3.5V to 1.0V |

| Data in Setup Time                                | TDVCL   | 30              |        | 20                |        | ns    |                   |

| Data in Hold Time                                 | TCLDX   | 10              |        | 10                |        | ns    |                   |

| RDY Setup Time into µPD8284                       | TRIVCL  | 35              |        | 35                |        | ns    |                   |

| RDY Hold Time into µPD8284                        | TCLR1X  | 0               |        | 0                 |        | ns    |                   |

| READY Setup Time into #PD8086                     | TRYHCH  | (2/3 TCLCL) -15 |        | (2/3 TCLCL) -15   |        | ns    |                   |

| READY Hold Time into µPD8086                      | TCHRYX  | 30              |        | 20                |        | ns    |                   |

| READY inactive to CLK                             | TRYLCL  | -8              | ч.     | -8                |        | ns    |                   |

| Setup Time for Recognition<br>(INTR, NMI, TEST) ② | TINVCH  | 30              |        | 15                |        | ns    |                   |

| RQ/GT Setup Time                                  | TGVCH   | 30              |        | . 15              |        | ns    |                   |

| RQ Hold Time into #PD8086                         | тсндх   | 40              |        | 30                |        | ns    |                   |

#### MAXIMUM MODE SYSTEM

With µPB8288 Bus Controller

|                                                  |        | #PD8086   |     | µPD8086-2 (Prelim | inary) |       |                                        |

|--------------------------------------------------|--------|-----------|-----|-------------------|--------|-------|----------------------------------------|

| PARAMETER                                        | SYMBOL | MIN       | мах | MIN               | мах    | UNITS | TEST<br>CONDITIONS                     |

| Command Active Delay<br>(See Note 1)             | TCLML  | 10        | 35  | 10                | 35     | ns    |                                        |

| Command Inactive Delay<br>(See Note 1)           | TCLMH  | 10        | 35  | 10                | 35     | ns    |                                        |

| READY Active to Status Passive<br>(See Note 3)   | TRYHSH |           | 110 |                   | 65     | ns    |                                        |

| Status Active Delay                              | TCHSV  | 10        | 110 | 10                | 60     | ns    |                                        |

| Status Inactive Delay                            | TCLSH  | 10        | 130 | 10                | 70     | ns    |                                        |

| Address Valid Delay                              | TCLAV  | 10        | 110 | 10                | 60     | ns    |                                        |

| Address Hold Time                                | TCLAX  | 10        |     | 10                |        | ns    |                                        |

| Address Float Delay                              | TCLAZ  | TCLAX     | 80  | TCLAX             | 50     | ns    |                                        |

| Status Valid to ALE High<br>(See Note 1)         | TSVLH  |           | 15  |                   | 15     | ns    |                                        |

| Status Valid to MCE High<br>(See Note 1)         | тѕумсн |           | 15  |                   | 15     | ns    |                                        |

| CLK Low to ALE Valid<br>(See Note 1)             | TCLLH  |           | 15  |                   | 15     | ns    |                                        |

| CLK Low to MCE High<br>(See Note 1)              | TCLMCH |           | 15  |                   | 15     | ns    |                                        |

| ALE Inactive Delay (See Note 1)                  | TCHLL  |           | 15  |                   | 15     | ns    | C <sub>L</sub> = 20-100 pF for         |

| MCE Inactive Delay (See Note 1)                  | TCLMCL |           | 15  |                   | 15     | ns    | all µPD8086 Outputs<br>(In addition to |

| Data Valid Delay                                 | TCLDV  | 10        | 110 | 10                | 60     | ns    | µPD8086 self-load)                     |

| Data Hold Time                                   | TCHDX  | 10        |     | 10                |        | ns    | 1                                      |

| Control Active Delay (See Note 1)                | TCVNV  | 5         | 45  | 5                 | 45     | ns    |                                        |

| Control Inactive Delay<br>(See Note 1)           | TCVNX  | 10        | 45  | 10                | 45     | ns    |                                        |

| Address Float to Read Active                     | TAZRL  | 0         |     | 0                 |        | ns    |                                        |

| RD Active Delay                                  | TCLRL  | 10        | 165 | 10                | 100    | ns    |                                        |

| RD Inactive Delay                                | TCLRH  | 10        | 150 | 10                | 80     | ns    |                                        |

| RD Inactive to Next Address Active               | TRHAV  | TCLCL-45  |     | TCLCL-40          |        | ns    |                                        |

| Direction Control Active Delay<br>(See Note 1)   | TCHDTL |           | 50  |                   | 50     | ns    |                                        |

| Direction Control Inactive Delay<br>(See Note 1) | тснотн |           | 30  |                   | 30     | ns    |                                        |

| GT Active Delay                                  | TCLGL  | 0         | 85  | 0                 | 50     | ns    |                                        |

| GT Inactive Delay                                | TCLGH  | 0         | 85  | 0                 | 50     | ns    |                                        |

| RD Width                                         | TRLRH  | 2TCLCL-50 |     | 2TCLCL-50         |        | ns    |                                        |

|                                                  |        |           |     |                   |        |       |                                        |

#### TIMING RESPONSES

NOTES:

① Signal at µPB8284 or µPB8288 shown for reference only.

②

Setup requirement for skynchronous signal only to guarantee recognition at next CLK.

③

Applies only to T3 and wait states.

④

Applies only to T2 state (8 ns into T3).

#### **TIMING WAVEFORMS**

# TIMING WAVEFORMS Maximum Mode System Using μPB8288 Controller (Con't.) 7

- (3) Cascade address is valid between first and second INTA cycle.

- Two INTA cycles run back-to-back. The 8086 local ADDR/Data Bus is floating during both INTA cycles. Control for pointer address is shown for second INTA cycle.

- (5) Signals at 8284 or 8288 are shown for reference only.

- (6) The issuance of the 8288 command and control signals (MRDC, MWTC, AMWC, IORC, IOWC, AIOWC, INTA and DEN) lags the active high 8288 CEN.

- ⑦ All timing measurements are made at 1.5V unless otherwise noted.

- (8) Status inactive in state just prior to T4.

NOTE: (1) Setup requirements for asynchronous signals only to guarantee recognition at next CLK.

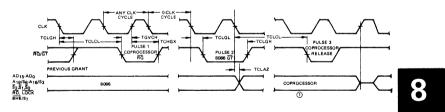

#### REQUEST/GRANT SEQUENCE TIMING\*

NOTE: (1) The coprocessor may not drive the buses outside the region shown without risking contention.

\*for Maximum Mode only

# HOLD/HOLD ACKNOWLEDGE TIMING\*

\*for Minimum Mode only

| ~  | 6  | •  |  |

|----|----|----|--|

| Ce | ra | Ip |  |

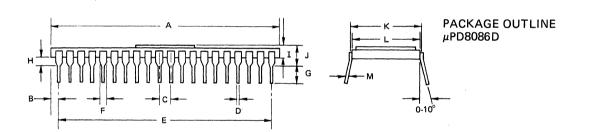

| ITEM | MILLIMETERS | INCHES        |

|------|-------------|---------------|

| A    | 51.5 MAX.   | 2.03 MAX.     |

| Β.   | 1.62 MAX.   | 0.06 MAX.     |

| С    | 2,54 ± 0.1  | 0.1 ± 0.004   |

| D    | 0.5 ± 0.1   | 0.02 ± 0.004  |

| E    | 48.26 ± 0.1 | 1.9 ± 0.004   |

| F    | 1.02 MIN.   | 0.04 MIN.     |

| G    | 3,2 MIN.    | 0,13 MIN.     |

| Н    | 1.0 MIN.    | 0.04 MIN.     |

| I    | 3.5 MAX.    | 0.14 MAX.     |

| J    | 4,5 MAX.    | 0.18 MAX.     |

| К    | 15.24 TYP.  | 0.6 TYP.      |

| L    | 14.93 TYP.  | 0.59 TYP.     |

| M    | 0.25 ± 0.05 | 0.01 ± 0.0019 |