# Standard Products UT699E 32-bit Fault-Tolerant SPARC<sup>TM</sup> V8/LEON 3FT Processor

Datasheet March 2015 www.aeroflex.com/LEON

#### FEATURES

- □ Backward compatible with the UT699

- □ Supports up to 100MHz clock rate

- □ Separate instruction and data cache architecture

- □ High-performance pipelined IEEE-754 FPU

- □ Enhanced pipeline with 1.2 DMIPS / MHz performance

- □ Implemented on 130nm CMOS technology

- □ Internally configured clock network

- □ Power saving 1.2V core power supply

- □ 3.3V I/O compatibility

- On-board programmable timers and interrupt controllers

- □ SEU hardened-by-design flip-flops and memory cells

- □ 10/100 Base-T Ethernet port for VxWorks development

- □ Integrated PCI 2.2 compatible core

- □ Four integrated multi-protocol SpaceWire nodes that support the RMAP protocol

- □ Two CAN 2.0 compliant bus interfaces

- Multifunctional memory controller

- $\Box$  -55°C to +105°C temperature range

- Operational environment:

- Intrinsic total-dose: 100 krad(Si)

- SEL Immune  $\leq 110 \text{ MeV-cm}^2/\text{mg}$

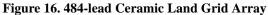

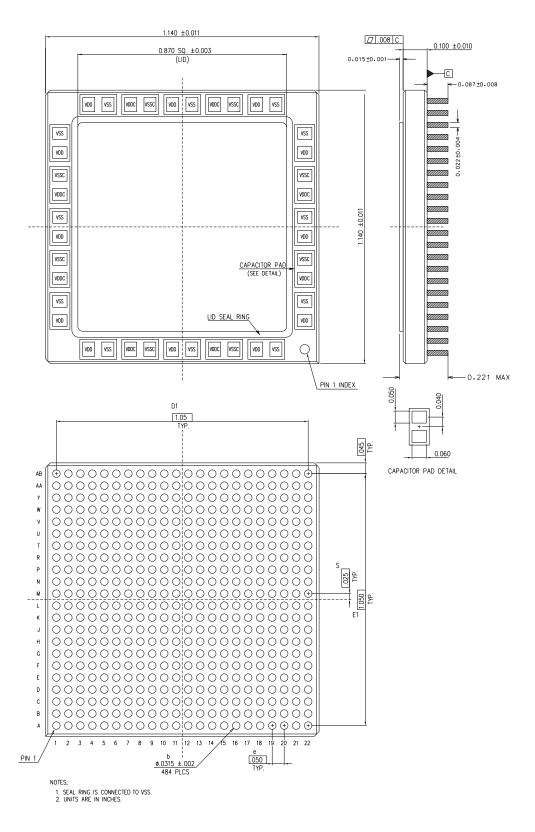

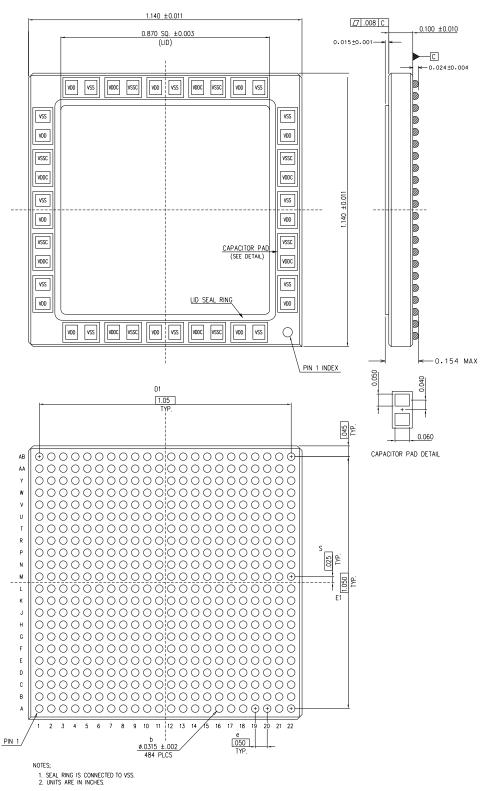

- □ Packaging options:

- 484-pin Ceramic Land Grid, Column Grid and Ball Grid Array packages

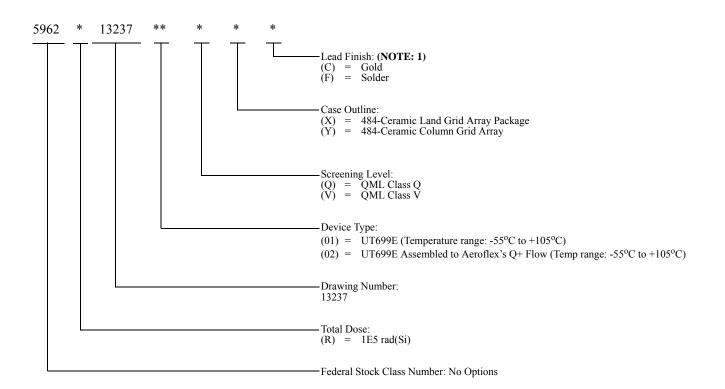

- □ Standard Microcircuit Drawing 5962-13237

- QML Q, Q+, and V (Pending)

- Applications

- Nuclear power plant controls

- Critical transportation systems

- High-altitude avionics

- Medical electronics

- X-Ray cargo scanning

- Spaceborne computer

- System controller boards

- Avionics processing boards

#### INTRODUCTION

The UT699E is an enhanced version of the UT699 featuring a seven stage pipelined monolithic, high-performance, fault-tolerant SPARC<sup>TM</sup> V8/LEON 3FT Processor. L1 cache has been increased to 16kB for both instruction and data caches. Performance is increased to 1.2 DMIPS / MHz. RMAP protocol is supported for all four SpaceWire ports. Other enhancements include cache snooping. The UT699E provides a 32-bit master/target PCI interface, including a 16 bit user I/O interface for off-chip peripherals. A compliant 2.0 AMBA bus interface integrates the on-chip LEON 3FT, SpaceWire, Ethernet, memory controller, cPCI, CAN bus, and programmable interrupt peripherals.

A passion for performance

The UT699E is SPARC V8 compliant; therefore, developers may use industry standard compilers, kernels, and development tools. A full software development suite is available including a C/C++ cross-compiler system based on GCC and the Newlib embedded C-library. Software developed for the UT699 will be 100% compatible with the UT699E.

BCC includes a small run-time kernel with interrupt support and Pthreads library. For multi-threaded applications, a SPARC<sup>TM</sup> compliant port of the eCos real-time kernel, RTEMS 4.10, and VxWorks 6.x is supported.

# **1.0 Introduction**

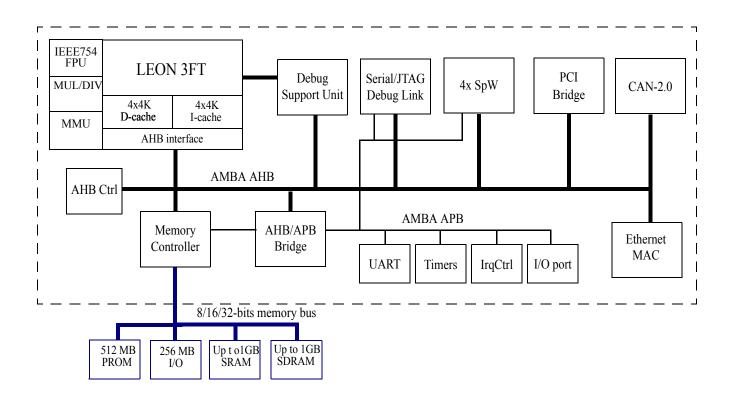

The UT699E LEON 3FT processor is based upon the industry-standard SPARC V8 architecture. The system-on-chip incorporates the SPARC V8 core and the peripheral blocks indicated below. The core and peripherals communicate internally via the AMBA (Advanced Microcontroller Bus Architecture) interconnect. This bus is comprised of the AHB (Advanced High-speed Bus) which is used for high-speed data transfer, and the APB (Advanced Peripheral Bus) which is used for low-speed data transfer.

Figure 1. UT699E Functional Block Diagram

The LEON 3FT architecture includes the following peripheral blocks:

- LEON3 SPARC V8 integer unit with 16kB instruction cache and 16kB of data cache

- IEEE-754 floating point unit

- Debug support unit

- UART, JTAG, SpaceWire, and PCI debug links

- 8/16/32-bit memory controller with EDAC for external PROM and SRAM

- 32-bit SDRAM controller with EDAC for external SDRAM

- Timer unit with three 32-bit timers and watchdog

- Interrupt controller for 15 interrupts in two priority levels

- 16-bit general purpose I/O port (GPIO) which can be used as external interrupt sources

- Up to four SpaceWire links with RMAP on all channels

- Up to two CAN controllers

- Ethernet with support for MII

- cPCI interface with 8-channel arbiter

# 2.0 Pin Identification and Description

| Pin Function | Description        |

|--------------|--------------------|

| Ι            | CMOS input         |

| IS           | CMOS input Schmitt |

| 0            | CMOS output        |

| I/O          | CMOS bi-direct     |

| OD           | CMOS open drain    |

| PCI-I        | PCI input          |

| PCI-O        | PCI output         |

| PCI-I/O      | PCI bi-direct      |

| PCI-3        | PCI three-state    |

|              |                    |

## 2.1. System Signals

| Pin Name           | Function | Pin<br>Number | Reset<br>Value | Description                                                   |

|--------------------|----------|---------------|----------------|---------------------------------------------------------------|

|                    |          | 484 CLGA      |                |                                                               |

| SYSCLK             | Ι        | Y20           |                | Main system clock                                             |

| RESET              | IS       | L19           |                | System reset                                                  |

| ERROR <sup>1</sup> | OD       | K19           |                | Processor error mode indicator. This is an active low output. |

| WDOG <sup>1</sup>  | OD       | J19           |                | Watchdog indicator. This is an active low output.             |

#### Notes:

1. This pin is actively driven low and must be tied to  $V_{\mbox{\scriptsize DD}}$  through a pull-up resistor.

#### 2.2 Address Bus

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description              |

|----------|-----------|---------------|----------------|--------------------------|

|          |           | 484 CLGA      | Value          |                          |

| ADDR[0]  | 0         | W5            | low            | Bit 0 of the address bus |

| ADDR[1]  | 0         | Y5            | low            | Bit 1 of the address bus |

| ADDR[2]  | 0         | W6            | low            | Bit 2 of the address bus |

| ADDR[3]  | 0         | AA5           | low            | Bit 3 of the address bus |

| ADDR[4]  | 0         | Y6            | low            | Bit 4 of the address bus |

| ADDR[5]  | 0         | AB5           | low            | Bit 5 of the address bus |

| ADDR[6]  | 0         | W7            | low            | Bit 6 of the address bus |

| ADDR[7]  | 0         | AA6           | low            | Bit 7 of the address bus |

| ADDR[8]  | 0         | Y7            | low            | Bit 8 of the address bus |

| Pin Name | Pin Name Direction | Pin<br>Number | Reset<br>Value | Description               |

|----------|--------------------|---------------|----------------|---------------------------|

|          |                    | 484 CLGA      | value          |                           |

| ADDR[9]  | 0                  | AA7           | low            | Bit 9 of the address bus  |

| ADDR[10] | 0                  | AB6           | low            | Bit 10 of the address bus |

| ADDR[11] | 0                  | W8            | low            | Bit 11 of the address bus |

| ADDR[12] | 0                  | AB7           | low            | Bit 12 of the address bus |

| ADDR[13] | 0                  | Y8            | low            | Bit 13 of the address bus |

| ADDR[14] | 0                  | AA8           | low            | Bit 14 of the address bus |

| ADDR[15] | 0                  | W9            | low            | Bit 15 of the address bus |

| ADDR[16] | 0                  | AB8           | low            | Bit 16 of the address bus |

| ADDR[17] | 0                  | Y9            | low            | Bit 17 of the address bus |

| ADDR[18] | 0                  | W10           | low            | Bit 18 of the address bus |

| ADDR[19] | 0                  | AB9           | low            | Bit 19 of the address bus |

| ADDR[20] | 0                  | Y10           | low            | Bit 20 of the address bus |

| ADDR[21] | 0                  | AA9           | low            | Bit 21 of the address bus |

| ADDR[22] | 0                  | W11           | low            | Bit 22 of the address bus |

| ADDR[23] | 0                  | AA10          | low            | Bit 23 of the address bus |

| ADDR[24] | 0                  | Y11           | low            | Bit 24 of the address bus |

| ADDR[25] | 0                  | AB10          | low            | Bit 25 of the address bus |

| ADDR[26] | 0                  | AB11          | low            | Bit 26 of the address bus |

| ADDR[27] | 0                  | AA11          | low            | Bit 27 of the address bus |

# 2.3 Data Bus

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description           |

|----------|-----------|---------------|----------------|-----------------------|

|          |           | 484 CLGA      | Value          |                       |

| DATA[0]  | I/O       | W12           | high-z         | Bit 0 of the data bus |

| DATA[1]  | I/O       | W13           | high-z         | Bit 1 of the data bus |

| DATA[2]  | I/O       | Y12           | high-z         | Bit 2 of the data bus |

| DATA[3]  | I/O       | AA13          | high-z         | Bit 3 of the data bus |

| DATA[4]  | I/O       | AA12          | high-z         | Bit 4 of the data bus |

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description            |

|----------|-----------|---------------|----------------|------------------------|

|          |           | 484 CLGA      |                |                        |

| DATA[5]  | I/O       | AB13          | high-z         | Bit 5 of the data bus  |

| DATA[6]  | I/O       | W14           | high-z         | Bit 6 of the data bus  |

| DATA[7]  | I/O       | AA14          | high-z         | Bit 7 of the data bus  |

| DATA[8]  | I/O       | Y13           | high-z         | Bit 8 of the data bus  |

| DATA[9]  | I/O       | W15           | high-z         | Bit 9 of the data bus  |

| DATA[10] | I/O       | AB15          | high-z         | Bit 10 of the data bus |

| DATA[11] | I/O       | Y14           | high-z         | Bit 11 of the data bus |

| DATA[12] | I/O       | AB14          | high-z         | Bit 12 of the data bus |

| DATA[13] | I/O       | W16           | high-z         | Bit 13 of the data bus |

| DATA[14] | I/O       | AA18          | high-z         | Bit 14 of the data bus |

| DATA[15] | I/O       | Y15           | high-z         | Bit 15 of the data bus |

| DATA[16] | I/O       | AB16          | high-z         | Bit 16 of the data bus |

| DATA[17] | I/O       | AA15          | high-z         | Bit 17 of the data bus |

| DATA[18] | I/O       | AB17          | high-z         | Bit 18 of the data bus |

| DATA[19] | I/O       | AA16          | high-z         | Bit 19 of the data bus |

| DATA[20] | I/O       | AA19          | high-z         | Bit 20 of the data bus |

| DATA[21] | I/O       | W17           | high-z         | Bit 21 of the data bus |

| DATA[22] | I/O       | AB18          | high-z         | Bit 22 of the data bus |

| DATA[23] | I/O       | Y16           | high-z         | Bit 23 of the data bus |

| DATA[24] | I/O       | Y17           | high-z         | Bit 24 of the data bus |

| DATA[25] | I/O       | AA17          | high-z         | Bit 25 of the data bus |

| DATA[26] | I/O       | W18           | high-z         | Bit 26 of the data bus |

| DATA[27] | I/O       | AB19          | high-z         | Bit 27 of the data bus |

| DATA[28] | I/O       | Y19           | high-z         | Bit 28 of the data bus |

| DATA[29] | I/O       | AB20          | high-z         | Bit 29 of the data bus |

| DATA[30] | I/O       | Y18           | high-z         | Bit 30 of the data bus |

| DATA[31] | I/O       | AA20          | high-z         | Bit 31 of the data bus |

### 2.4 Check Bits

| Pin Name | Direction | Pin<br>Number Reset<br>Value | Description |                         |

|----------|-----------|------------------------------|-------------|-------------------------|

|          |           | 484 CLGA                     |             |                         |

| CB[0]    | I/O       | V19                          | high-z      | Bit 0 of EDAC checkbits |

| CB[1]    | I/O       | AA21                         | high-z      | Bit 1 of EDAC checkbits |

| CB[2]    | I/O       | Y21                          | high-z      | Bit 2 of EDAC checkbits |

| CB[3]    | I/O       | W19                          | high-z      | Bit 3 of EDAC checkbits |

| CB[4]    | I/O       | Y22                          | high-z      | Bit 4 of EDAC checkbits |

| CB[5]    | I/O       | W20                          | high-z      | Bit 5 of EDAC checkbits |

| CB[6]    | I/O       | W22                          | high-z      | Bit 6 of EDAC checkbits |

| CB[7]    | I/O       | W21                          | high-z      | Bit 7 of EDAC checkbits |

# 2.5 Memory Control Signals

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description                      |

|----------|-----------|---------------|----------------|----------------------------------|

|          |           | 484 CLGA      | Value          |                                  |

| WRITE    | 0         | V21           | high           | PROM and I/O write enable strobe |

| ŌĒ       | 0         | U19           | high           | PROM and I/O output enable       |

| ĪOS      | 0         | T20           | high           | I/O area chip select             |

| ROMS[0]  | 0         | V22           | high           | PROM chip select                 |

| ROMS[1]  | 0         | U20           | high           | PROM chip select                 |

| RWE[0]   | 0         | U22           | high           | SRAM write enable strobe         |

| RWE[1]   | 0         | T19           | high           | SRAM write enable strobe         |

| RWE[2]   | 0         | T22           | high           | SRAM write enable strobe         |

| RWE[3]   | 0         | T21           | high           | SRAM write enable strobe         |

| RAMOE[0] | 0         | V20           | high           | SRAM output enable               |

| RAMOE[1] | 0         | R21           | high           | SRAM output enable               |

| RAMOE[2] | 0         | R20           | high           | SRAM output enable               |

| RAMOE[3] | 0         | R22           | high           | SRAM output enable               |

| RAMOE[4] | 0         | R19           | high           | SRAM output enable               |

| RAMS[0]  | 0         | P22           | high           | SRAM chip select                 |

| Pin Name | Pin Name Direction | Pin<br>Number | Reset<br>Value | Description                        |

|----------|--------------------|---------------|----------------|------------------------------------|

|          |                    | 484 CLGA      | Value          |                                    |

| RAMS[1]  | 0                  | P20           | high           | SRAM chip select                   |

| RAMS[2]  | 0                  | P21           | high           | SRAM chip select                   |

| RAMS[3]  | 0                  | P19           | high           | SRAM chip select                   |

| RAMS[4]  | 0                  | N19           | high           | SRAM chip select                   |

| READ     | 0                  | K20           | high           | SRAM, PROM, and I/O read indicator |

| BEXC     | Ι                  | K22           |                | Bus exception                      |

| BRDY     | Ι                  | K21           |                | Bus ready                          |

#### 2.6 SDRAM

| Pin Name | Pin Name Direction | Pin<br>Number | Reset<br>Value | Description                 |

|----------|--------------------|---------------|----------------|-----------------------------|

|          |                    | 484 CLGA      | Value          |                             |

| SDCLK    | 0                  | AB12          | high           | SDRAM clock                 |

| SDRAS    | 0                  | N22           | high           | SDRAM row address strobe    |

| SDCAS    | 0                  | N20           | high           | SDRAM column address strobe |

| SDWE     | 0                  | N21           | high           | SDRAM write enable          |

| SDCS[0]  | 0                  | M21           | high           | SDRAM chip select           |

| SDCS[1]  | 0                  | M22           | high           | SDRAM chip select           |

| SDDQM[0] | 0                  | L21           | high           | SDRAM data mask             |

| SDDQM[1] | 0                  | M20           | high           | SDRAM data mask             |

| SDDQM[2] | 0                  | L20           | high           | SDRAM data mask             |

| SDDQM[3] | 0                  | L22           | high           | SDRAM data mask             |

## 2.7 CAN 2.0 Interface

| Pin Name   | Direction | Pin<br>Number | Reset<br>Value | Description       |

|------------|-----------|---------------|----------------|-------------------|

|            |           | 484 CLGA      | vulue          |                   |

| CAN_RXD[0] | Ι         | J20           |                | CAN receive data  |

| CAN_TXD[0] | 0         | J22           | high           | CAN transmit data |

| Pin Name   | Direction | Pin<br>Number | Reset<br>Value | Description       |

|------------|-----------|---------------|----------------|-------------------|

|            |           | 484 CLGA      | vulue          |                   |

| CAN_RXD[1] | Ι         | J21           |                | CAN receive data  |

| CAN_TXD[1] | 0         | H22           | high           | CAN transmit data |

## 2.8 Debug Support Unit (DSU)

| Pin Name | Direction |          | nber Reset<br>Value | Description            |

|----------|-----------|----------|---------------------|------------------------|

|          |           | 484 CLGA |                     |                        |

| DSUACT   | 0         | H19      | low                 | DSUmode indicator      |

| DSUBRE   | Ι         | H20      |                     | DSU break              |

| DSUEN    | Ι         | G19      |                     | DSU enable             |

| DSURX    | Ι         | G20      |                     | DSU UART receive data  |

| DSUTX    | 0         | G21      | high                | DSU UART transmit data |

## 2.9 JTAG Interface

| Pin Name | Direction | Pin<br>Number<br>484 CLGA | Reset<br>Value | Description           |

|----------|-----------|---------------------------|----------------|-----------------------|

| TRST     | Ι         | F20                       |                | JTAG reset            |

| TMS      | Ι         | F21                       |                | JTAG test mode select |

| ТСК      | Ι         | G22                       |                | JTAG clock            |

| TDI      | Ι         | F22                       |                | JTAG test data input  |

| TDO      | 0         | F19                       |                | JTAG test data output |

#### 2.10 Ethernet Interface

| Pin Name | Direction | Pin<br>Number<br>484 CLGA | Reset<br>Value | Description                    |

|----------|-----------|---------------------------|----------------|--------------------------------|

| EMDC     | 0         | E22                       | low            | Ethernet media interface clock |

| ERX_CLK  | Ι         | D22                       |                | Ethernet RX clock              |

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description                                 |

|----------|-----------|---------------|----------------|---------------------------------------------|

|          |           | 484 CLGA      | Value          |                                             |

| EMDIO    | I/O       | D20           | high-z         | Ethernet media interface data               |

| ERX_COL  | Ι         | E21           |                | Ethernet collision error                    |

| ERX_CRS  | Ι         | E20           |                | Ethernet carrier sense detect               |

| ERX_DV   | Ι         | D21           |                | Ethernet receiver data valid                |

| ERX_ER   | Ι         | C21           |                | Ethernet reception error                    |

| ERXD[0]  | Ι         | C22           |                | Ethernet receive data                       |

| ERXD[1]  | Ι         | B21           |                | Ethernet receive data                       |

| ERXD[2]  | Ι         | C20           |                | Ethernet receive data                       |

| ERXD[3]  | Ι         | B20           |                | Ethernet receive data                       |

| ETXD[0]  | 0         | C19           | low            | Ethernet transmit data                      |

| ETXD[1]  | 0         | C18           | high           | Ethernet transmit data                      |

| ETXD[2]  | 0         | B18           | low            | Ethernet transmit data                      |

| ETXD[3]  | 0         | B19           | high           | Ethernet transmit data                      |

| ETX_CLK  | Ι         | A19           |                | Ethernet TX clock                           |

| ETX_EN   | 0         | A18           | low            | Ethernet transmit enable                    |

| ETX_ER   | 0         | A20           | low            | Ethernet transmit error. Always driven low. |

# 2.11 General Purpose I/O

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description                  |

|----------|-----------|---------------|----------------|------------------------------|

|          |           | 484 CLGA      | value          |                              |

| GPIO[0]  | I/O       | B17           | high-z         | Bit 0 of general purpose I/O |

| GPIO[1]  | I/O       | C17           | high-z         | Bit 1 of general purpose I/O |

| GPIO[2]  | I/O       | A17           | high-z         | Bit 2 of general purpose I/O |

| GPIO[3]  | I/O       | D17           | high-z         | Bit 3 of general purpose I/O |

| GPIO[4]  | I/O       | C16           | high-z         | Bit 4 of general purpose I/O |

| GPIO[5]  | I/O       | D16           | high-z         | Bit 5 of general purpose I/O |

| GPIO[6]  | I/O       | C15           | high-z         | Bit 6 of general purpose I/O |

| GPIO[7]  | I/O       | D15           | high-z         | Bit 7 of general purpose I/O |

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description                   |

|----------|-----------|---------------|----------------|-------------------------------|

|          |           | 484 CLGA      | value          |                               |

| GPIO[8]  | I/O       | C7            | high-z         | Bit 8 of general purpose I/O  |

| GPIO[9]  | I/O       | B5            | high-z         | Bit 9 of general purpose I/O  |

| GPIO[10] | I/O       | D7            | high-z         | Bit 10 of general purpose I/O |

| GPIO[11] | I/O       | A5            | high-z         | Bit 11 of general purpose I/O |

| GPIO[12] | I/O       | D6            | high-z         | Bit 12 of general purpose I/O |

| GPIO[13] | I/O       | C5            | high-z         | Bit 13 of general purpose I/O |

| GPIO[14] | I/O       | C6            | high-z         | Bit 14 of general purpose I/O |

| GPIO[15] | I/O       | D5            | high-z         | Bit 15 of general purpose I/O |

# 2.12 SpaceWire Interface

| Pin Name   | Direction | Pin<br>Number Reset<br>Value | Description |                           |

|------------|-----------|------------------------------|-------------|---------------------------|

|            |           | 484 CLGA                     | value       |                           |

| SPW_CLK    | Ι         | A11                          |             | SpaceWire clock           |

| SPW_RXS[0] | Ι         | A16                          |             | SpaceWire receive strobe  |

| SPW_RXD[0] | Ι         | A15                          |             | SpaceWire receive data    |

| SPW_TXS[0] | 0         | B16                          | low         | SpaceWire transmit strobe |

| SPW_TXD[0] | 0         | B15                          | low         | SpaceWire transmit data   |

| SPW_RXS[1] | Ι         | A14                          |             | SpaceWire receive strobe  |

| SPW_RXD[1] | Ι         | A13                          |             | SpaceWire receive data    |

| SPW_TXS[1] | 0         | B14                          | low         | SpaceWire transmit strobe |

| SPW_TXD[1] | 0         | B13                          | low         | SpaceWire transmit data   |

| SPW_RXS[2] | Ι         | A9                           |             | SpaceWire receive strobe  |

| SPW_RXD[2] | Ι         | A8                           |             | SpaceWire receive data    |

| SPW_TXS[2] | 0         | В9                           | low         | SpaceWire transmit strobe |

| SPW_TXD[2] | 0         | B8                           | low         | SpaceWire transmit data   |

| SPW_RXS[3] | Ι         | A7                           |             | SpaceWire receive strobe  |

| SPW_RXD[3] | Ι         | A6                           |             | SpaceWire receive data    |

| SPW_TXS[3] | 0         | B7                           | low         | SpaceWire transmit strobe |

| Pin Name   | Direction | Pin<br>Number | Reset<br>Value | Description             |

|------------|-----------|---------------|----------------|-------------------------|

|            |           | 484 CLGA      |                |                         |

| SPW_TXD[3] | 0         | B6            | low            | SpaceWire transmit data |

# 2.13 UART Interface

| Pin Name | Direction | Pin<br>Number | Reset<br>Value | Description        |

|----------|-----------|---------------|----------------|--------------------|

|          |           | 484 CLGA      |                |                    |

| RXD      | Ι         | C12           |                | UART receive data  |

| TXD      | 0         | C11           | high           | UART transmit data |

#### 2.14 PCI Address and Data Bus

| Pin Name   | Direction | Pin<br>Number | Reset<br>Value | Description                        |

|------------|-----------|---------------|----------------|------------------------------------|

|            |           | 484 CLGA      | Value          |                                    |

| PCI_AD[0]  | PCI-I/O   | AA2           | high-z         | Bit 0 of PCI address and data bus  |

| PCI_AD[1]  | PCI-I/O   | AA3           | high-z         | Bit 1 of PCI address and data bus  |

| PCI_AD[2]  | PCI-I/O   | Y1            | high-z         | Bit 2 of PCI address and data bus  |

| PCI_AD[3]  | PCI-I/O   | Y2            | high-z         | Bit 3 of PCI address and data bus  |

| PCI_AD[4]  | PCI-I/O   | Y3            | high-z         | Bit 4 of PCI address and data bus  |

| PCI_AD[5]  | PCI-I/O   | W1            | high-z         | Bit 5 of PCI address and data bus  |

| PCI_AD[6]  | PCI-I/O   | W2            | high-z         | Bit 6 of PCI address and data bus  |

| PCI_AD[7]  | PCI-I/O   | W3            | high-z         | Bit 7 of PCI address and data bus  |

| PCI_AD[8]  | PCI-I/O   | V2            | high-z         | Bit 8 of PCI address and data bus  |

| PCI_AD[9]  | PCI-I/O   | V3            | high-z         | Bit 9 of PCI address and data bus  |

| PCI_AD[10] | PCI-I/O   | U1            | high-z         | Bit 10 of PCI address and data bus |

| PCI_AD[11] | PCI-I/O   | U2            | high-z         | Bit 11 of PCI address and data bus |

| PCI_AD[12] | PCI-I/O   | U3            | high-z         | Bit 12 of PCI address and data bus |

| PCI_AD[13] | PCI-I/O   | T1            | high-z         | Bit 13 of PCI address and data bus |

| PCI_AD[14] | PCI-I/O   | R2            | high-z         | Bit 14 of PCI address and data bus |

| PCI_AD[15] | PCI-I/O   | R1            | high-z         | Bit 15 of PCI address and data bus |

| Pin Name   | Direction | Pin<br>Number | Reset<br>Value | Description                        |

|------------|-----------|---------------|----------------|------------------------------------|

|            |           | 484 CLGA      | Value          |                                    |

| PCI_AD[16] | PCI-I/O   | J1            | high-z         | Bit 16 of PCI address and data bus |

| PCI_AD[17] | PCI-I/O   | K2            | high-z         | Bit 17 of PCI address and data bus |

| PCI_AD[18] | PCI-I/O   | K1            | high-z         | Bit 18 of PCI address and data bus |

| PCI_AD[19] | PCI-I/O   | G1            | high-z         | Bit 19 of PCI address and data bus |

| PCI_AD[20] | PCI-I/O   | Н3            | high-z         | Bit 20 of PCI address and data bus |

| PCI_AD[21] | PCI-I/O   | H2            | high-z         | Bit 21 of PCI address and data bus |

| PCI_AD[22] | PCI-I/O   | F1            | high-z         | Bit 22 of PCI address and data bus |

| PCI_AD[23] | PCI-I/O   | F2            | high-z         | Bit 23 of PCI address and data bus |

| PCI_AD[24] | PCI-I/O   | E1            | high-z         | Bit 24 of PCI address and data bus |

| PCI_AD[25] | PCI-I/O   | E2            | high-z         | Bit 25 of PCI address and data bus |

| PCI_AD[26] | PCI-I/O   | F3            | high-z         | Bit 26 of PCI address and data bus |

| PCI_AD[27] | PCI-I/O   | D1            | high-z         | Bit 27 of PCI address and data bus |

| PCI_AD[28] | PCI-I/O   | D2            | high-z         | Bit 28 of PCI address and data bus |

| PCI_AD[29] | PCI-I/O   | E3            | high-z         | Bit 29 of PCI address and data bus |

| PCI_AD[30] | PCI-I/O   | D3            | high-z         | Bit 30 of PCI address and data bus |

| PCI_AD[31] | PCI-I/O   | C1            | high-z         | Bit 31 of PCI address and data bus |

## 2.15 PCI Control Signals

| Pin Name               | Direction | Pin<br>Number<br>484 CLGA | Reset<br>Value | Description                     |

|------------------------|-----------|---------------------------|----------------|---------------------------------|

|                        |           | 404 CLGA                  |                |                                 |

| PCI_RST                | PCI-I     | C3                        |                | PCI reset input                 |

| PCI_CLK                | PCI-I     | C2                        |                | PCI clock input                 |

| PCI_C/BE[0]            | PCI-I/O   | V1                        | high-z         | PCI bus command and byte enable |

| PCI_C/BE[1]            | PCI-I/O   | P2                        | high-z         | PCI bus command and byte enable |

| PCI_C/BE[2]            | PCI-I/O   | H1                        | high-z         | PCI bus command and byte enable |

| PCI_C/BE[3]            | PCI-I/O   | G2                        | high-z         | PCI bus command and byte enable |

| PCI_PAR                | PCI-I/O   | P1                        | high-z         | PCI parity checkbit             |

| PCI_FRAME <sup>1</sup> | PCI-3     | L1                        | high-z         | PCI cycle frame indicator       |

| Pin Name                | Direction | Pin<br>Number | Reset<br>Value | Description                                                   |

|-------------------------|-----------|---------------|----------------|---------------------------------------------------------------|

|                         |           | 484 CLGA      |                |                                                               |

| PCI_IRDY <sup>1</sup>   | PCI-3     | L2            | high-z         | PCI initiator ready indicator                                 |

| PCI_TRDY <sup>1</sup>   | PCI-3     | M1            | high-z         | PCI target ready indicator                                    |

| PCI_STOP <sup>1</sup>   | PCI-3     | N1            | high-z         | PCI target stop request                                       |

| PCI_DEVSEL <sup>1</sup> | PCI-3     | M2            | high-z         | PCI device select                                             |

| PCI_PERR <sup>1</sup>   | PCI-3     | N2            | high-z         | PCI parity error indicator                                    |

| PCI_IDSEL               | PCI-I     | G3            |                | PCI initialization device select                              |

| PCI_REQ                 | PCI-O     | A4            | high-z         | PCI request to arbiter in point to point configuration        |

| PCI_GNT                 | PCI-I     | B2            |                | PCI bus access indicator in point to point configura-<br>tion |

| PCI_HOST                | PCI-I     | AB3           |                | PCI host enable input (Connect to SYSEN in PCI bus)           |

#### Notes:

1. This pin must be tied to  $V_{DD}$  through a pull-up resistor as specified in the PCI Local Bus Specification Revision 2.1 Section 4.3.3.

#### 2.16 PCI Arbiter

| Pin Name       | Direction | Pin<br>Number | Reset<br>Value | Description             |

|----------------|-----------|---------------|----------------|-------------------------|

|                |           | 484 CLGA      | value          |                         |

| PCI_ARB_REQ[0] | PCI-I     | B4            |                | PCI arbiter bus request |

| PCI_ARB_REQ[1] | PCI-I     | AB4           |                | PCI arbiter bus request |

| PCI_ARB_REQ[2] | PCI-I     | Y4            |                | PCI arbiter bus request |

| PCI_ARB_REQ[3] | PCI-I     | Т3            |                | PCI arbiter bus request |

| PCI_ARB_REQ[4] | PCI-I     | Р3            |                | PCI arbiter bus request |

| PCI_ARB_REQ[5] | PCI-I     | M3            |                | PCI arbiter bus request |

| PCI_ARB_REQ[6] | PCI-I     | К3            |                | PCI arbiter bus request |

| PCI_ARB_REQ[7] | PCI-I     | C4            |                | PCI arbiter bus request |

| PCI_ARB_GNT[0] | PCI-O     | В3            | high-z         | PCI arbiter bus grant   |

| PCI_ARB_GNT[1] | PCI-O     | AA4           | high-z         | PCI arbiter bus grant   |

| PCI_ARB_GNT[2] | PCI-O     | W4            | high-z         | PCI arbiter bus grant   |

| PCI_ARB_GNT[3] | PCI-O     | R3            | high-z         | PCI arbiter bus grant   |

| Pin Name       | Direction | Pin<br>Number | Reset<br>Value | Description           |  |

|----------------|-----------|---------------|----------------|-----------------------|--|

|                |           | 484 CLGA      |                |                       |  |

| PCI_ARB_GNT[4] | PCI-O     | N3            | high-z         | PCI arbiter bus grant |  |

| PCI_ARB_GNT[5] | PCI-O     | L3            | high-z         | PCI arbiter bus grant |  |

| PCI_ARB_GNT[6] | PCI-O     | J3            | high-z         | PCI arbiter bus grant |  |

| PCI_ARB_GNT[7] | PCI-O     | A3            | high-z         | PCI arbiter bus grant |  |

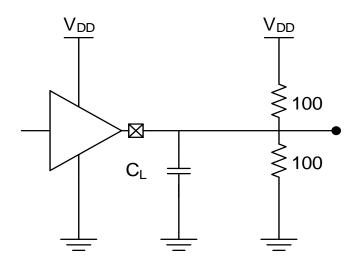

## 2.17 Power and Ground Pins

| Pin Name         | Pin Number                                                                                                                                                                                                                                                                                                                       | Description                                           |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| r in Name        | 484 CLGA                                                                                                                                                                                                                                                                                                                         | Description                                           |

| V <sub>DD</sub>  | B1, B10, B12, B22, E7, E9, E14, E16, F6, F10, F13, F17, G5, G9, G14, H6, H8, H10, H13, H15, J7, J16, J18, K5, K8, K15, K17, L6, M6, N5, N8, N15, N17, P7, P16, P18, R6, R8, R10, R13, R15, T5, T9, T14, U6, U9, U11, U12, U14, U17, V10, V13, AA1, AA22                                                                          | I/O supply voltage                                    |

| V <sub>SS</sub>  | A1, A12, A22, B11, C8, C10, C13, D4, D9, D14, D18, E4, E6, E10, E13, E17, E19, F4, G4, G8, G11, G12, G15, G17, H4, H7, H16, H18, J2, J4, J9, J14, K4, K10, K13, L7, L11, L12, L17, M7, M11, M12, M17, N4, N10, N13, P4, P9, P14, R4, R7, R16, R18, T2, T4, T8, T15, T17, U4, U10, U13, V4, V5, V8, V11, V12, V15, V18, AB1, AB22 | I/O supply ground                                     |

| V <sub>DDC</sub> | A2, A21, D10, D13, E5, E11, E12, E18, F8, F15, G7, G10, G13, G16, G18, H5, H9, H11, H12, H14, H17, J6, J8, J15, K7, K16, L4, L8, L15, L18, M4, M8, M15, M18, N7, N16, P6, P8, P15, R5, R9, R11, R12, R14, R17, T7, T10, T13, T16, T18, U8, U15, V6, V17, AB2, AB21                                                               | Core supply voltage                                   |

| V <sub>SSC</sub> | A10, C9, C14, D11, D12, E8, E15, F5, F7, F9, F11, F12, F14, F16, F18, G6, H21, J5, J10, J11, J12, J13, J17, K6, K9, K11, K12, K14, K18, L5, L9, L10, L13, L14, L16, M5, M9, M10, M13, M14, M16, M19, N6, N9, N11, N12, N14, N18, P5, P10, P11, P12, P13, P17, T6, T11, T12, U5, U7, U16, U18, U21, V7, V9, V14, V16              | Core supply ground                                    |

| Unused           | D8                                                                                                                                                                                                                                                                                                                               | This pin may be left floating or tied to $\rm V_{SS}$ |

| Unused           | D19                                                                                                                                                                                                                                                                                                                              | This pin must be tied to $V_{SS}$                     |

### 2.20 Bootstrap Signals

The states of the following signals are latched in upon the rising edge of reset in order to configure the UT699E for the indicated operation.

| Pin Name    | Function                                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------|

| GPIO[1:0]   | Sets the data width of the PROM area<br>00: 8 bits<br>01: 16 bits<br>10: 32 bits<br>11: Not used                          |

| GPIO[2]     | Enable EDAC checking of the PROM area<br>0: EDAC disabled<br>1: EDAC enabled                                              |

| GPIO[7:4]   | Set the SpW clock divisor link bits in the SpW Clock Divisor Register                                                     |

| GPIO[15:12] | Sets the least significant address nibble of the IP and MAC address for the Ethernet Debug Commu-<br>nication Link (EDCL) |

# **3.0 AC and DC Electrical Specifications**

# 3.1 Absolute Maximum Ratings<sup>1</sup>

| Symbol                      | Description                                                   |                    | Min                   | Max                   | Units |

|-----------------------------|---------------------------------------------------------------|--------------------|-----------------------|-----------------------|-------|

| V <sub>DDC</sub>            | Core supply voltage                                           |                    | -0.3                  | 1.85                  | V     |

| V <sub>DD</sub>             | I/O supply voltage                                            |                    | -0.3                  | 5.2                   | V     |

| V <sub>IN</sub>             | Input voltage any pin                                         |                    | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V     |

| P <sub>D</sub> <sup>2</sup> | Maximum power dissipation permitted @<br>$T_C = 105^{\circ}C$ |                    |                       | 4                     | W     |

| T <sub>J</sub>              | Junction temperature                                          |                    |                       | 150                   | °C    |

| $\Theta_{\rm JC}$           | Thermal resistance, junction to case                          | 484 CLGA/CCGA/CBGA |                       | 5                     | °C/W  |

| T <sub>STG</sub>            | Storage temperature                                           |                    | -65                   | 150                   | °C    |

| ESD <sub>HBM</sub>          | ESD protection (human body model) Class 2                     |                    | 2000                  |                       | V     |

#### Notes:

1. Stresses greater than those listed in the following table can result in permanent damage to the device. These parameters cannot be violated.

2. Per MIL-STD-883, Method 1012, Section 3.4.1, PD =  $(T_J(max)-T_c(max))/\Theta_{JC}$

#### **3.2 Recommended Operating Conditions**

| Symbol           | Description                                                                    | Min | Max             | Units |

|------------------|--------------------------------------------------------------------------------|-----|-----------------|-------|

| V <sub>DDC</sub> | Core supply voltage                                                            | 1.1 | 1.3             | V     |

| V <sub>DD</sub>  | I/O supply voltage                                                             | 3.0 | 3.6             | V     |

| V <sub>IN</sub>  | Input voltage any pin                                                          | 0   | V <sub>DD</sub> | V     |

| T <sub>C</sub>   | Case operating temperature                                                     | -55 | 105             | °C    |

| t <sub>R</sub>   | Rise time, all CMOS and PCI inputs $(0.1V_{DD} \text{ to } 0.9V_{DD})$         |     | 20              | ns    |

| t <sub>F</sub>   | Fall time, all CMOS and PCI inputs (0.9V <sub>DD</sub> to 0.1V <sub>DD</sub> ) |     | 20              | ns    |

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

#### **3.3 Operational Environmet**

The UT699E processor includes the following SEU mitigation features:

- \* Cache memory error-detection of up to 4 errors per tag or 32-bit word

- \* Autonomous and software transparent error handling

- \* No timing impact due to error detection or correction

| PARAMETER                                                                                                                                            | LIMIT        | UNITS                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|

| Total Ionizing Dose (TID) <sup>1</sup>                                                                                                               | 1E5          | rad (Si)                |

| Single Event Latchup Immune (SEL) <sup>2</sup>                                                                                                       | <u>≤</u> 110 | MeV-cm <sup>2</sup> /mg |

| Single Event Upset (SEU) <sup>3, 4</sup><br>Inherent register upset rate                                                                             | 5.2E-7       | errors/device-day       |

| Single Event Upset (SEU) <sup>3, 4</sup><br>Multiple-bit error (MBE) rate which over-<br>comes internal error detection & correction<br>architecture | 2.8E-11      | MBE/device-day          |

Notes:

1. TID irradation per MIL-STD-883, Test Method 1019, condition A. Post irradiation electrical testing performed at room temperature. 2. Worst case temperature and voltage of  $T_C = +105^{\circ}C$ ,  $V_{DD} = 3.6V$ ,  $V_{DDC} = 1.3V$ .

3. Contact factory for error rate information.

4. The error rate calculation was performed using SpaceRad 6.0 for a Geosynchronous orbit in the Adams 90% worst-case environment with 100mil Al shielding.

# 3.4 Power Supply Operating Characteristics (pre- and post-radiation) ( $V_{DD} = 3.3V \pm 0.3V$ ; $V_{DDC} = 1.2V \pm 0.1V$ ; $T_C = -55^{\circ}C$ to $105^{\circ}C$ )

| Symbol            | Description                                      | Conditions                                                  |                      |                                              | Max | Units |

|-------------------|--------------------------------------------------|-------------------------------------------------------------|----------------------|----------------------------------------------|-----|-------|

| I <sub>DDCS</sub> | Standby core power sup-<br>ply quiescent current | $V_{DDC} = 1.3V, V_{DD} = 3.6V$<br>All clock inputs at 0MHz |                      | $T_C = -55^{\circ}C$<br>and $25^{\circ}C$    | 8   |       |

|                   |                                                  |                                                             |                      | $T_{\rm C} = 105^{\rm o}{\rm C}$             | 100 | mA    |

|                   |                                                  |                                                             | Post Irradiation (R) | $T_C = 25^{\circ}C$                          | 50  |       |

| I <sub>DDS</sub>  | Standby I/O power sup-<br>ply quiescent current  | $V_{DDC} = 1.3V, V_{DD} = 3.6V$<br>All clock inputs at 0MHz |                      | $T_{\rm C} = -55^{\rm o}{\rm C}$<br>and 25°C | 0.7 | mA    |

|                   |                                                  |                                                             |                      | $T_{\rm C} = 105^{\rm o}{\rm C}$             | 2   |       |

# 3.5 DC Characteristics for LVCMOS3 Inputs (pre- and post-radiation) $(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C$ to $105^{\circ}C$ )

| Symbol                       | Description                                         | Conditions                                      | Min                | Max                | Units |

|------------------------------|-----------------------------------------------------|-------------------------------------------------|--------------------|--------------------|-------|

| V <sub>IH</sub> <sup>1</sup> | High-level input voltage                            |                                                 | 0.7V <sub>DD</sub> |                    | V     |

| V <sub>IL</sub> <sup>1</sup> | Low-level input voltage                             |                                                 |                    | 0.3V <sub>DD</sub> | V     |

| V <sub>T+</sub>              | Positive going threshold voltage for Schmitt inputs |                                                 |                    | 0.7V <sub>DD</sub> | V     |

| V <sub>T</sub> -             | Negative going threshold voltage for Schmitt inputs |                                                 | $0.3 V_{DD}$       |                    | V     |

| V <sub>H</sub>               | Hysteresis voltage for Schmitt inputs               |                                                 | 0.4                |                    | V     |

| I <sub>IN</sub>              | Input leakage current                               | $V_{IN} = V_{DD}$                               |                    | 1                  | μΑ    |

|                              |                                                     | $V_{IN} = V_{SS}$                               | -1                 |                    |       |

| C <sub>IN</sub> <sup>2</sup> | Input pin capacitance                               | $f = 1$ MHz; $V_{DD} = 0$ V,<br>$V_{DDC} = 0$ V |                    | 16                 | pF    |

Notes:

1. JTAG inputs are not tested.

2. Capacitance is measured for initial qualification and when design changes might affect the input/output capacitance.

#### 3.6 DC Characteristics for LVCMOS3 Outputs (pre- and post-radiation)

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol                        | Description                                                                                                                                                                                                                                                             | Conditions                                      | Min                   | Max  | Units |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------|------|-------|

| V <sub>OL1</sub> <sup>1</sup> | Low-level output voltage                                                                                                                                                                                                                                                | $I_{OL} = 100 \mu A$                            |                       | 0.25 | V     |

|                               | (All outputs except those listed below and in Section 3.8)                                                                                                                                                                                                              | $I_{OL} = 4mA$                                  |                       | 0.4  |       |

| $V_{OH1}^{1,2}$               | High-level output voltage                                                                                                                                                                                                                                               | $I_{OH} = -100 \mu A$                           | V <sub>DD</sub> -0.25 |      | V     |

|                               | (All outputs except those listed below and in Section 3.8)                                                                                                                                                                                                              | $I_{OH} = -4mA$                                 | 2.4                   |      |       |

| V <sub>OL2</sub>              | Low-level output voltage                                                                                                                                                                                                                                                | $I_{OL} = 100 \mu A$                            |                       | 0.25 | V     |

|                               | (GPIO[15:0], SPW_TXD[3:0],<br>SPW_TXS[3:0], TXD)                                                                                                                                                                                                                        | $I_{OL} = 12mA$                                 |                       | 0.4  |       |

| V <sub>OH2</sub>              | High-level output voltage<br>(GPIO[15:0], SPW TXD[3:0],                                                                                                                                                                                                                 | $I_{OH} = -100 \mu A$                           | V <sub>DD</sub> -0.25 |      | V     |

|                               | SPW_TXS[3:0], TXD)                                                                                                                                                                                                                                                      | $I_{OH} = -12mA$                                | 2.4                   |      |       |

| V <sub>OL3</sub>              | Low-level output voltage<br>(WRITE, OE, IOS, ROMS[1:0], RWE [3:0],                                                                                                                                                                                                      | $I_{OL} = 100 \mu A$                            |                       | 0.25 | V     |

|                               | $\frac{(WRITE, OE, IOS, ROMS[1:0], RWE[5:0],}{RAMOE [4:0], RAMS[4:0], SDCS[1:0],}$ $\overline{SDRAS}, \overline{SDCAS}, \overline{SDWE}, SDCLK, READ,$ $SDDQM[3:0], ADDR[27:0], DATA[31:0]$ and CB[7:0])                                                                | $I_{OL} = 24 \text{mA}$                         |                       | 0.4  |       |

| V <sub>OH3</sub>              | High-level output voltage                                                                                                                                                                                                                                               | $I_{OH} = -100 \mu A$                           | V <sub>DD</sub> -0.25 |      | V     |

|                               | $\frac{(WRITE, \overline{OE}, \overline{IOS}, \overline{ROMS[1:0]}, \overline{RWE [3:0]},}{RAMOE [4:0], \overline{RAMS[4:0]}, SDCS[1:0]},$<br>$\overline{SDRAS}, \overline{SDCAS}, \overline{SDWE}, SDCLK, READ,$<br>SDDQM[3:0], ADDR[27:0], DATA[31:0]<br>and CB[7:0]) | I <sub>OH</sub> = -24mA                         | 2.4                   |      |       |

| I <sub>OZ</sub>               | Three-state output current                                                                                                                                                                                                                                              | $V_{O} = V_{DD}$                                | -10                   | 10   | μΑ    |

|                               |                                                                                                                                                                                                                                                                         | $V_{O} = V_{SS}$                                | -10                   | 10   | 1     |

| I <sub>OS</sub> <sup>3</sup>  | Short-circuit output current                                                                                                                                                                                                                                            | $V_{\rm O} = V_{\rm DD}; V_{\rm DD} = 3.6 V$    |                       | 130  | mA    |

|                               | (All outputs except PCI outputs)                                                                                                                                                                                                                                        | $V_{\rm O} = V_{\rm SS}; V_{\rm DD} = 3.6 V$    | -65                   |      |       |

| C <sub>OUT</sub> <sup>4</sup> | Output pin capacitance                                                                                                                                                                                                                                                  | $f = 1$ MHz; $V_{DD} = 0$ V,<br>$V_{DDC} = 0$ V |                       | 16   | pF    |

Notes:

1. JTAG outputs are not tested.

2. Except open-drain output.

3. Guaranteed by design.

4. Capacitance is measured for initial qualification and when design changes might affect the input/output capacitance.

# 3.7 AC Electrical Characteristics for LVCMOS3 Inputs and Outputs (pre- and post-radiation)

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol                        | Description                                   | Conditions | Min | Max | Units |

|-------------------------------|-----------------------------------------------|------------|-----|-----|-------|

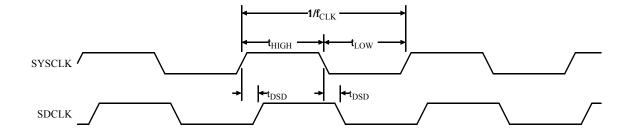

| f <sub>CLK</sub>              | System clock frequency                        |            |     | 100 | MHz   |

| t <sub>HIGH</sub>             | System clock high time                        |            | 4   |     | ns    |

| t <sub>LOW</sub>              | System clock low time                         |            | 4   |     | ns    |

| t <sub>DSD</sub> <sup>1</sup> | System clock to SDRAM clock propagation delay |            | 2.0 | 6.0 | ns    |

#### Notes:

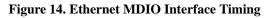

1. Reference Figure 15 for test load.

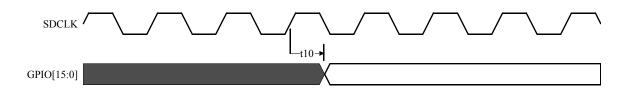

Figure 2. System Clock and SDCLK Timing Diagram

#### 3.8 DC Electrical Characteristics for PCI Inputs (pre- and post-radiation)

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol                       | Description              | Conditions                                      | Min                | Max                | Units |

|------------------------------|--------------------------|-------------------------------------------------|--------------------|--------------------|-------|

| V <sub>IH</sub>              | High-level input voltage |                                                 | 0.5V <sub>DD</sub> |                    | V     |

| V <sub>IL</sub>              | Low-level input voltage  |                                                 |                    | 0.3V <sub>DD</sub> | V     |

| I <sub>IN</sub>              | Input leakage current    | $V_{IN} = V_{DD}$                               |                    | 10                 | μΑ    |

|                              |                          | $V_{IN} = V_{SS}$                               | -10                |                    |       |

| C <sub>IN</sub> <sup>1</sup> | Input pin capacitance    | $f = 1$ MHz; $V_{DD} = 0$ V,<br>$V_{DDC} = 0$ V |                    | 22                 | pF    |

Notes:

1. Capacitance is measured for initial qualification and when design changes might affect the input/output capacitance.

#### 3.9 DC Electrical Characteristics for PCI Outputs (pre- and post-radiation)

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol                        | Description                                                                                                                                                     | Conditions                                      | Min                | Max                | Units |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------|--------------------|-------|

| V <sub>OH</sub>               | High-level output voltage<br>(PCI_AD[31:0], PCI_C/BE[3:0], PCI_RST,<br>PCI_IDSEL, PCI_FRAME, PCI_IRDY,<br>PCI_TRDY, PCI_DEVSEL, PCI_STOP,<br>PCI_PERR, PCI_PAR) | I <sub>OH</sub> = -500μA                        | 0.9V <sub>DD</sub> |                    | V     |

| V <sub>OL</sub>               | Low-level output voltage<br>(PCI_AD[31:0], PCI_C/BE[3:0], PCI_RST,<br>PCI_IDSEL, PCI_FRAME, PCI_IRDY,<br>PCI_TRDY, PCI_DEVSEL, PCI_STOP,<br>PCI_PERR, PCI_PAR)  | I <sub>OL</sub> = 1500μA                        |                    | 0.1V <sub>DD</sub> | V     |

| I <sub>OZ</sub>               | Three-state output current                                                                                                                                      | $V_{O} = V_{DD}$                                | -10                | 10                 | μΑ    |

|                               |                                                                                                                                                                 | $V_{O} = V_{SS}$                                | -10                | 10                 |       |

| I <sub>OS</sub> <sup>1</sup>  | Short-circuit output current                                                                                                                                    | $V_{\rm O} = V_{\rm DD}; V_{\rm DD} = 3.6 V$    |                    | 270                | mA    |

|                               |                                                                                                                                                                 | $V_{\rm O} = V_{\rm SS}; V_{\rm DD} = 3.6 V$    | -130               |                    |       |

| C <sub>OUT</sub> <sup>2</sup> | Output pin capacitance                                                                                                                                          | $f = 1$ MHz; $V_{DD} = 0$ V,<br>$V_{DDC} = 0$ V |                    | 22                 | pF    |

Notes:

1. Guaranteed by design.

2. Capacitance is measured for initial qualification and when design changes might affect the input/output capacitance.

# 3.10 AC Electrical Characteristics for PCI Inputs (pre- and post-radiation)

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

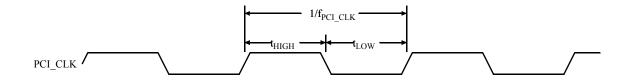

| Symbol               | Description         | Conditions | Min | Max | Units |

|----------------------|---------------------|------------|-----|-----|-------|

| f <sub>PCI_CLK</sub> | PCI clock frequency |            |     | 33  | MHz   |

| t <sub>HIGH</sub>    | PCI clock high time |            | 11  |     | ns    |

| t <sub>LOW</sub>     | PCI clock low time  |            | 11  |     | ns    |

# 4.0 Timing Specifications

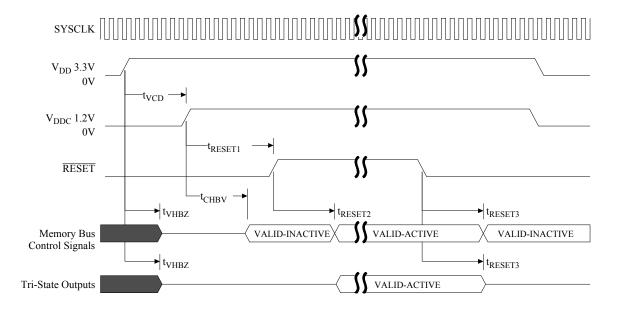

## 4.1 Power Sequencing and Reset

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol                           | Description                                                                                                                                                                                                          | Conditions                          | Min | Max | Units            |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|------------------|

| t <sub>VCD</sub> <sup>1</sup>    | $V_{\rm DD}$ valid to $V_{\rm DDC}$ delay                                                                                                                                                                            | $V_{DD} \ge 3.0V; V_{DDC} \ge 1.1V$ | 0   |     | ns               |

| t <sub>VHBZ</sub> <sup>1</sup>   | V <sub>DD</sub> valid to control signals high-z<br>(WRITE, OE, IOS, ROMS[1:0],<br>RWE[3:0], RAMOE [4:0], READ<br>SDWE, and SDCS[1:0])<br>V <sub>DD</sub> valid to outputs high-z                                     | $V_{DD} \ge 1.5 V; V_{DDC} = 0 V$   |     | 4   | t <sub>CLK</sub> |

|                                  | ([DATA[31:0], CB[7:0], and GPIO[15:0])                                                                                                                                                                               |                                     |     |     |                  |

| t <sub>CHBV</sub> 1              | $V_{DDC} \text{ valid to control signals valid-inac-tive} (WRITE, \overline{OE}, \overline{IOS}, \overline{ROMS[1:0]}, \overline{RWE[3:0]}, \overline{RAMOE [4:0]}, READ \overline{SDWE}, and \overline{SDCS[1:0]})$ | $V_{DD} \ge 3.0V; V_{DDC} \ge 1.1V$ |     | 4   | t <sub>CLK</sub> |

| t <sub>RESET1</sub> 1            | $V_{DDC}$ valid to $\overline{RESET}$ deassert                                                                                                                                                                       | $V_{DDC} \ge 1.1 V$                 | 4   |     | t <sub>CLK</sub> |

| t <sub>RESET2</sub> <sup>1</sup> | $\frac{\overline{\text{RESET}} \text{ deasserted to outputs valid-active}}{(\overline{\text{ROMS[0]}} \text{ and } \overline{\text{OE}})}$                                                                           |                                     |     | 12  | t <sub>CLK</sub> |

| t <sub>RESET3</sub> 1            | RESET asserted to control signals valid-<br>inactive<br>(WRITE, OE, IOS, ROMS[1:0],<br>RWE[3:0], RAMOE [4:0], READ<br>SDWE, and SDCS[1:0])RESET asserted to outputs high-z<br>(DATA[31:0], CB[7:0], and GPIO[15:0])  |                                     |     | 4   | t <sub>CLK</sub> |

Notes:

1. Guaranteed by design.

## 4.1.1. Power Sequencing

For optimal power sequencing, both power-up and power-down, ramp both  $V_{DD}$  and  $V_{DDC}$  together. During power-up, if  $V_{DDC} > V_{DD} + 0.3V$ , excessive current or damage may occur to the device. During power down, it is acceptable for  $V_{DD}$  to be less than  $V_{DDC}$  by more than 0.3V as long as  $V_{DDC}$  is not actively driven.

## 4.1.2 Bus Control and Bi-Direct Fail-Safe Circuitry

In order to prevent bus contention on the external memory interface while  $V_{DDC}$  is ramping up, the UT699E has functionality to ensure that the bi-direct and memory bus control signals described in Section 4.1 will be in a high-z state  $t_{VHBZ}$  delay after  $V_{DD}$  reaches 1.5V. The core logic will put these signals into their valid-inactive states  $t_{CHBV}$  clock cycles after  $V_{DDC}$  reaches 1.1V.

Aeroflex recommends that users place pull-up resistors on the indicated output enable, write enable, and chip select pins, and a pulldown resistor on the READ pin, if  $t_{VCD}$  is greater than 100ns. This will prevent bus capacitance or transients from inadvertently placing these pins in an active state, which could result in external memory devices driving the address and data buses.

## 4.1.3 Reset Circuitry

The reset circuitry is controlled by the core logic; therefore, the circuitry is functional only after  $V_{DDC}$  reaches its minimum operating voltage of 1.1V. After  $V_{DDC}$  is stable, the system must continue to assert  $\overline{RESET}$  for a minimum of  $t_{RESET1}$  clock cycles before it can be de-asserted. Asserting  $\overline{RESET}$  for less time could result in the  $\overline{RESET}$  signal not being recognized.

The UT699E will begin fetching code from external memory no more than  $t_{RESET2}$  clock cycles after  $\overline{RESET}$  is de-asserted. Control signals  $\overline{ROMS[0]}$  and  $\overline{OE}$  will be driven to their valid-active states in order for the UT699E to begin fetching code from PROM. During normal operation, the indicated bus control signals will go to a valid-inactive state, and the bi-directs will go to a high-z state, within  $t_{RESET3}$  clock cycles after the assertion of  $\overline{RESET}$ .

### 4.1.4 Boot Strap Programming on GPIO

Data on pins GPIO[2:0], GAPIO[7:4] and GPIO[15:12] are latched on the rising edge of reset. The states of GPIO[2:0] determine the data width of the PROM area, and enable EDAC for the PROM area. Chapter 3 of the User's Manual describes the value of these inputs to achieve the required operation. The states of GPIO[7:4] provides a means to configure the SpaceWire clock divisor link bits in the Clock Divisor Register. The states of GPIO[15:12] set the least significant address nibble of the IP and MAC address for the Ethernet Debug Communication Link (EDCL).

In order for the state of GPIO[2:0] to be properly latched, Aeroflex recommends placing pull-up or pull-down resistors on these pins to ensure that the setup and hold timing is met. The states of these pins should be statically set prior to the rising edge of  $\overline{\text{RESET}}$ .

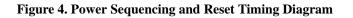

# 4.2 Output Timing Characteristics for Memory Interface, ERROR, and WDOG

| Symbol              | Description                                                                                                                                                                                                                           | Min | Max | Units |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| t1a <sup>1</sup>    | SDCLK↑ to ADDR[27:0] valid                                                                                                                                                                                                            | 1.5 | 8.5 | ns    |

| t1b <sup>1</sup>    | SDCLK↑ to SDCS[1:0] valid                                                                                                                                                                                                             | 2   | 7.5 | ns    |

| t1c <sup>1</sup>    | SDCLK↑ to output valid<br>SDRAS, SDCAS, and SDWE                                                                                                                                                                                      | 1.5 | 8.5 | ns    |

| t1d <sup>1</sup>    | SDCLK <sup>↑</sup> to SDDQM[3:0] valid                                                                                                                                                                                                | 2.5 | 8.5 | ns    |

| t1e <sup>1</sup>    | SDCLK <sup><math>\uparrow</math></sup> to output valid<br>(WRITE, $\overline{OE}$ , $\overline{IOS}$ , $\overline{ROMS[1:0]}$ , $\overline{RWE}$ [3:0], $\overline{RAMOE}$ [4:0],<br>$\overline{RAMS[4:0]}$ , and $\overline{READ}$ ) | 1   | 8   | ns    |

| t2 <sup>1,2</sup>   | SDCLK↑ to output valid<br>(DATA[31:0] and CB[7:0])                                                                                                                                                                                    | 2.5 | 8.5 | ns    |

| t3 <sup>1,2,3</sup> | SDCLK↑ to output high-Z<br>(DATA[31:0] and CB[7:0])                                                                                                                                                                                   | 2.5 | 8.5 | ns    |

| t4 <sup>1,4</sup>   | SDCLK↑ to signal low<br>(ERROR and WDOG)                                                                                                                                                                                              |     | 10  | ns    |

| t8 <sup>1,2,3</sup> | $\overline{\text{WRITE}}\uparrow$ or $\overline{\text{RWE}[3:0]}\uparrow$ to output high-z<br>(DATA [31:0] and CB[7:0])                                                                                                               | 0.5 |     | ns    |

| t9 <sup>1</sup>     | Skew from first memory output signal transition to last memory output signal transition                                                                                                                                               |     | 2   | ns    |

Notes:

All outputs are measured using the load conditions shown in Figure 15.

CB[7] is not tested.

3. High-Z defined as  $\pm$ -300mV change from steady state.

4.  $\overline{\text{WDOG}}$  guaranteed by design.

Figure 5. Memory Interface, ERROR, and WDOG Output Timing Diagram

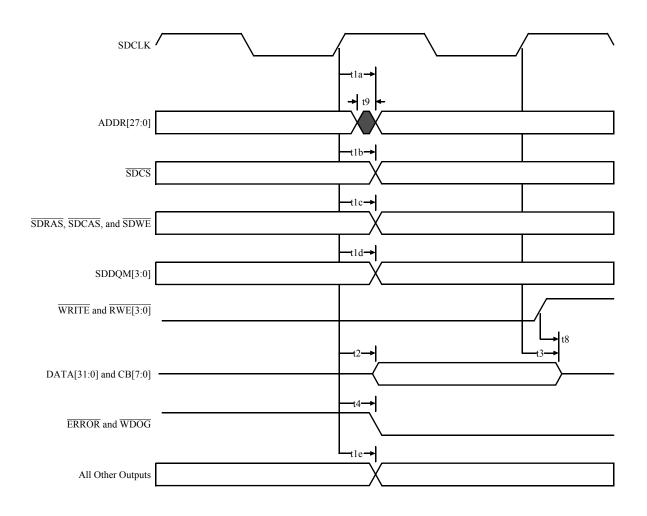

#### 4.3 Input Timing Characteristics for Memory Interface

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol             | Description                                                  | Min | Max | Units            |

|--------------------|--------------------------------------------------------------|-----|-----|------------------|

| t5a <sup>1,2</sup> | Setup time to SDCLK <sup>↑</sup><br>(DATA[31:0] and CB[7:0]) | 1   |     | ns               |

| t5b                | Setup time to SDCLK↑<br>(BEXC, and synchronous BRDY)         | 2   |     | ns               |

| t6a <sup>1,2</sup> | Hold time from SDCLK↑<br>(DATA[31:0] and CB[7:0])            | 1.5 |     | ns               |

| t6b                | Hold time from SDCLK↑<br>(Synchronous BRDY)                  | 0   |     | ns               |

| t7 <sup>3</sup>    | Asynchronous BRDY pulse width                                | 1.5 |     | t <sub>CLK</sub> |

#### Notes:

1. CB[7] is not tested.

2. CB[6:0] timing is guaranteed by design when used as inputs.

3. Supplied as a design limit. Neither guaranteed nor tested.

Figure 6. Memory Interface Input Timing Diagram

# 4.4 Timing Characteristics for General Purpose Input / Output (GPIO)

| Symbol           | Description                                 | Min | Max | Units |

|------------------|---------------------------------------------|-----|-----|-------|

| t10 <sup>1</sup> | SDCLK↑ to GPIO output valid<br>(GPIO[15:0]) |     | 10  | ns    |

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

#### Notes:

1. All outputs are measured using the load conditions shown in Figure 15.

Figure 7. General Purpose I/O Timing Diagram

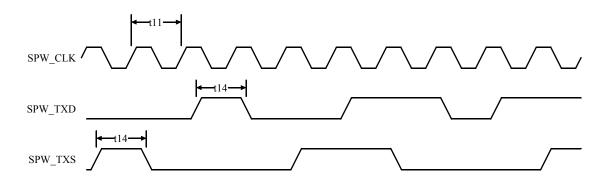

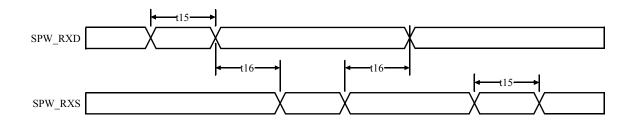

#### 4.5 Timing Characteristics SpaceWire Interface

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

| Symbol               | Description                                                                     | Min           | Max    | Units |

|----------------------|---------------------------------------------------------------------------------|---------------|--------|-------|

| t11 <sup>1,2</sup>   | SPW_CLK period                                                                  | 5             |        | ns    |

| t14 <sup>3,4,5</sup> | Transmit data and strobe bit width variation<br>(SPW_TXD[3:0] and SPW_TXS[3:0]) | UI-600        | UI+600 | ps    |

| t15 <sup>5,6</sup>   | Receive data and strobe bit width<br>(SPW_RXD[3:0] and SPW_RXS[3:0])            | 5             |        | ns    |

| t16 <sup>5</sup>     | Receive data and strobe edge separation<br>(SPW_RXD[3:0] and SPW_RXS[3:0])      | 1/2*t11 + 0.5 |        | ns    |

#### Notes:

1. The SPW\_CLK frequency must be less than or equal to 10x the SYSCLK frequency. For example, if SPW\_CLK is running at 200MHz, the SYSCLK frequency must be greater than or equal to 20MHz.

2. Functionally tested.

3. Applies to both high pulse and low pulse.

4. A unit interval (UI) is defined as the nominal, or ideal, bit width.

5. Guaranteed by design.

6. The SPW\_CLK period must be less than or equal to the minimum receive data/strobe bit width.

#### Figure 8. SpaceWire Transmit Timing Diagram

Figure 9. SpaceWire Receive Timing Diagram

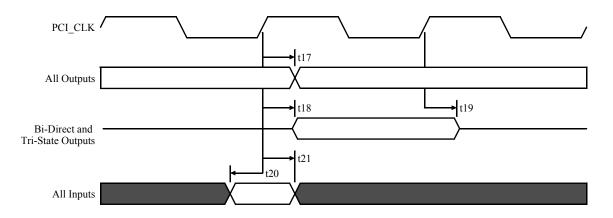

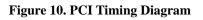

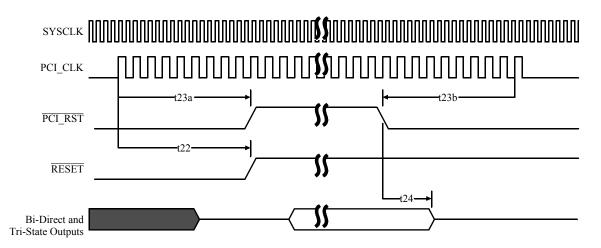

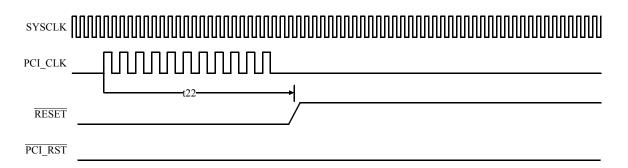

### 4.6 Timing Characteristics for PCI Interface

$(V_{DD} = 3.3V \pm 0.3V; V_{DDC} = 1.2V \pm 0.1V; T_C = -55^{\circ}C \text{ to } 105^{\circ}C)$

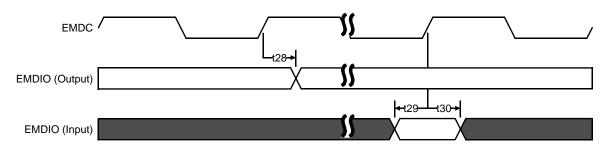

| Symbol             | Description                                                                                                                                                                           | Min | Max | Units      |