# UNISONIC TECHNOLOGIES CO., LTD

**UWD817 CMOS IC**

# MICROPOWER µP WATCH DOG **TIMER**

#### **DESCRIPTION**

The UTC UWD817 families are groups of high-precision, low current consumption voltage detectors with manual reset input and watchdog functions based on CMOS process. The series consist of a reference voltage source, delay circuit, comparator, and output driver. With the built-in delay circuit, the UTC UWD817 series do not require any external components to output signals with release delay time. The user can choose detect voltage thresholds.

The WDI pin in the UTC UWD817 can be left open if the watchdog function is not used. Whenever the watchdog pin is opened, the internal counter clears before the watchdog timeout occurs. Since the manual reset pin is internally pulled up to the V<sub>IN</sub> pin voltage level, the ICs can be used by leaving the manual reset pin unconnected if the pin is unused.

#### **FEATURES**

- \* Precision Supply-Voltage Monitor

- \* Operating Voltage Range: 1.0V~5.5V

- \* Output Configuration: CMOS

- \* Watchdog Function: Watchdog input WD \* Wide Temperature Range: -40°C to +85°C

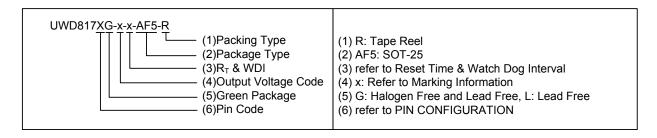

#### **ORDERING INFORMATION**

| Ordering Number    |                    | Reset | Watch           | LINUT | Cada | Dealters | Deaking   |

|--------------------|--------------------|-------|-----------------|-------|------|----------|-----------|

| Lead Free          | Halogen Free       | Time  | Dog<br>Interval | UNIT  | Code | Package  | Packing   |

| UWD817XL-x-x-AF5-R | UWD817XG-x-x-AF5-R | 210   | 1760            | ms    | F    | SOT-25   | Tape Reel |

# **■ MARKING INFORMATION**

| PACKAGE | VOLTAGE CODE                                                         | MARKING                             |

|---------|----------------------------------------------------------------------|-------------------------------------|

| SOT-25  | A: 2.63V<br>B: 2.93V<br>C: 3.08V<br>D: 4.00V<br>H: 4.40V<br>G: 4.65V | Pin Code W7AXF R <sub>T</sub> & WDI |

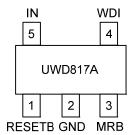

### **■ PIN CONFIGURATION**

# ■ PIN DESCRIPTION

| PIN NO. | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                                                  |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RESETB   | RESETB is active low. This pin can be push/pull.                                                                                                                                                                                                                             |

| 2       | GND      | Ground                                                                                                                                                                                                                                                                       |

| 3       | MRB      | Manual Reset. Active low. Pulling this pin low forces a reset. After a low to high transition reset remains asserted for exactly one reset timeout period. This pin is internally pulled high. If this function is unused then float this pin or tie it to V <sub>IN</sub> . |

| 4       | WDI      | Watch Dog Input. Any transition on this pin will reset the watch dog timer. If this pin remains high or low for longer than the watch dog interval then a reset is asserted. Float or tristate this pin to disable the watch dog feature.                                    |

| 5       | IN       | Positive power supply. A reset is asserted after this voltage drops below a predetermined level. After $V_{\text{IN}}$ rises above that level reset remains asserted until the end of the reset timeout period.                                                              |

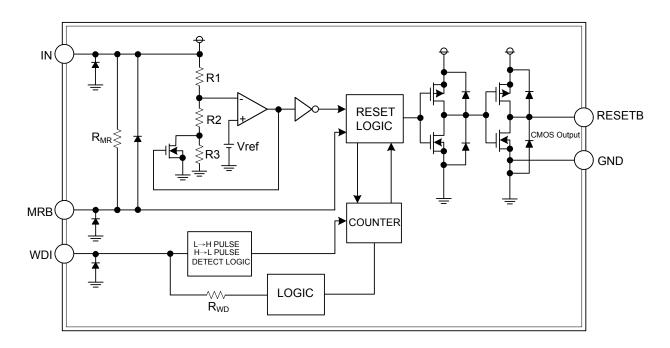

# ■ BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATING

| PARAMETER            | SYMBOL           | RATINGS    | UNIT |

|----------------------|------------------|------------|------|

| Supply Voltage       | $V_{IN}$         | 5.5        | V    |

| Power Dissipation    | $P_{D}$          | 400        | mW   |

| Junction Temperature | ΤJ               | +150       | °C   |

| Ambient Temperature  | T <sub>A</sub>   | -40 ~ +85  | °C   |

| Storage Temperature  | T <sub>STG</sub> | -65 ~ +150 | °C   |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

#### **■ THERMAL DATA**

| PARAMETER           | SYMBOL           | RATINGS | UNIT |

|---------------------|------------------|---------|------|

| Junction to Ambient | $\theta_{JA}$    | 310     | °C/W |

| Junction to Case    | $\theta_{ m JC}$ | 90      | °C/W |

# ■ **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub>=25°C, unless otherwise noted)

| PARAMETER                         | SYMBOL             | TEST CONDITIONS                                                   | MIN                    | TYP  | MAX                    | UNIT |

|-----------------------------------|--------------------|-------------------------------------------------------------------|------------------------|------|------------------------|------|

| V <sub>IN</sub> Range             | $V_{IN}$           |                                                                   | 1.0                    |      | 5.5                    | V    |

| Supply Current                    | I <sub>IN</sub>    |                                                                   |                        |      | 50                     | μA   |

| Reset Threshold                   | $V_{TH}$           |                                                                   | V <sub>TH</sub><br>-2% |      | V <sub>TH</sub><br>+2% | V    |

| Reset B Output Voltage High       | $V_{OH}$           | $V_{IN}$ > $V_{DF}$ Max. $I_{SOURCE}$ =0.5mA,<br>$T_A$ =-40~+85°C | 0.8V <sub>IN</sub>     |      |                        | >    |

| Reset B Output Voltage Low        | $V_{OL}$           | $V_{IN}$ < $V_{DF}$ Min. $I_{SNK}$ =1.2mA,<br>$T_A$ =-40~+85°C    |                        |      | 0.5                    | ٧    |

| V <sub>IN</sub> to Reset Delay    | $T_{D1}$           | V <sub>IN</sub> =V <sub>DF</sub> -100mV                           |                        | 40   |                        | μS   |

| Release Delay Time (Note 1)       | $t_{DR}$           |                                                                   | 140                    | 210  | 280                    | mS   |

| Watch Dog Timeout Period (Note 2) | $T_{WD}$           |                                                                   | 1120                   | 1760 | 2400                   | mS   |

| WDI Pulse Width                   | $T_{WDI}$          |                                                                   |                        | 300  |                        | nS   |

| WDI Input Throshold               | $W_{DI\;IL}$       | V <sub>IN</sub> =V <sub>TH</sub> x 1.2                            |                        |      | 0.7                    | V    |

| WDI Input Threshold               | $W_{DI\;IH}$       | VIN-VTH X 1.2                                                     | 0.8V <sub>IN</sub>     |      |                        | V    |

| M/DL Invest Comment               | I <sub>IL</sub>    | WDI=0V                                                            | -15                    | -8   |                        | μΑ   |

| WDI Input Current                 | I <sub>IH</sub>    | WDI=V <sub>IN</sub> =6.0V                                         |                        | 8    | 15                     | μΑ   |

| MDD Input Throshold               | M <sub>RB IL</sub> | \ -\\ \ \\ 12                                                     |                        |      | 0.7                    | V    |

| MRB Input Threshold               | M <sub>RB IH</sub> | $V_{IN}=V_{DF} \times 1.2$                                        | 0.8V <sub>IN</sub>     |      |                        | V    |

| MRB Pulse Width                   | $T_{WMRB}$         |                                                                   | 1                      |      |                        | μS   |

| MRB to Reset Delay                | $T_{DMRB}$         |                                                                   |                        | 500  |                        | nS   |

| MRB Pull Up Resistance            |                    |                                                                   | 80                     |      | 160                    | ΚΩ   |

Notes: 1. Release delay time (TWD) watchdog timeout period settings are available in 1.7s.

2. Watchdog timeout period settings are available in 1.7s.

**CMOS IC**

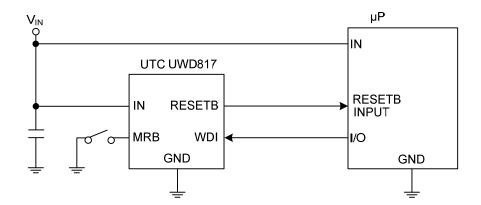

# TYPICAL APPLICATION CIRCUIT

#### OPERATIONAL EXPLANATION

The UTC **UWD817** series compare the voltage of the internal reference source with the voltage divided by R1, R2 and R3 connected to the  $V_{IN}$  pin. The resulting signal activates the watchdog logic, manual reset logic, delay circuit and the output driver. When the  $V_{IN}$  voltage gradually falls and finally reaches the detect voltage, the RESETB goes from high to low in the case of the  $V_{DFL}$  type ICs.

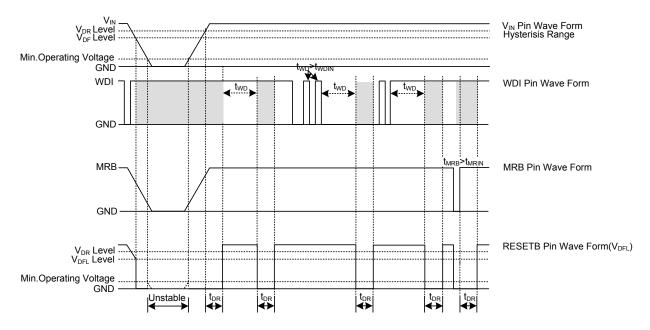

#### **Reset Output**

Each output pin in the series can be configured to be either CMOS. In addition each output may be either active high or active low. Active low reset outputs are denoted as RESETB.

When 3 things below are happen, the output will be reseted:

- 1. V<sub>IN</sub> drops below the threshold (V<sub>TH</sub>)

- 2. The MRB pin is pulled low.

- 3. The WDI pin does not detect a transition signal within the watch dog interval (TWD).

The reset will remain asserted for the prescribed reset interval after:

- 1. V<sub>IN</sub> rises above the threshold (V<sub>TH</sub>)

- 2. MRB goes high

- 3. The watch dog timer has timed out causing the reset to assert.

### **Manual Reset Input**

Using the MRB pin input, the RESETB pin signal can be forced to the detection state. When the MRB pin is driven from high to low, the RESETB pin output goes from high to low level in the case of the  $V_{DFL}$  type ICs. Even after the MRB pin is driven back high, the RESETB pin output maintains the detection state for the release delay time ( $t_{DR}$ ). Because of internally pulled up for the MRB pin, so leave the MRB pin open if unused. A diode, which is an input protection element, is connected between the MRB pin and  $V_{IN}$  pin. Therefore, when the MRB pin voltage exceeds  $V_{IN}$ , the current will flow to  $V_{IN}$  through the diode. Please use this IC within the stated maximum ratings ( $V_{SS}$ -0.3 $\sim$  $V_{IN}$ +0.3 $\leq$ 6.0V) on the MRB pin.

### ■ OPERATIONAL EXPLANATION (Cont.)

#### Watchdog Input

The UTC **UWD817** series use a watchdog timer to detect malfunction or "runaway" of the microprocessor. If neither rising nor falling signals are applied from the microprocessor within the watchdog timeout period, the RESETB pin output maintains the detection state for the release delay time ( $t_{DR}$ ), and thereafter the RESETB pin output returns to the release state. The timer in the watchdog is then restarted. Watchdog timeout period settings are available in 1.7s

#### **Release Delay Time**

Release delay time ( $t_{DR}$ ) is the time that elapses from when the  $V_{IN}$  pin reaches the release voltage, or when the watchdog timeout period expires with no rising signal applied to the WDI pin, until the RESETB pin output is released from the detection state.

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. UTC reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.