#### **Features**

- Output Frequencies from 155 MHz to 800 MHz

- Low Jitter < 1 ps rms in the 12kHz to 20MHz range

- < 1ps rms jitter in 50kHz to 80MHz range</li>

- 3.3V (see VS-500) or 5.0V operation

- Ideal for clock smoothing, frequency translation, clock and data retiming applications

- 10K ECL, PECL logic levels with fast transition times

- Complementary outputs

- · Low profile, surface mount package

- Output disable feature

#### **Applications**

- 2.5, 10 Gbit/s FEC and standard SONET/SDH Clock Smoothing and Frequency Translation

- 10 Gigabit Ethernet Clock Smoothing

- Frequency Translation

#### **Description**

The VS-500A is a SAW based voltage controlled oscillator that operates at the fundamental frequency of the internal SAW filter. This resonator is a high-Q quartz device that enables the circuit to achieve low phase jitter performance over a wide operating temperature range. The oscillator is housed in a hermetically sealed J-lead surface mount package offered on tape and reel. It has an output disable to facilitate on-board testing.

### **Pin Information**

| Table 1. Pin Function |         |                                   |            |  |  |  |  |  |

|-----------------------|---------|-----------------------------------|------------|--|--|--|--|--|

| Pin                   | Symbol  | Function                          | - 6 5 4    |  |  |  |  |  |

| 1                     | Vc      | VCSO Control Voltage              | 0 3 4      |  |  |  |  |  |

| 2                     | OD      | Output Disable                    | TOP VIEW   |  |  |  |  |  |

| 3                     | GND     | Case and electrical ground        | - TOP VIEW |  |  |  |  |  |

| 4                     | Output  | VCSO Output                       |            |  |  |  |  |  |

| 5                     | COutput | VCSO Complimentary Output         | 1 2 3      |  |  |  |  |  |

| 6                     | Vcc     | Power Supply Voltage (5.0 V ±10%) |            |  |  |  |  |  |

<sup>1.</sup> By setting OD low, the outputs are disabled and OUT is held high while Complementary OUT is held low. The threshold for Output Disable is 1.4V above pin 3. Output Disable should not be driven above mid supply and during normal operation, should be left floating (use with an open collector or 3-State gate for interfacing with standard logic).

#### **Performance Characteristics**

| Parameter                                                             | Symbol          | Minimum               | Typical | Maximum               | Units   |

|-----------------------------------------------------------------------|-----------------|-----------------------|---------|-----------------------|---------|

| Center Frequency, see ordering information                            | Fn              | 155                   |         | 800                   | MHz     |

| Operating Temperature                                                 | Тор             | -40                   | 25      | +85                   | °C      |

| Supply Current (no load)                                              | Icc             |                       | 55      | 70                    | mA      |

| Supply Voltage                                                        | V <sub>CC</sub> | 4.5                   | 5       | 5.5                   | V       |

| Absolute Pull Range over -40 to 85°C (Vc= 0.5 to 4.5)                 | APR             | ±50                   | -       | -                     | ppm     |

| Positive Gain Transfer @ 155.52MHz<br>(Frequency vs Control voltage)  | Kv              | -                     | 350     | -                     | ppm/V   |

| Positive Gain Transfer @ 622.080MHz<br>(Frequency vs Control voltage) | Kv              | -                     | 200     | -                     | ppm/V   |

| Linearity                                                             | Lin             |                       | ±3      |                       | %       |

| Frequency Stability, -40 to 85 wrt 25°C                               | FSTAB           |                       | ±150    |                       | ppm     |

| Output Level Low¹                                                     | Vol             | V <sub>CC</sub> -1.95 | -       | V <sub>CC</sub> -1.63 | V       |

| Output Level High <sup>1</sup>                                        | Vон             | V <sub>CC</sub> -0.98 | -       | V <sub>CC</sub> -0.75 | V       |

| Output Rise Time <sup>2</sup>                                         | t <sub>R</sub>  |                       | 250     | 400                   | ps      |

| Output Fall Time <sup>2</sup>                                         | t <sub>F</sub>  |                       | 250     | 400                   | ps      |

| Jitter @ 155.520 MHz, 12 KHz to 20 MHz                                |                 |                       | 0.439   |                       | ps, rms |

| Jitter @ 622.080 MHz, 12 KHz to 20 MHz                                |                 |                       | 0.276   |                       | ps, rms |

| Jitter @ 622.080 MHz, 50 KHz to 80 MHz                                |                 |                       | 0.293   |                       | ps, rms |

| Spurious Suppression                                                  |                 | -50                   | -60     |                       | dB      |

| Data Symmetry                                                         | SYM             | 45                    | 49/51   | 55                    | %       |

| Control Voltage Input Impedance                                       | Zc              | 8                     | 10      | 12                    | ΚΩ      |

| Control Voltage Modulation Bandwidth                                  | BW              | -                     | 500     | -                     | kHz     |

| Output Current                                                        | lout            | -                     | -       | 20                    | mA      |

<sup>1.</sup> Output Levels are standard 10K ECL and are fully 100K ECL compatible.

<sup>2.</sup> Transition times are measured from 20% to 80% of a full 10K ECL level swing.

| Table 3. Typical Single Side-Band Phase Noise (dBc/Hz) |        |      |       |        |  |  |  |  |

|--------------------------------------------------------|--------|------|-------|--------|--|--|--|--|

| Offset from Carrier                                    | 100 Hz | 1kHz | 10kHz | 100kHz |  |  |  |  |

| VS-500A 622.080                                        | -62    | -85  | -109  | -127   |  |  |  |  |

Note 2: To diasble output, connect Output Disable to ground. To enable output, leave pin 2 floating or open.

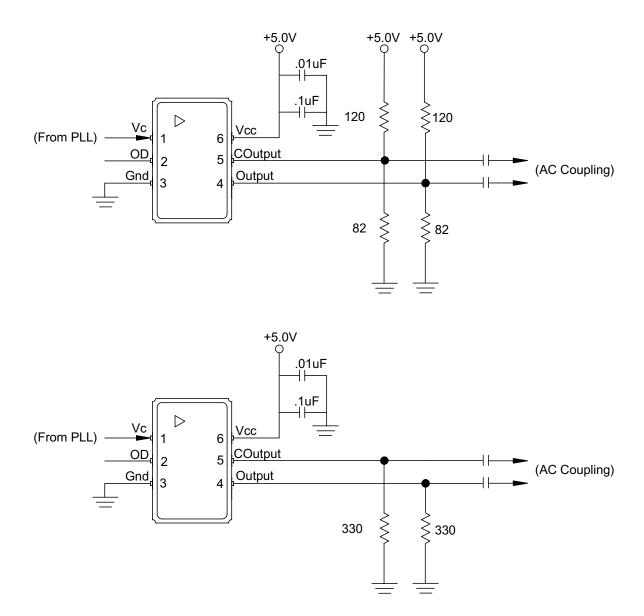

Figure 1 PECL Operation

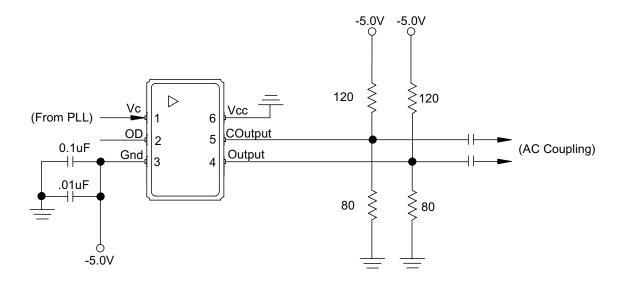

Note1: Conductive lid will be @ -5V for ECL configuration

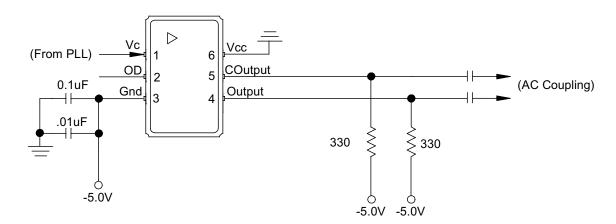

Note 2: To diasble output, connect Output Disable to -5V. To enable output, leave pin 2 floating or open.

Figure 2. ECL Operation

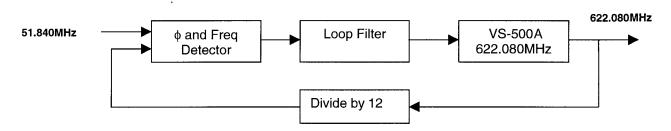

Figure 3. Typical Frequency Translation Diagram

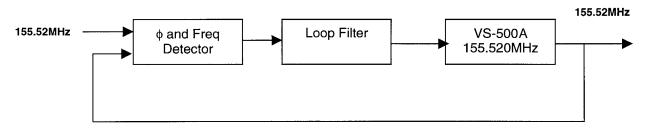

Figure 4. Typical Clock Smoothing Diagram

#### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can permanently damage the device. Functional operation is not implied at these or any other conditions in excess of conditions represented in the operational sections of this data sheet. Exposure to absolute maximum ratings for extended periods may adversely affect device reliability.

| Table 4. Absolute Maximum Ratings  |        |                 |            |  |  |  |  |  |

|------------------------------------|--------|-----------------|------------|--|--|--|--|--|

| Parameter                          | Symbol | Ratings         | Unit       |  |  |  |  |  |

| Power Supply                       | Vcc    | 0 to 8          | V          |  |  |  |  |  |

| Output Current <sup>1</sup>        | lout   | 20              | mA         |  |  |  |  |  |

| Output Current <sup>2</sup>        | lout   | 50              | mA         |  |  |  |  |  |

| Voltage Control Range <sup>1</sup> | Vc     | 0 to Vcc        | V          |  |  |  |  |  |

| Voltage Control Range <sup>2</sup> | Vc     | -0.5 to Vcc+0.5 | V          |  |  |  |  |  |

| Storage Temperature                | Ts     | -55 to 125      | °C         |  |  |  |  |  |

| Soldering Temp./Time               | TLS    | 220/10          | °C/Seconds |  |  |  |  |  |

<sup>1</sup> Limts beyond which performance can not be guaranteed.

#### **Qualification Conformance**

The VS-500A family passes the following Mil-Std qualification.

| Table 5. Environmental Compliance |                          |  |  |  |  |  |  |

|-----------------------------------|--------------------------|--|--|--|--|--|--|

| Parameter                         | Conditions               |  |  |  |  |  |  |

| Mechanical Shock                  | MIL-STD-883, Method 2002 |  |  |  |  |  |  |

| Mechanical Vibration              | MIL-STD-883, Method 2007 |  |  |  |  |  |  |

| Solderability                     | MIL-STD-883, Method 2003 |  |  |  |  |  |  |

| Gross and Fine Leak               | MIL-STD-883, Method 1014 |  |  |  |  |  |  |

| Resistance to Solvents            | MIL-STD-883, Method 2016 |  |  |  |  |  |  |

<sup>2</sup> Limits beyond which device life may be impaired.

#### **Handling Precautions**

Although ESD protection circuitry has been designed into the VS-500A proper precautions should be taken when handling and mounting. VI employs a human body model and a charged-device model (CDM) for ESD susceptibility testing and design protection evaluation. ESD thresholds are dependent on the circuit parameters used to define the model. Although no industry wide standard has been adopted for the CDM, a standard HBM of resistance = 1.5Kohms and capacitance = 100pF is widely used and therefore can be used for comparison purposes.

| Table 6. ESD Ratings       |       |  |  |  |  |  |

|----------------------------|-------|--|--|--|--|--|

| Model Minimum              |       |  |  |  |  |  |

| Human Body Model           | 1500V |  |  |  |  |  |

| Charged Device Model 1000V |       |  |  |  |  |  |

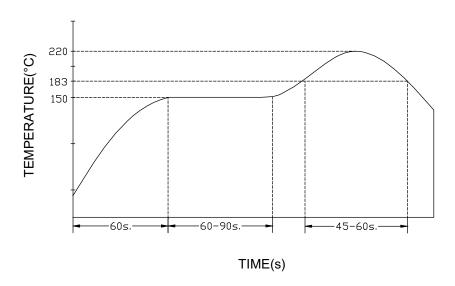

Figure 5. Suggested IR profile

VI qualification includes aging at various extreme temperatures, shock and vibration, temperature cycling and IR reflow simulation. The conditions a device can withstand are well understood and devices can be subjected to the profile in figure 5. This profile shows a ramp up condition to prevent thermal shock, a preheat period in which the flux is activated, a ramp up to 183°C which is the reflow temperature of Sn/Pb eutectic and a gradual cool down. The time above 183°C should not exceed 60 seconds and the peak temperature should be no more than 220°C for 10 seconds. The VS-500A's are 100% screened for hermiticity so an aqueous wash is not an issue.

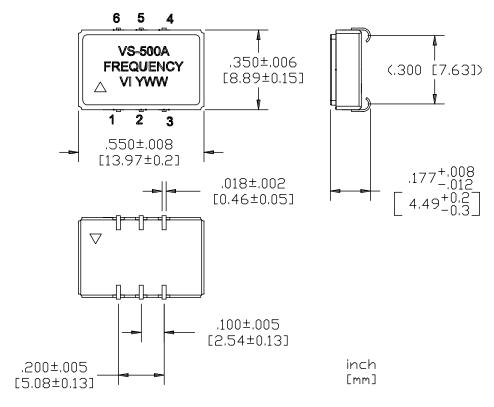

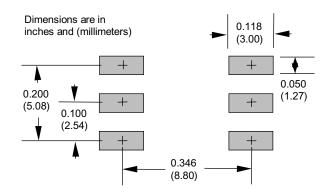

Figure 6. Outline Diagram

Figure 7. Suggested Pad Layout

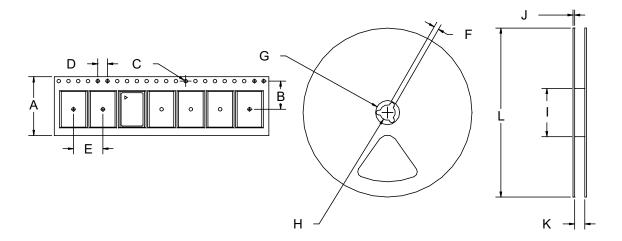

Figure 8. Tape Reel Drawing

| Table 7. Tape and Reel Dimensions (mm) |                                 |                         |     |   |    |      |    |    |     |            |    |     |     |

|----------------------------------------|---------------------------------|-------------------------|-----|---|----|------|----|----|-----|------------|----|-----|-----|

| Tape Dime                              | Tape Dimensions Reel Dimensions |                         |     |   |    |      |    |    |     | # Per Reel |    |     |     |

| Product                                | Α                               | A B C D E F G H I J K L |     |   |    |      |    |    |     |            |    |     |     |

| VS-500A                                | 24                              | 11.5                    | 1.5 | 4 | 12 | 1.78 | 21 | 13 | 100 | 5          | 25 | 330 | 200 |

### **Ordering Information**

| Table 8. Available Frequencies (MHz) |          |          |          |  |  |  |  |  |

|--------------------------------------|----------|----------|----------|--|--|--|--|--|

| 155.520                              | 156.250  | 161.1328 | 166.6286 |  |  |  |  |  |

| 177.7371                             | 311.040  | 622.080  | 624.7048 |  |  |  |  |  |

| 625. 000                             | 627.3296 | 644.5313 | 666.5143 |  |  |  |  |  |

| 669.1281                             | 669.3265 | 690.5692 | 719.7344 |  |  |  |  |  |

| 759.410                              | 765.5906 | 767.250  | 777.600  |  |  |  |  |  |

Other frequencies available upon request

## For additional information please contact:

USA: Vectron International • 267 Lowell Road, Hudson, NH 03051

.... Tel: 1-88-VECTRON-1 • Fax: 1-888-FAX-VECTRON

EUROPE:

.... Tel: 49 (0) 3328 4784 17 ĈFax: 49 (0) 3328 4784 30

www.vectron.com

ASIA: ...... Tel: +86 21 28909740 / 41 / 42 Ĝrax: +86 21 28909240 / 2890999

Vectron International reserves the right to make changes to the product(s) and/or information contained herein without notice.

No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

© 2001, Vectron International Printed in USA 2/02