# VS3000 Family Data Sheet

Version 1.2

### **Important Notice**

This document contains proprietary information on the Valens VS3000 Product Series. This document may not be photocopied. It may only be released to companies who have signed a Non-Disclosure Agreement with Valens Semiconductor Ltd. specifically regarding the Valens VS3000 Product Series.

Valens reserves the right to make corrections, modifications, enhancements, improvements and other changes to its products and services at any time and to discontinue any product or service without notice. Customers must obtain the latest relevant information before placing orders and must verify that such information is current and complete. All products are sold subject to Valens's terms and conditions of sale supplied at the time of order acknowledgment.

Valens does not warrant performance of its hardware and software products except to the specifications applicable at the time of sale in accordance with Valens's standard warranty. Testing and other quality control techniques are used to the extent Valens deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

Valens assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using Valens components. To minimize the risks associated with customer products and applications, customers must provide adequate design and operating safeguards.

Valens does not warrant or represent that any license, either expressed or implied, is granted under any Valens patent, copyright, mask work right or other Valens intellectual property right relating to any combination, machine or process in which Valens products or services are used. Information published by Valens regarding third-party products or services does not constitute a license from Valens to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party or a license from Valens under the patents or other intellectual property of Valens.

Valens products are not designed, intended or authorized for use as components in systems intended for surgical implantation into the body or other applications intended to support life or for any other application in which the failure of the Valens product may result in personal injury or death. Should the Buyer purchase or use Valens products for any such unintended or unauthorized application, the Buyer shall indemnify and not hold responsible Valens and its officers, employees, subsidiaries, affiliates and distributors against all claims, costs, damages and expenses and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Valens was negligent regarding the design or manufacture of the part. Reproduction of information in Valens data books or datasheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices.

Reproduction of this information with alteration is an unfair and deceptive business practice. Valens is not responsible or liable for such altered documentation.

Resale of Valens products or services with statements different from or beyond the parameters stated by Valens for that product or service voids all express and any implied warranties for the associated Valens product or service and is an unfair and deceptive business practice. Valens is not responsible or liable for any such statements.

HDBaseT™ and the Valens logo are trademarks of Valens Semiconductor. All other trademarks are the property of their respective owners.

Copyright © 2022, Valens Semiconductor Ltd.

### **Contact Information**

Valens Semiconductor Ltd.

8 Hanagar St. • POB 7152

Hod Hasharon 4501309 • Israel

Tel: +972-9-762-6900 • Fax: +972-9-762-6901

info@valens.com • www.valens.com

# **Revision History**

| Revision | Date             | Author      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.1      | May 2018         | Yaki Sfadya | First Draft                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 0.2      | August 2018      | Yaki Sfadya | <ul> <li>Second draft. Updated wording for all paragraphs.</li> <li>Updated electrical info:         <ul> <li>Table 4: VS3000 Functional Signal Table; needs further editing</li> <li>Table 6: Reference Resistor Values</li> <li>2.3.4 Ball Diagram</li> <li>Electrical specification: Absolute Maximum Rating</li> <li>Table 17: VS3000 Absolute Maximum Rating</li> <li>Table 19: VS3000 Power Supply</li> <li>Reference Clock Requirements</li> <li>Electrical Characteristics (DC Specifications)</li> <li>Table 25: VS3000 Electrical Specification</li> <li>Table 27: VS3000 AC Specification</li> </ul> </li> <li>Power on Reset Signal Timing edited note</li> </ul> |  |  |

| 0.3      | December 2018    | Yaki Sfadya | <ul> <li>Updated pin out tables</li> <li>Updated STRAP pins tables – HW and SW</li> <li>Added USB_ID strap</li> <li>Updated according to HW group review</li> <li>Updated Pin out table per last version</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 0.31     | January 2019     | Yaki Sfadya | Corrected mistake in pin out of HDBT swap (N) and (P)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.32     | January 2019     | Yaki Sfadya | <ul> <li>Updated pin out table according to EVK CDR</li> <li>Updated clock reference to 25Mhz only</li> <li>Updated Table 15</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 0.33     | January 2019     | Yaki Sfadya | Corrected VDDA_33 in table 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 0.34     | January 17, 2019 | Yaki Sfadya | Updated pin out to align with Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 0.35     | February 2019    | Yaki Sfadya | <ul> <li>Updated SW Straps and FW LED blinking -&gt;2hz</li> <li>Updated Power consumption rating</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|      |                |             | Updated AC electrical characteristic: RMII;     MDC/MDI; SGMII; QSPI; I2C; I2S; UART; DHDI     |

|------|----------------|-------------|------------------------------------------------------------------------------------------------|

|      |                |             | Updated mechanical drawing                                                                     |

|      |                |             | Updated Ethernet T-A interfaces                                                                |

| 0.36 | February 27,   | Yaki Sfadya | Updated Chapter 8: Quality and environmental                                                   |

|      | 2019           | ,           | Updated chapter 7: Thermal parameters                                                          |

| 0.37 | March 3, 2019  | Yaki Sfadya | Updated USB section                                                                            |

| 0.38 | March 4, 2019  | Yaki Sfadya | Updated Power consumption table                                                                |

|      | ,              | ,           | Corrected functionality of GPO [2] GPO [4]                                                     |

|      |                |             | Updated device marking                                                                         |

| 0.39 | March 17, 2019 | Yaki Sfadya | Updated GPOs and LEDs description                                                              |

|      |                | ,           | Corrected reference clock chapter                                                              |

| 0.40 | March 21, 2019 | Yaki Sfadya | Updated I/F block diagram                                                                      |

| 0.41 | April 7, 2019  | Yaki Sfadya | Updated ball map                                                                               |

|      | . ,            | ,           | <ul> <li>Updated figure 8, interface diagram</li> </ul>                                        |

|      |                |             | Corrected mistakes according to review                                                         |

|      |                |             | Updated CEC and DDC description                                                                |

| 0.42 | April 18, 2019 | Yaki Sfadya | Updated HDMI swappable option                                                                  |

|      |                |             | Removed UART rate of 1.8Mbps                                                                   |

|      |                |             | Updated FW LED indication description for wait state                                           |

|      |                |             | Corrected GPIO_x signals name to GPIOx                                                         |

|      |                |             | Updated the description connectivity of DHDI interface                                         |

| 0.43 | April 22, 2019 | Yaki Sfadya | Aligned PS names                                                                               |

|      |                |             | Corrected POR section description and pins                                                     |

|      |                |             | Corrected text errors                                                                          |

| 0.44 | April 28, 2019 | Yaki Sfadya | Updated POR figure 26 and text                                                                 |

|      |                |             | Corrected QSPI timing - table 28                                                               |

|      |                |             | Added note for 5V signals end of table 4                                                       |

| 0.45 | May 5, 2019    | Yaki Sfadya | Initial release                                                                                |

| 0.46 | August 6, 2019 | Yaki Sfadya | Clarified the STRAP bits notation                                                              |

|      |                |             | Updated UART port # assignment for Host IF and<br>Logger and added description for logger port |

|      |                |             | Updated pin names (T5, U5) from FU to DBG TX and RX                                            |

|      |                |             | Added to Power consumption description that<br>figures include concurrency HDMI operation      |

| 0.47 | November 2019  | Yaki Sfadya | Updated ordering code                                                                          |

| 0.48 | December 2019  | Yaki Sfadya | Updated the symbol and pin name: GPIO6 changed to: GPO9(/SW_STRAP[15])                         |

| 0.49 | March 2020     | Yaki Sfadya | Corrected SWStarp[10] description to 0 – boot; 1- WFH                                          |

|      |                |             | Added description for interrupt for I2C Clock<br>stretching removal – GPIO2                    |

|      |                |             | Added description for interrupt signals for<br>matrix design application support – GPIO7,<br>GPIO64, GPIO65             |  |  |

|------|----------------|-------------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.50 | April 2020     | Yaki Sfadya | <ul> <li>Updated the power supplies: VDD and VDDA =<br/>0.95V; HDBT_VDDA = 0.98V</li> </ul>                             |  |  |

|      |                |             | Updated the estimated Power consumption                                                                                 |  |  |

|      |                |             | Updated MSIO Compatibility with VS100 PDIF                                                                              |  |  |

|      |                |             | Removed future support, from Audio     Extract/insert                                                                   |  |  |

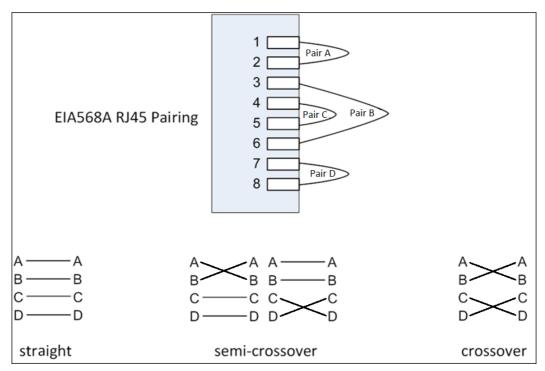

|      |                |             | <ul> <li>Added description of A -&gt; D &amp; B -&gt;C pairs<br/>swapping</li> </ul>                                    |  |  |

|      |                |             | Updated Package drawing                                                                                                 |  |  |

| 0.51 | July 2020      | Yaki Sfadya | Removed max Power consumption estimations                                                                               |  |  |

| 0.52 | July 2020      | Yaki Sfadya | Corrected signal name in table 5: to VDDIO_18                                                                           |  |  |

|      |                |             | <ul> <li>Corrected figure 9 pins T5 and U5 to DBG_RX and<br/>DBG_TX. And in DBG_RX to Input only in table 4.</li> </ul> |  |  |

| 0.53 | August 9, 2020 | Yaki Sfadya | <ul><li>Updated typical Power consumption figures</li><li>Updated marking and ordering info</li></ul>                   |  |  |

| 0.54 | September 2020 | Yaki Sfadya | Updated typical PC according to tests                                                                                   |  |  |

| 0.55 | October 2020   | Yaki Sfadya | Updated power consumption tables with split<br>per power supply                                                         |  |  |

| 0.56 | November 2020  | Yaki Sfadya | Updated conditions for power consumption                                                                                |  |  |

| 0.57 | November 2020  | Yaki Sfadya | Corrected SWStrap[14] description of USBH and USBD                                                                      |  |  |

|      |                |             | <ul> <li>Updated table 4. Signal description of USB_ID0<br/>(D19) - reset state as PU, Input</li> </ul>                 |  |  |

| 0.58 | December 2020  | Yaki Sfadya | Corrected refence to AN3001 and Host Interface<br>Reference Guide                                                       |  |  |

| 0.59 | January 2021   | Yaki Sfadya | <ul> <li>Added for USB – supported number of<br/>endpoints.</li> </ul>                                                  |  |  |

|      |                |             | Corrected wrong power supplies voltages value.                                                                          |  |  |

| 0.60 | March 2021     | Yaki Sfadya | Corrected description USBID in table 4                                                                                  |  |  |

| 0.61 | May 2021       | Yaki Sfadya | <ul> <li>Removed the 10Mb Ethernet from text Added full duplex</li> </ul>                                               |  |  |

|      |                |             | Updated the Crystal requirements                                                                                        |  |  |

| 1.0  | August 2021    | Yaki Sfadya | Removed preliminary version                                                                                             |  |  |

|      |                |             | Added definition for CAT6A U/FTP for max res.                                                                           |  |  |

|      |                |             | Added future support for multidevice support                                                                            |  |  |

| 1.1  | January 2022   | Yaki Sfadya | Updated Table 1 – CAT cable and range                                                                                   |  |  |

|      |                |             | Added description to HDMI LED - When partner  design is baselinesed 4.5D in disease DDG.                                |  |  |

|      |                |             | device is backward, LED indicates DDC transactions on HDCP addresses (0x74/0x75).                                       |  |  |

| 1.2  | May 2022       | Yaki Sfadya | Added support for 64Mbit Flash                                                                                          |  |  |

| 1.2  | 1VIQY 2022     | Taki Siauya | Updated the description of Mem BISR STRAP                                                                               |  |  |

|      |                |             | Added MSIO compatibility table with VS2000                                                                              |  |  |

|      |                |             | Removed STRAP[0]                                                                                                        |  |  |

|      | l              | 1           | I Land                                                                                                                  |  |  |

# Glossary

| Term             | Definition                                            |  |  |

|------------------|-------------------------------------------------------|--|--|

| ARC              | Audio Return Channel                                  |  |  |

| AFE              | Analog Front End                                      |  |  |

| AV               | Audio Video / Audio-Visual                            |  |  |

| CE               | Consumer Electronics                                  |  |  |

| CEC              | Consumer Electronic Control                           |  |  |

| CIR              | Consumer Infrared                                     |  |  |

| EVK              | Evaluation Kit                                        |  |  |

| CTS              | Compliance Test Specification                         |  |  |

| DDC              | Display Data Channel                                  |  |  |

| DVI              | Digital Visual Interface                              |  |  |

| EEPROM           | Electronically Erasable Programmable Read-Only Memory |  |  |

| GPIO             | General Purpose Input Output                          |  |  |

| HD               | High Definition                                       |  |  |

| HDBT             | HDBaseT                                               |  |  |

| HDCD             | HDBaseT Configuration Database                        |  |  |

| HDCP             | High-Bandwidth Digital Content Protection             |  |  |

| HDMI             | High Definition Multimedia Interface                  |  |  |

| HIF              | Host Interface                                        |  |  |

| HLIC             | HDBaseT Link Internal Controls                        |  |  |

| HPD              | Hot Plug Detect                                       |  |  |

| I/F              | Interface                                             |  |  |

| IC               | Integrated Circuit                                    |  |  |

| I <sup>2</sup> C | Inter IC                                              |  |  |

| I <sup>2</sup> S | Inter IC Sound                                        |  |  |

| KVM              | Keyboard / Video / Mouse                              |  |  |

| LPPF             | Low Power Partial Functionality                       |  |  |

| LSB              | Least Significant Bit                                 |  |  |

| LVDS             | Low-Voltage Differential Signaling                    |  |  |

| MSIO             | Multi Serial Input Output                             |  |  |

| MAC              | Media Access Control Layer                            |  |  |

| MCU              | Microcontroller Unit                                  |  |  |

| RoHS             | Restriction of Hazardous Substances Directive         |  |  |

| SNR              | Signal-to-Noise Ratio                                 |  |  |

| MIB              | Management Information Base                           |  |  |

| MSB              | Most Significant Bit                                  |  |  |

| ОМ               | Operation Mode                                        |  |  |

| Term   | Definition                              |  |

|--------|-----------------------------------------|--|

| PHY    | Physical Layer                          |  |

| PoE    | Power Over Ethernet                     |  |

| PRBS   | Pseudo Random Bit Stream                |  |

| SERDES | SERializer DESerializer                 |  |

| SPDIF  | Sony/Philips Digital Interface Format   |  |

| SPI    | Serial Peripheral Interface             |  |

| STB    | Set-Top Box                             |  |

| UART   | Universal Asynchronous Receive Transmit |  |

| USB    | Universal Serial Bus                    |  |

### **Contents**

| 1 | Introd | luction                                               | 15 |

|---|--------|-------------------------------------------------------|----|

|   | 1.1    | About the VS3000                                      | 15 |

|   | 1.2    | Main Benefits                                         | 15 |

|   | 1.3    | Main Applications                                     | 16 |

|   | 1.4    | Supported Protocols                                   | 16 |

|   | 1.5    | Block Diagram                                         | 17 |

|   | 1.6    | Features                                              | 17 |

|   | 1.7    | Typical Application Examples                          | 20 |

|   |        | 1.7.1 HDMI Extender Application                       | 20 |

|   |        | 1.7.2 Daisy-Chain Applications (future support)       | 21 |

|   |        | 1.7.3 Video Wall Multicasting (future support)        | 22 |

|   |        | 1.7.4 KVM Extension/Switching System (future support) | 23 |

|   |        | 1.7.5 Audio Extract and Insert                        | 24 |

|   | 1.8    | HDBaseT Technology Overview                           | 25 |

|   | 1.9    | HDBaseT Channel Terminology                           | 26 |

|   | 1.10   | VS3000 Port duality                                   | 26 |

| 2 | Pin an | d Signal Configuration                                | 27 |

|   | 2.1    | VS3000 Interface Diagram                              | 27 |

|   | 2.2    | Pin Type Convention                                   | 29 |

|   |        | 2.2.1 IO Pad Types                                    | 29 |

|   |        | 2.2.2 Unused Pins                                     | 29 |

|   | 2.3    | VS3000 Signal Description                             | 29 |

|   |        | 2.3.1 Functional Signals                              | 30 |

|   |        | 2.3.2 Non-Functional Signals                          | 39 |

|   |        | 2.3.3 Bias Resistors                                  | 39 |

|   |        | 2.3.4 Ball Diagram (Top View)                         | 39 |

| 3 | Functi | onal Description                                      | 41 |

|   | 3.1    | HDBaseT Interface                                     | 41 |

|   |        | 3.1.1 HDBaseT Operational Modes                       | 42 |

|   |        | 3.1.1.3 Active                                        | 43 |

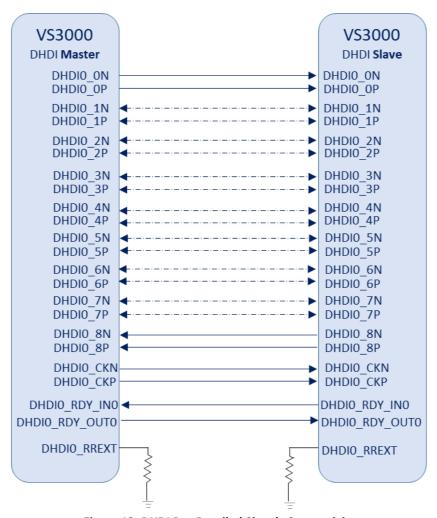

|   | 3.2    | Double High Definition Digital Interface (DHDI)       | 44 |

|   |        | 3.2.1 Setting DHDI Bus Mode of operation              | 44 |

|   |        | 3.2.2 Setting DHDI Bus Rate of Operation              | 44 |

|   |        | 3.2.3 Setting the DHDI Bus Link Master/Slave Role     | 44 |

|   | 3.3   | I-Adaptors                                      | 45 |

|---|-------|-------------------------------------------------|----|

|   |       | 3.3.1 HDMI Interface                            | 46 |

|   |       | 3.3.2 Ethernet PHY System                       | 49 |

|   |       | 3.3.3 USB Interface                             | 51 |

|   |       | 3.3.4 UART T-Adaptor Functionality              | 55 |

|   |       | 3.3.5 I <sup>2</sup> C T-Adaptor Functionality  | 57 |

|   |       | 3.3.6 Audio T-Adaptor                           | 58 |

|   |       | 3.3.7 IR T-Adaptor                              | 61 |

|   |       | 3.3.8 MSIO T-Adaptor                            | 62 |

|   | 3.4   | External FLASH Memory Interface                 | 63 |

|   | 3.5   | External Host Interfaces                        | 64 |

|   |       | 3.5.1 Managing the VS3000 IC                    | 64 |

|   |       | 3.5.2 I <sup>2</sup> C Host Interface           | 65 |

|   |       | 3.5.3 UART Host Interface                       | 65 |

|   |       | 3.5.4 Logger Port                               | 66 |

|   |       | 3.5.5 Debug Port                                | 66 |

|   |       | 3.5.6 JTAG Interface                            | 66 |

|   |       | 3.5.7 Ethernet Interface                        | 67 |

| 4 | Confi | iguration and Management                        | 68 |

|   | 4.1   | HW Strap Pins                                   | 68 |

|   | 4.2   | SW Strap Pins                                   | 69 |

|   | 4.3   | VS3000 Parameters                               | 71 |

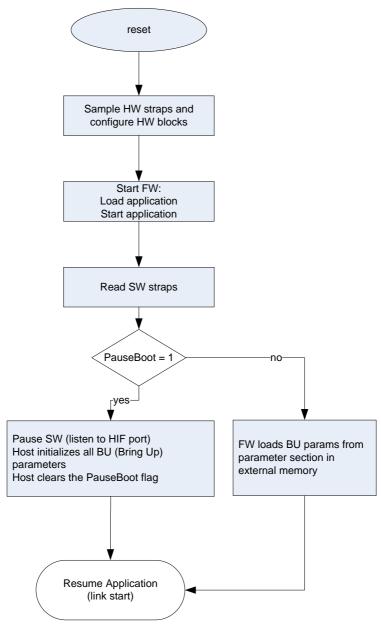

|   |       | 4.3.1 VS3000 Initialization Flow                | 72 |

|   |       | 4.3.2 Parameter List                            | 72 |

|   | 4.4   | GPIO Functionality                              | 72 |

|   |       | 4.4.1 FW LED (pin GPO[0])                       | 73 |

|   |       | 4.4.2 HDBaseT Link LED (pin GPO[1])             | 74 |

|   |       | 4.4.3 Interrupt to Host CPU (pin GPO[2])        | 74 |

|   |       | 4.4.4 HDMI Out LED (pin GPO[3])                 | 74 |

|   |       | 4.4.5 HDMI In LED (pin GPO[4])                  |    |

|   |       | 4.4.6 Device Gender indication LED (pin GPO[5]) | 75 |

| 5 | Elect | rical Specifications                            |    |

|   | 5.1   | Absolute Maximum Rating                         | 76 |

|   | 5.2   | Power Supplies                                  | 76 |

|   |       | 5.2.1 Power Supplies                            | 76 |

|   | 5.3   | Power Consumption Ratings                            | 78  |

|---|-------|------------------------------------------------------|-----|

|   |       | 5.3.1 Tx Power Consumption                           | 78  |

|   |       | 5.3.2 Rx Power Consumption                           | 78  |

|   | 5.4   | Reference Clock Requirements                         | 78  |

|   |       | 5.4.1 CMOS Oscillator Requirements                   | 78  |

|   |       | 5.4.2 Crystal Requirements                           | 79  |

|   | 5.5   | Recommended Operating Conditions                     | 81  |

|   |       | 5.5.1 Electrical Characteristics (DC Specifications) | 81  |

|   |       | 5.5.2 Timing (AC specifications)                     | 85  |

|   | 5.6   | ESD Ratings                                          | 95  |

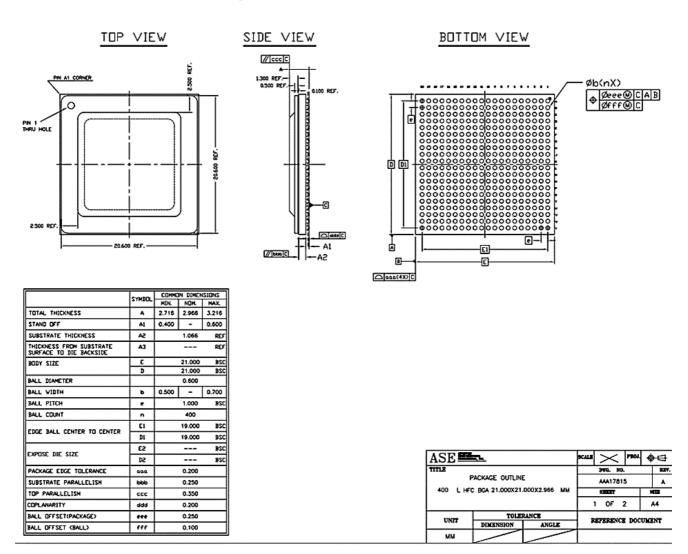

| 6 | Packa | age Mechanical Data                                  | 96  |

|   | 6.1   | VS3000 Package Mechanical Data                       | 96  |

|   | 6.2   | VS3000 Marking Information                           | 97  |

|   | 6.3   | Ordering Codes                                       | 97  |

| 7 | Theri | mal Parameters                                       | 98  |

|   | 7.1   | Terminology                                          | 98  |

|   | 7.2   | Simulation Conditions                                | 98  |

|   | 7.3   | Results Summary                                      | 99  |

| 8 | Quali | ity and Environmental Policy                         | 100 |

# **List of Figures**

| Figure 1: VS3000 Block Diagram                                        | 17 |

|-----------------------------------------------------------------------|----|

| Figure 2: HDMI Extender Application with USB and Ethernet Support     | 20 |

| Figure 3: Daisy-Chain Signage Application                             | 21 |

| Figure 4: Video Wall Multicasting                                     | 22 |

| Figure 5: KVM Extender Application with Ethernet Support              | 23 |

| Figure 6: Audio Extract and Insert HDMI In and HDMI Out               | 24 |

| Figure 7: HDBaseT Technology                                          | 25 |

| Figure 8: VS3000 I/F Signal Block Diagram                             | 28 |

| Figure 9: VS3000 Ball Diagram                                         | 40 |

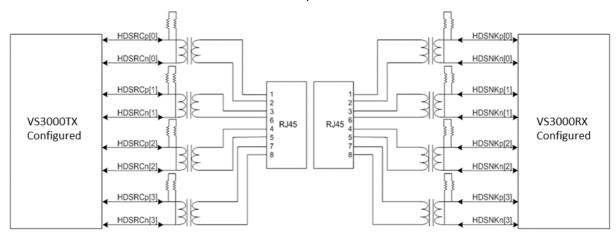

| Figure 10: Link Connection Example                                    | 41 |

| Figure 11: RX and TX Pair Coupling                                    | 42 |

| Figure 12: DHDI Bus Detailed Signals Connectivity                     | 45 |

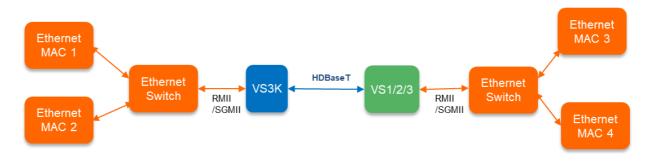

| Figure 13: VS3000 Ethernet Interfaces                                 | 49 |

| Figure 14: VS3000 Ethernet System                                     | 50 |

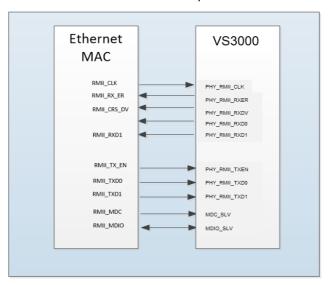

| Figure 15: VS3000 RMII Interface                                      | 50 |

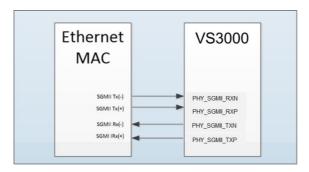

| Figure 16: VS3000 SGMII interface                                     | 51 |

| Figure 17: MDIO Topology                                              | 51 |

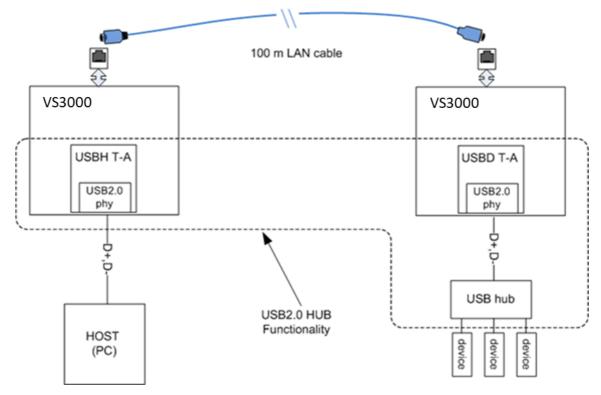

| Figure 18: USB2.0 Extension Over HDBaseT Link                         | 52 |

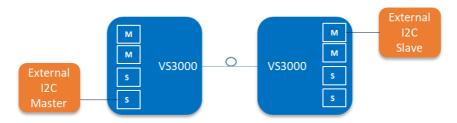

| Figure 19: Valens VS3000 I <sup>2</sup> C T-Adaptors                  | 57 |

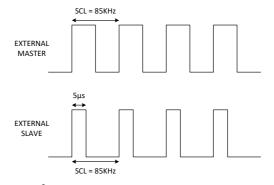

| Figure 20: I <sup>2</sup> C Interface Timing Representation (Example) | 57 |

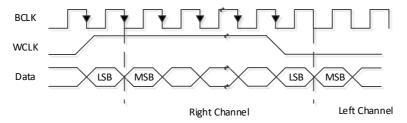

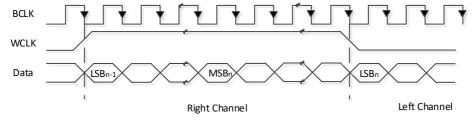

| Figure 21: Delayed-Bit/Standard I <sup>2</sup> S Transport Format     | 59 |

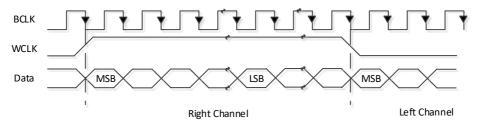

| Figure 22 : Left Justified Transport Format                           | 60 |

| Figure 23: Right Justified Transport Format LSB outside the frame     | 60 |

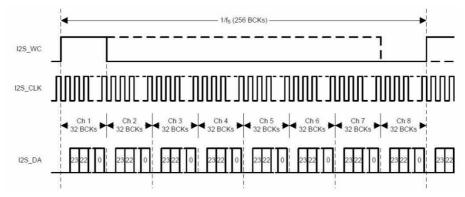

| Figure 24: TDM Mode                                                   | 61 |

| Figure 25: VS3000 Initialization Flow                                 | 72 |

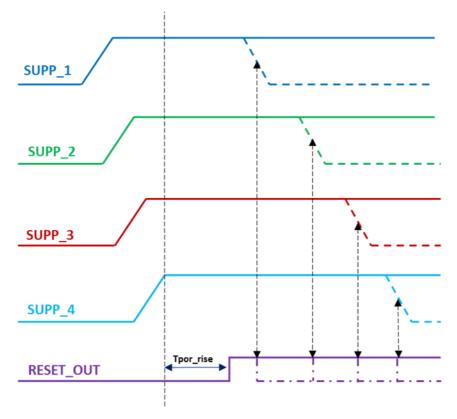

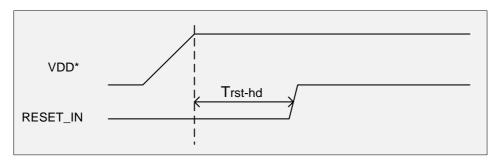

| Figure 26: Internal Power on Reset Timing                             | 80 |

| Figure 27: Reset Signal Timing                                        | 81 |

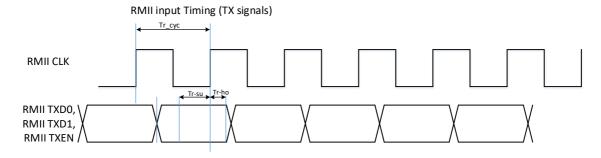

| Figure 28: RMII Timing Diagram                                        | 86 |

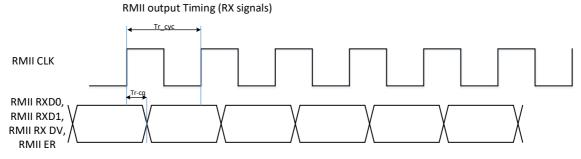

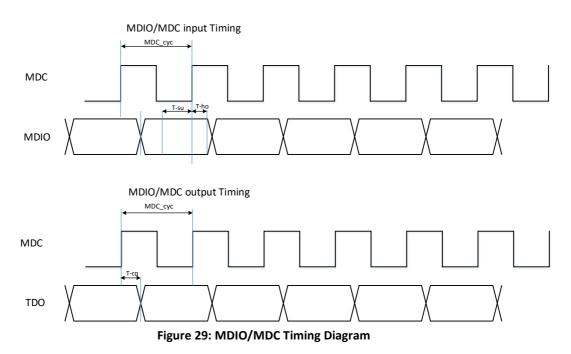

| Figure 29: MDIO/MDC Timing Diagram                                    | 87 |

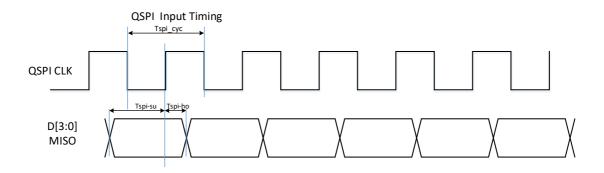

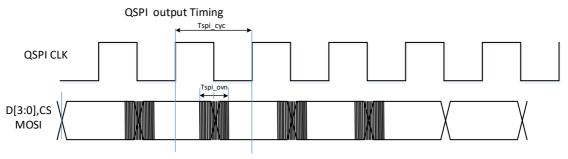

| Figure 30: QSPI Timing Diagram                                        | 88 |

| Figure 31: I <sup>2</sup> C Timing Diagram                            | 90 |

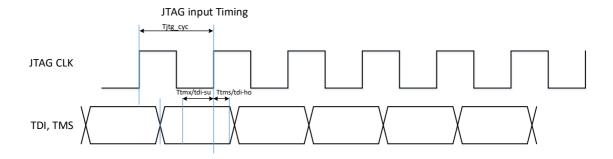

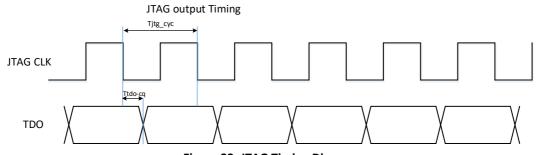

| Figure 32: JTAG Timing Diagram                                        | 91 |

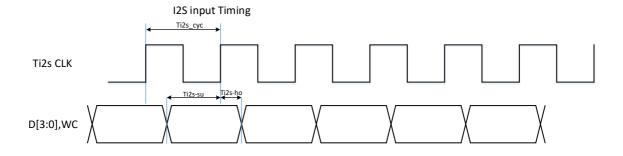

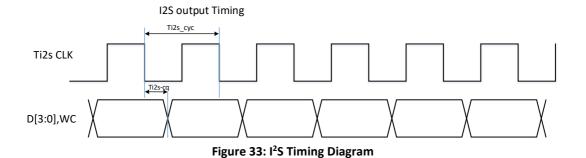

| Figure 33: I <sup>2</sup> S Timing Diagram                            | 92 |

| Figure 34: VS3000 Mechanical Information (all dimensions in mm)       | 96 |

### **List of Tables**

| Table 1: VS3000 CATx Cable Range Specification  | 19 |

|-------------------------------------------------|----|

| Table 2: VS3000 Pin Types                       | 29 |

| Table 3: VS3000 Unused Pin Types                | 29 |

| Table 4: VS3000 Functional Signal Table         | 30 |

| Table 5: VS3000 Non-Functional Signal Table     | 39 |

| Table 6: Reference Resistor Values in VS3000    | 39 |

| Table 7: Operating Mode Events                  | 43 |

| Table 8: Expected USB Performance               | 54 |

| Table 9: UART Pre-configured Parameter Settings | 56 |

| Table 10: UART Oversampled Parameter Settings   | 56 |

| Table 11: PDIF-MSIO Compatibility               | 62 |

| Table 12: MSIO Compatibility with VS2000        | 63 |

| Table 13: SPI default commands parameters       | 63 |

| Table 14: VS3000 HW Strap Pin Description       | 68 |

| Table 15: SW Strap Pin Description              | 69 |

| Table 16: GPIO pins and functionality           | 73 |

| Table 17: VS3000 Absolute Maximum Rating        | 76 |

| Table 18: VS3000 Power Supply                   | 76 |

| Table 19: Tx Power Consumption Ratings          | 78 |

| Table 20: Rx Power Consumption Ratings          | 78 |

| Table 21: CMOS Oscillator Phase Noise Mask      | 79 |

| Table 22: VS3000 Crystal Requirements           | 79 |

| Table 23: Internal Power on Reset Timing        | 80 |

| Table 24: External Power on Reset Timing        | 81 |

| Table 25: VS3000 Electrical Specification       | 81 |

| Table 26: RMII AC Specification                 | 85 |

| Table 27: SGMII AC Specifications               | 86 |

| Table 28: MDC/MDIO AC Specifications            | 86 |

| Table 29: QSPI AC Specifications                | 87 |

| Table 30: I <sup>2</sup> C AC Specifications    | 88 |

| Table 31: UART AC Specifications                | 91 |

| Table 32: JTAG AC Specifications                | 91 |

| Table 33: I <sup>2</sup> S AC Specifications    | 92 |

|                                                 |    |

| Table 35: TMDS AC Specifications            | 93 |

|---------------------------------------------|----|

| Table 36: ESD Ratings                       | 95 |

| Table 37: VS3000 Marking schema per example | 97 |

| Table 38: Ordering Codes                    | 97 |

| Table 39: Thermal Data                      | 99 |

| Table 40: PCB Constructions                 | 99 |

### 1 Introduction

This specification provides a detailed description of the Valens VS3000 ProAV IC. The specification provides essential information required for designing a VS3000 embedded application.

### 1.1 About the **VS3000**

Valens Semiconductor developed the VS3000 to enable high-quality, wired connectivity of a 5Play feature set over a single CATx cable. The 5Play feature set includes:

- Uncompressed high-definition (HD) video content, including HDMI 2.0 traffic

- High-fidelity digital audio

- 1000BaseTX Ethernet

- Various control/data formats including USB2.0, SPDIF and I<sup>2</sup>S audio, I<sup>2</sup>C, RS232 and consumer infrared (CIR).

- Up to 100W of power using PoH (Power over HDBaseT)

The VS3000 is based on HDBaseT<sup>™</sup> technology – which enables simplified, long-distance wired connectivity of uncompressed HD multimedia content, running at 16 Gbps over a single, standard CATx (CAT5e/6/6a/7) cable.

### 1.2 Main Benefits

The main benefits of the Valens VS3000 include:

- 16Gbps on main and 2Gbps on return link, support for uncompressed HDMI2.0 4K/60/4:4:4/8bit

- Port Duality: Each VS3000 IC can be configured as an HDBaseT transmitter (TX) or receiver (RX).

- Concurrent, "HDMI in" and "HDMI out" native interfaces

- Backward compatibility with Valens VS1xx and VS2xxx series ICs.

- Support HDCP2.2 termination and conversion capabilities enhance video content security.

- Support USB 2.0 up to 350Mbps data rate

- 1000Mbps/100Mbps Ethernet interface

- Integrated I2S-4: In and Out ports for High-fidelity digital audio

- Audio Extract and Insert on HDMI In, HDMI Out and HDBaseT

- DHDI Dual High speed digital interface for Multi-Chip interconnection

- Supports multiple ProAV topologies daisy chain, switch matrix, video wall, and redundant HDBaseT ring.

# 1.3 Main Applications

The VS3000 is ideal for the following applications:

- HDMI 2.0 extension over CATx cables

- NxK A/V matrixes

- A/V receivers

- HD projectors

- Industrial PCs

- Single wire TVs and two-box TVs

- KVM (Keyboard, Video, Mouse) extension

- Digital signage displays

- Multi-stream video switching / distribution / aggregation, and daisy chaining

## 1.4 Supported Protocols

The VS3000 uses Valens' T-Adaptor technology to tunnel a wide variety of protocols over an HDBaseT link:

Video: HDMI 2.0, HDCP 2.x/1.4

Audio: I<sup>2</sup>S-4, SPDIF

Ethernet: 1000Mbps/100Mbps over SGMII/RMII

Control: USB, I<sup>2</sup>C, UART, CIR

Multi-chip interconnection: DHDI

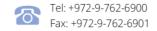

## 1.5 Block Diagram

The figure below is a block diagram illustrating the main functional blocks of the VS3000 IC:

Figure 1: VS3000 Block Diagram

### 1.6 Features

This section contains an in-depth look at the features of the VS3000.

- Port duality: A single VS3000 IC can be configured to operate as either a TX device on the video source side, or an RX device on the video sink side:

- Compliant with HDBaseT 2.0 Specification supporting 5Play™convergence over a single CATx (CAT5e/6/6a) cable.

- Audio, Video, Control, 1Gbps Ethernet, USB 2.0 and Power

- Concurrent HDMI In and HDMI Out Native ports with all its components:

- Fully compliant with HDMI 2.0 (4K 60Hz with 4:4:4 coding) and compatible with HDMI 1.4

- EDID adjustment mechanism for pixel clock higher than 594 MHz

- HDCP 2.x/1.4 compliant

- Audio Extract and Insert function on HDMI ports (future support)

- Glueless interface: directly connectable to all TMDS, DDC, CEC and HPD HDMI signals (TMDS, DDC, CEC, 5V and HPD)

- Ethernet Interface

- Delivers 1000BaseTX Ethernet auxiliary channel alongside the HDBaseT channel in both directions (upstream and downstream)

- Support for E-Adaptor SGMII for 1GbE. SGMII and RMII 100MbE for MAC interfaces (connectable to Phy / Switch)

- USB 2.0 interface

- Configurable either as Host or as a Device USB functionality per HDBaseT standard

- Transfer various control and audio formats over the HDBaseT link including:

- USB 2.0

- High quality audio over I2S-4 standard I/F

- High quality audio over S/PDIF standard I/F

- RS232 for standard UART control protocol

- IR for infra-red control unit

- I2C both slave and master interfaces

- 12 MSIO Pinouts: 6 In and 6 Out general purpose fast serial channels for delivering any proprietary user format

- Coexistence with IEEE802.3af, IEEE802.3at, IEEE802.3bt and PoH

- Backward compatible to HDBaseT 1.0 Specification and legacy HDBaseT products based on VS2000 and VS100 chip set families

- System Interfaces

- UART for external debugger

- I2C slave for External Host interface

- SPI boot Flash Interface

- Ethernet 100Mbps MAC

- 2 x DHDI proprietary digital interface for on-board inter-chip connectivity and applications

- Support for 16Gbps inter-device on-board connectivity

- HDBaseT Packets over inter-chip interconnection for additional flexibility

- Package Dimensions:

- VS3000: HSBGA 21 mm x 21 mm, 400-ball grid (20 x 20)

- Ball pitch 1 mm

- Operational maximum rated junction temperature: minimum 0°C, maximum +125°C

- HDBaseT transmission ranges according to CATx cable type:

- For max HDMI2.0 resolution recommended cable is: CAT6a U/FTP.

- The table indicates the total cable length supported (combination of straight cable and with cable patches).

- Patches used in all cases: 2 X patch cable of 5 meters each. Standard CAT6A, U/FTP,

26AWG.

- For CAT5e/ CAT6 cable a UTP, 24AWG type used

- All cases tested with real traffic—HDMI Video, 1Gbpe and USB2.0.

### Table 1: VS3000 CATx Cable Range Specification

| Cable Type | Mega-characters<br>per second, per<br>channel (Mcsc) | HDBaseT<br>Link Rate | Max Video<br>resolution                  | Range - Typical                                   |

|------------|------------------------------------------------------|----------------------|------------------------------------------|---------------------------------------------------|

| CAT6a      | 450 < Mcsc <= 594                                    | 16Gbps               | 4K/60Hz/4:4:4 video formats              | 100 meters (straight)<br>70 meters (with patches) |

| (U/FTP)    | <=450                                                | 12Gbps               | 4K/60Hz/4:2:0 HDR<br>12bit video formats | 100 meters (with patches)                         |

| CAT5e/CAT6 | 450 < Mcsc <= 594                                    | 16Gbps               | 4K/60Hz/4:4:4 video formats              | 40 meters (straight) 30 meters (with patches)     |

| (UTP)      | <=450                                                | 12Gbps               | 4K/60Hz/4:2:0 HDR<br>12bit video formats | 70 meters (with patches)                          |

### 1.7 Typical Application Examples

### 1.7.1 HDMI Extender Application

Using the VS3000, HDBaseT links can forward uncompressed HDMI 2.0 traffic at rates of up to 16 Gbps, fully supporting 4K/60fps/4:4:4/8bit video.

In the example in Figure 2 below, an HDBaseT link serves as an HDMI/KVM extender.

On the transmitter/source side, a Full HD or Ultra HD HDMI audiovisual source is connected to the HDMI input interface of the VS3000. An Ethernet device connected via the VS3000's SGMII interface, connects the system to the Ethernet network. The PC, acting as a KVM server, connects to the HDBaseT link as a USB2.0 host.

On the receiver/sink side, a monitor, display, or Ethernet-enabled smart-TV device is connected to the HDMI interface of the VS3000 to receive audiovisual content. The device is connected to the home network via the VS3000's SGMII interface. USB2.0 devices, such as a keyboard and mouse, connect to the USB2.0 host over the HDBaseT link.

Infrared control signals transmitted from the sink side are forwarded over the HDBaseT link and are blasted at the source side by the IR blaster.

# 4K/60fps/4:4:4/8bit Sink 4K/60fps/4:4:4/8bit USB HDMI USB 1GbE 16/2Gbps HDBaseT link VS3000 1GbE USB2.0

Figure 2: HDMI Extender Application with USB and Ethernet Support

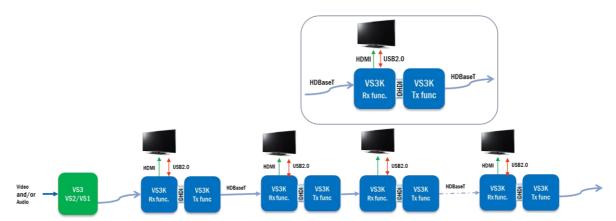

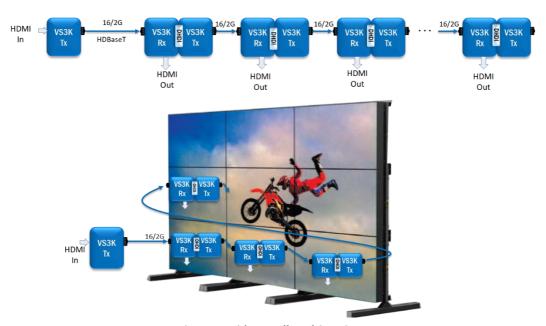

### 1.7.2 Daisy-Chain Applications (future support)

In a daisy chain application, a video/audio source is introduced at the beginning of the chain to a Valens ProAV device. At every node in the chain, the content is forwarded in a drop-and-continue paradigm:

- **Drop**. The content is restored to its native format by the RX-configured VS3000, and displayed in the sink device

- **Continue**. The content remains in HDBaseT format and is forwarded by the RX-configured VS3000 over the DHDI channel to the TX-configured VS3000, where it is forwarded over the next HDBaseT link in the chain.

Each node in the HDBaseT daisy-chain can be placed at a distance of up to 100 meters from the previous node.

The HDBaseT daisy chain forwards uncompressed 4K/60fps/4:4:4/8bit video and provides full HDCP support.

Figure 3: Daisy-Chain Signage Application

### 1.7.3 Video Wall Multicasting (future support)

In video wall applications, a video source is introduced at the beginning of a daisy chain to a Valens V3000 device that is configured as a TX node. The video source transmits unique content for each display in the video wall.

At every node in the chain, the content intended for that node is restored to its native format by the RX-configured VS3000. The rest of the content is forwarded by the RX-configured VS3000 over the DHDI channel to the TX-configured VS3000, where it is transmitted over the next HDBaseT link in the chain for use in other nodes.

Each HDBaseT link supports 16 Gbps of bandwidth for video wall applications.

Figure 4: Video Wall Multicasting

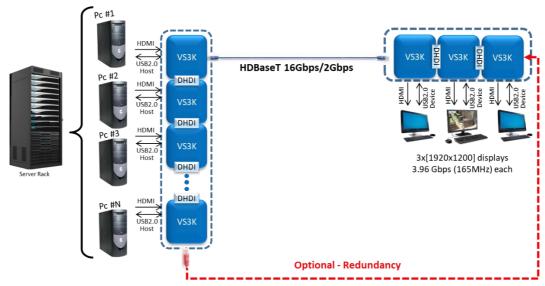

### 1.7.4 KVM Extension/Switching System (future support)

A KVM (keyboard/video/mouse) extension and switching system allows users to access a remotely deployed PC using dedicated peripheral devices installed at a workstation. This setup is excellent for Internet café applications, in which the users have no physical access to computing hardware.

In the example depicted below, three users access remote PC systems over an HDBaseT link supporting asymmetric bandwidth of 16Gbps downstream and 2Gbps upstream.

On the transmitter side, the PCs are connected to a node containing multiple TX-configured VS3000 devices that aggregate traffic using a DHDI link. An Ethernet device is connected via the SGMII interface to connect the system to the Ethernet network.

On the receiver side, a monitor, display, or Ethernet-enabled smart-TV device is connected to the HDMI interface in order to display audiovisual content. The device is connected to the local area network via the SGMII interface. A mouse and keyboard are connected via the USB device interface.

Figure 5: KVM Extender Application with Ethernet Support

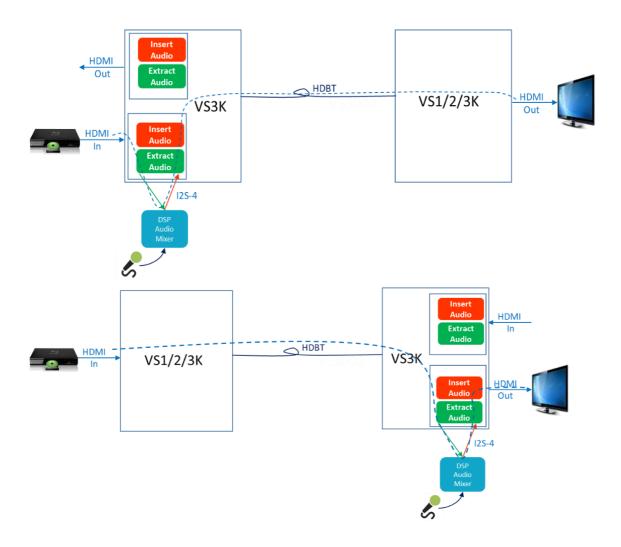

### 1.7.5 Audio Extract and Insert

Audio extraction and insertion functions allow you to extract audio signals in an audiovisual transmission, and insert a replacement signal. These functions are useful when it is necessary to replace an inferior audio signal, or when there is no signal at all.

To implement this feature, a VS3000 IC – either on the source side or the sink side of the HDBaseT link, receives an HDMI source transmission. The extracted audio can be delivered over the VS3000's I<sup>2</sup>S OUT T-adaptor to a DSP processor, which replaces the audio content, and returns the alternate content over the I<sup>2</sup>S IN T-adaptor to the VS3000, where the signal is reconnected to the HDMI transmission and forwarded to the sink device. The extracted Audio can be transmitted over the HDBaseT link to other devices, instead of I<sup>2</sup>S OUT T-adaptor.

Figure 6: Audio Extract and Insert HDMI In and HDMI Out

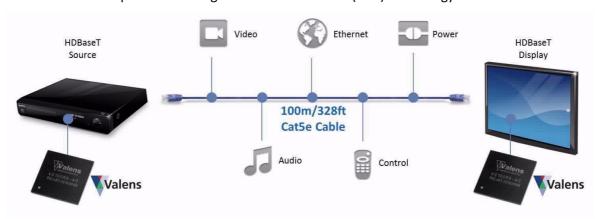

### 1.8 HDBaseT Technology Overview

Valens HDBaseT<sup>™</sup> technology empowers **5Play<sup>™</sup>** digital connectivity between high-definition video sources and remote displays. HDBaseT<sup>™</sup> enables plug-and-play delivery of multimedia traffic over a single 100 meter (328 foot) CATx cable:

- Video Uncompressed high-definition/3D video in up to 4K resolution

- Audio Any standard digital audio format

- Ethernet 100BaseTX Ethernet

- Control Various control signals including USB, CEC, RS-232, and IR

- Power Up to 100W using Power-over-HDBaseT (PoH) technology

Figure 7: HDBaseT Technology

### Video

HDBaseT<sup>™</sup> delivers up to 16 Gbps of bandwidth, supporting transmission of uncompressed HDMI2.0 4K/60/444/8bit video – to a network of devices, or over a point-to-point connection. HDBaseT<sup>™</sup> provides a transparent transport mechanism for HDMI traffic, thus supporting all key features of HDMI 2.0, including HPD, 5V, CEC, EDID and HDCP. Valens' proprietary video coding scheme ensures the highest video quality with zero latency.

### **Audio**

As with video, HDBaseT™ Audio is transparently transported directly from the HDMI device, thus supporting all standard formats, such as Dolby Digital, DTS, Dolby TrueHD, DTS HD-Master Audio and more.

### **Ethernet**

HDBaseT™ supports 1000Mbps or 100Mbps Ethernet capabilities, enabling televisions, hi-fi equipment, computers, and other consumer electronic devices to communicate with each other and access stored multimedia content, including video streaming, images and music.

### **Controls**

HDBaseT<sup>™</sup> delivers a variety of multipurpose control signals, including USB2.0, Consumer Electronic Controls (CEC), RS-232, USB, and infrared. Since HDBaseT<sup>™</sup> also supports an Ethernet channel, IP-based control can be employed as well. This opens up endless possibilities for equipment manufacturers, from remote device control to fully managed networks.

The control plane supports additional bandwidth of up to 250 Mbps for applications requiring extra capacity.

### **Power**

As part of its 5Play™ feature-set, HDBaseT™ supports transmission of up to 100W of DC power over the same CATx cable. Now, you can provide power without requiring access to an electric outlet – enhancing device mobility.

### 1.9 HDBaseT Channel Terminology

The HDBaseT channel consists of two distinct asymmetric unidirectional channels:

- Main Channel Directed downstream from the HDBaseT transmitter to the HDBaseT receiver, carrying uncompressed multimedia content (HDMI, USB, SPDIF, GP MSIO, UART, CIR, I<sup>2</sup>S) as well as the transmitter to receiver portion of the Ethernet data content and multimedia controls.

- Auxiliary Return Channel Directed upstream from the HDBaseT receiver to the HDBaseT transmitter, carrying the return channel controls and the receiver to transmitter portion of the data content.

### 1.10 VS3000 Port duality

The VS3000 IC can be configured (software or hardware) to act as an HDBaseT Transmitter or an HDBaseT Receiver – Port duality. The HDBaseT transmitter connects to the audiovisual source equipment (STBs, Blu-ray / DVD players, etc.) while the HDBaseT receiver connects to the audiovisual sink equipment (monitors, TVs, projectors, etc.). The term 'gender' selection (TX or RX) is used in the data sheet document.

# **2** Pin and Signal Configuration

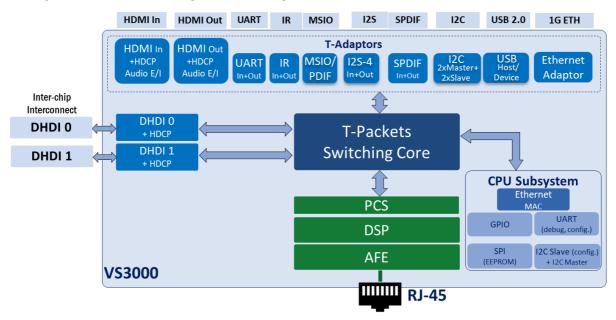

# 2.1 VS3000 Interface Diagram

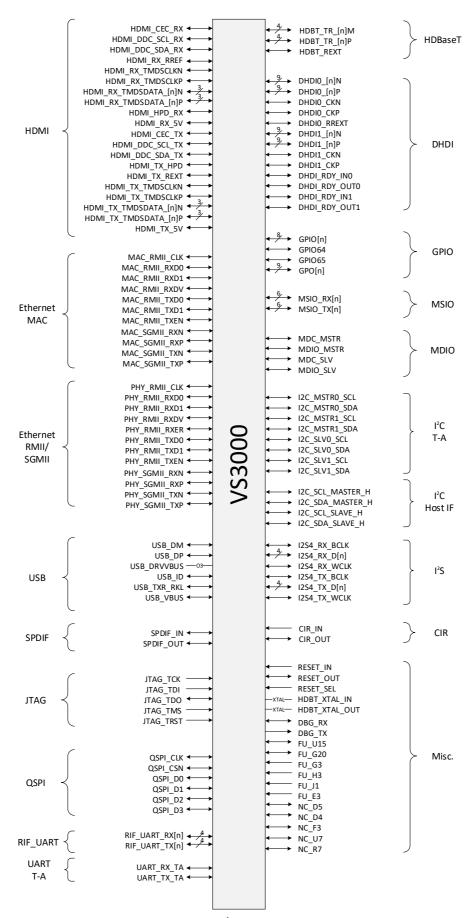

The interface diagram below details various interfaces by signal groups.

Figure 8: VS3000 I/F Signal Block Diagram

### 2.2 Pin Type Convention

### 2.2.1 IO Pad Types

The VS3000 pin types and their descriptions are listed below:

Table 2: VS3000 Pin Types

| Pin Type       | Description                                                     |

|----------------|-----------------------------------------------------------------|

| Input          | Digital input pad                                               |

| Output         | Digital output pad                                              |

| 10             | Bidirectional IO digital pad                                    |

| Input [PU/PD]  | Digital input pad [with integrated pull-up/pull-down resistor]  |

| Output [PU/PD] | Digital output pad [with integrated pull-up/pull-down resistor] |

| IO, PU         | Bidirectional IO digital pad with integrated pull-up resistor   |

| IO, PD         | Bidirectional IO digital pad with integrated pull-down resistor |

| AIO            | Analog bidirectional pad                                        |

| Al             | Analog input pad                                                |

| AO             | Analog output pad                                               |

| 03State        | Digital output pad with tri-state buffer                        |

| XTAL           | Crystal I/O pad                                                 |

### 2.2.2 Unused Pins

If your application does not use one or more interfaces, you should implement the connectivity of the interface's balls according to the *If Not Used* column in Table 4.

The following conventions are used to connect unused pins:

Table 3: VS3000 Unused Pin Types

| Category | Connection Requirement                                |  |  |  |  |  |  |

|----------|-------------------------------------------------------|--|--|--|--|--|--|

| NC       | Safe to leave unconnected (floating)                  |  |  |  |  |  |  |

| GND      | Must be connected to a ground                         |  |  |  |  |  |  |

| 1KPD     | Must be connected to a ground via 1Kohm resistor      |  |  |  |  |  |  |

| 1KPU     | Must be connected to a 1.8V supply via 1Kohm resistor |  |  |  |  |  |  |

# 2.3 VS3000 Signal Description

Table 4 below provides information on each pin of the VS3000 chip. Pins with more than one function use the following convention:

- F1: <function 1 description>

- F2: <function 2 description>

- ST: <strap function description>

Selecting between functions of multi-functional pins is performed by either using VS3000 chip parameters or asserting strap pins. For more details, refer to the section in Chapter 4 that corresponds with the relevant interface category.

# 2.3.1 Functional Signals

**Table 4: VS3000 Functional Signal Table**

| Signal Name     | Ball# | Pad<br>Type | Reset<br>State    | I/F<br>category | If Not<br>Used             | Functional Description                                                         |

|-----------------|-------|-------------|-------------------|-----------------|----------------------------|--------------------------------------------------------------------------------|

| HDMI_CEC_RX     | T15   | Ю           | PU, Input         | CEC             | NC                         | HDMI RX – CEC                                                                  |

| HDMI_CEC_TX     | T17   | 10          | PU, Input         | CEC             | NC                         | HDMI TX- CEC                                                                   |

| CIR_IN          | L3    | Input       | PD, Input         | CIR             | 4.7KΩ PU<br>to<br>VDDIO_18 | Consumer IR, input. Should connect to a $4.7 \text{K}\Omega$ pull up resistor. |

| CIR_OUT         | L2    | Ю           | PD, Input         | CIR             | 4.7KΩ PU<br>to<br>VDDIO_18 | Consumer IR, output. Should connect to a $4.7 K\Omega$ pull up resistor.       |

| FU_E3           | E3    | Input       | No pull,<br>Input | Reserved        | GND                        | Must be tied to ground                                                         |

| HDMI_DDC_SCL_RX | U14   | Ю           | PU, Input         | DDC I2C         | NC                         | HDMI Rx, display data channel (DDC), clock                                     |

| HDMI_DDC_SCL_TX | U17   | Ю           | PU, Input         | DDC I2C         | NC                         | HDMI Tx, display data channel (DDC), clock                                     |

| HDMI_DDC_SDA_RX | T14   | Ю           | PU, Input         | DDC I2C         | NC                         | HDMI Rx, display data channel (DDC), data                                      |

| HDMI_DDC_SDA_TX | U16   | Ю           | PU, Input         | DDC I2C         | NC                         | HDMI Tx, display data channel (DDC), data                                      |

| NC_D5           | D5    | AIO         | N/A               | Reserved        | NC                         | Reserved                                                                       |

| NC_D4           | D4    | AIO         | N/A               | Reserved        | NC                         | Reserved                                                                       |

| DHDI0_0N        | B1    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 0, (N)                                                         |

| DHDI0_0P        | C1    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 0, (P)                                                         |

| DHDI0_1N        | A2    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 1, (N)                                                         |

| DHDIO_1P        | B2    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 1, (P)                                                         |

| DHDI0_2N        | А3    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 2, (N)                                                         |

| DHDI0_2P        | В3    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 2, (P)                                                         |

| DHDI0_3N        | A4    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 3, (N)                                                         |

| DHDI0_3P        | B4    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 3, (P)                                                         |

| DHDI0_4N        | A6    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 4, (N)                                                         |

| DHDI0_4P        | В6    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 4, (P)                                                         |

| DHDI0_5N        | A7    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 5, (N)                                                         |

| DHDI0_5P        | В7    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 5, (P)                                                         |

| DHDI0_6N        | A8    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 6, (N)                                                         |

| DHDI0_6P        | B8    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 6, (P)                                                         |

| DHDI0_7N        | A9    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 7, (N)                                                         |

| DHDI0_7P        | В9    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 7, (P)                                                         |

| DHDI0_8N        | A10   | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 8, (N)                                                         |

| DHDI0_8P        | B10   | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, channel 8, (P)                                                         |

| DHDI0_CKN       | A5    | AIO         | N/A               | DHDI0           | NC                         | DHDI 0, clock, (N)                                                             |

| Signal Name       | Ball#      | Pad<br>Type | Reset<br>State | I/F<br>category | If Not<br>Used | Functional Description                                                               |

|-------------------|------------|-------------|----------------|-----------------|----------------|--------------------------------------------------------------------------------------|

| DHDI0_CKP         | B5         | AIO         | N/A            | DHDI0           | NC             | DHDI 0, clock, (P)                                                                   |

| DHDIO RREXT       | E6         | AIO         | N/A            | DHDIO_RRE<br>XT | 1KΩ PD         | DHDI bias external resistor, Should be tied to a $1K\Omega$ (1%) pull down resistor. |

| DHDI1 ON          | B20        | AIO         | N/A            | DHDI1           | NC NC          | DHDI 1, channel 0, (N)                                                               |

| DHDI1_0P          | C20        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 0, (P)                                                               |

| DHDI1_IN          | A19        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 1, (N)                                                               |

| DHDI1_1P          | B19        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 1, (P)                                                               |

| DHDI1_2N          | A18        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 2, (N)                                                               |

| DHDI1_2P          | B18        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 2, (P)                                                               |

| DHDI1_3N          | A17        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 3, (N)                                                               |

| DHDI1_3P          | B17        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 3, (P)                                                               |

| _                 | A15        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 4, (N)                                                               |

| DHDI1_4N DHDI1_4P | B15        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 4, (P)                                                               |

|                   | A14        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 5, (N)                                                               |

| DHDI1_5N          | B14        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 5, (N)                                                               |

| DHDI1_5P          | A13        | AIO         | N/A            | DHDI1           | NC<br>NC       |                                                                                      |

| DHDI1_6N          | B13        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 6, (N)                                                               |

| DHDI1_6P          | A12        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 6, (P)                                                               |

| DHDI1_7N          | B12        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 7, (N)                                                               |

| DHDI1_7P          | A11        | AIO         | N/A            | DHDI1           | NC<br>NC       | DHDI 1, channel 7, (P)                                                               |

| DHDI1_8N          |            |             |                |                 |                | DHDI 1, channel 8, (N)                                                               |

| DHDI1_8P          | B11        | AIO         | N/A            | DHDI1           | NC             | DHDI 1, channel 8, (P)                                                               |

| DHDI1_CKN         | A16<br>B16 | AIO         | N/A<br>N/A     | DHDI1<br>DHDI1  | NC<br>NC       | DHDI 1, clock, (N)                                                                   |

| DHDI1_CKP  GPIO0  | G4         | IO          | 1              |                 |                | DHDI 1, clock, (P)                                                                   |

|                   |            |             | PU, Input      | GPIO            | NC             | General purpose IO - bit 0                                                           |

| GPIO1             | G5         | 10          | PU, Input      | GPIO            | NC             | General purpose IO - bit 1                                                           |

|                   |            |             |                | GPIO            |                | Interrupt to Host interface CPU reduced I2C stretching                               |

| GPIO2             | H4         | Ю           | PU, Input      |                 | NC             | ST: General purpose IO - bit 2                                                       |

| GPIO3             | H5         | 10          | PU, Input      | GPIO            | NC             | General purpose IO - bit 3                                                           |

| GPIO4             | P1         | 10          | PU, Input      | GPIO            | NC             | General purpose IO - bit 4                                                           |

| GPIO5             | R1         | 10          | PU, Input      | GPIO            | NC             | General purpose IO - bit 5                                                           |

| GPO9/SW_STRAP[15  |            |             |                | GPIO            |                | General purpose Output - bit 9                                                       |

| ]                 | T1         | 10          | PU, Input      |                 | Must use       | ST: MAC SGMII AC/ DC coupling                                                        |

| CDIOCA            |            | 10          | DD Innut       | GPIO            | NC             | Interrupt to Host interface CPU matrix support                                       |

| GPIO64            | F5         | 10          | PD, Input      | CDIC            | NC             | ST: General purpose IO - bit 64                                                      |

| CDIOSE            | 12         | 10          | Dit learns     | GPIO            | NC             | Interrupt to Host interface CPU matrix support                                       |

| GPIO65            | J3         | Ю           | PU, Input      |                 | NC             | ST: General purpose IO - bit 65                                                      |

| Signal Name             | Ball# | Pad<br>Type | Reset<br>State | I/F<br>category | If Not<br>Used | Functional Description                                                   |

|-------------------------|-------|-------------|----------------|-----------------|----------------|--------------------------------------------------------------------------|

|                         |       |             |                | GPIO            |                | Interrupt to Host interface CPU matrix support                           |

| GPIO7                   | T2    | Ю           | PU, Input      |                 | NC             | ST: General purpose IO - bit 7                                           |

| GPO0/STRAP[2]           | M5    | 10          | PD, Input      | GPIO            | Must use       | Firmware LED<br>ST: I2C address - bit 0                                  |

| GPO1/STRAP[3]           | M4    | 10          | PD, Input      | GPIO            | Must use       | HDBT link LED<br>ST: I2C address - bit 1                                 |

| GPO2/STRAP[4]           | M3    | Ю           | PD, Input      | GPIO            | Must use       | Interrupt to Host interface CPU ST: I2C address - bit 2                  |

| GPO3/SW_STRAP[7]        | M2    | 10          | PD, Input      | GPIO            | Must use       | HDMI out status LED ST: MAC SGMII/RMII selection                         |

| GPO4/STRAP[1]           | M1    | 10          | PD, Input      | GPIO            | Must use       | HDMI in status LED<br>ST: Flash SPI 4/3 byte                             |

| GPO5                    | L1    | 10          | PD, Input      | GPIO            | 1-2KΩ<br>PD    | HDBaseT Gender LED                                                       |

| GPO6/STRAP[11]          | K1    | 10          | PD, Input      | GPIO            | Must use       | General purpose output - bit 6 ST: Memory BISR enable                    |

| GPO7/MCLK2/SW_S TRAP[5] | N19   | 10          | PU, Input      | GPIO /I2S       | Must use       | I2S Tx MCLK ST: HDBaseT Gender definition - bit 0                        |

| GPO8/MCLK1/SW_S TRAP[9] | M20   | 10          | PU, Input      | GPIO /I2S       | Must use       | I2S Rx MCLK<br>ST: External Flash not Present                            |

| HDBT_TR_OM              | Y3    | AIO         | N/A            | HDBT            | NC NC          | HDBaseT Transceiver Channel 0, (N)                                       |

| HDBT TR OP              | W3    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 0, (P)                                       |

| HDBT_TR_1M              | Y5    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 1, (N)                                       |

| HDBT_TR_1P              | W5    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 1, (P)                                       |

| HDBT_TR_2M              | Y7    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 2, (N)                                       |

| HDBT_TR_2P              | W7    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 2, (P)                                       |

| HDBT_TR_3M              | Y9    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 3, (N)                                       |

| HDBT_TR_3P              | W9    | AIO         | N/A            | HDBT            | NC             | HDBaseT Transceiver Channel 3, (P)                                       |

| NC_U7                   | U7    | AIO         | N/A            | Reserved        | NC             | Reserved                                                                 |

| NC_R7                   | R7    | AIO         | N/A            | Reserved        | NC             | Reserved                                                                 |

| HDBT REXT               | Т8    | AIO         | N/A            | HDBT            | 4.12KΩ<br>PD   | HDBT current Source Resistor, Should be tied to a $4.12K\Omega$ (1%) PD. |

| HDBT XTAL IN            | W1    | XTAL        | N/A            | XTAL            | Must use       | 25MHz oscillator or crystal input                                        |

| HDBT_XTAL_IN            | V1    | XTAL        | N/A            | XTAL            | NC NC          | 25MHz crystal output                                                     |

| HDMI_RX_RREF            | R11   | AIO         | N/A            | HDMI_RX         | 1.62KΩ<br>PD   | HDMI Rx external reference resistor, Should be tied to a 1.62KΩ (1%) PD. |

| HDMI_RX_TMDSCLK         | Y11   | AIO         | N/A            | HDMI_RX         | NC NC          | HDMI Rx, TMDS differential line clock, Receive, (N)                      |

| HDMI_RX_TMDSCLK         | W11   | AIO         | N/A            | HDMI_RX         | NC             | HDMI Rx, TMDS differential line clock, Receive, (P)                      |

| Signal Name             | Ball#  | Pad<br>Type | Reset<br>State | I/F<br>category | If Not<br>Used | Functional Description                                           |

|-------------------------|--------|-------------|----------------|-----------------|----------------|------------------------------------------------------------------|

| HDMI_RX_TMDSDAT         |        |             |                | HDMI_RX         |                | HDMI Rx, TMDS differential line data,                            |

| A_0N                    | Y12    | AIO         | N/A            |                 | NC             | Receive, channel 0, (N)                                          |

| HDMI_RX_TMDSDAT         |        |             |                | HDMI_RX         |                | HDMI Rx, TMDS differential line data,                            |

| A_1N                    | Y14    | AIO         | N/A            |                 | NC             | Receive, channel 1, (N)                                          |

| HDMI_RX_TMDSDAT         | V4F    | 410         | N1/A           | HDMI_RX         | NC             | HDMI Rx, TMDS differential line data,                            |

| A_2N                    | Y15    | AIO         | N/A            | LIBAU DV        | NC             | Receive, channel 2, (N)                                          |

| HDMI_RX_TMDSDAT<br>A_0P | W12    | AIO         | N/A            | HDMI_RX         | NC             | HDMI Rx, TMDS differential line data,<br>Receive, channel 0, (P) |

| HDMI RX TMDSDAT         |        |             |                | HDMI RX         |                | HDMI Rx, TMDS differential line data,                            |

| A_1P                    | W14    | AIO         | N/A            | _               | NC             | Receive, channel 1, (P)                                          |

| HDMI_RX_TMDSDAT         |        |             |                | HDMI_RX         |                | HDMI Rx, TMDS differential line data,                            |

| A_2P                    | W15    | AIO         | N/A            |                 | NC             | Receive, channel 2, (P)                                          |

| HDMI_TX_HPD*            | R15    | AIO         | N/A            | HDMI_TX         | NC             | HDMI Tx, hot plug detect, 5V signal                              |

|                         |        |             |                | TX_REXT         | 1.62ΚΩ         | HDMI Tx external reference resistor,                             |