# 11-Port Layer-2 GbE SGMII Enterprise Ethernet Switch with VeriTime

# INTRODUCTION

This document consists of descriptions and specifications for both functional and physical aspects of the VSC7420-02, VSC7421-02, and VSC7422-02 devices. It is intended for system designers and software developers.

In addition to the datasheet, Microchip maintains an extensive part-specific library of support and collateral materials that you may find useful in developing your own product. Depending upon the Microchip device, this library may include:

- Application notes that provide detailed descriptions of the use of the particular Microchip product to solve realworld problems

- White papers published by industry experts that provide ancillary and background information useful in developing products that take full advantage of Microchip product designs and capabilities

- · User guides that describe specific techniques for interfacing to the particular Microchip products

- Reference designs showing the Microchip device built in to applications in ways intended to exploit its relative strengths

- · Software Development Kits with sample commands and scripts

- Presentations highlighting the operational features and specifications of the devices to assist in developing your own product road map

- Input/Output Buffer Information specification (IBIS) models to help you create and support the interfaces available on the particular Microchip product

Visit and register as a user on the Microchip Web site to keep abreast of the latest innovations from research and development teams and the most current product and application documentation. The address of the Microchip website is www.Microchip.com.

# **Register Notation**

This datasheet uses the following general register notation:

<TARGET>:<REGISTER\_GROUP>:<REGISTER>.<FIELD>

<REGISTER\_GROUP> is not always present. In that case, the following notation is used:

<TARGET>::<REGISTER>.<FIELD>

When a register group does exist, it is always prepended with a target in the notation.

In sections where only one register is discussed, or the target (and register group) is known from the context, the <TAR-GET>:<REGISTER\_GROUP>: may be omitted for brevity, and uses the following notation:

<REGISTER>.<FIELD>

Also, when a register contains only one field, the .<FIELD> is not included in the notation.

#### **Standard References**

This document uses the following industry references.

| Document                  | Title                                | Revision |

|---------------------------|--------------------------------------|----------|

| IEEE                      |                                      |          |

| IEEE <sup>®</sup> 802.1ad | 802.1Q Amendment 4: Provider Bridges | -2005    |

| IEEE 802.1D               | Media Access Control (MAC) Bridges   | -2004    |

| IEEE 802.1Q               | Virtual Bridged Local Area Networks  | -2005    |

#### TABLE 1: REFERENCED DOCUMENTS

# TABLE 1: REFERENCED DOCUMENTS (CONTINUED)

| IEEE 802.3   | Local and metropolitan area networks — Specific requirements<br>Carrier sense multiple access with collision detection (CSMA/<br>CD) access method and physical layer specifications                                                                                                                                                                                                                                                  | -2008              |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| IEEE 802.3az | Standard for Information Technology - Telecommunications and<br>Information Exchange Between Systems - Local and Metropoli-<br>tan Area Networks - Specific Requirements Part 3: Carrier<br>Sense Multiple Access with Collision Detection (CSMA/CD)<br>Access Method and Physical Layer Specifications - Amend-<br>ment: Media Access Control Parameters, Physical Layers and<br>Management Parameters for Energy-Efficient Ethernet | -2010              |

| IETF         |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

| RFC-2236     | Internet Group Management Protocol, Version 2 (IGMPv2)                                                                                                                                                                                                                                                                                                                                                                                | November 1997      |

| RFC-2710     | Multicast Listener Discovery for IPv6 (MLDv1)                                                                                                                                                                                                                                                                                                                                                                                         | October 1999       |

| RFC-2819     | Remote Network Monitoring (RMON) MIB                                                                                                                                                                                                                                                                                                                                                                                                  | May 2000           |

| RFC-2863     | The Interfaces Group MIB                                                                                                                                                                                                                                                                                                                                                                                                              | June 2000          |

| RFC-3635     | Definitions of Managed Objects for Ethernet-like Interface<br>Types                                                                                                                                                                                                                                                                                                                                                                   | September 200<br>3 |

| Other        |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |

| ENG-46158    | Cisco Serial GMII (SGMII) Specification                                                                                                                                                                                                                                                                                                                                                                                               | 1.7                |

| EDCS-540123  | Cisco QSGMII Specification                                                                                                                                                                                                                                                                                                                                                                                                            | 1.3                |

# Terms and Abbreviations

The following terms and abbreviations are used throughout this document.

# TABLE 2: TERMS AND ABBREVIATIONS

| Term            | Explanation                                                                               |

|-----------------|-------------------------------------------------------------------------------------------|

| DEI             | IEEE Drop Eligible Indicator.                                                             |

| PB              | IEEE 802.1AD Provider Bridging (also known as "Q-in-Q").                                  |

| PCP             | IEEE Priority Code Point interpretation of Ethernet Priority (also known as 802.1p) bits. |

| VID             | IEEE VLAN Identifier.                                                                     |

| Classified VLAN | The final VLAN ID classification of a frame used in the forwarding process.               |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# Contents

| Intro | duction                                                                                         |      |

|-------|-------------------------------------------------------------------------------------------------|------|

| 1.0   | Product Overview                                                                                |      |

|       | 1.1 General Features                                                                            |      |

|       | 1.2 Applications                                                                                | 7    |

|       | 1.3 Related Products                                                                            | 7    |

|       | 1.4 Functional Overview                                                                         | 7    |

| 2.0   | Functional Descriptions                                                                         |      |

|       | 2.1 Port Modules                                                                                | . 13 |

|       | 2.2 SERDES6G                                                                                    |      |

|       | 2.3 Copper Transceivers                                                                         |      |

|       | 2.4 Statistics                                                                                  |      |

|       | 2.5 Classifier                                                                                  |      |

|       | 2.6 Analyzer                                                                                    |      |

|       | 2.7 Policers and Ingress Shapers                                                                |      |

|       | 2.8 Shared Queue System                                                                         |      |

|       | 2.9 Scheduler and Shaper                                                                        |      |

|       | 2.10Rewriter                                                                                    |      |

|       | 2.11CPU Port Module                                                                             |      |

| ~ ~   | 2.12Clocking and Reset                                                                          |      |

| 3.0   | VCore-le System and CPU Interface                                                               |      |

|       | 3.1 VCore-le Configurations                                                                     |      |

|       | 3.2 Clocking and Reset                                                                          |      |

|       | 3.3 Shared Bus                                                                                  |      |

|       | 3.4 VCore-le CPU                                                                                |      |

|       | <ul> <li>3.5 Manual Frame Injection and Extraction</li> <li>3.6 External CPU Support</li> </ul> |      |

|       | 3.7 VCore-le System Peripherals                                                                 |      |

| 10    | Features                                                                                        |      |

| 4.0   | 4.1 Port Mapping                                                                                |      |

|       | 4.2 Switch Control                                                                              |      |

|       | 4.3 Port Module Control                                                                         |      |

|       | 4.4 Layer-2 Switch                                                                              |      |

|       | 4.5 IGMP and MLD Snooping                                                                       |      |

|       | 4.6 Quality of Service (QoS)                                                                    |      |

|       | 4.7 CPU Extraction and Injection                                                                |      |

|       | 4.8 Energy Efficient Ethernet                                                                   |      |

| 5.0   | Registers                                                                                       |      |

|       | 5.1 Targets and Base Addresses                                                                  |      |

|       | 5.2 DEVCPU_ORG                                                                                  |      |

|       | 5.3 SYS                                                                                         |      |

|       | 5.4 ANA                                                                                         | 182  |

|       | 5.5 REW                                                                                         | 207  |

|       | 5.6 DEVCPU_GCB                                                                                  | 210  |

|       | 5.7 DEVCPU_QS                                                                                   | 240  |

|       | 5.8 HSIO                                                                                        | 247  |

|       | 5.9 DEV_GMII                                                                                    |      |

|       | 5.10DEV                                                                                         | 265  |

|       | 5.11ICPU_CFG                                                                                    | 285  |

|       | 5.12UART                                                                                        |      |

|       | 5.13TWI                                                                                         |      |

|       | 5.14PHY                                                                                         |      |

| 6.0   | Electrical Specifications                                                                       |      |

|       | 6.1 DC Characteristics                                                                          |      |

|       | 6.2 AC Characteristics                                                                          |      |

|       | 6.3 Current and Power Consumption                                                               | 405  |

| 6.4 Operating Conditions                      | 407 |

|-----------------------------------------------|-----|

| 6.5 Stress Ratings                            |     |

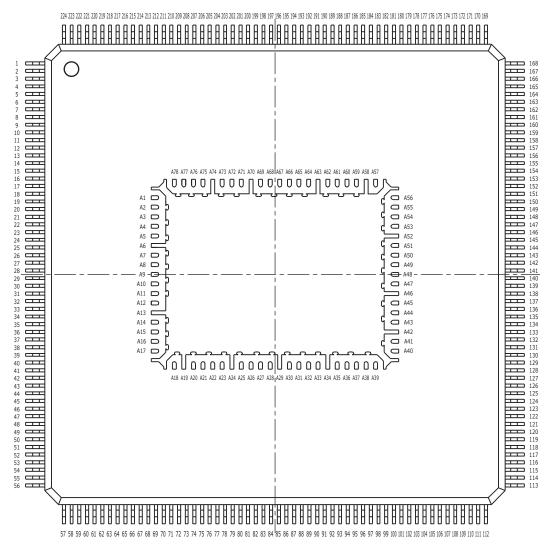

| 7.0 Pin Descriptions for VSC7420XJQ-02        |     |

| 7.1 Pin Diagram for VSC7420XJQ-02             |     |

| 7.2 Pins by Function for VSC7420XJQ-02        |     |

| 7.3 Pins by Number VSC7420XJQ-02              |     |

| 7.4 Pins by Name VSC7420XJQ-02                |     |

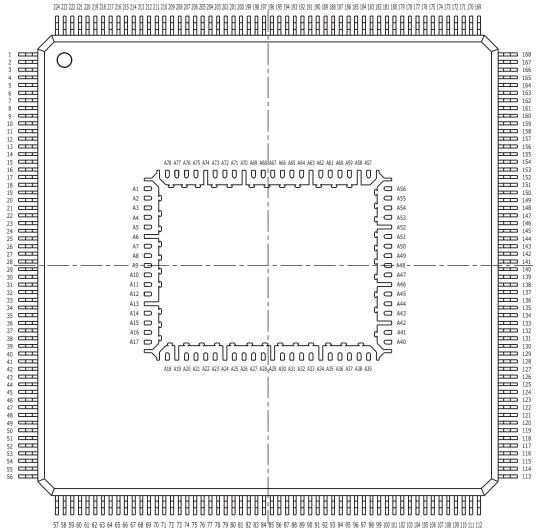

| 8.0 Pin Descriptions for VSC7420XJG-02        |     |

| 8.1 Pin Identifications                       |     |

| 8.2 Pin Diagram                               |     |

| 8.3 Pins by Function for VSC7420XJG-02        |     |

| 9.0 Pin Descriptions for VSC7421XJQ-02        |     |

| 9.1 Pin Diagram for VSC7421XJQ-02             |     |

| 9.2 Pins by Function for VSC7421XJQ-02        |     |

| 9.3 Pins by Number VSC7421XJQ-02              |     |

| 9.4 Pins by Name VSC7421XJQ-02                |     |

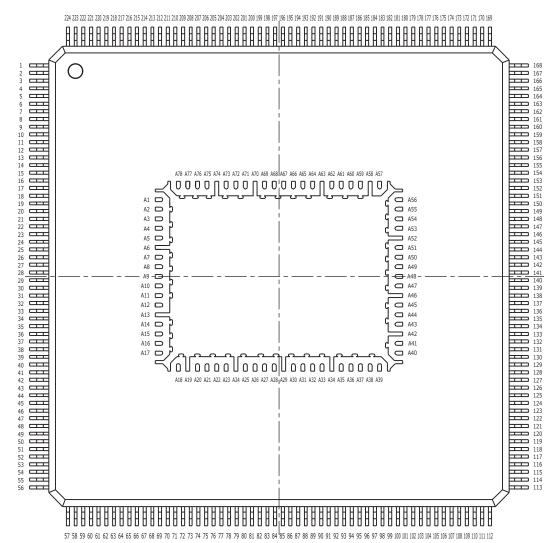

| 10.0 Pin Descriptions for VSC7421XJG-02       |     |

| 10.1Pin Identifications                       |     |

| 10.2Pin Diagram for VSC7421XJG-02             |     |

| 10.3Pins by Function for VSC7421XJG-02        |     |

| 11.0 Pin Descriptions for VSC7422XJQ-02       |     |

| 11.1Pin Diagram for VSC7422XJQ-02             |     |

| 11.2Pins by Function for VSC7422XJQ-02        |     |

| 11.3Pins by Number VSC7422XJQ-02              |     |

| 11.4Pins by Name VSC7422XJQ-02                |     |

| 12.0 Pin Descriptions for VSC7422XJG-02       |     |

| 12.1Pin Identifications                       |     |

| 12.2Pin Diagram for VSC7422XJG-02             |     |

| 12.3Pins by Function for VSC7422XJG-02        |     |

| 13.0 Package Information                      |     |

| 13.1Package Drawing                           |     |

| 13.2Thermal Specifications                    |     |

| 13.3Moisture Sensitivity                      |     |

| 14.0 Design Guidelines                        |     |

| 14.1Power Supplies                            |     |

| 14.2Power Supply Decoupling                   |     |

| 14.3Reference Clock                           |     |

| 14.4 Interfaces                               |     |

| 15.0 Design Consideration                     |     |

| 15.110BASE-T mode unable to re-establish link |     |

| 15.2Software script for link performance      |     |

| 15.310BASE-T signal amplitude                 |     |

| 15.4Clause 45 register 7.60                   |     |

| 15.5Clause 45 register 3.22                   |     |

| 15.6Clause 45 register 3.1                    |     |

| 15.7Clause 45 register address post-increment |     |

| 15.8IEEE1588 Out of Sync Situation            |     |

| 16.0 Ordering Information                     |     |

| Appendix A: Revision History                  |     |

| The Microchip WebSite                         |     |

| Customer Change Notification Service          |     |

| Customer Support                              |     |

# 1.0 PRODUCT OVERVIEW

The SparX-III family of Gigabit Ethernet switches are pin-compatible devices with port counts ranging from 10 Gigabit Ethernet ports to 25 Gigabit Ethernet ports. The switches integrate up to 12 Gigabit copper PHYs and provide both SGMII and quad SGMII (QSGMII) interfaces. Up to two ports can run at 2.5 Gbps.

These devices provide a rich set of Ethernet switching features such as Layer-2 forwarding with basic VLAN and QoS processing enabling delivery of differentiated services. Each product in the family contains an 8051 CPU enabling light management of the switch. Optionally, the switches can be managed from an external CPU using a serial interface.

The SparX-III family contains the following three products:

- VSC7420-02 supports 8× 1G copper PHYs + 2× 2.5G SGMII

- VSC7421-02 supports two major port configurations:

- 12× 1G copper PHY + 2× 1G SGMII + 2× 2.5G SGMII

- 12× 1G copper PHY + 1× 2.5G SGMII + 1× QSGMII

- VSC7422-02 supports 12× 1G copper PHYs + 3× QSGMII + 1× 2.5G SGMII

# 1.1 General Features

- All 1G Ethernet ports are tri-speed 10/100/1000 Mbps ports

- All 2.5G Ethernet ports are quad-speed 10/100/1000/2500 Mbps ports

- Integrated copper transceivers are compliant with IEEE 802.3ab and support Microchip ActiPHY™ link down power savings and PerfectReach™ smart cable reach algorithm

- · SGMII ports support both 100-BASE-FX and 1000-BASE-X-SERDES

- · Four megabits of integrated shared packet memory

- · Fully nonblocking wire-speed switching performance for all frame sizes

- · Eight priorities and eight queues per port

- · Policing per queue and per port

- · DWRR scheduler/shaper per queue and per port with a mix of strict and weighted queues

- · Energy Efficient Ethernet (IEEE 802.3az) is supported by both the switch core and the internal copper PHYs

- · VCore-le CPU system with integrated 8051

#### 1.1.1 LAYER-2 SWITCHING

- 8,192 MAC addresses

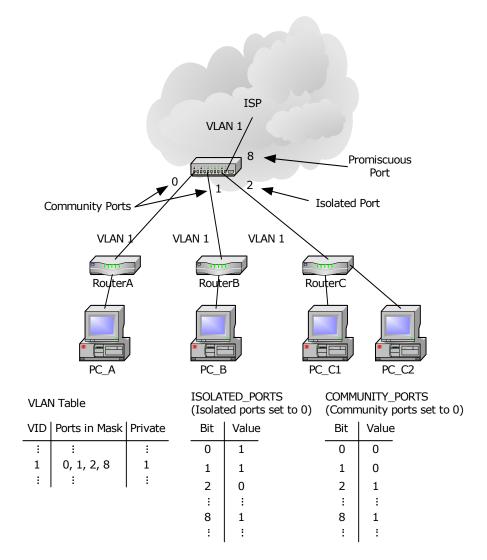

- 4,096 VLANs (IEEE 802.1Q)

- · Push and pop of VLAN tags

- Link aggregation (IEEE 802.3ad)

- Link aggregation traffic distribution is programmable and based on Layer 2 through Layer 4 information

- Wire-speed hardware-based learning and CPU-based learning configurable per port

- · Independent and shared VLAN learning

- Provider Bridging (VLAN Q-in-Q) support (IEEE 802.1ad)

- Rapid Spanning Tree Protocol support (IEEE 802.1w)

- · Jumbo frame support up to 9.6 kilobytes with programmable MTU per port

# 1.1.2 MULTICAST

- 8K L2 multicast group addresses with 64 port masks

- 8K IPv4/IPv6 multicast groups

- Internet Group Management Protocol version 2 (IGMPv2) support

- Multicast Listener Discovery (MLDv1) support

#### 1.1.3 QUALITY OF SERVICE

- · Eight QoS queues per port with strict or deficit weighted round-robin scheduling (DWRR)

- DSCP translation, both ingress and/or egress

- · DSCP remarking based on QoS class

- PCP and DEI remarking based on QoS class

- · Per-queue and per-port policing and shaping, programmable in steps of 100 kbps

- · Full-duplex flow control (IEEE 802.3X) and half-duplex backpressure, symmetric and asymmetric

#### 1.1.4 SECURITY

- · Generic storm controllers for flooded broadcast, flooded multicast, and flooded unicast traffic

- · Selectable CPU queues for segregation of CPU redirected traffic, with 8 queues supported

- Per-port, per-address registration for snooping of reserved IEEE MAC addresses (BPDU, GARP)

- Port-based and MAC-based access control (IEEE 802.1X)

- · Per-port CPU-based learning with option for secure CPU-based learning

- Per-port ingress and egress mirroring

- Mirroring per VLAN

#### 1.1.5 MANAGEMENT

- 8051 CPU system with 64 kilobytes of internal RAM

- CPU frame extraction (eight queues) and injection (two queues), which enables efficient data transfer between Ethernet ports and CPU

- Fourteen pin-shared general-purpose I/Os

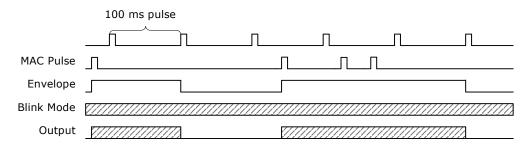

- · Serial LED controller controlling up to 32 ports with four LEDs each

- Serial GPIO controller

- PHY management controller

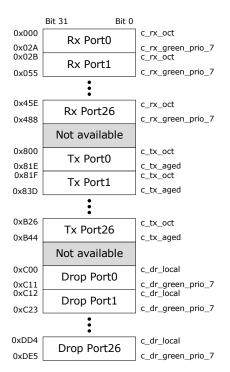

- Per-port 32-bit counter set with support for the RMON statistics group (RFC 2819) and SNMP interfaces group (RFC 2863)

# 1.2 Applications

VSC7420-02, VSC7421-02, and VSC7422-02 target the unmanaged and web-managed Ethernet switch equipment in the SMB.

# 1.3 Related Products

VSC7424-02 SparX-III managed Gigabit Ethernet switch: 10 ports with 8 integrated PHYs and 2 SGMIIs

VSC7425-02 SparX-III managed Gigabit Ethernet switch: 18 ports with 12 integrated PHYs and 6 SGMIIs

VSC7426-02 SparX-III managed Gigabit Ethernet switch: 24 ports with 12 integrated PHYs and 3 QSGMII

VSC7427-02 SparX-III managed Gigabit Ethernet switch: 26 ports with 12 integrated PHYs, 3 QSGMII, and 2 SGMIIs

The VSC7424-02, VSC7425-02, VSC7426-02, and VSC7427-02 family of fully managed Layer-2 Ethernet switches provides comprehensive support for QoS, VLAN, and security. They include advanced classification through the Versatile Contents Aware Processor (VCAP), as well as a CPU system enabled with a 416 MHz MIPS 24KEc<sup>™</sup> CPU.

# 1.4 Functional Overview

This section provides an overview all major blocks and functions involved in the bridging operation in the same order as a frame traverses through the devices. It also outlines other major functionality of the device such as the CPU port module, the CPU system, and CPU interfaces.

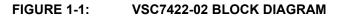

The following illustration shows the block diagram for the VSC7422-02. The other devices in the family have similar block diagrams.

#### 1.4.1 FRAME ARRIVAL

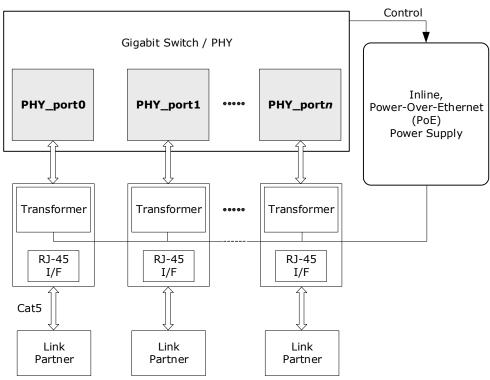

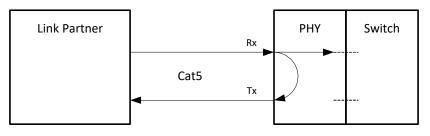

The Ethernet interfaces receive incoming frames and forwasrd these to the port modules. Supported interfaces include copper transceivers, QSGMII, SGMII, and SerDes.

The integrated low-power copper transceivers support full duplex operation at 10/100/1000 Mbps and half-duplex operation at 10/100 Mbps. The key PHY features are:

- Low power consumption in all modes through ActiPHY™ link down power savings, PerfectReach™ smart cable reach algorithm, and IEEE 802.3az Energy Efficient Ethernet idle power savings.

- VeriPHY<sup>®</sup> cable diagnostics suite provides extensive network cable operating conditions and status.

The device features a serial LED controller interface for driving LED pins on both internal and external PHYs.

The 1G SGMII and 2.5G SGMII ports support both 100BASE-X and 1000BASE-X-SERDES.

Each port module contains a Media Access Controller (MAC) that performs a full suite of checks, such as VLAN Tagaware frame size checking, frame check sequence (FCS) checking, and pause frame identification.

Each port module connecting to a SerDes macro contains a Physical Coding Sublayer (PCS) which perform 8 bits/ 10 bits encoding, auto-negotiation of link speed and duplex mode, and monitoring of the link status.

Full-duplex is supported for all speeds, and half-duplex is supported for 10 Mbps and 100 Mbps. Symmetric and asymmetric pause flow control are both supported.

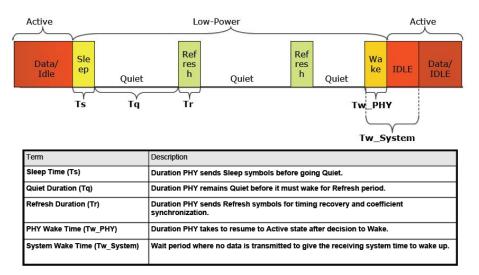

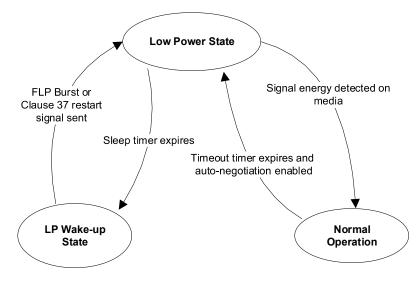

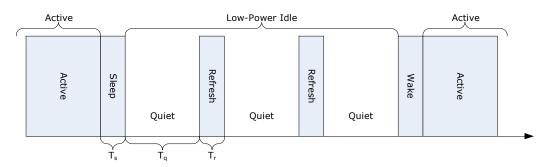

All Ethernet ports support Energy Efficient Ethernet (EEE) according to IEEE 802.3az. The shared queue system is capable of controlling the operating states, active or low-power, of the PCS or the internal PHYs. Both the PCS and PHYs understand the line signaling as required for EEE. This includes signaling of active, sleep, quiet, refresh, and wake.

Each QSGMII port can multiplex four port modules onto one I/O interface. Each of the underlying port modules has its own MAC and PCS and can negotiate link speed and duplex mode independently of the other port modules.

### 1.4.2 FRAME CLASSIFICATION

Each frame is sent to the ingress processing module for classification to a VLAN, classification to a Quality of Service (QoS) class, policing, collecting statistics, security enforcement, and Layer-2 forwarding.

The classification engine can understand up to two VLAN tags and can look for Layer-3 and Layer-4 information behind two VLAN tags. If frames are triple tagged, the higher-layer protocol information is not extracted.

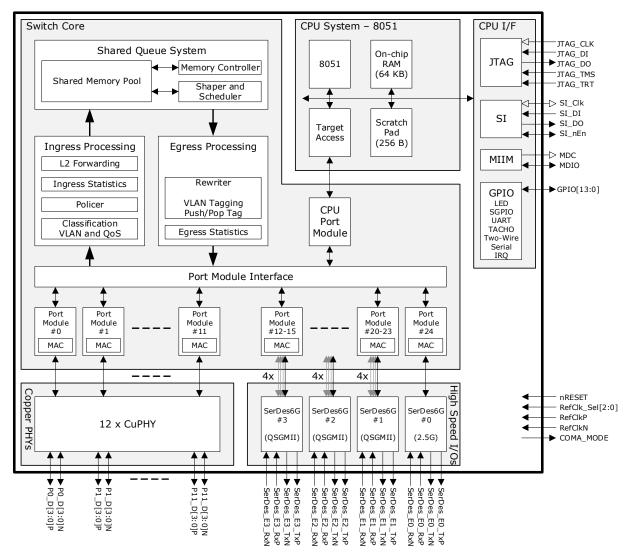

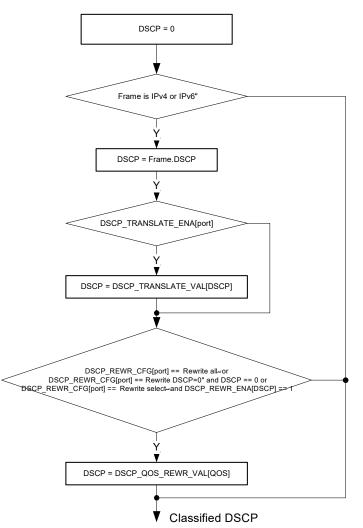

The following illustration shows the frame classification.

#### FIGURE 1-2: FRAME CLASSIFICATION

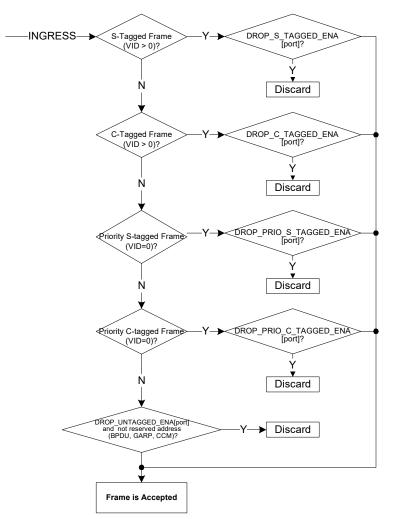

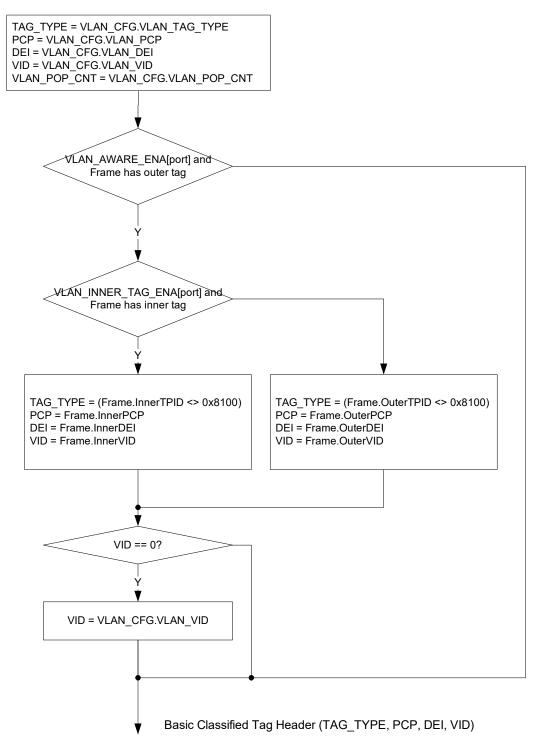

The classification classifies each frame to a VLAN, a QoS class, DSCP value, and an aggregation code. The basic classification also performs a general frame acceptance check.

**Frame Acceptance** The frame acceptance filter checks for valid combinations of VLAN tags against the ingress port's VLAN acceptance filter where it is possible to configure rules for accepting untagged, priority-tagged, C-, and S-tagged frames. In addition, the filter also enables discarding of frames with illegal MAC addresses (for instance null MAC address or multicast source MAC address).

**VLAN** Every incoming frame is classified to a VLAN by the basic VLAN classification. This is based on the VLAN in the frame, or if the frame is untagged or the ingress port is VLAN unaware, it is based on the ingress port's default VLAN. A VLAN classification includes the whole TCI (PCP, DEI, and VID) and also the TPID (C-tag or S-tag).

For double-tagged frames, it is selectable whether the inner or the outer tag is used.

The devices can recognize S-tagged frames with the standard TPID (0x88A8) or S-tagged frames using a custom programmable value. One custom value is supported by the devices.

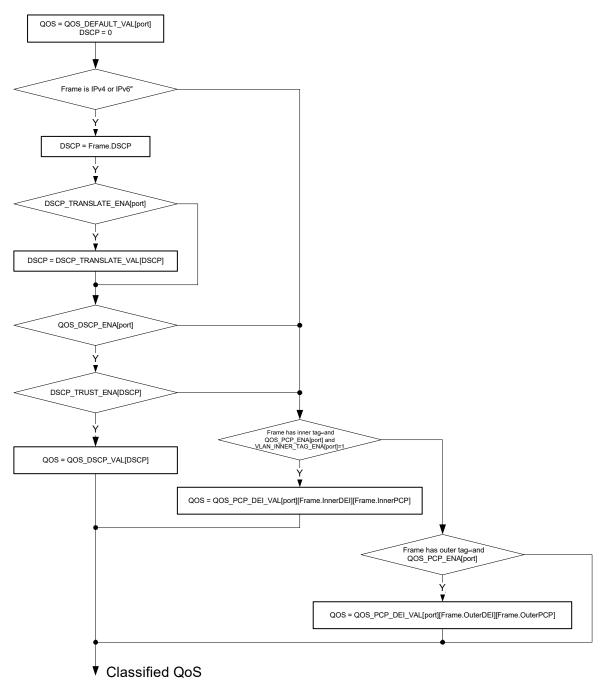

**QoS and DSCP** Each frame is classified to a Quality of Service (QoS) class. The QoS class is used throughout the devices for providing queuing, scheduling, and congestion control guarantees to the frame according to what is configured for that specific QoS class.

The QoS class is assigned based on the class of service information in the frame's VLAN tags (PCP and DEI) and/or the DSCP values from the IP header. Both IPv4 and IPv6 are supported. If the frame is non-IP or untagged, the port's default QoS class is used.

The DSCP values can be remapped before being used for QoS. This is done using a common table mapping the incoming DSCP to a new value. Remapping is enabled per port. In addition, for each DSCP value, it is possible to specify whether the value is trusted for QoS purposes.

Each IP frame is also classified to an internal DSCP value. By default, this value is taken from the IP header but it may be remapped using the common DSCP mapping table or rewritten based on the assigned QoS class. The classified DSCP value may be written into the frame at egress – this is programmable in the rewriter.

**Aggregation Code** Finally, the basic classification calculates an aggregation code, which is used to select between ports that are member of a link aggregation group. The aggregation code is based on selected Layer-2 through Layer-4 information, such as MAC addresses, IP addresses, IPv6 flow label, and TCP/UDP port numbers. The aggregation code ensures that frames belonging to the same conversation are using the same physical ports in a link aggregation group.

# 1.4.3 POLICING

Each frame is subject to a number of different policing operations. The devices feature per queue and per port programmable policers. It is programmable per port whether to use the port policer and the queue policers. It is also programmable whether the policers are working in serial or in parallel.

Each frame is counted in associated statistics reflecting the ingress port and the QoS class. The statistics can count bytes or frames.

Finally, the analyzer contains a group of storm control policers that are capable of policing various kinds of flooding traffic as well as CPU directed learn traffic. These policers are global policers working on all frames received by the switch.

All policers can measure frame rates or bit rates.

#### 1.4.4 LAYER-2 FORWARDING

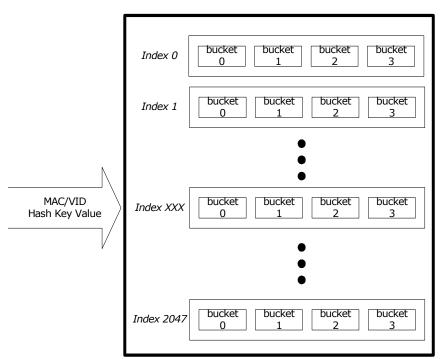

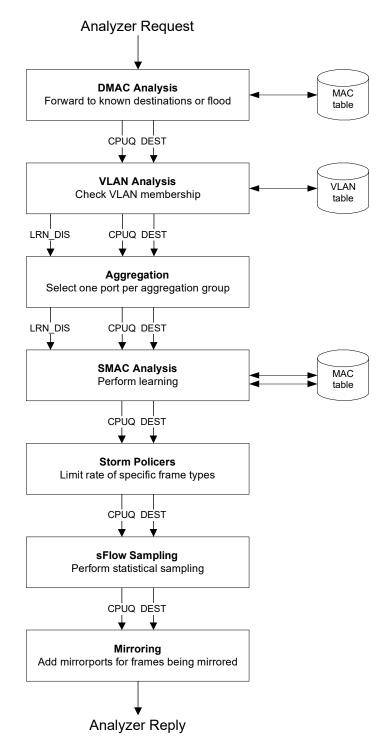

After the policers, the Layer-2 forwarding block (the analyzer) handles all fundamental bridging operations and maintains the associated MAC table, the VLAN table, and the aggregation table. The devices implement an 8K MAC table and a 4K VLAN table.

The main task of the analyzer is to determine the destination port set of each frame. This forwarding decision is based on various information such as the frame's ingress port, source MAC address, destination MAC address, and the VLAN identifier, as well as mirroring, and the destination port's link aggregation configuration.

The switch performs Layer-2 forwarding of frames. For unicast and Layer-2 multicast frames, this means forwarding based on the destination MAC address and the VLAN. For IPv4 multicast frames, the switch performs Layer-2 forward-ing, but based on Layer-3 information.

The following describes some of the contributions to the Layer-2 forwarding:

- VLAN classification VLAN-based forward filtering include source port filtering, destination port filtering, VLAN mirroring, asymmetric VLANs, and so on.

- MAC addresses Destination and source MAC address lookups in the MAC table determine if a frame is a learn frame, a flood frame, a multicast frame, or a unicast frame.

- Learning By default, the devices perform wire-speed learning on all ports. However, certain ports could be configured with secure learning enabled, where an incoming frame with unknown source MAC address is classified as a "learn frame" and is redirected to the CPU. The CPU performs the learning decision and also decides whether the frame is forwarded.

Learning can also be disabled. In that case, it does not matter if the source MAC address is in the MAC table.

- Link aggregation A frame targeted at a link aggregate is further processed to determine which of the link aggregate group ports the frame must be forwarded to.

- Mirroring Mirror probes may be set up in different places in the forwarding path for monitoring purposes. As part of a mirror a copy of the frame is sent either to the CPU or to another port.

# 1.4.5 SHARED QUEUE SYSTEM AND EGRESS SCHEDULER

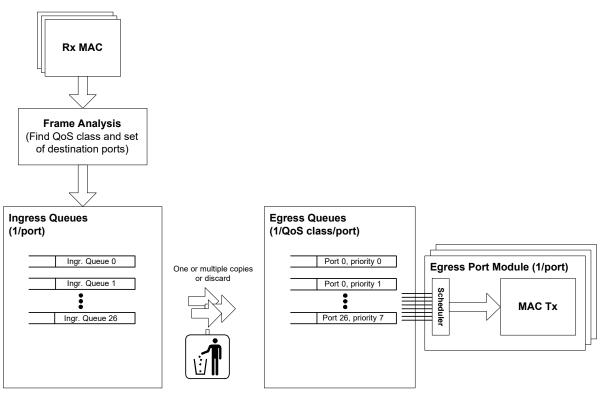

The analyzer provides the destination port set of a frame to the shared queue system. It is the queue system's task to control the frame forwarding to all destination ports.

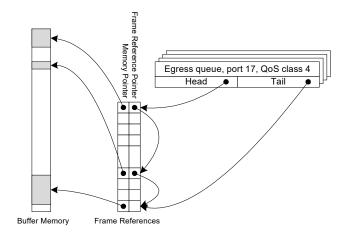

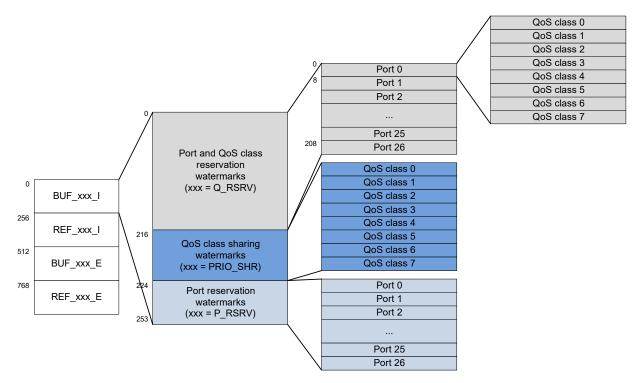

The shared queue system embeds 4Mbits of memory that can be shared between all queues and ports. The queue system implements egress queues per priority per ingress port. The sharing of resources between queues and ports is controlled by an extensive set of thresholds.

The overall frame latency through the switch is low due to the shared queue system only storing the frame once.

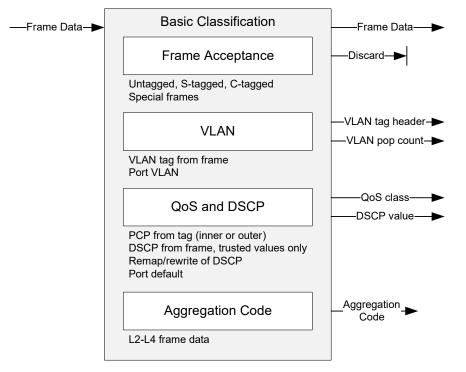

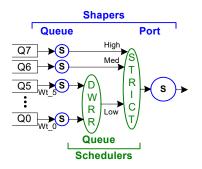

Each egress port implements a scheduler and shapers as shown in the following illustration. Per egress port, the scheduler sees the outcome of aggregating the egress queues (one per ingress port per Qos class) into eight queues, one queue per QoS class. The aggregation is done in a round-robin fashion per QoS class serving all ingress ports equally.

# FIGURE 1-3: EGRESS SCHEDULER AND SHAPER

When transmitting frames from the shared queue system out on an egress port, frames are scheduled within the port using one of two methods:

- Strict priority frames with the highest priority are always transmitted before frames with lower priority.

- Deficit Weighted Round Robin (DWRR) queues 6 and 7 are always strict, and queues 0 through 5 are weighted. Each queue sets a weight ranging from 0 to 31.

In addition, each egress port implements shapers, one per egress queue and one per port.

#### 1.4.6 REWRITER AND FRAME DEPARTURE

Before transmitting the frame on the egress line, the rewriter can modify selected fields in the frame, such as VLAN tags, DSCP value, and FCS.

The rewriter controls the final VLAN tagging of frames based on the classified VLAN, the VLAN pop count, and egressdetermined VLAN actions. The egress VLAN actions are by default given by the egress port settings. These include normal VLAN operations such as pushing a VLAN tag, untagging for specific VLANs, and simple translations of DEI and PCP.

The PCP and DEI bits in the VLAN tag are subject to remarking based on translating the classified tag header or by using the classified QoS value from ingress.

In addition, the DSCP value in IP frames can be updated using the classified DSCP value from ingress. The DSCP value can be remapped at egress before writing it into the frame.

Finally, the rewriter updates the FCS if the frame was modified before the frame is transmitted.

The egress port module controls the flow control exchange of pause frames with a neighboring device when the interconnection link operates in full-duplex flow control mode. When the connected device triggers flow control through transmission of a pause frame, the MAC stops the egress scheduler's forwarding of frames out of the port. Traffic then builds up in the queue system but sufficient queuing is available to ensure wire speed lossless operation.

In half-duplex operation, the port module's egress path responds to back pressure generation from a connected device by collision detection and frame retransmission.

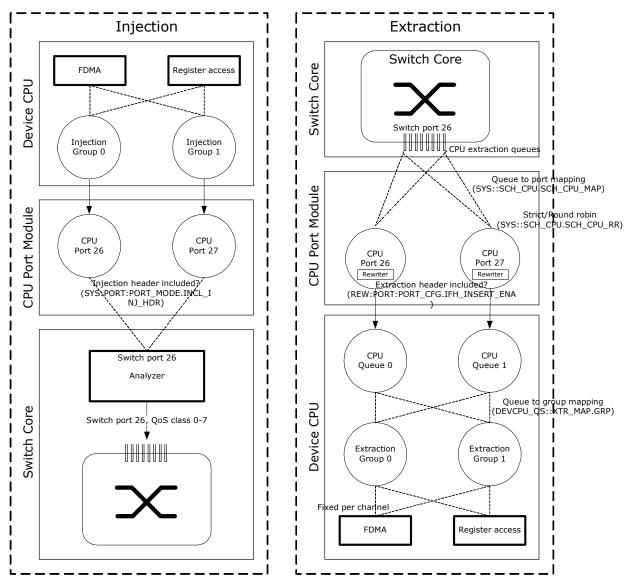

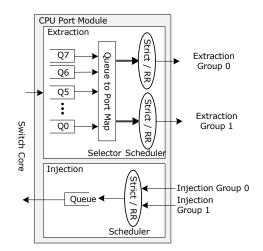

# 1.4.7 CPU PORT MODULE

The CPU port module contains eight CPU extraction queues and two CPU injection queues. These queues provide an interface for exchanging frames between the internal CPU system and the switch core. An external CPU using the serial interface can also inject and extract frames to and from the switch core by using the CPU port module. Additionally, any Ethernet interface on the devices can be used for extracting and injecting frames.

The switch core can intercept a variety of different frame types and copy or redirect these to the CPU extraction queues. The classifier can identify a set of well-known frames such as IEEE reserved destination MAC addresses (BPDUs, GARPs), as well as IP-specific frames (IGMP, MLD). In addition, frames can be intercepted based on the MAC table, the VLAN table, or the learning process.

Whenever a frame is copied or redirected to the CPU, a CPU extraction queue number is associated with the frame and used by the CPU port module when enqueuing the frame into the 8 CPU extraction queues. The CPU extraction queue number is programmable for every interception option in the switch core.

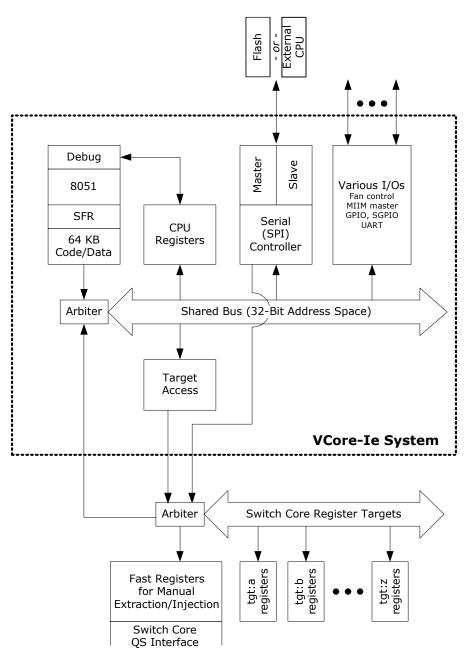

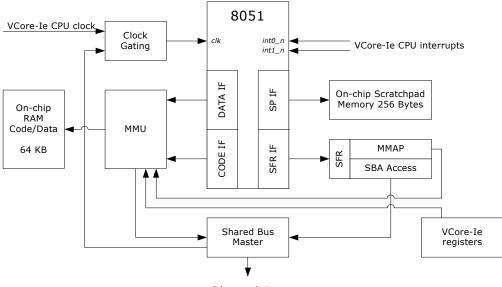

# 1.4.8 CPU SYSTEM AND INTERFACES

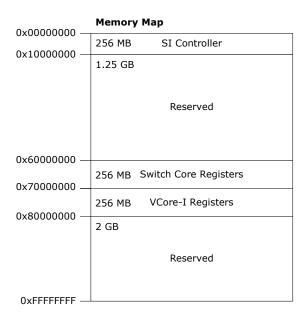

The devices feature a VCore-le CPU system containing a 208 MHz 8051 CPU. It is suitable for basic switch tasks such as simple runtime protocols and port state monitoring. VCore-le includes 64 kilobytes of internal storage, which can be used for code and data.

In addition to the integrated processor, the CPU system permits the attachment of an external CPU. For configuration of switch register, an external CPU can use a serial interface. For frame transfers, the external CPU has the option of using the serial interface or an SGMII port.

The devices include a GPIO interface with 14 individually configurable pins. Through the GPIOs, various interfaces are supported by the devices:

- Two-wire serial interface (two GPIO pins)

- UART (two GPIO pins)

- External interrupt (one interrupt pin)

- Serial GPIO (SGPIO) and LED interface (four GPIO pins)

- Fan controller with speed input and pulse-width-modulated output (two GPIO pins)

The Serial GPIO and LED interface can specifically be used for driving external LEDs for the internal and external copper PHYs or for serializing external interrupts, for instance link down events from external PHYs, before being input to the devices.

Finally, each of the devices has two MII management controllers; one for the internal PHYs and one connected to the MIIM interface for controlling external PHYs.

# 2.0 FUNCTIONAL DESCRIPTIONS

This section provides detailed information about the functional aspects of the VSC7420-02, VSC7421-02, and VSC7422-02 Gigabit Ethernet switch devices, available configurations, operational features, and testing functionality.

# 2.1 Port Modules

The port modules contain the following functional blocks:

- MAC

- PCS (ports connecting to a high-speed I/O SerDes macro)

Ports connecting to one of the integrated copper transceivers do not have a PCS.

# 2.1.1 PORT MODULE NUMBERING AND MACRO CONNECTIONS

The port modules connect to the interface macros. The interface macros can be of two types:

- Internal copper PHY

- SERDES6G macro

The interface macros connect to the external interface pins. For more information about the SerDes macros and integrated copper transceivers, see Section 2.2, SERDES6G and Section 2.3, Copper Transceivers. Which switch core port modules are connected to which interface macros depends on part number and for some parts on internal configuration.

VSC7421-02 can be used in two different port configurations: switch mode 0 or switch mode 1. The VSC7420-02 and VSC7422-02 devices run in switch mode 0. The switch mode is controlled through DEVCPU\_GCB::MISC\_CFG.SW\_MODE.

The following table lists the mapping from the switch core port modules to the interface macros. Empty cells in the table imply that the port module number is not in use for the specific part number.

When programming registers depending on port numbers, the switch core port module number must always be used. Examples of this are when accessing port module registers (PORT::) or using port masks in system or analyzer registers (SYS::, ANA::).

The number next to the interface macro type (for example, "3" in cell SERDES6G, 3) indicates either the macro number or the internal PHY number that must be used when addressing the macros and PHYs for programming.

| Switch Core | VSC7420-02  | VSC7421-02    | VSC7421-02    | VSC7422-02  |

|-------------|-------------|---------------|---------------|-------------|

| Port Module |             | Switch Mode 0 | Switch Mode 1 |             |

| 0-7         | CuPHY, 0-7  | CuPHY, 0-7    | CuPHY, 0-7    | CuPHY, 0-7  |

| 8-11        | —           | CuPHY, 8-11   | CuPHY, 8-11   | CuPHY, 8-11 |

| 12-15       | —           | SERDES6G, 3   | —             | SERDES6G, 3 |

| 16          | —           | —             | SERDES6G, 3   | SERDES6G, 2 |

| 17          | —           | —             | —             | SERDES6G, 2 |

| 18          | —           | —             | —             | SERDES6G, 2 |

| 19          | —           | —             | SERDES6G, 2   | SERDES6G, 2 |

| 20-23       | —           | —             | —             | SERDES6G, 1 |

| 24          | SERDES6G, 1 | —             | SERDES6G, 1   | —           |

| 25          | SERDES6G, 0 | SERDES6G, 0   | SERDES6G, 0   | SERDES6G, 0 |

| 26          | CPU port    | CPU port      | CPU port      | CPU port    |

# TABLE 2-1: PORT MAPPING FROM SWITCH CORE PORT MODULE TO INTERFACE MACROS

# 2.1.2 MAC

This section provides information about the high-level functionality and the configuration options of the Media Access Controller (MAC) that is used in each of the port modules.

The MAC supports the following speeds and duplex modes:

- PHY ports support 10/100/1000 Mbps in full-duplex mode and 10/100 Mbps in half-duplex mode.

- SERDES6G ports support 10/100/1000 Mbps in full-duplex mode and 10/100 Mbps in half-duplex mode.

The MACs also support 2500 Mbps in full-duplex mode as follows: VSC7420-02: Port modules 24 and 25. VSC7421-02: Port modules 24 and 25 in switch mode 1. In switch mode 0, port module 25. VSC7422-02: Port module 25.

The following table lists the registers associated with configuring the MAC.

| Register                 | Description                      | Replication |

|--------------------------|----------------------------------|-------------|

| CLOCK_CFG                | Reset and speed configuration    | Per port    |

| MAC_ENA_CFG              | Enabling of Rx and Tx data paths | Per port    |

| MAC_MODE_CFG             | Port mode configuration          | Per port    |

| MAC_MAXLEN_CFG           | Maximum length configuration     | Per port    |

| MAC_TAGS_CFG             | VLAN tag length configuration    | Per port    |

| MAC_ADV_CHK_CFG          | Type length configuration        | Per port    |

| MAC_IFG_CFG              | Interframe gap configuration     | Per port    |

| MAC_HDX_CFG              | Half-duplex configuration        | Per port    |

| MAC_FC_CFG               | Flow control configuration       | Per port    |

| MAC_F-<br>C_MAC_LOW_CFG  | LSB of SMAC used in pause frames | Per port    |

| MAC_F-<br>C_MAC_HIGH_CFG | MSB of SMAC used in pause frames | Per port    |

| MAC_STICKY               | Sticky bit recordings            | Per port    |

#### TABLE 2-2: MAC CONFIGURATION REGISTERS

#### 2.1.2.1 Resets

There are a number of resets in the port module. All of the resets can be set and cleared simultaneously. By default, all blocks are in the reset state. With reference to register CLOCK\_CFG, the resets are:

- MAC\_RX\_RST Reset of the MAC receiver

- MAC\_TX\_RST Reset of the MAC transmitter

- · PORT\_RST Reset of the ingress and egress queues

- PHY\_RST Reset of the integrated PHY (only present for port modules connecting to a PHY)

- · PCS\_RX\_RST Reset of the PCS decoder (only present for port modules connecting to a SerDes macro)

- PCS\_TX\_RST Reset of the PCS encoder (only present for port modules connecting to a SerDes macro)

When changing the MAC configuration, the port must go through a reset cycle. This is done by writing register CLOCK\_CFG twice. On the first write, the reset bits are set. On the second write, the reset bits are cleared. Bits that are not reset bits in CLOCK\_CFG must keep their new value for both writes.

For more information about resetting a port, see Section 4.3.3, Port Reset Procedure.

#### 2.1.2.2 Port Mode Configuration

The MAC provides a number of handles for configuring the port mode. With reference to the MAC\_MODE\_CFG, MAC\_IFG\_CFG, and MAC\_ENA\_CFG registers, the handles are:

- Duplex mode (FDX\_ENA). Half or full duplex.

- Data sampling (GIGA\_MODE\_ENA). Must be 1 in 1 Gbps and 2.5 Gbps and 0 in 10 Mbps and 100 Mbps.

- Enabling transmission and reception of frames (TX\_ENA/RX\_ENA). Clearing RX\_ENA stops the reception of frames and further frames are discarded. An ongoing frame reception is interrupted. Clearing TX\_ENA stops the dequeuing of frames from the egress queues, which means that frames are held back in the egress queues. An ongoing frame transmission is completed.

- Tx to Tx inter-frame gap (TX\_IFG).

For ports connecting to an internal PHY, the link speed is determined by the PHY. For other ports, the link speed is configured using CLOCK\_CFG.LINK\_SPEED with the following options:

• Link speed (CLOCK\_CFG.LINK\_SPEED)

#### 1 Gbps (125 MHz clock)

Ports 24 and 25: 1 Gbps or 2.5 Gbps (125 MHz or 312.5 MHz clock). The actual clock frequency depends on the SerDes configuration.

100 Mbps (25 MHz clock)

10 Mbps (2.5 MHz clock)

#### 2.1.2.3 Half-Duplex Mode

A number of special configuration options are available for half-duplex (HDX) mode:

- Seed for back-off randomizer Field MAC\_HDX\_CFG.SEED seeds the randomizer used by the backoff algorithm. Use MAC\_HDX\_CFG.SEED\_LOAD to load a new seed value.

- **Backoff after excessive collision** Field MAC\_HDX\_CFG.WEXC\_DIS determines whether the MAC backs off after an excessive collision has occurred. If set, backoff is disabled after excessive collisions.

- **Retransmission of frame after excessive collision** Field MAC\_HDX\_CFG.RETRY\_AFTER\_EXC\_COL\_ENA determines if the MAC retransmits frames after an excessive collision has occurred. If set, a frame is not dropped after excessive collisions, but the backoff sequence is restarted. Although this is a violation of IEEE 802.3, it is useful in non-dropping half-duplex flow control operation.

- Late collision timing Field MAC\_HDX\_CFG.LATE\_COL\_POS adjusts the border between a collision and a late collision in steps of 1 byte. According to IEEE 802.3, section 21.3, this border is permitted to be on data byte 56 (counting frame data from 1); that is, a frame experiencing a collision on data byte 55 is always retransmitted, but it is never retransmitted when the collision is on byte 57. For each higher LATE\_COL\_POS value, the border is moved 1 byte higher.

- **Rx-to-Tx inter-frame gap** The sum of MAC\_IFG\_CFG.RX\_IFG1 and MAC\_IFG\_CFG.RX\_IFG2 establishes the time for the Rx-to-Tx inter-frame gap. RX\_IFG1 is the first part of half-duplex Rx-to-Tx inter-frame gap. Within RX\_IFG1, this timing is restarted if carrier sense (CRS) has multiple high-low transitions (due to noise). RX\_IFG2 is the second part of half-duplex Rx-to-Tx inter-frame gap. Within RX\_IFG2, transitions on CRS are ignored.

When enabling a port for half-duplex mode, the switch core must also be enabled (SYS::FRONT\_PORT\_MODE.HDX-\_MODE).

#### 2.1.2.4 Frame and Type/Length Check

The MAC supports frame lengths of up to 16 kilobytes. The maximum length accepted by the MAC is configurable in MAC\_MACLEN\_CFG.MAX\_LEN.

The MAC allows tagged frames to be 4 bytes longer and double-tagged frames to be 8 bytes longer than the specified maximum length (MAC\_TAGS\_CFG.VLAN\_LEN\_AWR\_ENA). The MAC must be configured to look for VLAN tags. By default, EtherType 0x8100 identifies a VLAN tag. In addition, a custom EtherType can be configured in MAC\_TAGS\_CFG.TAG\_ID. The MAC can be configured to look for none, or two tags (MAC\_TAG\_CFG.VLAN\_AW-R\_ENA).

The type/length check (MAC\_ADV\_CHK\_CFG.LEN\_DROP\_ENA) causes the MAC to discard frames with type/length errors (in-range and out-of-range errors).

#### 2.1.2.5 Flow Control

In full-duplex mode, the MAC provides independent support for transmission of pause frames and reaction to incoming pause frames. This allows for asymmetric flow control configurations.

The MAC obeys received pause frames (MAC\_FC\_CFG.RX\_FC\_ENA) by pausing the egress traffic according to the timer values specified in the pause frames.

The transmission of pause frames is triggered by assertion of a flow control condition in the ingress queues caused by a queue filling exceeding a watermark. For more information, see Section 2.8, Shared Queue System. The MAC handles the formatting and transmission of the pause frame. The following configuration options are available:

- Transmission of pause frames (MAC\_CFG\_CFG.TX\_FC\_ENA).

- Pause timer value used in transmitted pause frames (MAC\_FC\_CFG.PAUSE\_VAL\_CFG).

- Flow control cancellation when the ingress queues de-assert the flow control condition by transmission of a pause frame with timer value 0 (MAC\_FC\_CFG.ZERO\_PAUSE\_ENA).

- · Source MAC address used in transmitted pause frames (MAC\_FC\_MAC\_HIGH\_CFG, MAC\_F-

# C\_MAC\_LOW\_CFG).

The MAC has the option to discard incoming frames when the remote link partner is not obeying the pause frames transmitted by the MAC. The MAC discards an incoming frame if a Start-of-Frame is seen after the pause frame was transmitted. It is configurable how long reaction time is given to the link partner (MAC\_FC\_CFG.FC\_LATENCY\_CFG). The benefit of this approach is that the queue system is not risking being overloaded with frames due to a non-complying link partner.

In half-duplex mode, the MAC does not react to received pause frames. If the flow control condition is asserted by the ingress queues, the industry-standard backpressure mechanism is used. Together with the ability to retransmit frames after excessive collisions (MAC\_HDX\_CFG.RETRY\_AFTER\_EXC\_COL\_ENA), this enables non-dropping half-duplex flow control.

#### 2.1.2.6 Frame Aging

The following table lists the registers associated with frame aging.

| TABLE 2-3. FRAME AGING CONFIGURATION REGISTERS | <b>TABLE 2-3</b> : | FRAME AGING CONFIGURATION REGISTERS |

|------------------------------------------------|--------------------|-------------------------------------|

|------------------------------------------------|--------------------|-------------------------------------|

| Register              | Description         | Replication |

|-----------------------|---------------------|-------------|

| SYS::FRM_AGING        | Frame aging time    | None        |

| REW::PORT_CFG.AGE_DIS | Disable frame aging | Per port    |

The MAC supports frame aging where frames are discarded if a maximum transit delay through the switch is exceeded. All frames, including CPU-injected frames, are subject to aging. The transit delay is time from when a frame is fully received until that frame is scheduled for transmission through the egress MAC. The maximum allowed transit delay is configured in SYS::FRM AGING.

Frame aging can be disabled per port (REW::PORT\_CFG.AGE\_DIS).

Discarded frames due to frame aging are counted in the c\_tx\_aged counter.

#### 2.1.3 PCS

This section provides information about the Physical Coding Sublayer (PCS) block, where the auto-negotiation process establishes mode of operation for a link. The PCS supports both SGMII mode and two SerDes modes, 1000BASE-X and 100BASE-FX.

The PCS block is only available in port modules 12 through 25.

The following table lists the registers associated with PCS.

| Registers            | Description                                                            | Replication |

|----------------------|------------------------------------------------------------------------|-------------|

| PCS1G_CFG            | PCS configuration                                                      | Per PCS     |

| PCS1G_MODE_CFG       | PCS mode configuration                                                 | Per PCS     |

| PCS1G_SD_CFG         | Signal detect configuration                                            | Per PCS     |

| PCS1G_ANEG_CFG       | Configuration of the PCS auto-<br>negotiation process                  | Per PCS     |

| PCS1G_ANEG_NP_CFG    | Auto-negotiation next page config-<br>uration                          | Per PCS     |

| PCS1G_LB_CFG         | Loop-back configuration                                                | Per PCS     |

| PCS1G_ANEG_STATUS    | Status signaling of the PCS auto-negotiation process                   | Per PCS     |

| PCS1G_ANEG_NP_STATUS | Status signaling of the PCS<br>auto-negotiation next page pro-<br>cess | Per PCS     |

| PCS1G_LINK_STATUS    | Link status                                                            | Per PCS     |

| PCS1G_LINK_DOWN_CNT  | Link down counter                                                      | Per PCS     |

| PCS1G_STICKY         | Sticky bit register                                                    | Per PCS     |

TABLE 2-4:PCS CONFIGURATION REGISTERS

The PCS is enabled in PCS1G\_CFG.PCS\_ENA and supports both SGMII and 1000BASE-X SERDES mode (PCS\_MODE\_CFG.SGMII\_MODE\_ENA), as well as 100-BASE-FX. For information about enabling 100BASE-FX, see Section 2.1.3.7, 100BASE-FX.

The PCS also supports the IEEE 802.3, Clause 66 unidrectional mode, where the transmission of data is independent of the state of the receive link (PCS\_MODE\_CFG.UNIDIR\_MODE\_ENA).

#### 2.1.3.1 Auto-Negotiation

Auto-negotiation is enabled in PCS1G\_ANEG\_CFG.ANEG\_ENA. To restart the auto-negotiation process, PCS1G\_ANEG\_CFG.ANEG\_RESTART\_ONE\_SHOT must be set.

In SGMII mode (PCS\_MODE\_CFG.SGMII\_MODE\_ENA=1), matching the duplex mode with the link partner must be ignored (PCS1G\_ANEG\_CFG.SW\_RESOLVE\_ENA). Otherwise, the link is kept down when the auto-negotiation process fails.

The advertised word for the auto-negotiation process (base page) is configured in PCS1G\_ANEG\_CFG.ADV\_ABILITY. The next page information is configured in PCS1G\_ANEG\_NP\_CFG.NP\_TX.

When the auto-negotiation state machine has exchanged base page abilities, the PCS1G\_ANEG\_STATUS.PAGE\_RX-\_STICKY is asserted indicating that the link partner's abilities were received (PCS1G\_ANEG\_STATUS.LP\_ADV\_ABIL-ITY).

If next page information is exchanged, PAGE\_RX\_STICKY must be cleared, next page abilities must be written to PCS1G\_ANEG\_NP\_CFG.NP\_TX, and PCS1G\_ANEG\_NP\_CFG.NP\_LOADED\_ONE\_SHOT must be set. When the auto-negotiation state machine has exchanged the next page abilities, the PCS1G\_ANEG\_STATUS.PAGE\_RX\_STICKY is asserted again, indicating that the link partner's next page abilities were received (PCS1G\_ANEG\_STA-TUS.LP\_NP\_RX). Additional exchanges of next page information are possible using the same procedure.

After the last next page is received, the auto-negotiation state machine enters the IDLE\_DETECT state and the PCS1G\_ANEG\_STATUS.PR bit is set indicating that ability information exchange (base page and possible next pages) is finished and software can now resolve priority. Appropriate actions, such as Rx or Tx reset, or auto-negotiation restart, can then be taken, based on the negotiated abilities. The LINK OK state is reached one link timer period later.

When the auto-negotiation process reaches the LINK\_OK state, PCS1G\_ANEG\_STATUS.ANEG\_COMPLETE is asserted.

# 2.1.3.2 Link Surveillance

The current link status can be observed through PCS1G\_LINK\_STATUS.LINK\_STATUS. The LINK\_STATUS is defined as either the PCS synchronization state or as bit 15 of PCS1G\_ANEG\_STATUS.LP\_ADV\_ABILTY, which carries information about the link status of the attached PHY in SGMII mode.

Link down is defined as the auto-negotiation state machine being in neither the AN\_DISABLE\_LINK\_OK state nor the LINK\_OK state for one link timer period. If a link down event occurs, PCS1G\_STICKY.LINK\_DOWN\_STICKY is set, and PCS1G\_LINK\_DOWN\_CNT is incremented. In SGMII mode, the link timer period is 1.6 ms; in SerDes mode, the link timer period is 10 ms.

The PCS synchronization state can be observed through PCS1G\_LINK\_STATUS.SYNC\_STATUS. Synchronization is lost when the PCS is not able to recover and decode data received from the attached serial link.

# 2.1.3.3 Signal Detect

The PCS can be enabled to react to loss of signal through signal detect (PCS1G\_SD\_CFG.SD\_ENA). At loss of signal, the PCS Rx state machine is restarted, and frame reception stops. If signal detect is disabled, no action is taken upon loss of signal. The polarity of signal detect is configurable in PCS1G\_SD\_CFG.SD\_POL.

The source of signal detect is selected in PCS1G\_SD\_CFG.SD\_SEL to either the SerDes PMA or the PMD receiver. If the SerDes PMA is used as source, the SerDes macro provides the signal detect. If the PMD receiver is used as source, signal detect is sampled externally through one of the GPIO pins on the devices. For more information about the configuration of the GPIOs and signal detect, see Section 3.7.5, GPIO Controller.

PCS1G\_LINK\_STATUS.SIGNAL\_DETECT contains the current value of the signal detect input.

#### 2.1.3.4 Tx Loopback

For debug purposes, the Tx data path in the PCS can be looped back into the Rx data path. This feature is enabled through PCS1G\_LB\_CFG.TBI\_HOST\_LB\_ENA.

### 2.1.3.5 Test Patterns

The following table lists the registers associated with configuring test patterns.

#### TABLE 2-5: TEST PATTERN REGISTERS

| Registers                     | Description                | Replication |

|-------------------------------|----------------------------|-------------|

| PCS1G_TSTPAT_MODE_CFG         | Test pattern configuration | Per PSC     |

| PCS1G_TSTPAT_MODE_STA-<br>TUS | Test pattern status        | Per PCS     |

PCS1G\_TSTPAT\_MODE\_CFG.JTP\_SEL overwrites normal operation of the PCS and enables generation of jitter test patterns for debugging. The jitter test patterns are defined in IEEE 802.3, Annex 36A, and the following patterns are supported:

- High frequency test pattern

- · Low frequency test pattern

- Mixed frequency test pattern

- · Continuous random test pattern with long frames

- Continuous random test pattern with short frames

PCS1G\_TSTPAT\_MODE\_STATUS register holds information about error and lock conditions while running the jitter test patterns.

#### 2.1.3.6 Low Power Idle

The following table lists the registers associated with low power idle (LPI).

#### TABLE 2-6: LOW POWER IDLE REGISTERS

| Registers                | Description                                        | Replication |

|--------------------------|----------------------------------------------------|-------------|

| PCS1G_LPI_CFG            | Configuration of the PCS Low<br>Power Idle process | Per PSC     |

| PCS1G_LPI_WAKE_ERROR_CNT | Error counter                                      | Per PCS     |

| PCS1G_LPI_STATUS         | Low Power Idle status                              | Per PCS     |

The PCS supports Energy Efficient Ethernet (EEE) as defined by IEEE 802.3az. The PCS converts Low Power Idle (LPI) encoding between the MAC and the serial interface transparently. In addition, the PCS provides control signals allowing to stop data transmission in the SerDes macro. During low power idles the serial transmitter in the SerDes macro can be powered down, only interrupted periodically while transmitting refresh information, which allows the receiver to notice that the link is still up but in power down mode.

When a SERDES6G macro operating in QSGMII mode is enabled for powering down of the serial transmitter during low power idles, one of the four PCSs connected to the macro must be selected master (PCS1G\_LPI\_CFG.QSGMII\_MS\_SEL). The master PCS sends refresh information to the attached receivers periodically. Note that the serial transmitter can only power down when all four attached ports are in low power idle.

For more information about powering down the serial transmitter in the SerDes macros, see Section 2.2, SERDES6G.

It is not necessary to enable the PCS for EEE, because it is controlled indirectly by the shared queue system. It is possible, however, to manually force the PCS into the low power idle mode through PCS1G\_LPI\_CFG.TX\_ASSERT\_LPI-DLE. During LPI mode, the PCS constantly encodes low power idle with periodical refreshes. For more information about EEE, see Section 2.8.10, Energy Efficient Ethernet.

The current low power idle state can be observed through PCS1G\_LPI\_STATUS for both receiver and transmitter:

- RX\_LPI\_MODE: Set if the receiver is in low power idle mode.

- RX\_QUIET: Set if the receiver is in the Quiet state of the low power idle mode. If cleared while RX\_LPI\_MODE is set, the receiver is in the refresh state of the low power idle mode.

The same is observable for the transmitter through TX\_LPI\_MODE and TX\_QUIET.

If an LPI symbol is received, the RX\_LPI\_EVENT\_STICKY bit is set, and if an LPI symbol is transmitted, the TX\_LPI\_EVENT\_STICKY bit is set. These events are sticky.

The PCS1G\_LPI\_WAKE\_ERROR\_CNT wake-up error counter increments when the receiver detects a signal and the PCS is not synchronized. This can happen when the transmitter fails to observe the wake-up time or if the receiver is not able to synchronize in time.

#### 2.1.3.7 100BASE-FX

The following table lists the registers associated with 100BASE-FX configuration.

#### TABLE 2-7: 100BASE-FX REGISTERS

| Registers        | Description                                 | Replication |

|------------------|---------------------------------------------|-------------|

| PCS_FX100_CFG    | Configuration of the PCS<br>100BASE-FX mode | Per PSC     |

| PCS_FX100_STATUS | Status of the PCS 100BASE-FX mode           | Per PCS     |

The PCS supports a 100BASE-FX mode in addition to the SGMII and 1000BASE-X SerDes modes. The 100BASE-FX mode uses 4-bit/5-bit coding as specified in IEEE 802.3 Clause 24 for fiber connections. The 100BASE-FX mode is enabled through PCS\_FX100\_CFG.PCS\_ENA, which masks out all PCS1G related registers.

The following options are available:

**Far-End Fault facility** In 100BASE-FX, the PCS supports the optional Far-End Fault facility. Both Far-End Fault generation (PCS\_FX100\_CFG.FEF\_GEN\_ENA) and Far-End Fault Detection (PCS\_FX100\_CFG.FEF\_CHK\_ENA) are supported. An Far-End Fault incident is recorded in PCS\_FX100\_STATUS.FEF\_FOUND.

**Signal Detect** 100BASE-FX has a similar signal detect scheme to the SGMII and SerDes modes. For 100BASE-FX, PCS\_FX100\_CFG.SD\_ENA enables signal detect, PCS\_FX100\_CFG.SD\_POL controls the polarity, and PCS\_FX-100\_CFG.SD\_SEL selects the input source. The current status of the signal detect input can be observed through PCS\_FX100\_STATUS.SIGNAL\_DETECT. For more information about signal detect, see Section 2.1.3.3, Signal Detect.

**Link Surveillance** The PCS synchronization status can be observed through PCS\_FX100\_STATUS.SYNC\_STATUS. When synchronization is lost, the link breaks and PCS\_FX100\_STATUS.SYNC\_LOST\_STICKY is set. The PCS continuously tries to recover the link.

**Unidirectional mode** 100BASE-FX has a similar unidirectional mode as SGMII and SerDes modes. PCS\_FX-100\_CFG.UNIDIR\_MODE\_ENA enables unidirectional mode.

# 2.2 SERDES6G

The SERDES6G is a high-speed SerDes interface that operates at 100 Mbps (100BASE-FX), 1 Gbps (SGMII/SerDes), 2.5 Gbps (SGMII), and 4 Gbps (QSGMII). The 100BASE-FX mode is supported by oversampling.

The following table lists the registers associated with SERDES6G.

| Registers           | Description                 | Replication |

|---------------------|-----------------------------|-------------|

| SERDES6G_COMMON_CFG | Common configuration        | Per SerDes  |

| SERDES6G_DES_CFG    | Deserializer configuration  | Per SerDes  |

| SERDES6G_IB_CFG     | Input buffer configuration  | Per SerDes  |

| SERDES6G_IB_CFG1    | Input buffer configuration  | Per SerDes  |

| SERDES6G_SER_CFG    | Serializer configuration    | Per SerDes  |

| SERDES6G_OB_CFG     | Output buffer configuration | Per SerDes  |

| SERDES6G_OB_CFG1    | Output buffer configuration | Per SerDes  |

| SERDES6G_PLL_CFG    | PLL configuration           | Per SerDes  |

| SERDES6G_MISC_CFG   | Miscellaneous configuration | Per SerDes  |

TABLE 2-8: SERDES6G REGISTERS

For increased performance in specific application environments, SERDES6G supports the following:

- Baud rate support, configurable from 1 Gbps to 4 G, for quarter, half, and full rate modes

- Programmable loop bandwidth and phase regulation for the deserializer

- · Configurable input buffer features such as signal detect/loss of signal (LOS) options

- Configurable output buffer features, such as programmable de-emphasis, amplitude drive levels, and slew rate control

- Synchronous Ethernet support

- Loopbacks for system test

#### 2.2.1 SERDES6G BASIC CONFIGURATION

The SERDES6G is enabled in SERDES6G\_COMMON\_CFG.ENA\_LANE. By default, the SERDES6G is held in reset and must be released before the interface is active. This is done through SERDES6G\_COMMON\_CFG.SYS\_RST and SERDES6G\_MISC\_CFG.LANE\_RST.

#### 2.2.1.1 SERDES6G Parallel Interface Configuration

The SERDES6 block includes a parallel data interface, which can operate in two different modes. It must be set according to the mode of operation (SERDES6G\_COMMON\_CFG.IF\_MODE). For 100 Mbps, 1 Gbps, and 2.5 Gbps operation, the 10-bit mode is used, and for 4 Gbps operation (QSGMII), the 20-bit mode is used.

#### 2.2.1.2 SERDES6G PLL Frequency Configuration

To operate the SERDES6G block at the correct frequency, configure the internal macro as follows. The PLL calibration is enabled through SERDES6G\_PLL\_CFG.PLL\_FSM\_ENA.

- 1. Configure SERDES6G\_PLL\_CFG.PLL\_FSM\_CTRL\_DATA in accordance with data rates listed in the following two tables.

- 2. Set SYS\_RST = 0 (active) and PLL\_FSM\_ENA = 0 (inactive).

- 3. Set SYS\_RST = 1 (deactive) and PLL\_FSM\_ENA = 1 (active).

#### TABLE 2-9: PLL CONFIGURATION

| Mode                      | SERDES6G_PLL_CFG.PLL_FSM_CTRL_DATA |

|---------------------------|------------------------------------|

| SGMII/SerDes, 1 Gbps data | 60                                 |

| SGMII, 2.5 Gbps data      | 48                                 |

| QSGMII, 4 Gbps data       | 120                                |

#### 2.2.1.3 SERDES6G Frequency Configuration

The following table lists the range of data rates that are supported by SERDES6G.

#### TABLE 2-10: SERDES6 FREQUENCY CONFIGURATION REGISTERS

| Configuration                | SGMII/SerDes<br>1 Gbps | SGMII<br>2.5 Gbps | QSGMII<br>4 Gbps |

|------------------------------|------------------------|-------------------|------------------|

| SERDES6G_PLL_CFG.PLL_ROT_FRQ | 0                      | 1                 | 0                |

| SERDES6G_PLL_CFG.PLL_ROT_DIR | 1                      | 0                 | 0                |

| SERDES6G_PLL_CFG.PLL_ENA_ROT | 0                      | 1                 | 0                |

| SERDES6G_COMMON_CFG.QRATE    | 1                      | 0                 | 0                |

| SERDES6G_COMMON_CFG.HRATE    | 0                      | 1                 | 0                |

#### 2.2.2 SERDES6G LOOPBACK MODES

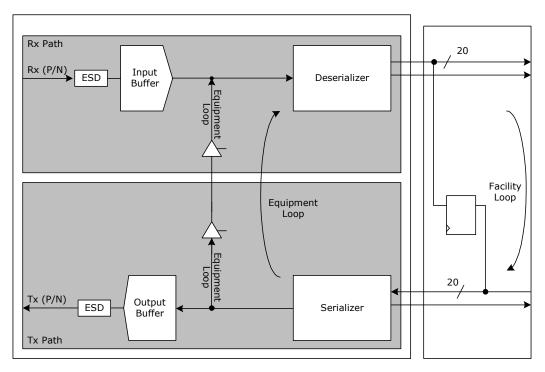

The SERDES6G interface supports two different loopback modes for testing and debugging data paths: equipment loopback and facility loopback.

**Equipment loopback (SERDES6G\_COMMON\_CFG.ENA\_ELOOP)** Data is looped back from serializer output to the deserializer input, and the receive clock is recovered. The equipment loopback includes all transmit and receive functions, except for the input and output buffers. The Tx data can still be observed on the output.

**Facility loopback (SERDES6G\_COMMON\_CFG.ENA\_FLOOP)** The clock and parallel data output from deserializer are looped back to the serializer interface. Incoming serial data passes through the input buffer, the CDR, the deserializer, back to the serializer, and finally out through the output buffer.

Only one of the loopbacks can be enabled at the same time.

The following illustration shows the loopback paths for the SERDESG6.

# FIGURE 2-1: SERDES LOOPBACK

# 2.2.3 SERDES6G DESERIALIZER CONFIGURATION

The SERDES6G block includes digital control logic that interacts with the analog modules within the block and compensates for the frequency offset between the received data and the internal high-speed reference clock. To gain high jitter performance, the phase regulation is a PI-type regulator, whose proportional (P) and integrative (I) characteristics can be independently configured.

The integrative part of the phase regulation loop is configured in SERDES6G\_DES\_CFG.DES\_PHS\_CTRL. The limits of the integrator are programmable, allowing different settings for the integrative regulation while guaranteeing that the proportional part still is stronger than the integrative part. Integrative regulation compensates frequency modulation from DC up to cut-off frequency. Frequencies above the cut-off frequency are compensated by the proportional part.

The DES\_BW\_HYST register field controls the time constant of the integrator independently of the proportional regulator. The range of DES\_BW\_HYST is programmable as follows:

- Full rate mode = 3 to 7

- Half-rate mode = 2 to 7

- Quarter-rate mode = 1 to 7

The lower the configuration setting, the smaller the time-constant of the integrative regulation. For normal operation, configure DES\_BW\_HYST to 5.

The cut-off-frequency is calculated to:

fco = 1/(2 × PI × 128 × PLL period × 32 × 2<sup>(</sup>DES\_BW\_HYST + 1 – DES\_BW\_ANA))

PLL period =  $1/(n \times \text{data rate})$

where, n = 1 (full rate mode), 2 (half-mode) or 4 (quarter-rate mode)

The integrative regulator can compensate a static frequency offset within the programmed limits down to a remaining frequency error of below 4 ppm. In steady state, the integrator toggles between two values around the exact value, and the proportional part of the phase regulation takes care of the remaining phase error.

After a device reset, the phase regulation may be 180° out of phase compared to the incoming data, resulting in a deadlock condition at the sampling stage of the deserializer. To prevent this situation, the SERDES6G provides a 180° deadlock protection mechanism (SERDES6G\_DES\_CFG.DES\_MBTR\_CTRL). If the deadlock protection mechanism is

enabled, a small frequency offset is applied to the phase regulation loop. The offset is sufficient to move the sampling point out of the 180° deadlock region, while at the same time, small enough to allow the regulation loop to compensate when the sample point is within the data eye.

The loop bandwidth for the proportional part of the phase regulation loop is controlled by configuring SER-DES6G\_DES\_CFG.DES\_BW\_ANA.

The fastest loop bandwidth setting (lowest configuration value) results in a loop bandwidth that is equal to the maximum frequency offset compensation capability. For improved jitter performance, use a setting with sufficient margin to track the expected frequency offset rather than using the maximum frequency offset. For example, if a 100 ppm offset is expected, use a setting that is four times higher than the offset. For more information about possible bandwidth selections, see Table 5-209.

The following table provides the limits for the frequency offset compensation. The values are theoretical limits for input signals without jitter, because the actual frequency offset compensation capability is dependent on the toggle rate of the input data and the input jitter. Note that only applicable configuration values are listed. HRATE and QRATE are the configuration settings of SERDES6G\_COMMON\_CFG.HRATE and SERDES6G\_COMMON\_CFG.QRATE.

| DES_BW_ANA | Limits when<br>HRATE = 0<br>QRATE = 0 | Limits when<br>HRATE = 1<br>QRATE = 0 | Limits when<br>HRATE = 0<br>QRATE = 1 |

|------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 2          | —                                     | —                                     | 1953 ppm                              |

| 3          | —                                     | 1953 ppm                              | 977 ppm                               |

| 4          | 1953 ppm                              | 977 ppm                               | 488 ppm                               |

| 5          | 977 ppm                               | 488 ppm                               | 244 ppm                               |

| 6          | 488 ppm                               | 244 ppm                               | 122 ppm                               |

| 7          | 244 ppm                               | 122 ppm                               | 61 ppm                                |

TABLE 2-11: SERDES6G LOOP BANDWIDTH

# 2.2.4 SERDES6G SERIALIZER CONFIGURATION

The serializer provides the ability to align the phase of the internal clock and data to a selected source (SER-DES6G\_SER\_CFG.SER\_ENALI). The phase align logic is used when SERDES6G operates in the facility loopback mode.

# 2.2.5 SERDES6G INPUT BUFFER CONFIGURATION

The SERDES6G input buffer supports configuration options for:

- Automatic input voltage offset compensation

- · Loss of signal detection

The input buffer is normally AC-coupled and therefore the common-mode termination is switched off (SER-DES6G\_IB\_CFG1.IB\_CTERM\_ENA). In order to support type-2 loads (DC-coupling at 1.0 V termination voltage) according to the OIF CEI specifications, common-mode termination must be enabled.

The sensitivity of the level detect circuit can be adapted to the input signal's characteristics (amplitude and noise). The threshold value for the level detect circuit is set in SERDES6G\_IB\_CFG.IB\_VBCOM. The default value is suitable for normal operation.

When the SerDes interface operates in 100BASE-FX mode, the input buffer of the SERDES6G macro must also be configured for 100BASE-FX (SERDES6G\_IB\_CFG.IB\_FX100\_ENA).

During test or reception of low data rate signals (for example, 100BASE-FX), the DC-offset compensation must be disabled. For all other modes, the DC-offset compensation must be enabled for optimized performance. DC-offset compensation is controlled by SERDES6G\_IB\_CFG1.IB\_ENA\_OFFSAC and SERDES6G\_IB\_CFG1.IB\_ENA\_OFFSDC.

# 2.2.6 SERDES6G OUTPUT BUFFER CONFIGURATION

The SERDEDS6G output buffer supports the following configuration options:

- Amplitude control

- De-emphasis and output polarity inversion

- Slew rate control

- Skew adjustment

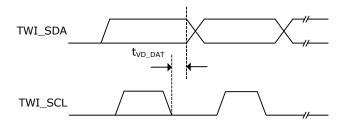

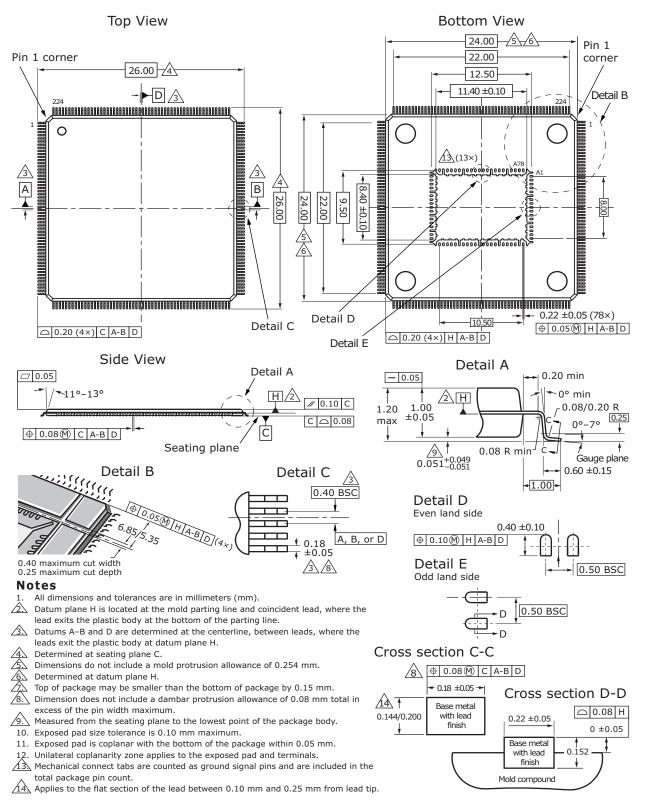

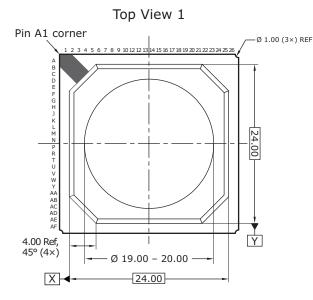

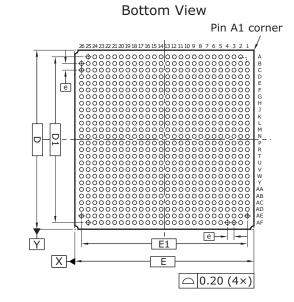

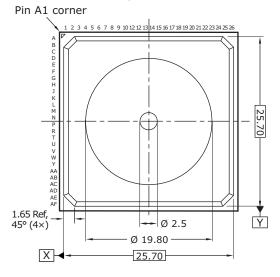

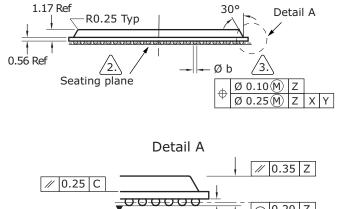

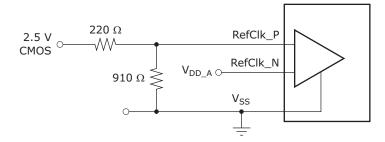

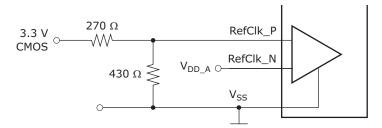

- Idle mode