## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

### **Features**

- 2.48832Gb/s 16-Bit Transceiver

- Targeted for SONET OC-48 / SDH STM-16 Applications

- LVPECL Low-Speed Interface

- On-chip PLL-Based Clock Generator

- High-Speed Clock Output With Power-Down Option

- Supports Parity at the 16-Bit Parallel Transmit and Receive Interfaces

- Provides Equipment, Facilities and Split Loopback Modes as well as Loop Timing Modes

- Loss of Signal (LOS) Detect input

- Meets Bellcore Jitter Performance Specifications

- Single +3.3V Supply

- 2.25 Watts Typical Power Dissipation

- Packages: 128-pin PQFP or 208-pin TBGA

## **General Description**

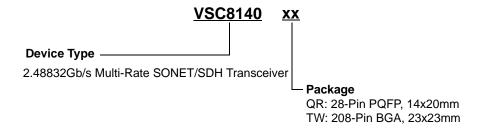

The VSC8140 is a SONET/SDH compatible transceiver with integrated clock generator for use in SONET/SDH systems operating at a 2.48832Gb/s data rate. The internal clock generator uses a Phase-Locked Loop (PLL) to multiply either a 77.76MHz or 155.52MHz reference clock in order to provide the 2.48832GHz clock for internal logic and output retiming. The 16-bit parallel interface incorporates an on-board FIFO eliminating loop timing design issues by providing a flexible parallel timing architecture. In addition, the device provides both facility and equipment loopback modes and two loop timing modes. The VSC8140 operates using a 3.3V power supply, and is available in either a thermally-enhanced 128-PQFP or a thermally-enhanced 208-pin TBGA package.

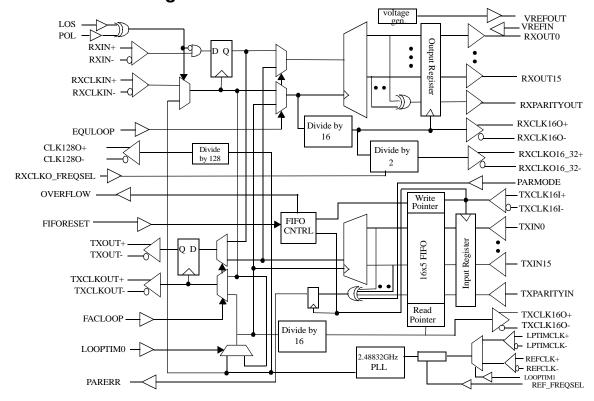

## VSC8140 Block Diagram

Data Sheet VSC8140

### Functional Description

### **Transmitter Low-Speed Interface**

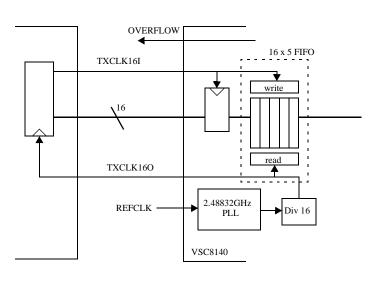

The Upstream Device should use the TXCLK16O as the timing source for its final output latch (see Figure 1). The Upstream Device should then generate a TXCLK16I that is phase-aligned with the data. The VSC8140 will latch TXIN[15:0]± on the rising edge of TXCLK16I+. The data must meet setup and hold times with respect to TXCLK16I (see Table 1).

A FIFO exists within the VSC8140 to eliminate difficult system loop timing issues. Once the PLL has locked to the reference clock, RESET must be held low for a minimum of five CLK16 cycles to initialize the FIFO, then RESET should be set high and held constant for continuous FIFO operation. For the transparent mode of operation (no FIFO), simply hold RESET at a constant low state (see Figure 2).

The use of a FIFO permits the system designer to tolerate an arbitrary amount of delay between TXCLK16O and TXCLK16I. Once RESET is asserted and the FIFO initialized, the delay between TXCLK16O and TXCLK16I can decrease or increase up to one period of the low-speed clock (6.4ns). Should this delay drift exceed one period, the write pointer and the read pointer could point to the same word in the FIFO, resulting in a loss of transmitted data (a FIFO overflow). In the event of a FIFO overflow, an active low OVERFLOW signal is asserted (for a minimum of five TXCLK16I cycles) which can be used to initiate a reset signal from an external controller.

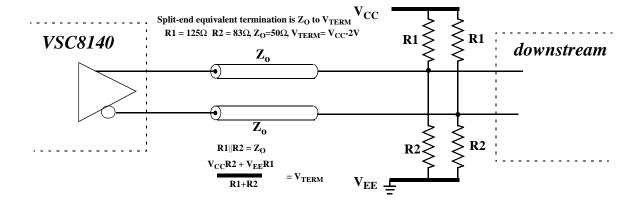

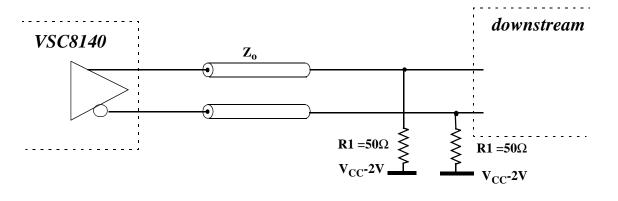

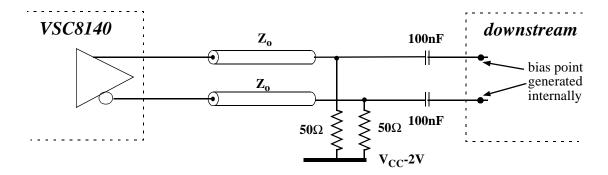

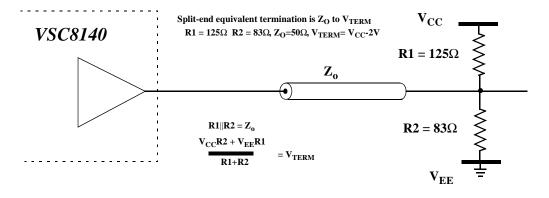

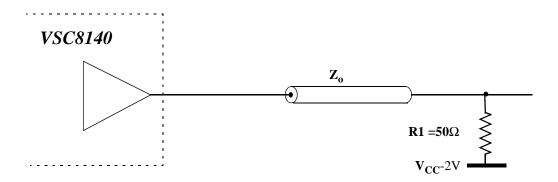

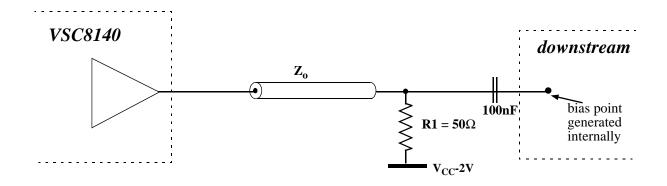

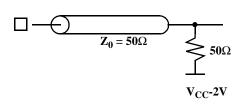

The TXCLK16O $\pm$  output driver is a LVPECL output driver designed to drive a  $50\Omega$  transmission line. The transmission line can be DC terminated with a split-end termination scheme (see Figure 3), or DC terminated by  $50\Omega$  to  $V_{CC}$ -2V on each line (see Figure 4). At any time, the equivalent split-end termination technique can be substituted for the traditional  $50\Omega$  to  $V_{CC}$ -2V on each line. AC-coupling can be achieved by a number of methods. Figure 5 illustrates an AC-coupling method for the occasion when the downstream device provides the bias point for AC-coupling.

Figure 1: Low-Speed Systems Interface

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

Figure 2: Enabling FIFO Operation

PLL locked to reference clock.

Minimum 5 CLK16 cycles

Transparent Mode Operation

Transparent Mode Operation

Holding RESET "low" for a minimum of 5 CLK16 cycles, then setting "high" enables FIFO operation. Holding RESET constantly "low" bypasses the FIFO for transparent mode operation.

Figure 3: DC Termination of Low-Speed LVPECL RXCLK16O, RXCLK16\_32O, TXCLK16O Outputs

Figure 4: DC Termination of Low-Speed LVPECL RXCLK160, RXCLK16\_320, TXCLK160 Outputs

Data Sheet VSC8140

Figure 5: AC Termination of Low-Speed LVPECL RXCLK160, RXCLK16\_320, TXCLK160 Outputs

### **Receiver Low-Speed Interface**

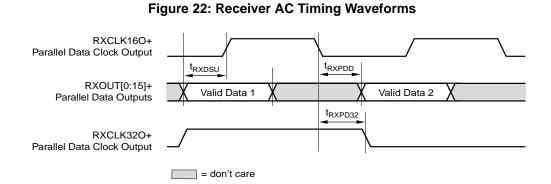

The demultiplexed serial stream is made available by a 16-bit single-ended LVPECL interface RXOUT[15:0] with accompanying differential LVPECL divide-by-16 clock RXCLK16O± and selectable LVPECL divide-by-16 or -32 clock RXCLK16\_32O±.

RXCLKO\_FREQSEL is used to select RXCLK16\_32O±. RXCLKO\_FREQSEL = "0" designates RXCLK16\_32O± output as 77.76MHz, RXCLKO\_FREQSEL = "1" designates RXCLK16\_32O± output as 155.52MHz.

The RXCLK16O and RXCLK16\_32O output drivers are designed to drive a  $50\Omega$  transmission line. The transmission line can be DC terminated with a split-end termination scheme (see Figure 3), or DC terminated by  $50\Omega$  to  $V_{CC}$ -2V on each line (see Figure 4). AC-coupling can be achieved by a number of methods. Figure 5 illustrates an AC-coupling method for the occasion when the downstream device provides the bias point for AC-coupling. The divide-by-16 output (RXCLK16O) or the divide-by-16 or -32 output (RXCLK16\_32O) can be used to provide an external looptiming reference clock (after external filtering with a 1x REFCLK PLL) for the clock multiplication unit on the VSC8140.

The RXOUT[15:0] output drivers are designed to drive a  $50\Omega$  transmission line which can be DC terminated with a split-end termination scheme (see Figure 6), or a traditional termination scheme (see Figure 7).

Figure 6: Split-end DC Termination of Low-Speed LVPECL RXOUT[15:0] Outputs

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

Figure 7: Traditional DC Termination of Low-Speed LVPECL RXOUT[15:0] Outputs

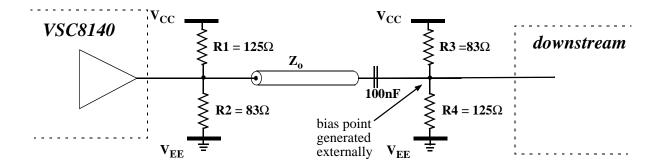

The RXOUT[15:0] output drivers can also be appropriately AC-coupled by a number of methods, however, DC-coupling is preferred since there is no guarantee of transition density for individual bits in the 16-bit word. Figure 8 illustrates an AC-coupling method for the occasion when the downstream device provides the bias point for AC-coupling. Figure 9 illustrates an AC-coupling method for the occasion when the bias point needs to be generated externally. The resistor values in Figure 9 were selected to generate a bias point of 1.98V, the mid-point for LVPECL  $V_{OH}$  and  $V_{OL}$  as specified for the VSC8140. Resistor values should be selected to generate the necessary bias point for the downstream device.

Figure 8: AC Termination of Low-Speed LVPECL RXOUT[15:0] Outputs

Data Sheet VSC8140

Figure 9: AC Termination of Low-Speed LVPECL RXOUT[15:0] Outputs

#### **Parity**

Systems employing internal parity are supported by the VSC8140. On the transmit side, a parity check is performed between the TXPARITYIN input and the 16 TXIN[15:0] bits.

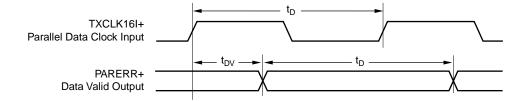

PARMODE is used to select even or odd parity expected for these 17 bits. (TXIN[15:0] and TXPARITYIN). PARMODE = "0" selects odd, PARMODE = "1" selects even. The PARERR output (parity error output) is asserted active high when the parity of the 17 bits (TXIN[15:0] and TXPARITYIN) does not conform to the expected parity designated by PARMODE. PARERR becomes available  $T_{\rm DV}$  after the rising edge of TXCLK16I. PARERR is a NRZ pulse that is updated every 6.4 ns, i.e., the period of TXCLK16I. The timing relationship of PARERR to TXCLK16I is shown in Figure 17. The PARERR pin may be left open if parity is unused.

On the receive side, the parity output (RXPARITYOUT) is simply the XOR of all 16 outputs.

#### **Loss of Signal**

The VSC8140 has a TTL input LOS to force the part into a Loss of Signal (LOS) state. Most optics have a TTL output usually called Signal Detect (SD), based on the optical power of the incoming light stream. Depending on the optics manufacturer, this signal is either active high or low. To accommodate polarity differences, the internal Loss of Signal is generated when the POL and LOS inputs are of opposite states. Once active, all zeroes "0" will be propagated downstream using the transmit clock until the optical signal is regained and LOS and POL are in the same logic state.

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

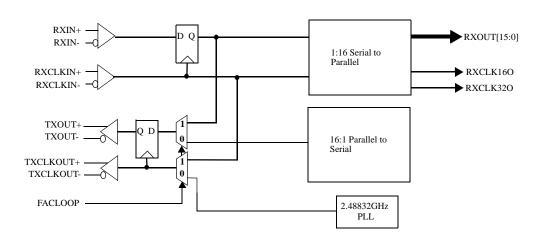

Figure 10: Facility Loopback Data Path

#### **Facility Loopback**

The facility loopback function is controlled by the FACLOOP signal. When the FACLOOP signal is set high, the Facility Loopback mode is activated and the high-speed serial receive data (RXIN) is presented at the high-speed transmit output (TXOUT), as depicted in Figure 10. In addition, the high-speed receive clock input (RXCLKI) is selected and presented at the high-speed transmit clock output (TXCLKOUT). In Facility Loopback mode, the high-speed receive data (RXIN) is also converted to parallel data and presented at the low-speed receive output pins (RXOUT[15:0]). The receive clock (RXCLKIN) is also divided down and presented at the low-speed clock output (RXCLK16O).

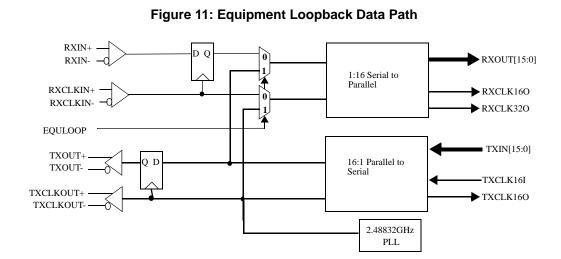

#### **Equipment Loopback Data Path**

The Equipment Loopback function is controlled by the EQULOOP signal, which is active high. When the Equipment Loopback mode is activated, the high-speed transmit data generated from the parallel to serial conversion of the low-speed data (TXIN[15:0]) is selected and converted back to parallel data in the receiver section and presented at the low-speed parallel data outputs (RXOUT[15:0]), as shown in Figure 11. The internally generated OC-48 clock is used to generate the low-speed receive output clocks (RXCLK16O and RXCLK16\_32O). In Equipment Loopback mode, the transmit data (TXIN[15:0]) is serialized and presented at the high-speed output (TXOUT) along with the high-speed transmit clock (TXCLKOUT) which is generated by the on-chip PLL.

# Data Sheet VSC8140

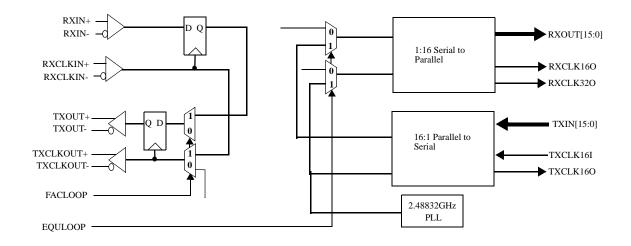

Figure 12: Split Loopback Datapaths

### **Split Loopback**

Equipment and Facility Loopback modes can be enabled simultaneously. In this case, high-speed serial data received (RXIN) and clock (RXCLKIN) are muxed through to the high-speed serial outputs (TXOUT and TXCLKOUT). The low-speed 16-bit transmit stream (TXIN[15:0]) is muxed into the low-speed 16-bit receive output stream (RXOUT[15:0]). See Figure 12.

### Looptiming

LOOPTIM0 mode bypasses the PLL when LOOPTIM0 is asserted high. In this mode, the PLL is bypassed using the receive high-speed clock (RXCLKIN), and the entire part is synchronously clocked from a single external source.

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

When LOOPTIM1 is asserted high, the RXCLK16\_32O or RXCLK16O output can be tied to the LPTIM-CLK input. In order to meet jitter transfer, the RXCLK16\_32O or RXCLOCK16O needs to be filtered by a 1X PLL circuit with a narrow pass characteristic. The part is forced out of this mode in Equipment Loopback to prevent the PLL from feeding its own clock back.

#### **Clock Generator**

An on-chip PLL generates the 2.48832GHz transmit clock from the externally provided REFCLK input. The on-chip PLL uses a low phase noise reactance-based Voltage Controlled Oscillator (VCO) with an on-chip loop filter (with two external  $0.1\mu F$  peaking capacitors). The loop bandwidth of the PLL is within the SONET specified limit of 2MHz.

The customer can select to provide either a 77.76MHz reference, or 2x of that reference, 155.52MHz. REF\_FREQSEL is used to select the desired reference frequency. REF\_FREQSEL = "0" designates REFCLK input as 77.76MHz, REF\_FREQSEL = "1" designates REFCLK input as 155.52MHz.

The REFCLK should be of high quality since noise on the REFCLK below the loop bandwidth of the PLL will pass through the PLL and appear as jitter on the output. Preconditioning of the REFCLK signal with a VCXO may be required to avoid passing REFCLK noise with greater than 2ps RMS of jitter to the output. The VSC8140 will output the REFCLK noise in addition to the intrinsic jitter from the VSC8140 itself during such conditions.

### **Loop Filter**

The PLL on the VSC8140 employs an internal loop filter with off-chip peaking capacitors. The PLL design is fully differential, therefore the loop filter must also be fully differential. One capacitor should be connected between FILTAO and FILTAI, with the other connected between FILTAON and FILTAIN. Recommended capacitors are low-inductance  $0.1\mu F$  0603 ceramic SMT X7R devices with a voltage rating equal to or greater than 10V.

$V_{CC}$   $50\Omega$   $Z_0 = 50\Omega$   $V_{EE}$

Figure 13: High-Speed Output Termination

Data Sheet VSC8140

### **Transmitter High-Speed Data and Clock Outputs**

The high-speed data and clock output drivers (TXOUT and TXCLKOUT) consist of a differential pair designed to drive a  $50\Omega$  transmission line. The transmission line should be terminated with a  $100\Omega$  resistor at the load between true and complement outputs (see Figure 13). No connection to a termination voltage is required. The output driver is back terminated to  $50\Omega$  on-chip, providing a snubbing of any reflections. If used single-ended, the high-speed output driver must still be terminated differentially at the load with a  $100\Omega$  resistor between true and complement outputs.

In order to save power, the high-speed transmit clock output (TXCLKOUT) can be powered down by connecting the power pins VEEP\_CLK and VEE\_PWRDN to the  $V_{CC}$  supply instead of to  $V_{EE}$ .

Figure 14: AC Termination of Low-Speed LVPECL REFCLK and LPTIMCLK Inputs

### **Reference Clock Inputs**

The incoming low-speed reference clock inputs are received by differential LVPECL inputs REFCLK $\pm$  . Off-chip termination of these inputs is required (see Figure 14).

In most situations these inputs will have high transition density and little DC offset. However, in cases where this does not hold, direct DC connection is possible. All serial clock inputs have the same circuit topology, as shown in Figure 14. If the input signal is driven differentially and DC-coupled to the part, the mid-point of the input signal swing should be centered about the input common-mode voltage  $V_{CM}$  and not exceed the maximum allowable amplitude. For single-ended, DC-coupling operations, it is recommended that the user provides an external reference voltage. The external reference should have a nominal value equivalent to the common-mode switch point of the DC-coupled signal, and can be connected to either side of the differential gate.

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

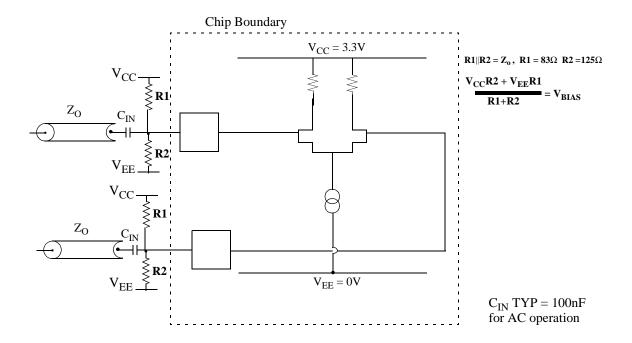

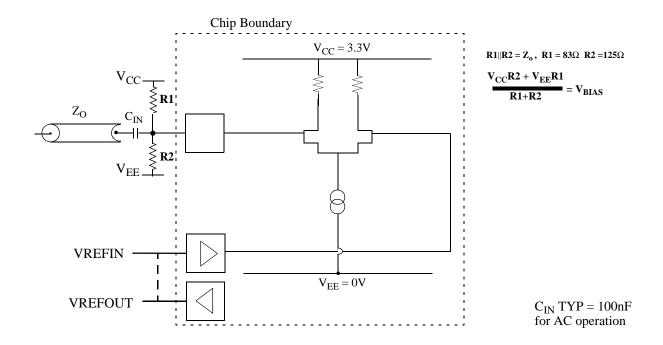

Figure 15: Termination of Low-Speed LVPECL TXIN[15:0] Inputs

### **Low-Speed Inputs**

The incoming low-speed inputs are received by single-ended LVPECL inputs TXIN[15:0]. A reference voltage is necessary to provide for optimal switching of the inputs. The user can either provide an input voltage reference from the upstream device (VREFIN), or can use the reference voltage provided from the VSC8140 (VREFOUT). Side-by-side placement of the VREFIN and VREFOUT pins facilitates easy implementation.

For DC or AC operation, the external reference should have a nominal value equivalent to the common-mode switch point of an LVPECL DC-coupled signal, and adhere to the DC characteristics as specified by the Table 3 DC characteristics ( $V_{CM}$ ).

Data Sheet VSC8140

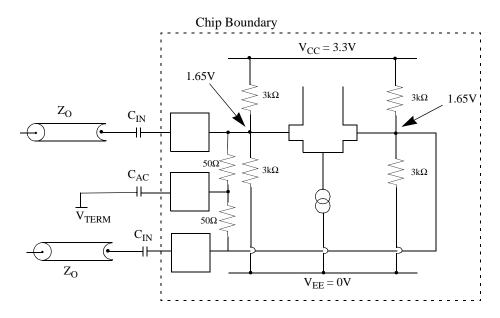

Figure 16: High-Speed Clock and High-Speed Data Inputs

$C_{IN} TYP = 100nF$

$C_{AC} TYP = 100nF$

### **High-Speed Clock and High-Speed Data Inputs**

The incoming high-speed data and high-speed clock are received by high-speed inputs RXIN and RXCLKIN. The inputs are internally biased to accommodate AC-coupling.

The data input receiver is internally terminated by a center-tapped resistor network. For differential input DC-coupling, the network is terminated to the appropriate termination voltage  $V_{TERM}$  providing a  $50\Omega$  to  $V_{TERM}$  termination for both true and complement inputs. For differential input AC-coupling, the network is terminated to  $V_{TERM}$  via a blocking capacitor.

In most situations, these inputs will have high transition density and little DC offset. However, in cases where this does not hold, direct DC connection is possible. All serial data and clock inputs have the same circuit topology, as shown in Figure 16. The reference voltage is created by a resistor divider as shown. If the input signal is driven differentially and DC-coupled to the part, the mid-point of the input signal swing should be centered about this reference voltage and not exceed the maximum allowable amplitude. For single-ended, DC-coupling operations, it is recommended that the user provides an external reference voltage which has better temperature and power supply noise rejection than the on-chip resistor divider. The external reference should have a nominal value equivalent to the common-mode switch point of the DC-coupled signal, and can be connected to either side of the differential gate.

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

#### **Supplies**

The VSC8140 is specified as a PECL device with a single positive 3.3V supply. Should the user desire to use the device in an ECL environment with a negative 3.3V supply, then  $V_{CC}$  will be ground and  $V_{EE}$  will be - 3.3V. If used with  $V_{EE}$  tied to -3.3V, the TTL control signals are still referenced to  $V_{EE}$ .

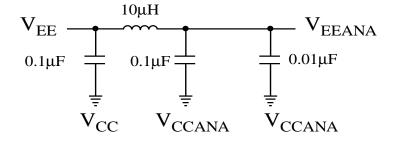

Decoupling of the power supplies is a critical element in maintaining the proper operation of the part. It is recommended that the  $V_{CC}$  power supply be decoupled using a  $0.1\mu F$  and  $0.01\mu F$  capacitor placed in parallel on each  $V_{CC}$  power supply pin as close to the package as possible. If room permits, a  $0.001\mu F$  capacitor should also be placed in parallel with the  $0.1\mu F$  and  $0.01\mu F$  capacitors mentioned above. Recommended capacitors are low-inductance ceramic SMT X7R devices. For the  $0.1\mu F$  capacitor, a 0603 package should be used. The  $0.01\mu F$  and  $0.001\mu F$  capacitors can be either 0603 or 0403 packages.

Extra care needs to be taken when decoupling the analog power supply pins (labeled  $V_{CCANA}$ ). In order to maintain the optimal jitter and loop bandwidth characteristics of the PLL contained in the VSC8140, the analog power supply pins should be filtered from the main power supply with a  $10\mu H$  C-L-C pi filter. If preferred, a ferrite bead may be used to provide the isolation. The  $0.1\mu F$  and  $0.01\mu F$  decoupling capacitors are still required and must be connected to the supply pins between the device and the C-L-C pi filter (or ferrite bead).

For low frequency decoupling,  $47\mu F$  tantalum low-inductance SMT caps are sprinkled over the board's main +3.3V power supply and placed close to the C-L-C pi filter.

If the device is being used in an ECL environment with a -3.3V supply, then all references to decoupling  $V_{CC}$  must be changed to  $V_{EE}$ , and all references to decoupling 3.3V must be changed to -3.3V.

Figure 17: PLL Power Supply Decoupling Scheme

Note:  $V_{CC}$  can be tied to  $V_{CCANA}$

Data Sheet VSC8140

### AC Characteristics

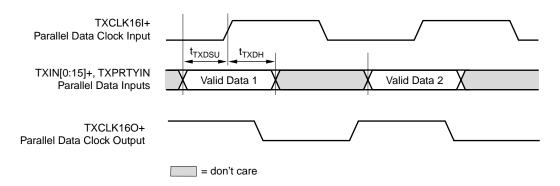

### Figure 18: Transmitter Parallel Data Timing Waveforms

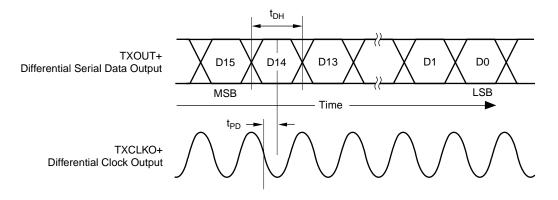

Figure 19: Transmitter Serial Data and Clock Phase Timing

NOTE: Bit 15 (MSB) is transmitted first, Bit 0 (LSB) is transmitted last.

**Figure 20: Transmitter Parity Timing**

2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

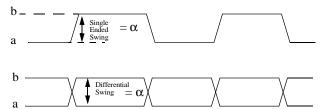

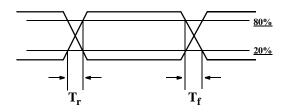

Figure 21: Differential and Single-Ended Input / Output Voltage Measurement

<sup>\*</sup> Differential swing ( $\alpha$ ) is specified as |b-a| (or |a-b|), as is the single-ended swing. Differential swing is specified as equal in magnitude to single-ended swing.

**Table 1: Transmitter AC Characteristics**

| Parameters                                       | Description                                           | Min  | Тур           | Max  | Units | Conditions                                                                                                                                         |

|--------------------------------------------------|-------------------------------------------------------|------|---------------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| $T_{\mathrm{D}}$                                 | TXCLK16I/TXCLK16O period                              |      | 6.4           |      | ns    |                                                                                                                                                    |

| T <sub>TXDSU</sub>                               | Data setup time to the rising edge of TXCLK16I+       | 0.75 |               |      | ns    |                                                                                                                                                    |

| $T_{TXDH}$                                       | Data hold time after the rising edge of TXCLK16I+     | 1.0  |               |      | ns    |                                                                                                                                                    |

| $T_{TXDOR}$ , $T_{TXDOF}$                        | TXOUT± rise and fall time                             |      |               | 120  | ps    | 20% to 80% into 100 $\Omega$ load. See Figure 13.                                                                                                  |

| TXCLK <sub>D</sub>                               | Transmit clock duty cycle                             | 40   |               | 60   | %     |                                                                                                                                                    |

| t <sub>TXCLK16R</sub> ,<br>t <sub>TXCLK16F</sub> | TXCLK16O± rise and fall times                         |      | 300           |      | ps    | See Figure 24                                                                                                                                      |

| TXCLK16O <sub>D</sub>                            | TXCLK16O± duty cycle                                  | 42   |               | 58   | %     |                                                                                                                                                    |

| TXCLK16I <sub>D</sub>                            | TXCLK16I± duty cycle                                  | 40   |               | 60   | %     | Assuming 10% distortion of TXCLK16O.                                                                                                               |

| RCK <sub>D</sub>                                 | Reference clock duty cycle                            | 40   |               | 60   | %     |                                                                                                                                                    |

| $T_{DV}$                                         | Parallel data to DINVALID                             |      | $3 t_D + 0.3$ |      | ns    |                                                                                                                                                    |

| $t_{DH}$                                         | TXCLKO period                                         |      | 401.9         |      | ps    |                                                                                                                                                    |

| t <sub>PD</sub>                                  | Center of output data eye from falling edge of TXCLKO | -75  |               | +75  | ps    | See Figure 19                                                                                                                                      |

| Clock Multiplie                                  | r Performance                                         |      |               |      |       |                                                                                                                                                    |

| $T_{\mathrm{DJ}}$                                | Output data jitter                                    |      |               | 4    | ps    | Tested to SONET specification (12kHz to 20MHz) with 2ps rms jitter on REFCLK. Normal mode operation, 500mV maximum per side on RXCLKIN.            |

| $T_{\mathrm{CJ}}$                                | Output clock jitter                                   |      |               | 4    | ps    | Tested to SONET specification<br>(12kHz to 20MHz) with 2ps rms<br>jitter on REFCLK. Normal mode<br>operation, 500mV maximum per<br>side on RXCLKIN |

|                                                  | Tuning Range                                          | -100 |               | +100 | ppm   |                                                                                                                                                    |

# Data Sheet VSC8140

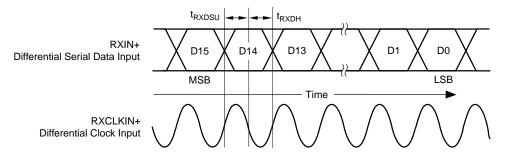

Figure 23: Receiver Setup and Hold Time Requirements

NOTE: Bit 15 (MSB) is received first, Bit 0 (LSB) is received last.

**Table 2: Receiver AC Characteristics**

| Parameters                                   | Description                                                    | Min | Тур | Max | Units               | Conditions                                             |

|----------------------------------------------|----------------------------------------------------------------|-----|-----|-----|---------------------|--------------------------------------------------------|

| t <sub>RXPDD</sub>                           | Data valid from falling edge of RXCLK16O+                      | 0   |     | 800 | ps                  |                                                        |

| t <sub>RXPD32</sub>                          | RXCLK32O transition from falling edge of RXCLK16O+             | 0   |     | 1.0 | ns                  |                                                        |

| t <sub>RXDR</sub> , t <sub>RXDF</sub>        | RXOUT[15:0]+/- rise and fall times                             |     | 300 |     | ps                  | 20% to 80% into DC termination.<br>See Figure 24.      |

| t <sub>RXCLKR</sub> ,<br>t <sub>RXCLKF</sub> | RXCLK16O+/- rise and fall times                                |     | 300 |     | ps                  | $20\%$ to $80\%$ into $100\Omega$ load. See Figure 24. |

| RXCLK16O <sub>D</sub>                        | RXCLK16O+/- duty cycle distortion                              | 45  |     | 55  | % of<br>clock cycle | High-speed clock input at 2.48832GHz.                  |

| t <sub>RXDSU</sub>                           | RXIN+ setup time with respect to falling edge of RXCLKIN+      | 100 |     |     | ps                  |                                                        |

| t <sub>RXDH</sub>                            | RXIN+ hold time with<br>respect to falling edge of<br>RXCLKIN+ | 75  |     |     | ps                  |                                                        |

| RXCLKIN <sub>D</sub>                         | RXCLKIN+/- duty cycle distortion                               | 40  |     | 60  | % of<br>clock cycle |                                                        |

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

### **DC Characteristics**

Table 3: DC Characteristics (Over recommended operating conditions)

| Parameter             | Description                                                            | Min                                   | Тур  | Max                                   | Units | Conditions                                                              |

|-----------------------|------------------------------------------------------------------------|---------------------------------------|------|---------------------------------------|-------|-------------------------------------------------------------------------|

| V <sub>OHHSO</sub>    | Output HIGH voltage (TXOUT, TXCLKOUT)                                  | V <sub>CC</sub> -0.40                 |      | V <sub>CC</sub> <sup>(1)</sup>        | V     | $50\Omega$ termination to $V_{CC}$                                      |

| V <sub>OLHSO</sub>    | Output LOW voltage (TXOUT, TXCLKOUT)                                   | V <sub>CC</sub> -1.20 <sup>(1)</sup>  |      | V <sub>CC</sub> -0.50                 | V     | $50\Omega$ termination to $V_{CC}$                                      |

| $\Delta V_{ m ODHSO}$ | Output differential voltage<br>(TXCLKOUT)                              | 450                                   | 600  | 1000                                  | mV    | 100Ω termination between ± output at load. See Figure 13.               |

|                       | Output differential voltage (TXOUT)                                    | 500                                   | 600  | 1000                                  |       | output at load. See Figure 13.                                          |

| V <sub>CMHSO</sub>    | Output common-mode voltage                                             | V <sub>CC</sub> -1.20                 |      | V <sub>CC</sub> -0.300                | V     | $100\Omega$ termination between ± output at load. See Figure 13.        |

| R <sub>HSO</sub>      | Back termination impedance                                             | 40                                    |      | 60                                    | Ω     | See Note 1                                                              |

| $\Delta V_{IHS}$      | Serial input differential voltage<br>(RXIN, RXCLKIN)                   | 200                                   |      | 500                                   | mV    | AC-coupled, internally biased to (V <sub>CC</sub> +V <sub>EE</sub> )/2. |

| V <sub>OHL</sub>      | Output HIGH voltage (LVPECL)                                           | V <sub>CC</sub> -1.020                |      | V <sub>CC</sub> -0.700 <sup>(1)</sup> | V     | See Figure 24                                                           |

| V <sub>OL</sub>       | Output LOW voltage (LVPECL)                                            | V <sub>CC</sub> -2.000 <sup>(1)</sup> |      | V <sub>CC</sub> -1.620                | V     | See Figure 24                                                           |

| $\Delta V_{\rm O}$    | Low-speed output voltage single-<br>ended, peak-to-peak swing (LVPECL) | 600                                   |      | 1300 <sup>(1)</sup>                   | mV    | See Figure 24                                                           |

| V <sub>IH</sub>       | Input HIGH voltage (LVPECL)                                            | V <sub>CC</sub> -1.100                |      | $V_{CC}$ -0.700 <sup>(1)</sup>        | V     |                                                                         |

| V <sub>IL</sub>       | Input LOW voltage(LVPECL)                                              | $V_{CC}$ -2.0 <sup>(1)</sup>          |      | V <sub>CC</sub> -1.540                | V     |                                                                         |

| I <sub>IH</sub>       | Input HIGH current (LVPECL)                                            |                                       |      | 200                                   | μΑ    | V <sub>IN</sub> =V <sub>IH</sub> (max)                                  |

| $I_{IL}$              | Input LOW current (LVPECL)                                             | -100                                  |      |                                       | μΑ    | V <sub>IN</sub> =V <sub>IL</sub> (min)                                  |

| R <sub>i</sub>        | Input Resistance (LVPECL)                                              |                                       | 10   |                                       | kΩ    |                                                                         |

| $\Delta V_{\rm I}$    | Input differential voltage (LVPECL)                                    | 200                                   |      |                                       | mV    |                                                                         |

| V <sub>CM</sub>       | Input common-mode voltage (LVPECL)                                     | V <sub>CC</sub> -1.5                  |      | V <sub>CC</sub> -0.5                  | V     |                                                                         |

| V <sub>OH</sub>       | Output HIGH voltage (TTL)                                              | 2.4                                   |      |                                       | V     | $I_{OH} = -1.0 \text{mA}$                                               |

| V <sub>OL</sub>       | Output LOW voltage (TTL)                                               |                                       |      | 0.5                                   | V     | $I_{OL} = +1.0$ mA                                                      |

| V <sub>IH</sub>       | Input HIGH voltage (TTL)                                               | 2.0                                   |      | 5.5 <sup>(1)</sup>                    | V     |                                                                         |

| V <sub>IL</sub>       | Input LOW voltage (TTL)                                                | $0.0^{(1)}$                           |      | 0.8                                   | V     |                                                                         |

| I <sub>IH</sub>       | Input HIGH Current (TTL)                                               |                                       |      | 500                                   | μΑ    | $V_{IN} = 2.4V$                                                         |

| $I_{IL}$              | Input LOW current (TTL)                                                |                                       |      | -500                                  | μΑ    | $V_{IN} = 0.5V$                                                         |

| V <sub>CC</sub>       | Supply voltage                                                         | 3.14                                  |      | 3.47                                  | V     | 3.3V± 5%                                                                |

| $P_{\mathrm{D}}$      | Power dissipation                                                      |                                       | 2.25 | 2.75                                  | W     | Outputs open, TXCLKOUT powered down                                     |

| I <sub>CC</sub>       | Supply current                                                         |                                       |      | 850                                   | mA    | Outputs open                                                            |

NOTE: (1) Guaranteed but not tested to cover these conditions.

Data Sheet VSC8140

Figure 24: Parametric Measurement Information

**PECL Rise and Fall Time**

### **Parametric Test Load Circuit**

### **Serial Output Load**

## Absolute Maximum Ratings (1)

| Power Supply Voltage (V <sub>CC</sub> ) | 0.5V to +3.8V           |

|-----------------------------------------|-------------------------|

| DC Input Voltage (differential inputs)  |                         |

| DC Input Voltage (TTL inputs)           | 0.5V to +5.5V           |

| DC Output Voltage (TTL outputs)         | 0.5V to $V_{CC} + 0.5V$ |

| Output Current (TTL outputs)            | +/-50mA                 |

| Output Current (differential outputs)   | +/-50mA                 |

| Case Temperature Under Bias             | 55°C to +125°C          |

## **Recommended Operating Conditions**

| Power Supply Voltage (V <sub>CC</sub> ) | +3.3V <u>+</u> 5% |

|-----------------------------------------|-------------------|

| Operating Temperature Range             |                   |

NOTE: (1) CAUTION: Stresses listed under "Absolute Maximum Ratings" may be applied to devices one at a time without causing permanent damage. Functionality at or above the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

## **ESD Ratings**

Proper ESD procedures should be used when handling this product. The VSC8140 is rated to the following ESD voltages based on the human body model:

1. All pins are rated at or above 1500V.

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

## Package Pin Descriptions

### Table 4: Package Pin Identification - 128 PQFP

| Pin# | Name      | I/O | Level      | Description                                                     |

|------|-----------|-----|------------|-----------------------------------------------------------------|

| 1    | OVERFLOW  | О   | TTL        | FIFO overflow indication                                        |

| 2    | VEET      | Pwr | GND typ.   | TTL V <sub>EE</sub> power supply                                |

| 3    | VCCT      | Pwr | +3.3V typ. | TTL V <sub>CC</sub> power supply                                |

| 4    | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 5    | HSDREF    | I   | 0V->3.3V   | High-speed data input termination voltage reference             |

| 6    | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 7    | RXIN+     | I   | HS         | High-speed data input, true                                     |

| 8    | RXIN-     | I   | HS         | High-speed data input, complement                               |

| 9    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 10   | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 11   | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 12   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 13   | RXCLKIN-  | I   | HS         | High-speed clock input, complement                              |

| 14   | HSCLKREF  | I   | 0V->3.3V   | High-speed clock input termination voltage reference            |

| 15   | RXCLKIN+  | I   | HS         | High-speed clock Input, true                                    |

| 16   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 17   | NC        |     |            | No connect, leave unconnected <sup>(1)</sup>                    |

| 18   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 19   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 20   | TXOUT+    | О   | HS         | High-speed data output, true                                    |

| 21   | TXOUT-    | О   | HS         | High-speed data output, complement                              |

| 22   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 23   | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 24   | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 25   | VEE       | Pwr | GND typ.   | Negative power supply                                           |

| 26   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 27   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 28   | TXCLKOUT+ | О   | HS         | High-speed clock output, true                                   |

| 29   | TXCLKOUT- | О   | HS         | High-speed clock output, complement                             |

| 30   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 31   | VEEP_CLK  | Pwr | GND typ.   | HS clock $V_{EE}$ power supply (tie to $V_{CC}$ for power down) |

| 32   | VEEP_CLK  | Pwr | GND typ.   | HS clock $V_{EE}$ power supply (tie to $V_{CC}$ for power down) |

| 33   | VEE_PWRDN | Pwr | GND typ.   | HS clock $V_{EE}$ power supply (tie to $V_{CC}$ for power down) |

| 34   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 35   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

| 36   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                           |

# Data Sheet VSC8140

### Table 4: Package Pin Identification - 128 PQFP

| Pin # | Name        | I/O | Level      | Description                                                                  |

|-------|-------------|-----|------------|------------------------------------------------------------------------------|

| 37    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| 38    | FACLOOP     | I   | TTL        | Facility loopback, active high                                               |

| 39    | LOOPTIM0    | I   | TTL        | Enable internal looptiming operation, active high                            |

| 40    | PARMODE     | I   | TTL        | Parity mode select                                                           |

| 41    | FIFORESET   | I   | TTL        | Reset to align FIFO write and read pointers                                  |

| 42    | LOOPTIM1    | I   | TTL        | Enable external loop timing operation, active high                           |

| 43    | REF_FREQSEL | I   | TTL        | Reference clock input select                                                 |

| 44    | LPTIMCLK+   | I   | LVPECL     | External loop timing clock, true                                             |

| 45    | LPTIMCLK-   | I   | LVPECL     | External loop timing clock, complement                                       |

| 46    | VCC_ANA     | Pwr | +3.3V typ. | Positive power supplys for analog parts of CMU                               |

| 47    | VEE_ANA     | Pwr | GND typ.   | Negative power supplys for analog parts of CMU                               |

| 48    | REFCLK+     | I   | LVPECL     | Reference clock input, true                                                  |

| 49    | REFCLK-     | I   | LVPECL     | Reference clock input, complement                                            |

| 50    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| 51    | FILTAO      |     |            | Loop filter pin - connect via capacitor to FILTAI (pin 53)                   |

| 52    | FILTAON     |     |            | Loop filter pin - connect via capacitor to FILTAIN (pin 54)                  |

| 53    | FILTAI      |     |            | Loop filter pin - connect via capacitor to FILTAO (pin 51)                   |

| 54    | FILTAIN     |     |            | Loop filter pin - connect via capacitor to FILTAON (pin 52)                  |

| 55    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| 56    | TXCLK16O+   | О   | LVPECL     | Low-speed clock output, true. A divide-by-16 version of the PLL clock.       |

| 57    | TXCLK16O-   | О   | LVPECL     | Low-speed clock output, complement. A divide-by-16 version of the PLL clock. |

| 58    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| 59    | TXCLK16I-   | I   | LVPECL     | Low-speed clock input for latching low-speed data, complement                |

| 60    | TXCLK16I+   | I   | LVPECL     | Low-speed clock input for latching low-speed data, true                      |

| 61    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| 62    | TXPARITYIN  | I   | LVPECL     | Transmitter parity bit input                                                 |

| 63    | TXIN15      | I   | LVPECL     | Low-speed single-ended data (MSB) <sup>(2)</sup>                             |

| 64    | TXIN14      | I   | LVPECL     | Low-speed single-ended data                                                  |

| 65    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| 66    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| 67    | TXIN13      | I   | LVPECL     | Low-speed single-ended data                                                  |

| 68    | TXIN12      | I   | LVPECL     | Low-speed single-ended data                                                  |

| 69    | TXIN11      | I   | LVPECL     | Low-speed single-ended data                                                  |

| 70    | TXIN10      | I   | LVPECL     | Low-speed single-ended data                                                  |

| 71    | TXIN9       | I   | LVPECL     | Low-speed single-ended data                                                  |

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

Table 4: Package Pin Identification - 128 PQFP

| Pin# | Name    | I/O | Level     | Description                                                                     |

|------|---------|-----|-----------|---------------------------------------------------------------------------------|

| 72   | VEE     | Pwr | GND typ.  | Negative power supply                                                           |

| 73   | TXIN8   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 74   | TXIN7   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 75   | TXIN6   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 76   | TXIN5   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 77   | TXIN4   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 78   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 79   | TXIN3   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 80   | TXIN2   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 81   | VEE     | Pwr | GND typ.  | Negative power supply                                                           |

| 82   | TXIN1   | I   | LVPECL    | Low-speed single-ended data                                                     |

| 83   | TXIN0   | I   | LVPECL    | Low-speed single-ended data (LSB) <sup>(2)</sup>                                |

| 84   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 85   | VREFIN  | I   | Voltage   | Voltage reference for single-ended TXIN V <sub>CM</sub> or VREFOUT              |

| 86   | VREFOUT | О   | Voltage   | Voltage reference for single-ended RXOUT (V <sub>OH</sub> +V <sub>OL</sub> )/2. |

| 87   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 88   | RXOUT0  | О   | LVPECL    | Low-speed single-ended data (LSB) <sup>(2)</sup>                                |

| 89   | RXOUT1  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 90   | VEE     | Pwr | GND typ.  | Negative power supply                                                           |

| 91   | RXOUT2  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 92   | RXOUT3  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 93   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 94   | RXOUT4  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 95   | RXOUT5  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 96   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 97   | RXOUT6  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 98   | RXOUT7  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 99   | VEE     | Pwr | GND typ.  | Negative power supply                                                           |

| 100  | RXOUT8  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 101  | RXOUT9  | О   | LVPECL    | Low-speed single-ended data                                                     |

| 102  | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 103  | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 104  | RXOUT10 | 0   | LVPECL    | Low-speed single-ended data                                                     |

| 105  | RXOUT11 | 0   | LVPECL    | Low-speed single-ended data                                                     |

| 106  | RXOUT12 | 0   | LVPECL    | Low-speed single-ended data                                                     |

| 107  | VCC     | Pwr | 3.3V typ. | Positive power supply                                                           |

| 108  | RXOUT13 | 0   | LVPECL    | Low-speed single-ended data                                                     |

# Data Sheet VSC8140

### Table 4: Package Pin Identification - 128 PQFP

| Pin # | Name           | I/O | Level     | Description                                      |

|-------|----------------|-----|-----------|--------------------------------------------------|

| 109   | RXOUT14        | О   | LVPECL    | Low-speed single-ended data                      |

| 110   | VEE            | Pwr | GND typ.  | Negative power supply                            |

| 111   | RXOUT15        | О   | LVPECL    | Low-speed single-ended data (MSB) <sup>(2)</sup> |

| 112   | RXPARITYOUT    | О   | LVPECL    | Receiver parity bit output                       |

| 113   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| 114   | RXCLK16O-      | О   | LVPECL    | Parallel clock output (155.52MHz), complement    |

| 115   | RXCLK16O+      | О   | LVPECL    | Parallel clock output (155.52MHz), true          |

| 116   | VEE            | Pwr | GND typ.  | Negative power supply                            |

| 117   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| 118   | RXCLK16_32O-   | О   | LVPECL    | Divide-by-16 or -32 clock output, complement     |

| 119   | RXCLK16_32O+   | О   | LVPECL    | Divide-by-16 or -32 clock output, true           |

| 120   | CLK128O-       | О   | LVPECL    | Divide-by-128 clock output, complement           |

| 121   | CLK128O+       | О   | LVPECL    | Divide-by-128 clock output, true                 |

| 122   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| 123   | RXCLKO_FREQSEL | I   | TTL       | RXCLKO16_32 frequency select                     |

| 124   | LOS            | I   | TTL       | Loss of Signal control                           |

| 125   | POL            | I   | TTL       | Polarity Signal Control                          |

| 126   | EQULOOP        | I   | TTL       | Equipment loopback, active high                  |

| 127   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| 128   | PARERR         | 0   | TTL       | Parity error output                              |

NOTES: (1) No connect (NC) pin must be left unconnected. Connecting this pin to either the positive or negative power supply rails may cause improper operation or failure of the device; or in extreme cases, cause permanent damage to the device.

<sup>(2)</sup> There has been a change in the naming of the pins of the Low-Speed Parallel Receive and Transmit pins of the VSC8140. RXOUT0; pin 88 (MSB) has been changed to RXOUT15; pin 111 (MSB) and TXIN15; pin 63 (LSB) has been changed to TXIN0; pin 83 (LSB).

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

## Package Information

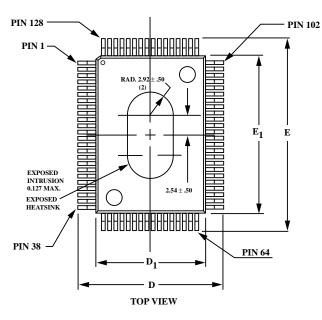

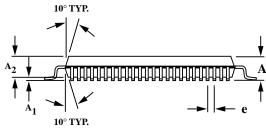

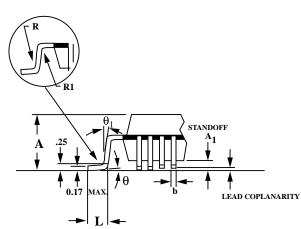

### 128 PQFP Package Drawings

| Key | mm    | Tolerance |

|-----|-------|-----------|

| A   | 2.35  | MAX       |

| A1  | 0.25  | MAX       |

| A2  | 2.00  | +.10      |

| D   | 17.20 | ±.20      |

| D1  | 14.00 | ±.10      |

| Е   | 23.20 | ±.20      |

| E1  | 20.00 | ±.10      |

| L   | .88   | +.15/10   |

| e   | .50   | BASIC     |

| b   | .22   | ±.05      |

| q   | 0°-7° |           |

| R   | .30   | TYP       |

| R1  | .20   | TYP       |

Drawing is not to scale All dimensions in mm

Package represented is also used for the 64, 80, & 100 PQFP packages. not reflect the 128 Package.

NOTES:

Package #: 101-322-5 Issue #: 2

# Data Sheet VSC8140

## Package Pin Descriptions

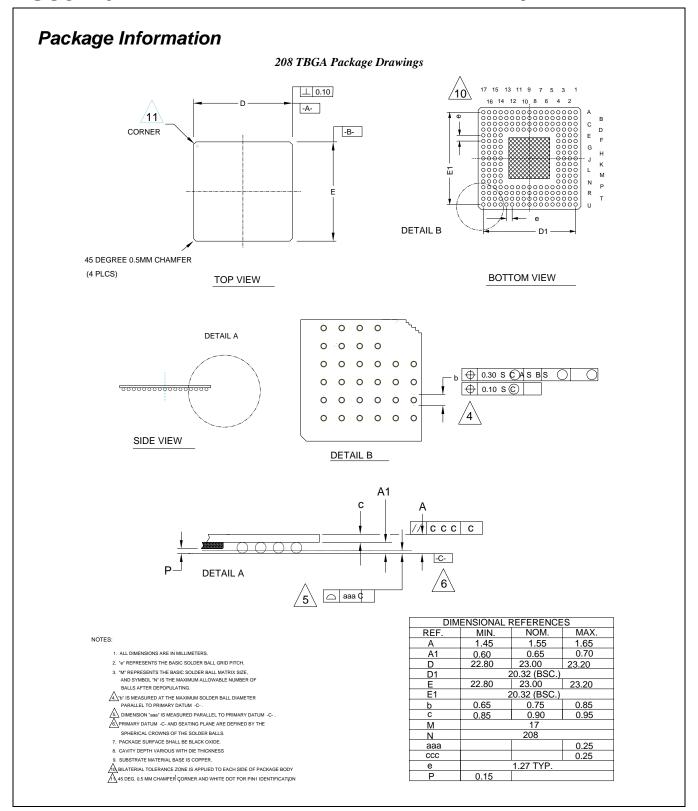

Table 5: Package Pin Identification - 208 BGA

| Pin # | Name      | I/O | Level      | Description                                                                   |

|-------|-----------|-----|------------|-------------------------------------------------------------------------------|

| B17   | OVERFLOW  | О   | TTL        | FIFO overflow indication                                                      |

| B16   | VEET      | Pwr | GND typ.   | TTL V <sub>EE</sub> power supply                                              |

| B15   | VCCT      | Pwr | +3.3V typ. | TTL V <sub>CC</sub> power supply                                              |

| C14   | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| D13   | HSDREF    | I   | 0V->3.3V   | High-speed data input termination voltage reference                           |

| A16   | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| B14   | RXIN+     | I   | HS         | High-speed data input, true                                                   |

| B13   | RXIN-     | I   | HS         | High-speed data input, complement                                             |

| A14   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| A13   | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| D11   | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| C11   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| B11   | RXCLKIN-  | I   | HS         | High-speed clock input, complement                                            |

| D10   | HSCLKREF  | I   | 0V->3.3V   | High-speed clock input termination voltage reference                          |

| B10   | RXCLKIN+  | I   | HS         | High-speed clock input, true                                                  |

| A10   | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| В9    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| D9    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| A9    | TXOUT+    | О   | HS         | High-speed data output, true                                                  |

| A8    | TXOUT-    | О   | HS         | High-speed data output, complement                                            |

| C8    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| D8    | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| A7    | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| A6    | VEE       | Pwr | GND typ.   | Negative power supply                                                         |

| D7    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| A5    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| A4    | TXCLKOUT+ | О   | HS         | High-speed clock output, true                                                 |

| A3    | TXCLKOUT- | О   | HS         | High-speed clock output, complement                                           |

| B4    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

| D5    | VEEP_CLK  | Pwr | GND typ.   | HS clock V <sub>EE</sub> power supply (tie to V <sub>CC</sub> for power down) |

| A2    | VEEP_CLK  | Pwr | GND typ.   | HS clock V <sub>EE</sub> power supply (tie to V <sub>CC</sub> for power down) |

| A1    | VEE_PWRDN | Pwr | GND typ.   | HS clock V <sub>EE</sub> power supply (tie to V <sub>CC</sub> for power down) |

| C4    | VCC       | Pwr | 3.3V typ.  | Positive power supply                                                         |

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

Table 5: Package Pin Identification - 208 BGA

| Pin # | Name        | I/O | Level      | Description                                                                  |

|-------|-------------|-----|------------|------------------------------------------------------------------------------|

| В3    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| D4    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| C3    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| C1    | FACLOOP     | I   | TTL        | Facility loopback, active high                                               |

| F4    | LOOPTIM0    | I   | TTL        | Enable internal looptiming operation, active high                            |

| F3    | PARMODE     | I   | TTL        | Parity mode select                                                           |

| D1    | FIFORESET   | I   | TTL        | Reset to align FIFO write and read pointers                                  |

| E1    | LOOPTIM1    | I   | TTL        | Enable external loop timing operation, active high                           |

| G4    | REF_FREQSEL | I   | TTL        | Reference clock input select                                                 |

| G3    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| F2    | LPTIMCLK+   | I   | LVPECL     | External loop timing clock, true                                             |

| G2    | LPTIMCLK-   | I   | LVPECL     | External loop timing clock, complement                                       |

| F1    | VCC_ANA     | Pwr | +3.3V typ. | Positive power supplies for analog parts of CMU                              |

| НЗ    | VEE_ANA     | Pwr | GND typ.   | Negative power supplies for analog parts of CMU                              |

| H2    | REFCLK+     | I   | LVPECL     | Reference clock input, true                                                  |

| G1    | REFCLK-     | I   | LVPECL     | Reference clock input,complement                                             |

| H1    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| J2    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| J4    | FILTAO      |     |            | Loop filter pin - connect via capacitor to FILTAI (pin 53)                   |

| J3    | FILTAON     |     |            | Loop filter pin - connect via capacitor to FILTAIN (pin 54)                  |

| K1    | FILTAI      |     |            | Loop filter pin - connect via capacitor to FILTAO (pin 51)                   |

| K2    | FILTAIN     |     |            | Loop filter pin - connect via capacitor to FILTAON (pin 52)                  |

| К3    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| K4    | TXCLK16O+   | О   | LVPECL     | Low-speed clock output, true. A divide-by-16 version of the PLL clock.       |

| L1    | TXCLK16O-   | О   | LVPECL     | Low-speed clock output, complement. A divide-by-16 version of the PLL clock. |

| M1    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

| L2    | TXCLK16I-   | I   | LVPECL     | Low-speed clock input for latching low-speed data, complement                |

| L3    | TXCLK16I+   | I   | LVPECL     | Low-speed clock input for latching low-speed data, true                      |

| L4    | VCC         | Pwr | 3.3V typ.  | Positive power supply                                                        |

| M2    | TXPARITYIN  | I   | LVPECL     | Transmitter parity bit input                                                 |

| M3    | TXIN15      | I   | LVPECL     | Low-speed single-ended data (MSB) <sup>(1)</sup>                             |

| M4    | TXIN14      | I   | LVPECL     | Low-speed single-ended data                                                  |

| P1    | VEE         | Pwr | GND typ.   | Negative power supply                                                        |

# Data Sheet VSC8140

Table 5: Package Pin Identification - 208 BGA

| Pin # | Name    | I/O | Level     | Description                                                                    |  |

|-------|---------|-----|-----------|--------------------------------------------------------------------------------|--|

| Т3    | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| P5    | TXIN13  | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| R5    | TXIN12  | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| T4    | TXIN11  | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| P6    | TXIN10  | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| T5    | TXIN9   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| R6    | VEE     | Pwr | GND typ.  | Negative power supply                                                          |  |

| U5    | TXIN8   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| R7    | TXIN7   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| Т6    | TXIN6   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| U6    | TXIN5   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| P8    | TXIN4   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| R8    | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| Т8    | TXIN3   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| U7    | TXIN2   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| U8    | VEE     | Pwr | GND typ.  | Negative power supply                                                          |  |

| Т9    | TXIN1   | I   | LVPECL    | Low-speed single-ended data                                                    |  |

| P9    | TXIN0   | I   | LVPECL    | Low-speed single-ended data (LSB) <sup>(1)</sup>                               |  |

| R9    | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| U9    | VREFIN  | I   | Voltage   | Voltage reference for single-ended TXIN V <sub>CM</sub> or VREFOUT             |  |

| U10   | VREFOUT | О   | Voltage   | Voltage reference for single-ended RXOUT (V <sub>OH</sub> +V <sub>OL</sub> )/2 |  |

| T10   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| R10   | RXOUT0  | О   | LVPECL    | Low-speed single-ended data (LSB) <sup>(1)</sup>                               |  |

| P10   | RXOUT1  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| U11   | VEE     | Pwr | GND typ.  | Negative power supply                                                          |  |

| U12   | RXOUT2  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| T11   | RXOUT3  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| R11   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| P11   | RXOUT4  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| U13   | RXOUT5  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| T12   | VCC     | Pwr | 3.3V typ. | Positive power supply                                                          |  |

| T13   | RXOUT6  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| R12   | RXOUT7  | О   | LVPECL    | Low-speed single-ended data                                                    |  |

| P12   | VEE     | Pwr | GND typ.  | Negative power supply                                                          |  |

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

Table 5: Package Pin Identification - 208 BGA

| Pin # | Name           | I/O | Level     | Description                                      |

|-------|----------------|-----|-----------|--------------------------------------------------|

| U14   | RXOUT8         | 0   | LVPECL    | Low-speed single-ended data                      |

| U15   | RXOUT9         | О   | LVPECL    | Low-speed single-ended data                      |

| R13   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| N16   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| P17   | RXOUT10        | О   | LVPECL    | Low-speed single-ended data                      |

| L14   | RXOUT11        | О   | LVPECL    | Low-speed single-ended data                      |

| L15   | RXOUT12        | О   | LVPECL    | Low-speed single-ended data                      |

| M16   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| L16   | RXOUT13        | О   | LVPECL    | Low-speed single-ended data                      |

| M17   | RXOUT14        | О   | LVPECL    | Low-speed single-ended data                      |

| K14   | VEE            | Pwr | GND typ.  | Negative power supply                            |

| K15   | RXOUT15        | 0   | LVPECL    | Low-speed single-ended data (MSB) <sup>(1)</sup> |

| K16   | RXPARITYOUT    | О   | LVPECL    | Receiver Parity bit output                       |

| L17   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| J17   | RXCLK16O-      | О   | LVPECL    | Parallel clock output (155.52MHz), complement    |

| H17   | RXCLK16O+      | О   | LVPECL    | Parallel clock output (155.52MHz), true          |

| H16   | VEE            | Pwr | GND typ.  | Negative power supply                            |

| H15   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| H14   | RXCLK16_32O-   | О   | LVPECL    | Divide-by-16 or -32 clock output, complement     |

| G17   | RXCLK16_32O+   | О   | LVPECL    | Divide-by-16 or -32 clock output, true           |

| F17   | CLK128O-       | 0   | LVPECL    | Divide-by-128 clock output, complement           |

| G16   | CLK128O+       | 0   | LVPECL    | Divide-by-128 clock output, true                 |

| G15   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| G14   | RXCLKO_FREQSEL | I   | TTL       | RXCLKO16_32 frequency select                     |

| D17   | LOS            | I   | TTL       | Loss of Signal control                           |

| C17   | POL            | I   | TTL       | Polarity Signal Control                          |

| E15   | EQULOOP        | I   | TTL       | Equipment loopback, active high                  |

| D16   | VCC            | Pwr | 3.3V typ. | Positive power supply                            |

| E14   | PARERR         | O   | TTL       | Parity error output                              |

| A17   | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

| A15   | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

| A12   | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

| A11   | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

| B12   | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

| В8    | NC             |     |           | No connect, leave unconnected <sup>(2)</sup>     |

# Data Sheet VSC8140

### Table 5: Package Pin Identification - 208 BGA

| Pin # | Name | I/O | Level | Description                                  |

|-------|------|-----|-------|----------------------------------------------|

| B7    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| В6    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| B5    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| B2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| B1    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C13   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C12   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C10   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C9    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C7    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C6    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C5    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| C2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D12   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D6    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D3    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| D2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| E17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| E16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| E4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| E3    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| E2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| F16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| F15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| F14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| H4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| J16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| J15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| J14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| J1    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| K17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

## 2.48832Gb/s 16:1 SONET/SDH Transceiver with Integrated Clock Generator

### Table 5: Package Pin Identification - 208 BGA

| Pin # | Name | I/O | Level | Description                                  |

|-------|------|-----|-------|----------------------------------------------|

| M15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| M14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N3    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| N1    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P13   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P7    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| Р3    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| P2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R3    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| R1    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T15   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T14   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| Т7    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T2    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| T1    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| U17   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| U16   | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

| U4    | NC   |     |       | No connect, leave unconnected <sup>(2)</sup> |

# Data Sheet VSC8140

### Table 5: Package Pin Identification - 208 BGA

| Pin # | Name | I/O | Level | Description                                  |