Vendor PN:VT1165MFQX

**VOLTERRA**

PRELIMINARY

# VT1165M CHIPSET

REVISION - December 8, 2005

# PROGRAMMABLE OUTPUT, MULTIPHASE SWITCHING REGULATOR WITH SMBus

| Smart<br>Slave™ | Current<br>Rating | Input<br>Voltage | Output<br>Voltage | VID                                   |

|-----------------|-------------------|------------------|-------------------|---------------------------------------|

| VT1105S*        | 25A per           |                  | 0.800V<br>to      | VRMs 9,                               |

| VT1125S         | Phase             | 10.8V to         | 1.850V            | 10.X, and                             |

| VT1115S         | 30A per           | 13.2V            | or<br>0.450V      | Opteron <sup>™</sup> or<br>Serial VID |

| VT1135S         | Phase             |                  | to<br>2.0375V     | (SVID) Mode                           |

### **GENERAL DESCRIPTION**

The VT1165M chipset, Volterra's fourth-generation chipset, is a complete, integrated, scalable architecture for the highest density multi-phase synchronous buck regulators. This ultra high density solution minimizes external components and offers enhanced regulator performance, comprehensive control and reporting features, ease of design and the smallest footprint available for demanding multi-phase synchronous buck converters. The chipset is targeted for applications such as servers and networking systems.

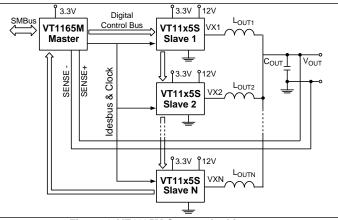

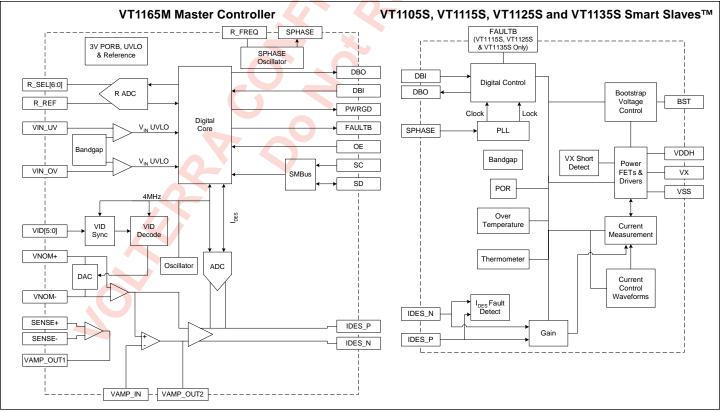

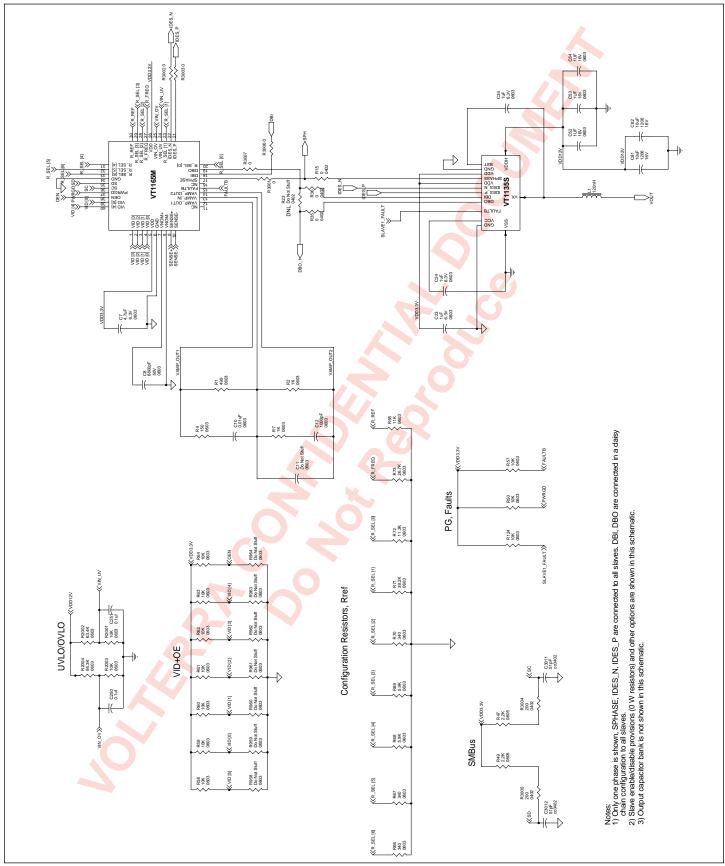

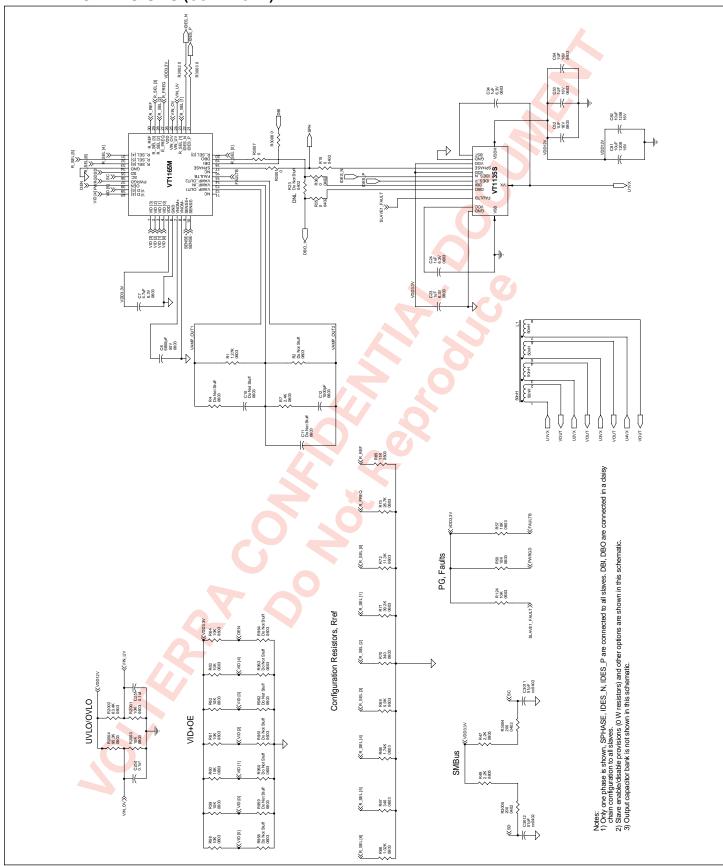

The VT1165M system architecture consists of a master controller (VT1165M), multiple Smart Slave<sup>™</sup> integrated output devices, input capacitors, output capacitors and output inductors. The actual number of Smart Slaves<sup>™</sup> can be set by the designer and application requirements. The desired slave and load operating conditions are controlled and monitored via an interconnecting digital bus as shown in Figure 1.

With this chipset, Volterra implements enhancements to the digital SMBus interface for monitoring and controlling of the voltage regulator. Regulator parameters can be set and monitored via the two-way SMBus for control, protection and shutdown of the regulator. The SMBus can provide a reading of faults such as VX short-circuit or slave over-temperature, so that the regulator can be controlled and protected during all operating conditions. The SMBus can also provide temperature readings of individual slaves.

A key benefit of the VT1165M is that it provides excellent scalability. This flexibility allows the designer to trade-off cost and performance for a given application using one VT1165M controller and different slave configurations with no redesign or re-layout. The number of phases can be determined by the designer and easily populated or de-populated to meet different load and performance targets.

#### \*NOTE: The VT1165M, VT1115S, VT1125S & VT1135S have a status of PRELIMINARY. The VT1105S has a status of NEW PRODUCT. See the back page of this datasheet for details on these statuses.

#### **KEY FEATURES**

- Smallest Footprint: Typical Solution Occupies Less than 1600mm<sup>2</sup> in a 150A VRM Application

- Lowest Profile: 5mm Maximum Height

- Highest Accuracy Current Sharing

- Differential Voltage Sense at Point of Load

- 1A/ns Step Load Transient Response

- Scalable Output Current: Up to 8 Slaves

- Slave Temperature Reporting

- Compatible with Coupled Inductors

- Programmable Switching Frequency: 500kHz-1.5MHz

- 6-Bit VID Input, with 12.5mV Steps and Setpoint Trim for Programmable V<sub>OUT</sub>

- Intel<sup>®</sup> VRM 9: 1.100V-1.850V

- Intel® VRM 10.X: 0.8375V-1.6000V

- AMD<sup>®</sup> Opteron<sup>™</sup>: 0.800V-1.550V

- Serial VID (SVID) Mode: 0.450V-2.0375V

- Dynamic VID

- Programmable VID via SMBUS

- Programmable Setpoint and Droop

- Programmable OVP, OVLO and UVLO

- Cycle-by-Cycle Current Limiting

- Power Good Flag, Fault Flag and Output Enable

#### SYSTEMS

- Servers and Workstations

- Enterprise Storage

- Broadband Communication & Networking

- Small Form Factor Desktops

#### APPLICATIONS

Voltage Regulator Modules (VRMs) and On-Board Regulators (VR Down)

- Microprocessors (μP): 32 and 64 Bit I/A and RISC Architectures

- Memory

- Graphics Processors

- Network, Chipset ICs

#### **BASIC APPLICATION CIRCUIT**

Figure 1. VT1165M System Architecture

#### **ORDERING INFORMATION**

| Part Number   | IC             | Package Style | Drawing Number | Shipment Method   | Package Marking |

|---------------|----------------|---------------|----------------|-------------------|-----------------|

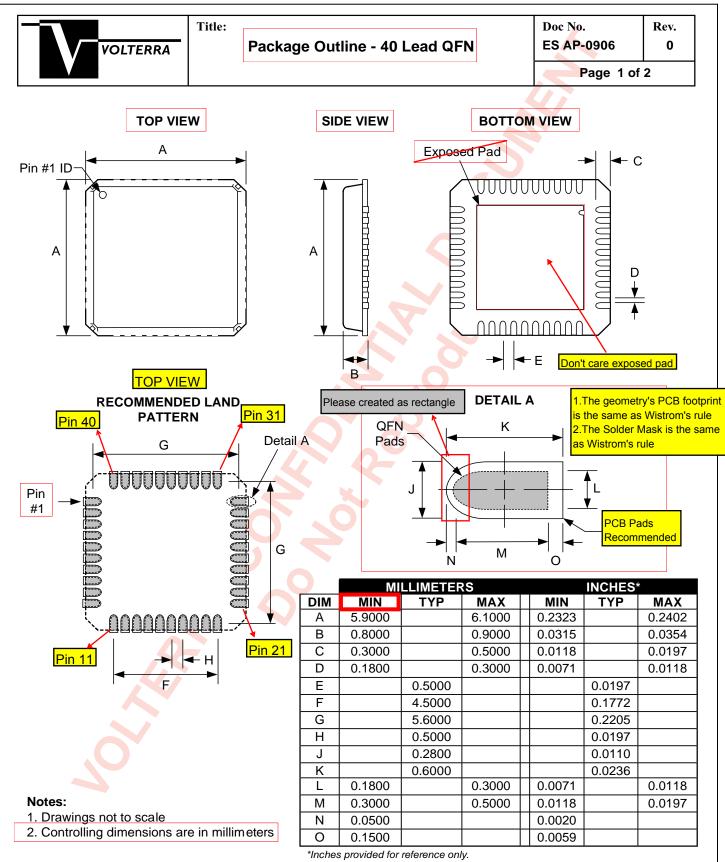

| VT1165MQ      | Master         | QFN-40        | ES AP-0906     | Trays 🔶           | VT1165M         |

| VT1165MQX     | waster         | QFN-40        | ES AP-0906     | 2.5ku Tape & Reel |                 |

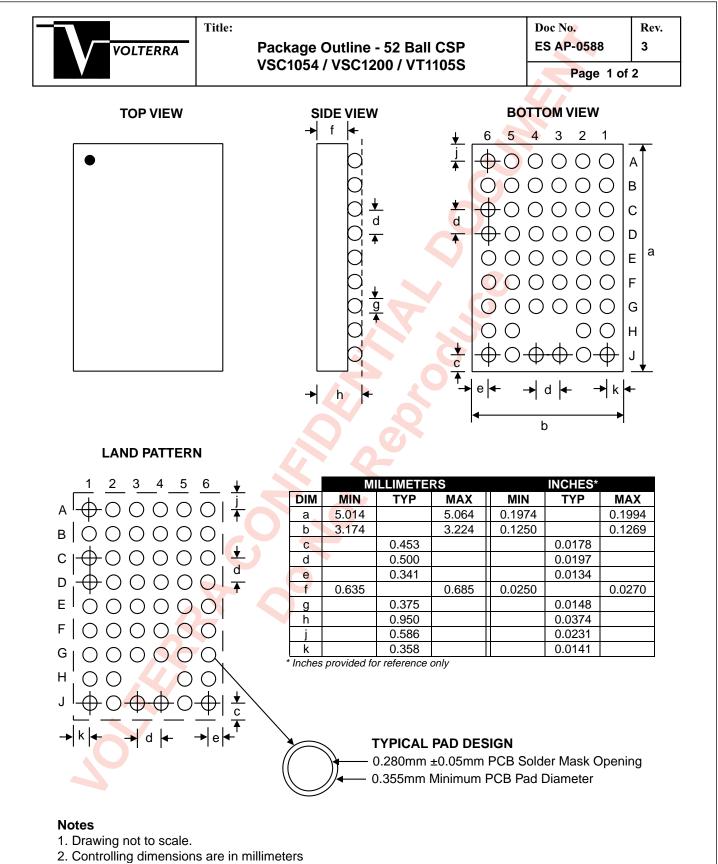

| VT1105SCR     | 25A Smart      | CSP-52        | ES AP-0588     | 250u Tape & Reel  | VT1105S         |

| VT1105SCX     | Slave™         | 03F-52        | ES AF-0500     | 2.5ku Tape & Reel | V111055         |

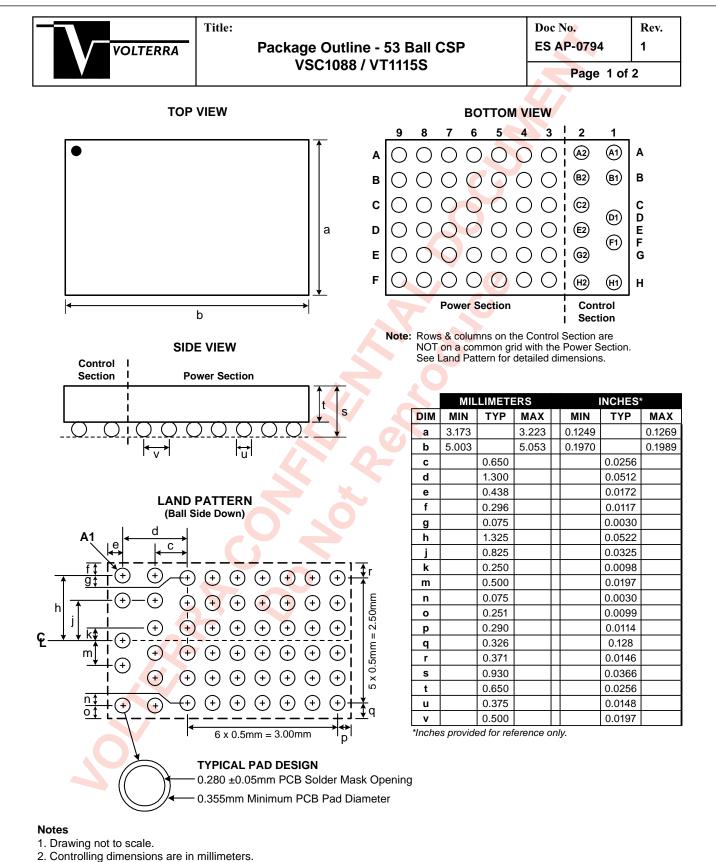

| VT1115SCR     | 30A Smart      | CSP-53        | ES AP-1088     | 250u Tape & Reel  | VT1115S         |

| VT1115SCX     | Slave™         | 036-03        | ES AF-1000     | 2.5ku Tape & Reel | V11155          |

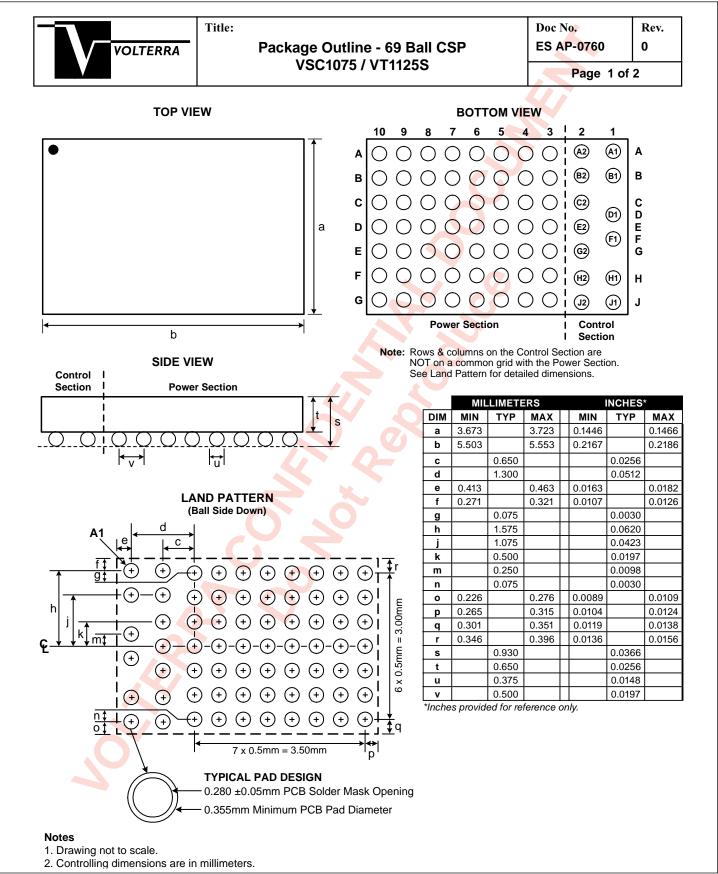

| VT1125SCR     | 25A Smart      | CSP-69        | ES AP-0760     | 250u Tape & Reel  | VT1125S         |

| VT1125SCX     | Slave™         | C3F-09        | ES AF-0700     | 2.5ku Tape & Reel | V111255         |

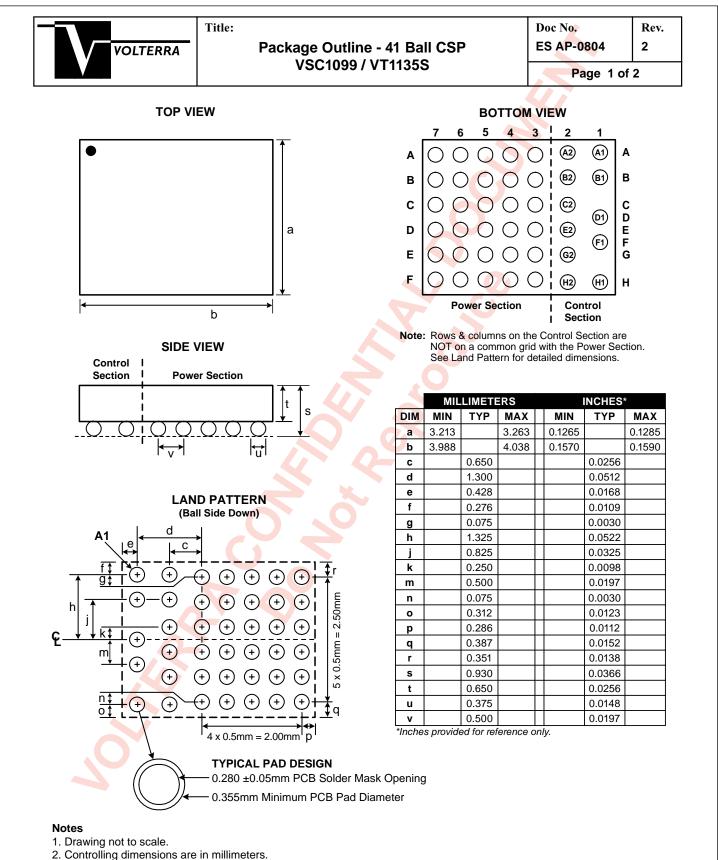

| VT1135SCR     | 30A Smart      | CSP-41        | ES AP-0804     | 250u Tape & Reel  | VT11250         |

| VT1135SCX     | Slave™         | C3P-41        | ES AP-0604     | 2.5ku Tape & Reel | VT1135S         |

| Lead-Free Opt | ions (RoHS Com | pliant)       |                |                   |                 |

| VT1165MFQ     | Maatar         |               |                | Trays             |                 |

| VT1165MFQX    | Master         | QFN-40        | ES AP-0906     | 2.5ku Tape & Reel | VT1165MF        |

| VT1105SFCR    | 25A Smart      | CSP-52        | ES AP-0588     | 250u Tape & Reel  | VT1105SF        |

| VT1105SFCX    | Slave™         | C3F-52        | ES AF-0500     | 2.5ku Tape & Reel | VIIIUDOF        |

| VT1115SFCR    | 30A Smart      | CSP-53        | ES AP-1088     | 250u Tape & Reel  |                 |

| VT1115SFCX    | Slave™         | CSP-53        | ES AP-1000     | 2.5ku Tape & Reel | VT1115SF        |

| VT1125SFCR    | 25A Smart      |               |                | 250u Tape & Reel  |                 |

| VT1125SFCX    | Slave™         | CSP-69        | ES AP-0760     | 2.5ku Tape & Reel | VT1125SF        |

| VT1135SFCR    | 30A Smart      | CSP-41        | ES AP-0804     | 250u Tape & Reel  | VT11258E        |

| VT1135SFCX    | Slave™         | 03P-41        | ES AP-0004     | 2.5ku Tape & Reel | VT1135SF        |

### ABSOLUTE MAXIMUM RATINGS (SEE NOTE 1)

| Supply Voltage (12V)                   | 0.3V to 16V  |

|----------------------------------------|--------------|

| Supply & Input Pin Voltages (3.3V)     | 0.3V to 4V   |

| VT1165M SC and SD Pin Voltages         | 0.3V to 7V   |

| Junction Temperature (T <sub>J</sub> ) | 150°C        |

| Storage Temperature Range              | 65° to 150°C |

| Peak Reflow Temperature Eutectic       |              |

| Peak Reflow Temperature Lead-Free      | 260°C        |

### THERMAL RATINGS

| Θ <sub>JC</sub> Max (QFN-40)              | 14.8°C/W |

|-------------------------------------------|----------|

| Θ <sub>JC</sub> Max (CSP-41)              | 0.6°C/W  |

| <sup>●</sup> Θ <sub>JC</sub> Max (CSP-52) | 0.5°C/W  |

| Θ <sub>JC</sub> Max (CSP-53)              | 0.5°C/W  |

| Θ <sub>JC</sub> Max (CSP-69)              | 0.3°C/W  |

| Θ <sub>JA</sub> <sup>2</sup> Typ (CSP-41) | 21°C/W   |

| Θ <sub>JA</sub> <sup>2</sup> Typ (CSP-52) | 19°C/W   |

| Θ <sub>JA</sub> <sup>2</sup> Typ (CSP-53) | 19°C/W   |

| Θ <sub>JA</sub> <sup>2</sup> Typ (CSP-69) | 17°C/W   |

#### **OPERATING RATINGS**

| Input 3.3V Voltages (Master & Slave)                                                     |     |

|------------------------------------------------------------------------------------------|-----|

| Slave 12V Supply<br>Junction Temperature (T <sub>J</sub> ) Master & Slave                |     |

| Frequency (Fsw)                                                                          |     |

| Design Guideline for Maximum Slave DC Output Current (VT1105S, VT1125S)                  |     |

| Design Guideline for Maximum Slave DC Output Current (VT1115S, VT1135S)                  |     |

| Electrical DC Current Limit Per Slave Assuming No Thermal Limitations (VT1105S, VT1125S) |     |

| Electrical DC Current Limit Per Slave Assuming No Thermal Limitations (VT1115S, VT1135S) |     |

| Peak Instantaneous Slave Current (VT1105S, VT1125S)                                      |     |

| Peak Instantaneous Slave Current (VT1115S, VT1135S)                                      | 63A |

**NOTE 1:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

NOTE 2: Data taken with Volterra's evaluation kit.

#### **ELECTRICAL CHARACTERISTICS**

$V_{DD-M} = V_{DD-S} = V_{CC-S} = 3.3V \pm 10\%$ ,  $V_{DD-H} = 10.8V$  to 13.2V unless otherwise specified. The \* symbol denotes specifications which apply over the following operating junction temperature ranges ( $T_{J-SLAVE} = 0$  to 125°C and  $T_{J-MASTER} = 0$  to 100°C), otherwise specifications are for  $T_{J} = 25$ °C. The # denotes parameters that are programmable.

| Symbol                                   | wise specifications are for $T_J = 25^{\circ}C$   | Conditior                                         |                          |          | Min    | Тур   | Max    | Units     |

|------------------------------------------|---------------------------------------------------|---------------------------------------------------|--------------------------|----------|--------|-------|--------|-----------|

| Supply Voltages, \                       |                                                   |                                                   |                          | -        |        | - 7 P |        |           |

| V <sub>DD-M</sub>                        | Supply Voltage Range (Master)                     | 1                                                 |                          | *        | 2.97   | 3.3   | 3.63   | V         |

|                                          |                                                   |                                                   |                          |          |        |       |        |           |

| V <sub>DD-S</sub> ,<br>V <sub>CC-S</sub> | Supply Voltage Range (Slave 3.3V)                 |                                                   |                          | *        | 2.97   | 3.3   | 3.63   | V         |

| V <sub>DDH</sub>                         | Supply Voltage Range (Slave 12V)                  |                                                   |                          | *        | 10.8   | 12.0  | 13.2   | V         |

|                                          | Supply Current (Master)                           | PWM                                               |                          |          | 10.0   | 13    | 10.2   | mA        |

| IDD-M                                    |                                                   | Shutdown                                          | OE = 0                   | -        |        | 10    |        | mA        |

| I                                        | Supply Current (Slave 3.3V)                       | VT1105S                                           | , <u>OE = 0</u><br>  PWM |          |        | 45    |        | mA        |

| I <sub>DD-S</sub> ,                      |                                                   | 111055                                            | Shutdown                 | -        |        | 20    |        |           |

| I <sub>CC-S</sub>                        |                                                   | VT44450                                           | PWM                      | -        |        |       |        | mA<br>m A |

|                                          |                                                   | VT1115S                                           |                          |          |        | 25    |        | mA        |

|                                          |                                                   | V/T44050                                          | Shutdown                 |          |        | 20    |        | mA        |

|                                          |                                                   | VT1125S                                           | PWM                      |          |        | 55    |        | mA        |

|                                          |                                                   |                                                   | Shutdown                 | <u> </u> |        | 20    |        | mA        |

|                                          |                                                   | VT1135S                                           | PWM                      |          |        | 25    |        | mA        |

|                                          |                                                   |                                                   | Shutdown                 |          |        | 20    |        | mA        |

| I <sub>DDH</sub>                         | Quiescent Supply Current                          | VT1105S                                           |                          |          |        | 1     |        | mA        |

|                                          | (Slave 12V)                                       | VT1115S                                           |                          |          |        | 2     |        | mA        |

|                                          |                                                   | VT1125S                                           |                          |          |        | 1     |        | mA        |

|                                          |                                                   | VT1135S                                           |                          |          |        | 2     |        | mA        |

| Output Voltage and                       | d DC Accuracy                                     |                                                   |                          |          |        |       |        |           |

| V <sub>OUT</sub>                         | Output Voltage Range                              | VRM 9 VII                                         | D Code                   | *        | 1.100  |       | 1.850  | V         |

|                                          |                                                   | VRM 10.X VID Code                                 |                          | *        | 0.8375 |       | 1.6000 | V         |

|                                          |                                                   | Opteron <sup>™</sup> VID Code                     |                          | *        | 0.800  |       | 1.550  | V         |

| ERROR <sub>MASTER-REF</sub>              | DC Setpoint Accuracy (including                   | Full VID Range:<br>The Greater of                 |                          | *        | -6     |       | +9     | mV        |

|                                          | voltage reference and master                      |                                                   |                          |          | or     |       | or     |           |

|                                          | amplifier)                                        |                                                   |                          |          | -0.8   |       | 0.8    | %         |

| Regulation and Sy                        | stem Specifications (Specified by design          | gn, tested usir                                   | ng circuits in Figur     | es 5     | & 6)   |       |        |           |

| ΔVout                                    | Line Regulation                                   | V <sub>DDH-S12V</sub>                             | = 12V ±10%               |          |        | 5     |        | mV        |

|                                          | Output Ripple                                     |                                                   |                          |          |        | 10    |        | mV        |

| SR <sub>OUT</sub>                        | Output Slew Rate                                  |                                                   |                          |          |        | 1000  |        | A/μs      |

| T <sub>TURN-ON</sub>                     | Turn-On Response Time. Time to                    | From Vpp                                          | -M > UVLO                | $\vdash$ | 4.6    |       | 5.4    | ms        |

|                                          | $V_{OUT} > 95\%$ of Final Value.                  | $(8 \text{ slaves}, I_{MAX} = 28A,$               |                          |          |        |       |        |           |

|                                          |                                                   |                                                   | 800kHz, 300µF/slave,     |          |        |       |        |           |

|                                          |                                                   | $C_{NOM} = 6.8$ nF). Includes configuration time. |                          |          |        |       |        |           |

|                                          |                                                   |                                                   |                          |          |        |       |        |           |

|                                          |                                                   | From OE Positive Edge                             |                          |          | 0      | 100   | 200    | μS        |

|                                          |                                                   | (8 slaves, $I_{MAX} = 28A$ ,                      |                          |          |        |       |        |           |

|                                          |                                                   |                                                   | 800μF/slave,             |          |        |       |        |           |

|                                          | The Orion sectors                                 | $C_{NOM} = 6.$                                    |                          | -        |        |       |        | 0/        |

| Vovershoot                               | Turn-On Overshoot                                 | Built in So                                       |                          |          |        |       | 0      | %         |

| VUNDERSHOOT                              | Turn-Off Undershoot                               | 30Ω Load                                          |                          | <u> </u> |        | 0     |        | mV        |

| CMRR <sub>SENSE</sub>                    | Common-Mode Rejection Ratio of Differential Sense |                                                   |                          |          |        | 40    |        | dB        |

| I <sub>SENSE</sub>                       | SENSE Pin Currents                                | SENSE+ S                                          |                          |          |        | 60    | 100    | μA        |

|                                          | 1                                                 | SENSE- S                                          | Couroing                 | 1        | 1      | 1     | 1      |           |

### ELECTRICAL CHARACTERISTICS (CONTINUED)

| Symbol                             | Parameter                                      | Conditior                 | ns                                                                   | -      | Min         | Тур       | Max      | Units |

|------------------------------------|------------------------------------------------|---------------------------|----------------------------------------------------------------------|--------|-------------|-----------|----------|-------|

| Regulation                         | and System Specifications (Specified           | d by design, te           | ested using circuits in                                              | n Figu | ires 5 & 6) | (CONTINUE | ED)      |       |

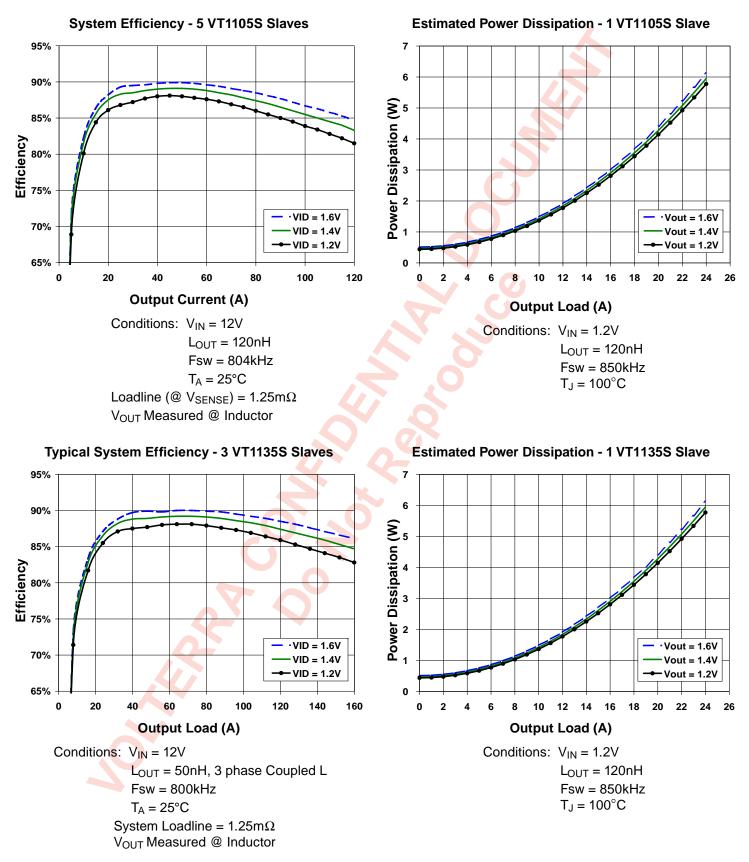

| Eff                                | Efficiency (Measured at Inductor),<br>6 Phases | VT1105S                   | VID = 1.4V,<br>V <sub>OUT</sub> = 1.197V,                            |        |             | 80        |          | %     |

|                                    | 01110363                                       |                           | $I_{OUT} = 150A$                                                     |        |             |           |          |       |

|                                    |                                                |                           | VID = 1.4V,                                                          |        | X           | 83        |          | %     |

|                                    |                                                |                           | V <sub>OUT</sub> = 1.233V,<br>I <sub>OUT</sub> = 130A                |        |             |           |          |       |

|                                    | Efficiency (Measured at Inductor),<br>6 Phases | VT1115S                   | VID = 1.4V,<br>$V_{OUT} = 1.197V,$                                   |        | 5           | 83        |          | %     |

|                                    |                                                |                           | I <sub>OUT</sub> = 150A<br>VID = 1.4V,<br>V <sub>OUT</sub> = 1.233V, | P      |             | 85        |          | %     |

|                                    |                                                | N/ <b>T</b> 4405 <b>O</b> | I <sub>OUT</sub> = 130A                                              |        |             |           |          |       |

|                                    | Efficiency (Measured at Inductor),<br>6 Phases | VT1125S                   | VID = 1.4V,<br>V <sub>OUT</sub> = 1.197V,<br>I <sub>OUT</sub> = 150A | 7      |             | 83        |          | %     |

|                                    |                                                |                           | VID = 1.4V,<br>V <sub>OUT</sub> = 1.233V,<br>I <sub>OUT</sub> = 130A |        |             | 85        |          | %     |

|                                    | Efficiency (Measured at Inductor),<br>6 Phases | VT1135S                   | VID = 1.4V,<br>V <sub>OUT</sub> = 1.197V,<br>I <sub>OUT</sub> = 150A |        |             | 80        |          | %     |

|                                    |                                                | 0                         | VID = 1.4V,<br>V <sub>OUT</sub> = 1.233V,<br>I <sub>OUT</sub> = 130A |        |             | 83        |          | %     |

| Slave Scala                        | bility and Peak Current Limit                  |                           |                                                                      |        |             |           |          | 1     |

| N <sub>SLAVE</sub>                 | Maximum total number of slaves                 |                           |                                                                      |        |             |           | 8        |       |

| I <sub>LIM-SL</sub>                | Peak Current Limit Per Slave                   | VT1105S,                  |                                                                      |        |             |           | 56       | A     |

|                                    |                                                | VT1115S,                  |                                                                      |        |             |           | 63       | A     |

| I <sub>MAX-SL(DC)</sub>            | DC Maximum Output Current Per                  | VT1105S,<br>VT1115S,      |                                                                      | #      |             |           | 25<br>30 | A     |

| -                                  | Slave DC Current Accuracy                      | VT1105S,                  |                                                                      | *      |             | 5         | 7        | %     |

|                                    |                                                | VT1125S,                  | VT1135S                                                              |        |             |           |          |       |

|                                    | IGITAL CONTROL AND STATUS PIN                  |                           |                                                                      |        |             |           |          |       |

| . ,                                | nd Clock (SC) Pins (SMBus High Po              | ower Speci                | fication Version 2                                                   | 2.0)   |             | 1         |          |       |

| VIL                                | Input Low Voltage<br>Input High Voltage        |                           |                                                                      | -      | 2.1         |           | 0.8      |       |

| V <sub>IH</sub><br>V <sub>OL</sub> | Output Low Voltage (SD)                        | @ I <sub>SINK</sub>       |                                                                      |        | 2.1         |           | 0.4      |       |

| I <sub>SINK</sub>                  | Current Sinking (SD)                           | $V_{OL} = 0.4$            | /                                                                    |        | 2.5         |           | 0.4      | mA    |

| -                                  | External Pull-Up Voltage                       |                           | •                                                                    |        | 2.0         |           | 5.5      | V     |

| OE and VID                         | 0[0:5] Pins for VRM 9, Opteron <sup>™</sup> an | d Program                 | mable VID Mode                                                       | I      |             |           |          |       |

| V <sub>IL</sub>                    | Input Low Voltage                              |                           |                                                                      | 1      |             |           | 0.8      | V     |

| VIH                                | Input High Voltage                             |                           |                                                                      |        | 1.7         |           |          | V     |

|                                    | D[0:5] Pins for VRM 10.X                       |                           |                                                                      |        |             |           |          |       |

| V <sub>IL</sub>                    | Input Low Voltage                              |                           |                                                                      |        |             |           | 0.4      | V     |

| VIH                                | Input High Voltage                             |                           |                                                                      |        | 0.8         |           |          | V     |

### ELECTRICAL CHARACTERISTICS (CONTINUED)

| Symbol                              | Parameter                                  | Conditions                         |          | Min      | Тур   | Max      | Units            |

|-------------------------------------|--------------------------------------------|------------------------------------|----------|----------|-------|----------|------------------|

| PWRGD and FAULTB P                  | ins                                        |                                    |          |          |       |          |                  |

| -                                   | PWRGD DC Threshold Error                   |                                    |          | -40      |       | +40      | mV               |

| -                                   | Delay from V <sub>OUT</sub> to PWRGD       | After Startup                      |          | 8        |       | 20       | μS               |

| -                                   | PWRGD Lockout after OE goes High           |                                    |          | 1.6      | 2.0   | 2.4      | ms               |

|                                     | (UVLO & OVLO Low)                          |                                    |          |          |       |          |                  |

| V <sub>OL</sub>                     | Output Low Voltage                         | @ I <sub>SINK</sub>                |          |          |       | 0.4      | V                |

| I <sub>SINK</sub>                   | Current Sinking (PWRGD, FAULTB)            | V <sub>OL</sub> = 0.4V             |          | 2.5      |       |          | mA               |

| OVP                                 |                                            |                                    |          |          |       | -        |                  |

| -                                   | DC Threshold Error                         |                                    |          | -40      |       | +40      | mV               |

| -                                   | OVP Lockout OE goes High (UVLO & OVLO Low) |                                    |          | 1.6      | 2.0   | 2.4      | ms               |

| OCP                                 |                                            |                                    |          |          | 1     | 1        |                  |

| I <sub>OCP</sub>                    | OCP Inception Point                        | Refer to Table 10                  |          | on for a |       | settings | :)               |

|                                     | Peak Current for Short Circuit             | Refer to Table 1D                  |          |          |       | -        |                  |

| ISC-PK                              | Hiccup Period                              |                                    |          | 46       | 50    | 54       | s)<br>ms         |

|                                     | Hiccup Period<br>Hiccup Duty Cycle         |                                    | -        | 40       | 10    | <u> </u> | %<br>%           |

| -                                   |                                            |                                    |          | 4 5      |       |          |                  |

| -                                   | Latch Off Delay                            |                                    |          | 4.5      | 5.0   | 5.5      | ms               |

|                                     | rvoltage Lockout 12V Supply                |                                    | <u> </u> | 4.000    | 1 000 | 4 000    |                  |

| IN_UVLO <sub>RE</sub>               | 12V UVLO Reference Voltage Rising<br>Edge  |                                    |          | 1.262    | 1.300 | 1.338    | V                |

| IN_UVLO <sub>FE</sub>               | 12V UVLO Reference Voltage Falling<br>Edge | 0                                  |          | 1.191    | 1.230 | 1.269    | V                |

| IN_UVLO <sub>HYSTERESIS</sub>       | UVLO Hysteresis                            | 7                                  |          | 30       | 67    |          | mV               |

| IN_OVLO <sub>RE</sub>               | 12V OVLO Reference Voltage Rising<br>Edge  |                                    |          | 1.262    | 1.300 | 1.338    | V                |

| IN_OVLO <sub>FE</sub>               | 12V OVLO Reference Voltage Falling<br>Edge |                                    |          | 1.191    | 1.230 | 1.269    | V                |

| IN_OVLO <sub>HYSTERESIS</sub>       | OVLO Hysteresis                            |                                    |          | 30       | 67    |          | mV               |

| t <sub>UVLO</sub> ,                 | 12V UVLO and OVLO Response                 | Including time to shut             |          |          | 7.25  |          | μS               |

| tovLo                               | Time                                       | down the slave                     |          |          |       |          | μο               |

| t <sub>UVLO-REC</sub> ,             | 12V UVLO and OVLO Recovery Time            |                                    |          |          | 7.25  |          | μs               |

| tovlo-rec                           |                                            | start delay                        |          |          |       |          | •                |

| Undervoltage Lockout                | 3.3V Supply (Master-Internal)              | •                                  |          |          | -     | -        |                  |

| 3_3V_UVLO                           | 3.3V Internal UVLO                         | Rising Threshold                   |          |          |       | 2.85     | V                |

|                                     |                                            | Falling Threshold                  |          | 2.69     |       |          | V                |

| 3_3V_UVLO <sub>HYSTERESIS</sub>     | Hysteresis                                 |                                    |          |          | 100   |          | mV               |

|                                     | 1115S, VT1125S, VT1135S)                   | 1                                  |          |          | 1     |          |                  |

| Vol-faultb                          | FAULTB Output Low Voltage                  | With 4.7kΩ external pull-up        |          |          | 0.1   | 0.4      | V                |

|                                     | FAULTB Pull-down Resistance                |                                    |          |          | 50    | 200      | Ω                |

| RPULLDOWN-FAULTB<br>SMBus Reporting |                                            |                                    |          | L        |       | 200      | 22               |

|                                     | SMBus Current Reporting Error              |                                    |          | -10      |       | +10      | % of             |

| -                                   |                                            |                                    |          | 10       |       |          | I <sub>MAX</sub> |

| SPHASE                              |                                            |                                    |          |          |       |          |                  |

| -                                   | SPHASE Clock Period Tolerance              | Including 1% Resistor<br>Tolerance | *        | -6       |       | +6       | %                |

#### **TYPICAL OPERATING CHARACTERISTICS**

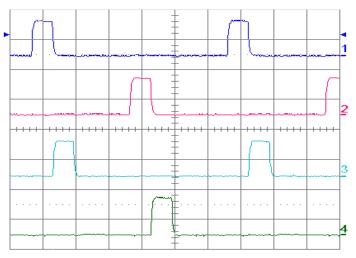

Output Switching Nodes - Eight Slaves Switching Out-of-Phase (Slaves 1-4)

#### Time/Div: 200ns

Conditions: V<sub>OUT</sub> = 1.2V, No Load

- 1: Vx Switching Node for Slave #1 (10V/div)

- 2: Vx Switching Node for Slave #2 (10V/div)

- **3:** Vx Switching Node for Slave #3 (10V/div)

- 4: Vx Switching Node for Slave #4 (10V/div)

(Triggered From Slave #1)

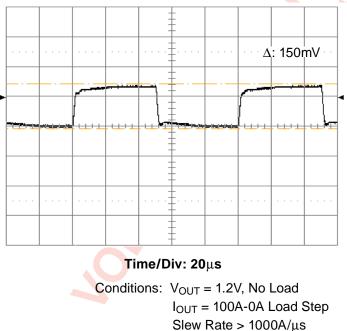

#### Load Transient Response - 8 Slave VT1105S System

$C_{OUT} = 58 \times 22 \mu F$

1: Output Voltage (100mV/div)

Output Switching Nodes - Eight Slaves Switching Out-of-Phase (Slaves 5-8)

#### Time/Div: 200ns

Conditions: V<sub>OUT</sub> = 1.2V, No Load

- 1: Vx Switching Node for Slave #5 (10V/div)

- 2: Vx Switching Node for Slave #6 (10V/div)

- 3: Vx Switching Node for Slave #7 (10V/div)

- 4: Vx Switching Node for Slave #8 (10V/div)

- (Triggered From Slave #1)

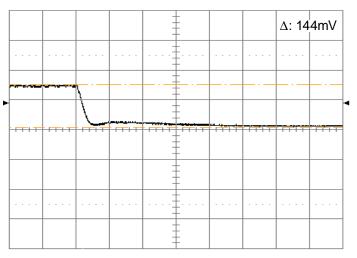

#### Output Voltage Overshoot - 8 Slave VT1105S System

#### Time/Div: 5µs

Conditions:  $V_{OUT} = 1.2V$   $I_{OUT} = 100A-0A$  Load Step Loadline =  $1.28m\Omega$   $C_{OUT} = 58 \times 22\mu F$ 1: Output Voltage (100mV/div)

#### TYPICAL OPERATING CHARACTERISTICS (CONTINUED)

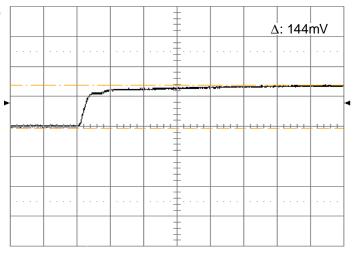

#### Output Voltage Undershoot - 8 Slave VT1105S System

#### Time/Div: 5µs

Conditions:  $V_{OUT} = 1.2V$   $I_{OUT} = 0.100A$  Load Step Loadline =  $1.28m\Omega$   $C_{OUT} = 58 \times 22\mu F$ 1: Output Voltage (100mV/div)

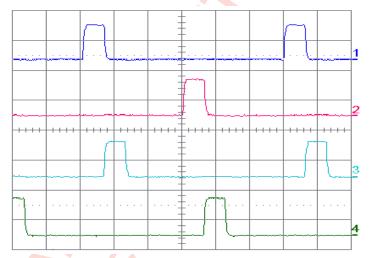

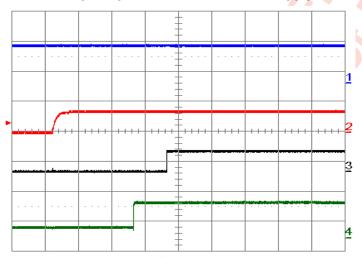

#### Startup Response References 3.3V Supply

#### Time/Div: 2ms

- Conditions: V<sub>OUT</sub> = 1.2V, No Load 1: 12V Input Voltage (10V/div) 2: 3.3V Input Voltage (5V/div)

- 3: PWRGD Signal (5V/div)

- **4:** Output Voltage (1V/div)

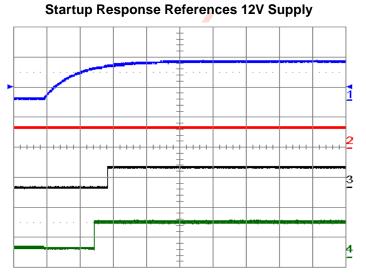

#### Time/Div: 5ms

Conditions: V<sub>OUT</sub> = 1.2V, No Load 1: 12V Input Voltage (10V/div)

- 2: 3.3V Input Voltage (5V/div)

- 3: PWRGD Signal (5V/div)

- 4: Output Voltage (1V/div)

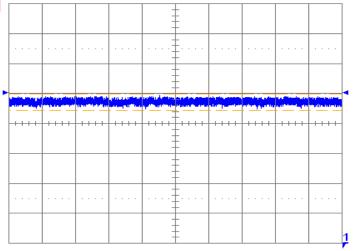

#### Output Ripple - 8 Slave VT1105S System

#### Time/Div: 20µs

Conditions:  $V_{OUT} = 1.2V$   $I_{OUT} = 160A$   $C_{OUT} = 58 \times 22\mu F$ 1: Output Voltage (20mV/div) 25MHz BWL Measured @ Output Capacitor

#### TYPICAL OPERATING CHARACTERISTICS (CONTINUED)

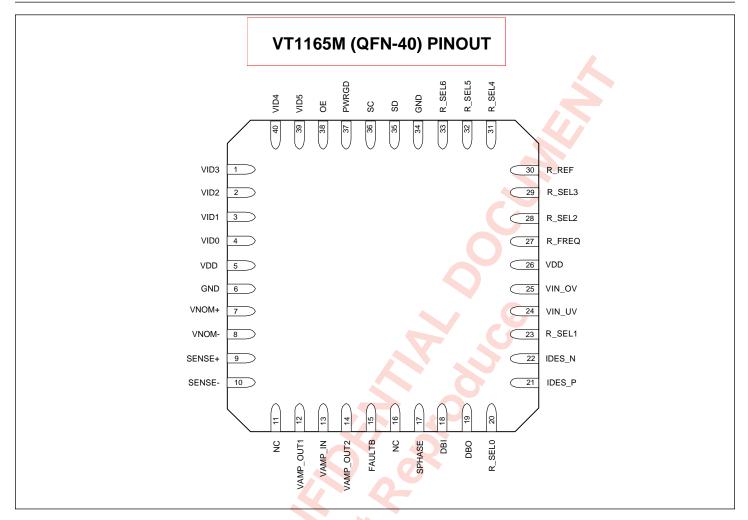

#### PIN INFORMATION FOR MASTER CONTROLLER

**VID[5:0]** (Pins 1-4, 39, 40): Output voltage identification code.

VDD (Pins 5, 26): 3.3V power.

GND (Pins 6, 34): Ground.

**VNOM+, VNOM-** (Pins 7, 8): DAC output used as the regulation reference. The no-load output voltage is equal to this reference. See the Output Voltage Programming section for additional design information.

SENSE+ (Pin 9): Positive remote sense.

SENSE- (Pin 10): Negative remote sense.

NC (Pin 11, 16): No connect.

VAMP\_OUT1 (Pin 12): Sense amplifier output.

VAMP\_IN (Pin 13): Error amplifier inverting input.

VAMP\_OUT2 (Pin 14): Error amplifier output.

FAULTB (Pin 15): Active low fault condition flag. This open

drain output should be externally pulled high with a resistor.

**SPHASE** (Pin 17): Slave phase clock output. This pin provides a switching frequency reference clock signal to each slave in the system. It should be connected to each slave's SPHASE input.

DBI (Pin 18): Digital control bus input.

**DBO** (Pin 19): Digital control bus output.

**R\_SEL[6:0]** (Pins 20, 23, 28, 29, 31-33): System configuration resistors. (Programmable features detailed in Table 5.)

IDES\_P (Pin 21): Idesired command (+).

**IDES\_N** (Pin 22): Idesired command (-).

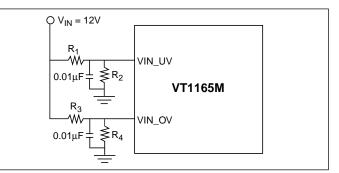

**VIN\_UV** (Pin 24): Scaled version of slave VDDH voltage for undervoltage shutdown. This pin is used to program the input undervoltage lockout threshold for the slave VDDH supply. See the Undervoltage and Overvoltage Programming and Protection section for additional design information.

**VIN\_OV** (Pin 25): Scaled version of slave VDDH voltage used for overvoltage shutdown. This pin is used to program the input overvoltage lockout threshold for the slave VDDH supply. See the Undervoltage and Overvoltage Programming and Protection section for additional design information.

**R\_FREQ** (Pin 27): Resistor used to program switching frequency.

$R_REF$  (Pin 30): Reference resistor used to calibrate  $R_SEL$ .

**SD** (Pin 35): Serial data pin for SMBus interface. See the SMBus Communication with the VT1165M section for additional design information. When not in use, this pin should be connected to VDD.

**SC** (Pin 36): Serial clock pin for SMBus interface. See the SMBus Communication with the VT1165M section for additional design information. When not in use, this pin should be connected to VDD.

**PWRGD** (Pin 37): Power good output pin. This pin indicates whether the output voltage is within regulation. This opendrain output should be externally pulled HIGH with a resistor. See the Power Good and Undervoltage and Overvoltage Programming and Protection sections for additional design information.

**OE** (Pin 38): Output enable input pin. When this pin is HIGH, the output voltage is enabled. When this pin is LOW, the output voltage is disabled.

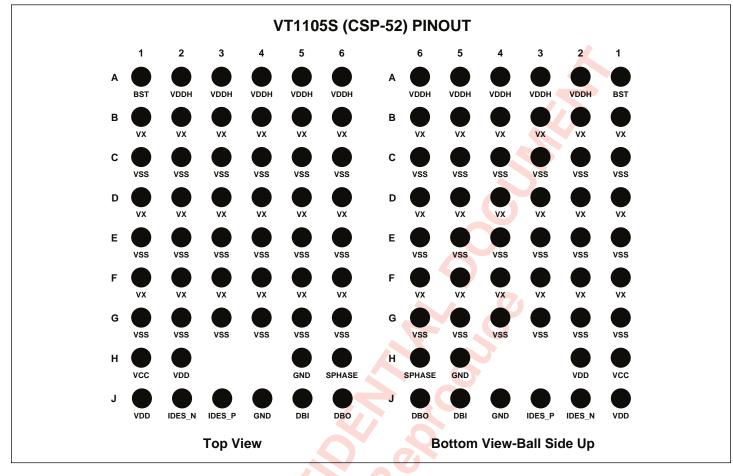

#### PIN INFORMATION FOR VT1105S SMART SLAVE™

BST (Ball A1): Bootstrap supply for high side drivers.

**VDDH** (Balls A2-A6): 12V input supply voltage node. These balls connect to the 12V input power supply source.

**VX** (Balls B1-B6, D1-D6, F1-F6): Switching node. These balls connect the switching node of the power devices to the output inductor.

**VSS** (Balls C1-C6, E1-E6, G1-G6): Power FETs ground node. These balls connect directly to the ground plane.

VCC (Ball H1): 3.3V supply for low side drivers.

**VDD** (Balls H2, J1): 3.3V supply for control circuits.

GND (Balls H5, J4): Ground for control circuits.

**SPHASE** (Ball H6): SPHASE clock input from VT1165M master controller.

**IDES\_N** (Ball J2): Negative input side of differential desired current signal.

**IDES\_P** (Ball J3): Positive input side of differential desired current signal.

**DBI** (Ball J5): Digital control bus input.

**DBO** (Ball J6): Digital control bus output.

## VT1165M CHIPSET PRELIMINARY

### **PROGRAMMABLE OUTPUT, MULTIPHASE SWITCHING REGULATOR WITH SMBus**

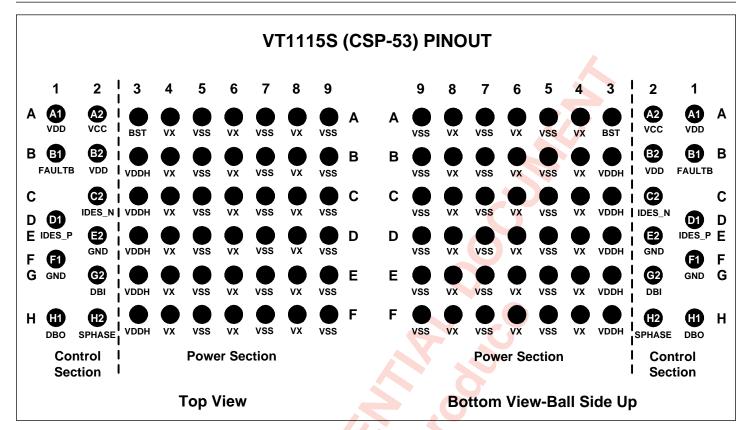

#### PIN INFORMATION FOR VT1115S SMART SLAVE™

VDD (Balls A1, B2): 3.3V supply for control circuits.

VCC (Ball A2): 3.3V supply for low side drivers.

BST (Ball A3): Bootstrap supply for high side drivers.

**VX** (Balls A4-F4, A6-F6, A8-F8): Switching node. These balls connect the switching node of the power devices to the output inductor.

**VSS** (Balls A5-F5, A7-F7, A9-F9): Power FETs ground node. These balls connect directly to the ground plane.

**FAULTB** (Ball B1): Fault signal. Active low. This open-drain output should be externally pulled high with a resistor.

**VDDH** (Balls B3-F3): 12V input supply voltage node. These balls connect to the 12V input power supply source.

**IDES\_N** (Ball C2): Negative input side of differential desired current signal.

**IDES\_P** (Ball D1): Positive input side of differential desired current signal.

GND (Balls E2, F1): Ground for control circuits.

DBI (Ball G2): Digital control bus input.

DBO (Ball H1): Digital control bus output.

**SPHASE** (Ball H2): SPHASE clock input from VT1165M master controller. A  $1k\Omega$  resistor is recommended in series with each slave's SPHASE line.

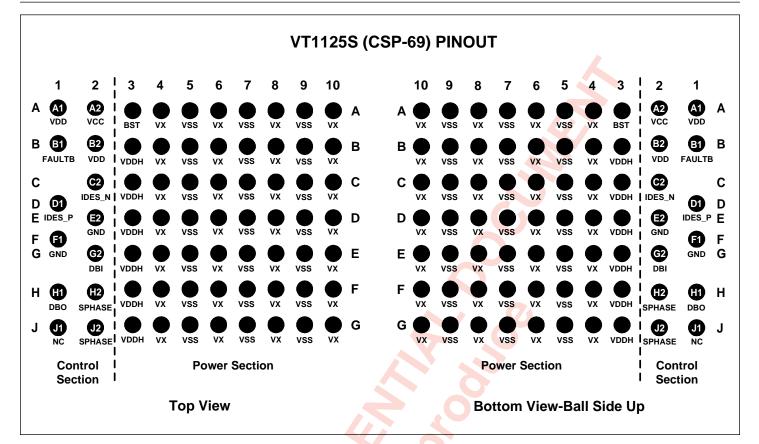

#### PIN INFORMATION FOR VT1125S SMART SLAVE™

VDD (Balls A1, B2): 3.3V supply for control circuits.

VCC (Ball A2): 3.3V supply for low side drivers.

BST (Ball A3): Bootstrap supply for high side drivers.

VX (Balls A4-G4, A6-G6, A8-G8, A10-G10): Switching node. These balls connect the switching node of the power devices to the output inductor.

**VSS** (Balls A5-G5, A7-G7, A9-G9): Power FETs ground node. These balls connect directly to the ground plane.

**FAULTB** (Ball B1): Fault signal. Active low. This open-drain output should be externally pulled high with a resistor.

**VDDH** (Balls B3-G3): 12V input supply voltage node. These balls connect to the 12V input power supply source.

**IDES\_N** (Ball C2): Negative input side of differential desired current signal.

**IDES\_P** (Ball D1): Positive input side of differential desired current signal.

GND (Balls E2, F1): Ground for control circuits.

DBI (Ball G2): Digital control bus input.

DBO (Ball H1): Digital control bus output.

SPHASE (Balls H2, J2): SPHASE clock input from VT1165M master controller. A 1k $\Omega$  resistor is recommended in series with each slave's SPHASE line.

NC (Ball J1): No connect.

## VT1165M CHIPSET PRELIMINARY

### **PROGRAMMABLE OUTPUT, MULTIPHASE SWITCHING REGULATOR WITH SMBus**

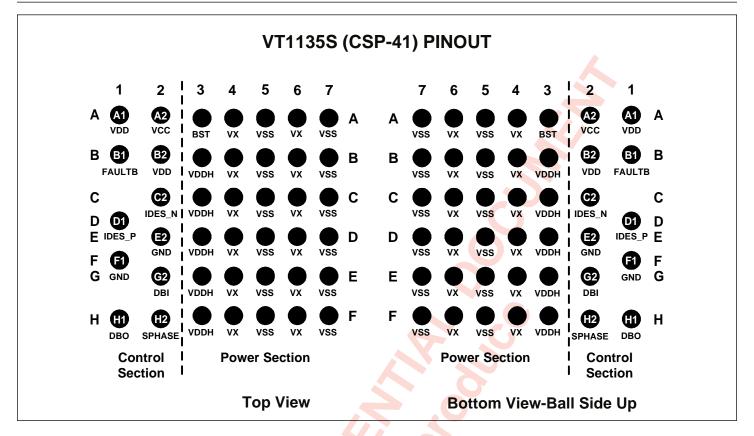

#### PIN INFORMATION FOR VT1135S SMART SLAVE™

VDD (Balls A1, B2): 3.3V supply for control circuits.

VCC (Ball A2): 3.3V supply for low side drivers.

BST (Ball A3): Bootstrap supply for high side drivers.

VX (Balls A4-F4, A6-F6): Switching node. These balls connect the switching node of the power devices to the output inductor.

**VSS** (Balls A5-F5, A7-F7): Power FETs ground node. These balls connect directly to the ground plane.

**FAULTB** (Ball B1): Fault signal. Active low. This open-drain output should be externally pulled high with a resistor.

**VDDH** (Balls B3-F3): 12V input supply voltage node. These balls connect to the 12V input power supply source.

**IDES\_N** (Ball C2): Negative input side of differential desired current signal.

**IDES\_P** (Ball D1): Positive input side of differential desired current signal.

GND (Balls E2, F1): Ground for control circuits.

DBI (Ball G2): Digital control bus input.

DBO (Ball H1): Digital control bus output.

**SPHASE** (Ball H2): SPHASE clock input from VT1165M master controller. A  $1k\Omega$  resistor is recommended in series with each slave's SPHASE line.

#### OPERATION

The VT1165M chipset provides a high frequency, highly integrated, compact multi-phase solution for high performance, low-voltage power conversion. The basic system architecture consists of a master controller and multiple Smart Slave<sup>™</sup> devices. These integrated circuits, along with a small number of external components, provide a complete solution for multi-phase buck voltage regulation.

#### **Synchronous Rectification**

Each Smart Slave<sup>™</sup> utilizes the full benefits of a synchronous rectification topology. Both the Sync FET and Control FET Power FETs are integrated on-chip and no external power components (MOSFETs or Schottky diodes) are required. During normal device operation, the bottom side switch acts as a synchronous rectifier, carrying the current that would normally flow through an external catch diode. This technique reduces losses associated with the diode's forward voltage drop. The resulting power savings are especially important in low-output-voltage applications.

#### **Control Architecture**

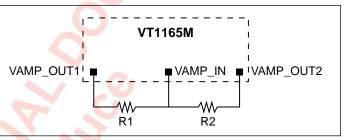

The VT1165M system has a fully differential voltage feedback path with excellent common mode rejection and adjustable gain and compensation. The remote output voltage is connected directly to the VT1165M at the SENSE+ and SENSE- pins. The gain of the error amplifier can be set by two external resistor values across the VAMP pins (VAMP\_IN, VAMP\_OUT1, VAMP\_OUT2). Additional resistors and capacitors in parallel with these resistors can provide additional poles and zeros for different compensation schemes.

Desired output current (I<sub>DES</sub>) is an analog differential signal communicated to the slaves by an Idesired bus (IDES\_N, IDES\_P). The slaves respond to the Idesired signal by producing a DC current proportional to the differential Idesired voltage, with zero volts commanding zero amps and 1.6V corresponding to the full scale current of the slave. The value of the full scale current is programmable via the selection resistor R\_SEL4. The slaves use their own internal control and current sense to switch their own FETs to control their inductor currents at the correct DC level, phase and frequency.

Volterra provides standard reference designs with all of the programmable parameters optimized for common VRM applications.

#### **Output Current Scalability**

Each Smart Slave<sup>™</sup> incorporates all MOSFETs, gate drivers, control and sense circuitry required to implement a single phase of a multi-phase buck regulation system. The output current of each slave is user programmable via the R\_SEL4 resistor of the master controller. Each master controller supports up to 8 phase shifted slaves, controlled via the differential current signal (I<sub>DES</sub>). Thus with one basic topology the load supplied can be scaled to any output current level and the total maximum output current setting of each slave. No more

Figure 2. VT1165M Chipset Block Diagram

than eight slaves should be connected to a single master, due to fan-out limitations.

Because the architecture requires no additional components or other modifications to support different output currents, a single PCB layout can support a wide range of load currents with simple loading (or unloading) options. The VT1165M supports all Smart Slave<sup>™</sup> devices in Volterra's fourth generation architecture.

The maximum output current of each slave is selected by connecting a resistor between the R\_SEL4 pin and ground. Tables 1A and 1B provide lists of typical values for R\_SEL4 and I<sub>MAX</sub>. For example, in a VT1125S system where the maximum operating current per slave is 20A, choosing I<sub>MAX</sub> = 24A is the recommended setting to provide headroom for excursions around the 20A operating value.

Fore each I<sub>MAX</sub> setting (programmed by R\_SEL4), there are two relevant current levels: I<sub>OCP</sub> and I<sub>SC\_PK</sub>. I<sub>OCP</sub> indicates the current level at which the system enters the user-specified OCP mode (i.e., hiccup, latchoff or CCM.) I<sub>SC-PK</sub> indicates the peak current observable during short-circuit conditions. The average DC short-circuit current depends on the OCP mode chosen. Tables 1C and 1D provide detailed current levels.

The R\_SEL4 resistor also controls an internal slave setting which affects the current control algorithm during an unloading transient. For applications using uncoupled inductors, internal setting "1" is recommended to minimize the output voltage overshoot during a transient event. When using coupled inductors, setting "3" will provide the optimal transient response.

#### **Output Voltage Programming**

The output voltage of the VT1165M chipset is digitally programmable from 0.800V to 1.850V with a DC set point accuracy of  $\pm 0.8\%$ . The master controller provides built-in support for the industry standard VID codes as follows:

| Table 1A: I <sub>MAX</sub> Programming for VT1105S and VT1125S |                      |                        |  |  |  |  |

|----------------------------------------------------------------|----------------------|------------------------|--|--|--|--|

| <b>R_SEL4 (</b> Ω)                                             | I <sub>MAX</sub> (A) | Internal Slave Setting |  |  |  |  |

| 340                                                            | 24                   | 1                      |  |  |  |  |

| 1.02k                                                          | 24                   | 2                      |  |  |  |  |

| 1.74k                                                          | 24                   | 3                      |  |  |  |  |

| 2.43k                                                          | 24                   | 4                      |  |  |  |  |

| 5.90k                                                          | 32                   | 1                      |  |  |  |  |

| 6.49k                                                          | 32                   | 2                      |  |  |  |  |

| 7.15k                                                          | 32                   | 3                      |  |  |  |  |

| 7.87k                                                          | 32                   | 4                      |  |  |  |  |

| 8.66k                                                          | 28                   | 4                      |  |  |  |  |

| 9.31k                                                          | 28                   | 3                      |  |  |  |  |

| 10.0k                                                          | 28                   | 2                      |  |  |  |  |

| 10.7k                                                          | 28                   | 1                      |  |  |  |  |

| Table 1B: I <sub>MAX</sub> F<br>VT1135S | Programming          | for VT1115S and        |

|-----------------------------------------|----------------------|------------------------|

| R_SEL4 (Ω)                              | I <sub>MAX</sub> (A) | Internal Slave Setting |

| 340 (GND)                               | 24                   | 1                      |

| 1.02k                                   | 24                   | 2                      |

| 1.74k                                   | 24                   | 3                      |

| 2.43k                                   | 24                   | 4                      |

| 3.09k                                   | 36                   | 4                      |

| 3.74k                                   | 36                   | 3                      |

| 4.42k                                   | 36                   | 2                      |

| 5.11k                                   | 36                   | 1                      |

| 5.90k                                   | 32                   | 1                      |

| 6.49k                                   | 32                   | 2                      |

| 7.15k                                   | 32                   | 3                      |

| 7.87k                                   | 32                   | 4                      |

| 8.66k                                   | 28                   | 4                      |

| 9.31k                                   | 28                   | 3                      |

| 10.0k                                   | 28                   | 2                      |

| 10.7k                                   | 28                   | 1                      |

| 11.3k                                   | 26                   | 1                      |

| 12.1k                                   | 26                   | 2                      |

| 13.0k                                   | 26                   | 3                      |

| 14.0k                                   | 26                   | 4                      |

| 15.4k                                   | 38                   | 4                      |

| 16.9k                                   | 38                   | 3                      |

| 18.7k                                   | 38                   | 2                      |

| 20.5k                                   | 38                   | 1                      |

| 23.7k                                   | 34                   | 1                      |

| 27.4k                                   | 34                   | 2                      |

| 31.6k                                   | 34                   | 3                      |

| 39.2k                                   | 34                   | 4                      |

| 49.9k                                   | 30                   | 4                      |

| 69.8k                                   | 30                   | 3                      |

| 118k                                    | 30                   | 2                      |

| 348k (VDD)                              | 30                   | 1                      |

| Table 1C: I <sub>OCP</sub> Levels for All I <sub>MAX</sub> Settings |                      |      |      |  |  |  |

|---------------------------------------------------------------------|----------------------|------|------|--|--|--|

| IMAX Setting Programmed by                                          | I <sub>OCP</sub> (A) |      |      |  |  |  |

| R_SEL4 (A)                                                          | Min                  | Тур  | Max  |  |  |  |

| 24                                                                  | 20.9                 | 22.6 | 24.2 |  |  |  |

| 26                                                                  | 22.7                 | 24.5 | 26.2 |  |  |  |

| 28                                                                  | 25.0                 | 26.3 | 28.2 |  |  |  |

| 30                                                                  | 26.3                 | 28.2 | 30.2 |  |  |  |

| 32                                                                  | 28.0                 | 30.1 | 32.2 |  |  |  |

| 34                                                                  | 30.0                 | 32.0 | 34.2 |  |  |  |

| 36                                                                  | 31.6                 | 33.9 | 36.1 |  |  |  |

| 38                                                                  | 33.4                 | 35.8 | 38.1 |  |  |  |

| Table 1D: I <sub>SC-PK</sub> Levels for All I <sub>MAX</sub> Settings |      |      |      |  |  |

|-----------------------------------------------------------------------|------|------|------|--|--|

| IMAX Setting Programmed by ISC-PK (A)                                 |      |      |      |  |  |

| R_SEL4 (A)                                                            |      |      |      |  |  |

| 24                                                                    | 22.6 | 23.8 | 25.0 |  |  |

| 26                                                                    | 24.6 | 25.9 | 27.2 |  |  |

| 28                                                                    | 26.6 | 28.0 | 29.4 |  |  |

| 30                                                                    | 28.6 | 30.1 | 31.6 |  |  |

| 32                                                                    | 30.5 | 32.1 | 33.7 |  |  |

| 34                                                                    | 32.5 | 34.2 | 35.9 |  |  |

| 36                                                                    | 34.5 | 36.3 | 38.1 |  |  |

| 38                                                                    | 36.4 | 38.3 | 40.2 |  |  |

- VRM 9 specification (1.100V to 1.850V)

- VRM 10.X specification (0.8375V to 1.600V)

- Opteron<sup>™</sup> VID code specification (0.800V to 1.550V)

- Serial VID (SVID) Mode (0.450V to 2.0375V)

See Tables 19, 20 and 21 for VID tables.

VID code selection is accomplished by connecting a resistor between the R\_SEL3 pin and ground. The value of this resistor determines the VID code selected, as shown in Table 2A. In conjunction with the R\_SEL3 pin, the VID[5:0] pins program an internal DAC that sets the regulator's output voltage. External resistors can be used to set VID[5:0]. At zero output load, the output voltage is equal to the nominal voltage value. This value depends on the VID standard, VID code and setpoint value. Table 2A shows the nominal voltage for each VID standard.

The VT1165M includes a new Serial VID (SVID) Mode with the following modified behavior for the traditional six VID bits.

- Two pins to select a V<sub>START</sub> voltage

- Two pins to select between 4 SMBus programmable output voltages

- Two pins tied to V<sub>DD-M</sub>

In SVID Mode, the 6-bit VID defines a starting ( $V_{START}$ )  $V_{NOM}$  DAC voltage according to Table 2B.

Override is an SMBus programmable bit which is 0 at power-up, so that until the VT1165M receives an SMBus DAC code or override command, the  $V_{NOM}$  DAC voltage (subject to OE and other shutdown/fault conditions) must be equal to  $V_{START}$ .

The VID [3:2] bits should both be tied high for default operation.

#### Programmable Setpoint

The regulator's output voltage setpoint can be adjusted by connecting a resistor from the R\_SEL1 pin to ground. The value of this resistor determines the magnitude of the setpoint adjustment, as summarized in Table 3, as well as the OCP mode. Overcurrent protection is discussed in more detail in the Overcurrent Protection Mode section.

| Table 2A: VID Code Selection |      |                      |                     |                               |  |  |

|------------------------------|------|----------------------|---------------------|-------------------------------|--|--|

| R_SEL3<br>(Ω)                | Code | VID Code             | FAULTB =<br>VRM_HOT | V <sub>NOM</sub> Value<br>(V) |  |  |

| 340<br>(GND)                 | 0    | VRM 10.X             | No                  | VID - 25mV<br>+ SP            |  |  |

| 1.02k                        | 1    | VRM 10.X             | No                  | VID - 25mV<br>+ SP            |  |  |

| 1.74k                        | 2    | VRM 10.X             | Yes                 | VID - 25mV<br>+ SP            |  |  |

| 2.43k                        | 3    | VRM 10.X             | Yes                 | VID - 25mV<br>+ SP            |  |  |

| 3.09k                        | 4    | Opteron™             | No                  | VID + 25mV<br>+ SP            |  |  |

| 3.74k                        | 5    | Opteron <sup>™</sup> | No                  | VID + 25mV<br>+ SP            |  |  |

| 4.42k                        | 6    | Opteron <sup>™</sup> | Yes                 | VID + 25mV<br>+ SP            |  |  |

| 5.11k                        | 7    | Opteron <sup>™</sup> | Yes                 | VID + 25mV<br>+ SP            |  |  |

| 5.90k                        | 8    | VRM 9                | No                  | VID - 12.5mV<br>+ SP          |  |  |

| 6.49k                        | 9    | VRM 9                | No                  | VID - 12.5mV<br>+ SP          |  |  |

| 7.15k                        | 10   | VRM 9                | Yes                 | VID - 12.5mV<br>+ SP          |  |  |

| 7.87k                        | 11   | VRM 9                | Yes                 | VID - 12.5mV<br>+ SP          |  |  |

| 8.66k                        | 12   | SVID<br>Mode         | No                  | SMBus<br>Value                |  |  |

| 9.31k                        | 13   | SVID<br>Mode         | No                  | SMBus<br>Value                |  |  |

| 10.0k                        | 14   | SVID<br>Mode         | Yes                 | SMBus<br>Value                |  |  |

| 10.7k                        | 15   | SVID<br>Mode         | Yes                 | SMBus<br>Value                |  |  |

### Table 2B: SVID Functionality (VID [3:2] = 11)

| 2-Bit<br>Code | Override = 0<br>V <sub>START</sub><br>(VID[1:0]) | Override = 1<br>V <sub>OUT</sub> Select<br>(VID[5:4]) |

|---------------|--------------------------------------------------|-------------------------------------------------------|

| 00            | 1.00V                                            | SMBus Voltage 1 (Register 21d)                        |

| 01            | 1.05V                                            | SMBus Voltage 2 (Register 22d)                        |

| 10            | 1.10V                                            | SMBus Voltage 3 (Register 23d)                        |

| 11            | 1.15V                                            | SMBus Voltage 4 (Register 24d)                        |

#### **Programmable Droop**

The VT1165M chipset enables flexibility in matching system load lines. To achieve the correct system load line, the proper system gain must be chosen via resistor settings on the VT1165M.

| Table 3: Setpc<br>R_SEL1 (Ω) | Setpoint Adjust (mV) | OCP Action |

|------------------------------|----------------------|------------|

| 340 (GND)                    | +21.9                | Hiccup     |

| 1.02k                        | +18.8                | Hiccup     |

| 1.02k                        | +15.6                | Hiccup     |

| 2.43k                        | +13.0                | Hiccup     |

| 2.43k<br>3.09k               | +9.4                 | Hiccup     |

| 3.09k                        | +9.4                 | Hiccup     |

| 4.42k                        | +3.1                 | Hiccup     |

|                              |                      | · · · ·    |

| 5.11k                        | 0                    | Hiccup     |

| 5.90k                        | -3.1                 | Hiccup     |

| 6.49k                        | -6.3                 | Hiccup     |

| 7.15k                        | -9.4                 | Hiccup     |

| 7.87k                        | -12.5                | Hiccup     |

| 8.66k                        | -15.6                | Hiccup     |

| 9.31k                        | -18.8                | Hiccup     |

| 10.0k                        | -21.9                | Hiccup     |

| 10.7k                        | -21.9                | Hiccup     |

| 11.3k                        | -21.9                | Latch off  |

| 12.1k                        | -18.8                | Latch off  |

| 13.0k                        | -15.6                | Latch off  |

| 14.0k                        | -12.5                | Latch off  |

| 15.4k                        | -9.4                 | Latch off  |

| 16.9k                        | -6.3                 | Latch off  |

| 18.7k                        | -3.1                 | Latch off  |

| 20.5k                        | 0                    | Latch off  |

| 23.7k                        | +3.1                 | Latch off  |

| 27.4k                        | +6.3                 | Latch off  |

| 31.6k                        | +9.4                 | Latch off  |

| 39.2k                        | +12.5                | Latch off  |

| 49.9k                        | +15.6                | Latch off  |

| 69.8k                        | +18.8                | Latch off  |

| 118k                         | +21.9                | Latch off  |

| 348k (VDD)                   | FAULT                |            |

System gain relates total system current to output voltage droop where system gain (in current per droop voltage) is described in the following equation:

$$I_{SLAVE} = \frac{R2}{R1} \cdot \left(\frac{I_{MAX}}{1.6}\right) \cdot \{6,13,20\} \cdot V_{DROOP}$$

Where  $I_{SLAVE}$  is the current per slave. For a total slave count of  $N_{SLAVES}$  the total regulator current is simply given by:

R2 and R1 are external resistors connected around an amplifier as shown in Figure 3. For best performance, the ratio of R2/R1 should be between 0.5 and 5. The recommended value for R1 is  $500\Omega$ .

$I_{MAX}$  is selectable via R\_SEL4 as described previously in Tables 1A and 1B. The choice of gain (6 or 13 or 20) is made with R\_SEL0 as shown in Table 4.

#### Example Droop Calculation

Consider a system with 120A, 1.25m $\Omega$  load line, with 6 VT1125S slaves and 20A per slave.

- 1. In order to ensure that there is some tolerance for current ripple, choose  $I_{MAX} = 24$ . Based on Table 1A, use R\_SEL4 = 340 $\Omega$ .

- 2. Note that with 120A and 1.25m $\Omega$  load line, the voltage droop at full load is 150mV.

Figure 3. Amplifier Gain Programmability Resistors

| Table 4: System Gain and SMBus Address Programming |      |      |                 |  |  |

|----------------------------------------------------|------|------|-----------------|--|--|

| <b>R_SEL0 (</b> Ω)                                 | Code | Gain | SMBus Addr[2:0] |  |  |

| 340 (GND)                                          | 0    | 20   | 0               |  |  |

| 1.02k                                              | 1    | 20   | 1               |  |  |

| 1.74k                                              | 2    | 20   | 2               |  |  |

| 2.43k                                              | 3    | 20   | 3               |  |  |

| 3.09k                                              | 4    | 20   | 4               |  |  |

| 3.74k                                              | 5    | 20   | 5               |  |  |

| 4.42k                                              | 6    | 20   | 6               |  |  |

| 5.11k                                              | 7    | 20   | 7               |  |  |

| 5.90k                                              | 8    | 13   | 0               |  |  |

| 6.49k                                              | 9    | 13   | 1               |  |  |

| 7.15k                                              | 10   | 13   | 2               |  |  |

| 7.87k                                              | 11   | 13   | 3               |  |  |

| 8.66k                                              | 12   | 13   | 4               |  |  |

| 9.31k                                              | 13   | 13   | 5               |  |  |

| 10.0k                                              | 14   | 13   | 6               |  |  |

| 10.7k                                              | 15   | 13   | 7               |  |  |

| 11.3k                                              | 16   | 6    | 0               |  |  |

| 12.1k                                              | 17   | 6    | 1               |  |  |

| 13.0k                                              | 18   | 6    | 2               |  |  |

| 14.0k                                              | 19   | 6    | 3               |  |  |

| 15.4k                                              | 20   | 6    | 4               |  |  |

| 16.9k                                              | 21   | 6    | 5               |  |  |

| 18.7k                                              | 22   | 6    | 6               |  |  |

| 20.5k                                              | 23   | 6    | 7               |  |  |

- 3. Using the equation above, with V<sub>DROOP</sub> = 150mV, I<sub>SLAVE</sub> = 20A, I<sub>MAX</sub> = 24A, R2/R1 {6,13,20} = 8.89.

- 4. Choose gain of 6. Thus R\_SEL0 is  $11.3k\Omega$  (for SMBus address = 0).

- 5. The remaining gain is R2/R1 = 1.48. Choose R1 = 500 $\Omega$ , R2 = 741 $\Omega$ .

#### **On-the-Fly VID**

The VT1165M chipset meets  $AMD^{\textcircled{R}}$  Opteron<sup>TM</sup> and Intel<sup>R</sup> VRM 10.X 'VID on the fly' VID specifications.

#### **Output Enable**

The OE pin enables or disables the regulator's output voltage. It should be pulled HIGH using an external pull-up resistor. When forced LOW, the output voltage is disabled.

#### **Power Good**

The Power Good (PWRGD) pin provides an open drain output that indicates the status of the output voltage. This pin is externally pulled HIGH using a pull-up resistor of  $10k\Omega$  or higher. The signal remains high during normal regulator operation. A low signal indicates an output voltage deviation above or below V<sub>NOM</sub> for at least 20µs. The deviation threshold is user programmable using R\_SEL2 as shown in Table 9.

#### **FAULTB Flags**

The FAULTB pin on the master provides an open drain output that indicates a fault condition in the system. This pin should be externally pulled HIGH using a  $10k\Omega$  or larger pull-up resistor. During normal operation, the signal on the pin will remain HIGH unless one of the following fault conditions occurs, in which case it will latch in the LOW position:

- R\_FREQ resistor is out of range (less than  $10k\Omega$  or greater than  $300k\Omega$ ).

- Master cannot configure itself due to improper R\_SEL selection.

- A slave reports an over-temperature event or V<sub>X</sub> fault.

- The daisy-chain digital bus connecting the slaves is broken.

For the VT1115S, VT1125S and VT1135S slaves, the slave fault is directly indicated on the slave's FAULTB ball as well. Cycling the 3.3V power supply resets the slave and clears the fault condition.

### MASTER-SLAVE DIGITAL INTERFACE

The Smart Slaves<sup>™</sup> are configured and monitored via a digital daisy chain interface between the master and all slaves where all devices are connected in a ring. The master controller automatically detects the number of phases present and then sets the phase spacing appropriately. Each slave is assigned its own sequential number via the daisy chain control bus and switches in accordance to its required phase offset to the SPHASE

signal. For example, with only two slaves, phase spacing is 180 degrees; with three slaves, spacing is 120 degrees.

Each slave's phase offset and other configuration settings are communicated over the digital bus during startup. Fault conditions are communicated from slave to master during normal operation.

#### SMBus COMMUNICATION WITH THE VT1165M

The following sections assume basic familiarity with the SMBus interface. Additional background information is available at http://www.smbus.org. The SMBus interface follows the following subset of the SMBus 2.0 specification (appropriate section numbers in parentheses):

- Compliant with 3.3V to 5V ±10% supply levels (2.0)

- SMBus slave support only

- No packet error checking (PEC) (5.4)

- No support for Address Resolution Protocol (5.6)

- Resistor setting allows unique addressing of eight VT1165M devices per bus

- Supports SMBus protocols:

- Write byte/word (5.5.4)

- Read byte/word (5.5.5)

The following regulator <u>monitoring</u> information is available over the SMBus interface:

- Average regulator output current

- Peak regulator output current (max average)

- Individual slave junction temperature

- Number of slaves

- Slave status monitoring at the master (VX short, overtemperature, bus break)

- Slave status for each slave (VX short, over-temperature, phase lock, boost voltage, desired current)

- Status of power good signal

- Status of input undervoltage monitor

- Status of input overvoltage monitor

- Status of output overvoltage monitor

- Status of output enable signal

- Status of output overcurrent monitor

- Status of digital bus monitor

- Status of slave configuration

- Status of system clock reference

- VID code settings

- Controller ID number

- Controller revision number

- System RADC programmable settings

The following regulator <u>control</u> capabilities are supported over the SMBus interface:

- Override the VID code settings to program the output voltage

- Override the OE signal to shutdown the regulator

SMBus details, features and programmability are described separately in Volterra Application Note 11.

#### Setting the SMBus Address

Addr[2:0] are determined by the resistor value connected to the R\_SEL0 pin. Table 4 explains this relationship between resistor value and addr[2:0]. Table 5 shows the bit description for this register.

| Table 5: Address Byte for VT1165M |       |       |       |         |         |         |       |

|-----------------------------------|-------|-------|-------|---------|---------|---------|-------|

| Bit 7                             | Bit 6 | Bit 5 | Bit 4 | Bit 3   | Bit 2   | Bit 1   | Bit 0 |

| 1                                 | 1     | 1     | 0     | addr[2] | addr[1] | addr[0] | R/W   |

# SMBus and Output Voltage Programming in SVID Mode

The relevant SMBus locations are the DAC registers (registers 21d-24d), the override bit (register 25d, bit0) and write\_enable (register 29d). Table 6 shows the bit descriptions for these registers. Table 7 shows a typical startup flow.

| Table 6: Data Format for Registers 21d-24d |       |       |       |       |       |       |        |

|--------------------------------------------|-------|-------|-------|-------|-------|-------|--------|

| Bit 7                                      | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

| 0                                          | 800mV | 400mV | 200mV | 100mV | 50mV  | 25mV  | 12.5mV |

NOTE: An auxiliary 450mV DAC leg is forced on in SVID Mode, so the voltage code written to these registers should be 450mV less than the desired output voltage. For example, if 1.1V is desired, then the value that should be written to the DAC register is 1.1V - 0.45V = 0.65V (0011 0100b).

| Table 7: | Startup Flow                                                                                                                         |                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Step     | Description                                                                                                                          | V <sub>OUT</sub> Value                    |