ADVANCED<sup>\*</sup>

# 64Mx32 Flash Multi-Chip Package 3.0V Page Mode Flash Memory

#### **FEATURES**

- Single power supply operation

- · 3 volt read, erase, and program operations

- I/O Control

- All input levels (address, control, and DQ input levels) and outputs are determined by voltage on Vio input. Vio range is 1.65 to Vcc

- Secured Silicon Sector region

- 128-word/256-byte sector for permanent, secure identification through an 8-word/16-byte random Electronic Serial Number, accessible through a command sequence

- May be programmed and locked at the factory or by the customer

- Flexible sector architecture

- Five hundred twelve 64 Kword (128 Kbyte) sectors

- Two hundred fifty-six 64 Kword (128 Kbyte) sectors

- One hundred twenty-eight 64 Kword (128 Kbyte) sectors

- Compatibility with JEDEC standard

- Provides software compatibility for single-power supply flash, and superior inadvertent write protection

- 100,000 erase cycles per sector typical

- 20-year data retention typical

#### PERFORMANCE CHARACTERISTICS

- High Performance

- 100, 120 ns

- 8-word/16-byte page read buffer

- · 25 ns page read times

- 16-word/32-byte write buffer reduces overall programming time for multiple-word updates

- Package option

- 107 BGA, 14mm x 17mm

- 1.0mm pitch

#### Software features

- Program Suspend and Resume: read other sectors before programming operation is completed

- Erase Suspend and Resume: read/program other sectors before an erase operation is completed

- Data# polling and toggle bits provide status

- Unlock Bypass Program command reduces overall multiple-word programming time

- CFI (Common Flash Interface) compliant: allows host system to identify and accommodate multiple flash devices

- Hardware features

- Advanced Sector Protection

- WP#/ACC input accelerates programming time (when high voltage is applied) for greater throughput during system production. Protects first or last sector regardless of sector protection settings

- · Hardware reset input (RESET#) resets device

- Ready/Busy# output (RY/BY#) detects program or erase cycle completion

<sup>\*</sup> This product is under development, is not qualified or characterized and is subject to change or cancellation without notice.

ADVANCED<sup>®</sup>

## **GENERAL DESCRIPTION**

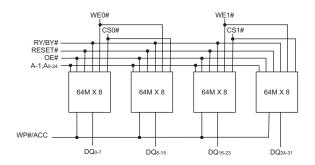

The W764MB2V-XSBX device is a 3.0V single power flash memory. The device utilizes four organized as 33,554,432 words or 67, 108,864 bytes. The device has 64 -bit wide data bus that can also function as an 32-bit wide data bus by using the BYTE# input. The device can be programmed either in the host system or in standard EPROM programmers.

Each device requires a single 3.0 volt power supply for both read and write functions. In addition to a Vcc input, an high-voltage accelerated program (WP/ACC) input provides shorter programming times through increased current. This feature is intended to facilitate factory throughput during system production, but may also be used in the field if desired.

The devices are entirely command set compatible with the JEDEC single power-supply Flash standard. Commands are written to the device using standard microprocessor write timing. Write cycles also internally latch addresses and data needed for the programming and erase operations.

The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully erased when shipped from the factory.

Device programming and erasure are initiated through command sequences. Once a program or erase operation has begun, the host system need only poll the DQ7 (Data# Polling) or DQ6 (toggle) status bits or monitor the Ready / Busy# (RY / BY#) output to determine whether the operation is complete. To facilitate programming, an Unlock Bypass mode reduces command sequence over head by requiring only two write cycles to program data instead of four.

The I/O ( $V_{\rm IO}$ ) control allows the host system to set the voltage levels that the device generates and tolerates on all input levels (address, chip control, and DQ input levels) to the same voltage level that is asserted on the  $V_{\rm IO}$  pin. This allows the device to operate in a 1.8 V or 3 V system environment as required.

Hardware data protection measures include a low V<sub>CC</sub> detector that automatically inhibits write operations during power transitions. Persistent Sector Protection provides in-system, comand-enabled protection of any combination of sectors using a single power supply at V<sub>CC</sub>. Password

Sector Protection prevents unauthorized write and erase operations in any combination of sectors through a user-defined 64-bit password.

The erase Suspend / Erase Resume feature allows the host system to pause and erase operation in a given sector to read or program any other sector and then complete the erase operation. The Program Suspend / Program Resume feature enables the host system to pause the program operation in a given sector to read any other sector and then complete the program operation.

The hardware RESET# pin terminates any operation in progress and resets the device, after which it is then ready for a new operation. The RESET# pin may be tied to the system reset circuitry. A system reset would thus also reset the device, enabling the host system to read boot-up firmware from the Flash memory device.

The device reduces power consumption in the standby mode when it detects specific voltage levels on CS# and RESET#, or when addresses have been stable for a specified period of time.

The Secured Silicon Sector provides a 128-work/256-byte area for code or data that can be permanently protected. Once this sector is protected, no further changes within the sector can occur.

The Write Protect (WP# / ACC) feature protects the first or last sector by asserting a logic low on the WP# pin.

# FIG 1: PIN CONFIGURATION (TOP VIEW)

1 2 3 4 5 6 7 8 9

#### **PIN DESCRIPTION**

| DQ <sub>0-63</sub>       | Data Inputs/Outputs     |

|--------------------------|-------------------------|

| A <sub>0-24</sub> , A-1* | Address Inputs          |

| WE# <sub>0-1</sub>       | Write Enables           |

| CS# <sub>0-1</sub>       | Chip Selects            |

| OE#                      | Output Enable           |

| RESET#                   | Hardware Reset          |

| WP#/ACC                  | Hardware Write          |

|                          | Protection/Acceleration |

| RY/BY#                   | Ready/Busy Output       |

| Vcc                      | Power Supply            |

| Vio                      | I/O Power Supply        |

| GND                      | Ground                  |

| DNU                      | Do Not Use              |

<sup>\*</sup> A-1 is the least significant address.

#### **BLOCK DIAGRAM**

ADVANCED\*

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      |                  | Unit   |

|--------------------------------|------------------|--------|

| Operating Temperature          | -55 to +125      | °C     |

| Supply Voltage Range (Vcc)     | -0.5 to +4.0     | V      |

| Signal Voltage Range           | -0.5 to Vcc +0.5 | V      |

| Storage Temperature Range      | -55 to +125      | °C     |

| Endurance (write/erase cycles) | 1,000,000 min.   | cycles |

#### NOTES:

- Minimum DC voltage on input or input or I/Os is -0.5V. During voltage transitions, inputs or I/Os may overshoot Vss to -2.0V for periods of up to 20ns. Maximum DC voltage on input or I/Os us VCC + 0.5V. During voltage transitions, input or I/O pins may overshoot to Vcc + 2.0V for periods up to 20ns

- Minimum DC input voltage on pins A9, OE#, and ACC is 0.5V. During voltage transitions, A9, OE#, and ACC may overshoot Vss to -2.0V for periods of up to 20ns. Maximum DC input voltage on pin A9, OE#, and ACC is +12.5V which may overshoot to +14.0V for periods up to 20ns

- No more than one output may be shorted to ground at a time. Duration of the short circuit should not be greater than one second.

- 4. Stresses above those listed under Absolute Maxium Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of the data sheet is not implied. Exposure of the device to absolute maxium rating conditions for extended peroids may affect device reliability

#### RECOMMENDED OPERATING CONDITIONS

| Parameter              | Symbol | Min | Max  | Unit |

|------------------------|--------|-----|------|------|

| Supply Voltage         | Vcc    | 3.0 | 3.6  | V    |

| Operating Temp. (Mil.) | TA     | -55 | +125 | °C   |

| Operating Temp. (Ind.) | TA     | -40 | +85  | °C   |

#### **CAPACITANCE**

$T_A = +25$ °C, F = 1.0MHz

| Parameter                 | Symbol           | Max | Unit |

|---------------------------|------------------|-----|------|

| WE1-4# capacitance        | Cwe              | TBD | pF   |

| CS1-4# capacitance        | Ccs              | TBD | pF   |

| Data I/O capacitance      | C <sub>I/O</sub> | TBD | pF   |

| Address input capacitance | C <sub>AD</sub>  | TBD | pF   |

| RESET# capacitance        | C <sub>RS</sub>  | TBD | pF   |

| RY/BY# capacitance        | C <sub>RB</sub>  | TBD | pF   |

| OE# capacitance           | COE              | TBD | pF   |

This parameter is guaranteed by design but not tested.

#### **DATA RETENTION**

| Parameter      | Test Conditions | Min | Unit  |

|----------------|-----------------|-----|-------|

| Pattern Data   | 150°C           | 10  | Years |

| Retention Time | 125°C           | 20  | Years |

#### DC CHARACTERISTICS - CMOS COMPATIBLE

$V_{CC} = 3.3V \pm 0.3V, -55^{\circ}C \le T_{A} \le +125^{\circ}C$

| Parameter                                                | Symbol          | Conditions                                                                                                       | Min                    | Тур | Max                    | Unit |

|----------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| Input Load Current (1)                                   | lu              | VIN = Vss to Vcc, #Vcc = Vcc(MAX)                                                                                |                        |     | WP/ACC: ±2.0           |      |

|                                                          |                 |                                                                                                                  |                        |     | Others: ±1.0           | μΑ   |

| A9 Input Load Current                                    | Ішт             | Vcc = to Vcc(MAX); A9 = 12.5V                                                                                    |                        |     | 35                     | μA   |

| Output Leakage Current                                   | ILO             | Vout = Vss to Vcc, # Vcc = Vcc(MAX)                                                                              |                        |     | ±1.0                   | μΑ   |

| www.DataSheet4U.com                                      | l               | CE# = V <sub>IL</sub> #, OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub> ; # f = 1 MHz, Byte Mode |                        | 24  | 80                     | mA   |

| Vcc Active Current for Read (1)                          | lcc1            | CE# = VIL#, OE# = VIH, VCC = VCC(MAX); # f = 5MHz, Word Mode                                                     |                        | 120 | 200                    | mA   |

| Vcc Intra-Page Read Current (1)                          | Icc2            | CE# = V <sub>IL</sub> #, OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub> ; f = 10MHz              |                        | 1   | 10                     | mA   |

| Vcc Active Erase/Program Current (2,3)                   | Іссз            | CE# = V <sub>IL</sub> #, OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub>                          |                        | 200 | 320                    | mA   |

| Vcc Standby Current                                      | Icc4            | Vcc = Vcc(MAX); Vio = Vcc; OE# = ViH; # ViL = Vss + 0.3V/-0.1V; # CE#, RESET# = Vss ± 0.3V                       |                        | 4   | 20                     | μΑ   |

| Vcc Reset Current                                        | Icc5            | Vcc = Vcc(MAX); Vio = Vss + 0.3V/-<br>0.1V; RESET# = Vss ± 0.3V                                                  |                        | 4   | 20                     | μΑ   |

| Automatic Sleep Mode (4)                                 | Icc6            | Vcc = Vcc(MAX); Vio = Vcc; Vih = Vcc ± 0.3V; #ViL = Vss + 0.3V/- 0.1V; WP#/Acc = Vih                             |                        | 4   | 20                     | μA   |

|                                                          |                 | CE# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , V <sub>CC</sub> =                                                | WP#/Acc pin            | 40  | 80                     |      |

| Acc Accelerated Program Current                          | IACC            | Vcc(MAX), #WP#/Acc = ViH                                                                                         | V <sub>CC</sub> pin    | 200 | 320                    | mA   |

| Input Low Voltage (5)                                    | VIL             |                                                                                                                  | -0.1                   |     | 0.3 x V <sub>IO</sub>  | V    |

| Input High Voltage (5)                                   | VIH             |                                                                                                                  | 0.7 x V <sub>IO</sub>  |     | V <sub>IO</sub> + 0.3  | V    |

| Voltage for ACC Erase/Program Acceleration               | V <sub>НН</sub> | V <sub>CC</sub> = 2.7 - 3.6V                                                                                     | 11.5                   |     | 12.5                   | V    |

| Voltage for Autoselect and Temporary<br>Sector Unprotect | VID             | Vcc = 2.7 - 3.6V                                                                                                 | 11.5                   |     | 12.5                   | V    |

| Output Low Voltage (5)                                   | Vol             | I <sub>OL</sub> = -100 μA                                                                                        |                        |     | 0.15 x V <sub>IO</sub> | V    |

| Output High Voltage (5)                                  | Voн             | I <sub>OH</sub> = -100 µA                                                                                        | 0.85 x V <sub>IO</sub> |     |                        | V    |

| Low Vcc Lock-Out Voltage                                 | VLKO            |                                                                                                                  | 2.3                    |     | 2.5                    | V    |

#### NOTES:

- 1. The lcc current is typically less than 2 mA/MHz, with OE# at VIH

- 2. Icc active while Embedded Erase or Embedded Program or Write Buffer Programming is in progress.

- 3. Not 100% tested

- 4. Automatic sleep mode enables the lower power mode when addresses remain stable for tacc + 30ns.

- 5. V<sub>IO</sub> = 1.65-1.95V or 2.7-3.6V.

- 6. Vcc = 3 V and Vlo = 3V or 1.8V. When Vlo is at 1.8V, I/O pins cannot operate at 3V.

#### AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS - WE# CONTROLLED

$V_{CC} = 3.3V \pm 0.3V, -55^{\circ}C \le T_{A} \le +125^{\circ}C$

| Parameter                                               | Syr    | nbol  | -1<br>Min | 00<br>Max | -12<br>Min | 20<br>Max | Unit |

|---------------------------------------------------------|--------|-------|-----------|-----------|------------|-----------|------|

| Write Cycle Time (3)                                    | tavav  | twc   | 100       |           | 120        |           | ns   |

| Chip Select Setup Time (3)                              | telwl  | tcs   | 0         |           | 0          |           | ns   |

| Write Enable Pulse Width                                | tww    | twp   | 35        |           | 50         |           | ns   |

| Address Setup Time                                      | tavwl  | tas   | 0         |           | 0          |           | ns   |

| Data Setup Timeeet 4U.com                               | tоvwн  | tos   | 45        |           | 50         |           | ns   |

| Data Hold Time                                          | twndx  | tон   | 0         |           | 0          |           | ns   |

| Address Hold Time                                       | twlax  | tан   | 45        |           | 50         |           | ns   |

| Write Enable Pulse Width High (3)                       | twhwL  | twph  | 30        |           | 30         |           | ns   |

| Duration of Byte Programming Operation (1)              | twnwh1 |       |           | 500       |            | 500       | μs   |

| Sector Erase (2)                                        | twhwh2 |       |           | 3.5       |            | 5         | sec  |

| Read Recovery Time before Write (3)                     | tghwl  |       | 0         |           | 0          |           | ns   |

| VCC Setup Time                                          | tvcs   |       | 50        |           | 50         |           | μs   |

| Address Setup Time to OE# low during toggle bit polling |        | taso  | 15        |           | 15         |           | ns   |

| Write Recovery Time from RY/BY# (3)                     |        | trв   | 0         |           | 0          |           | ns   |

| Program/Erase Valid to RY/BY#                           |        | tBUSY | 90        |           | 90         |           | ns   |

#### NOTES:

- 1. Typical value for twhwh1 is 60 μs.

- 2. Typical value for twhwh2 is 0.5 sec.

- 3. Guaranteed by design, but not tested.

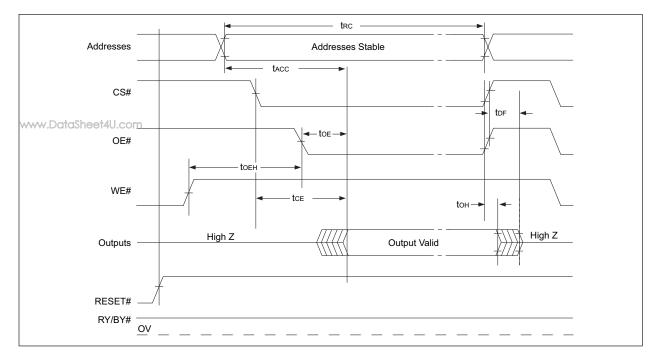

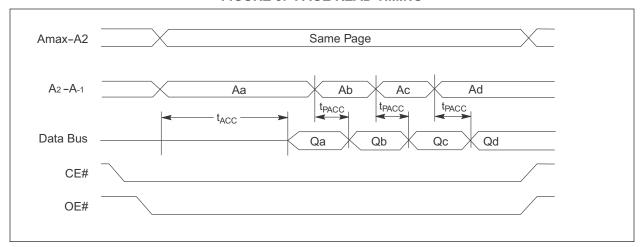

#### AC CHARACTERISTICS - READ-ONLY OPERATIONS

$V_{CC} = 3.3V \pm 0.3V, -55^{\circ}C \le T_{A} \le +125^{\circ}C$

| Parameter                                                 | Parameter                |       | Symbol          |     | -100<br>Min Max |     | -120<br>Min Max |    |

|-----------------------------------------------------------|--------------------------|-------|-----------------|-----|-----------------|-----|-----------------|----|

| Read Cycle Time (1)                                       |                          | tavav | t <sub>RC</sub> | 100 |                 | 120 |                 | ns |

| Address Access Time                                       |                          | tavqv | tacc            |     | 100             |     | 120             | ns |

| Chip Select Access Time                                   |                          | tELQV | tce             |     | 100             |     | 120             | ns |

| Page Access Time                                          |                          |       | <b>t</b> PACC   |     | 25              |     | 30              | ns |

| Output Enable to Output Valid                             |                          | tglqv | toe             |     | 25              |     | 35              | ns |

| Chip Select High to Output High Z                         |                          | tehqz | tor             |     | 20              |     | 20              | ns |

| Output Enable High to Output High Z                       |                          | tgнqz | tor             |     | 20              |     | 20              | ns |

| Output Hold from Addresses, CS# or Whichever occurs first | OE# Change,              | taxqx | tон             | 0   |                 | 0   |                 | ns |

| Output Enable Hold Time (1)                               | Read                     |       | tоен            | 0   |                 | 0   |                 | ns |

|                                                           | Toggle and Data# Polling |       |                 | 10  |                 | 10  |                 | ns |

<sup>1.</sup> Guaranteed by design, not tested.

#### FIGURE 3: PAGE READ TIMING

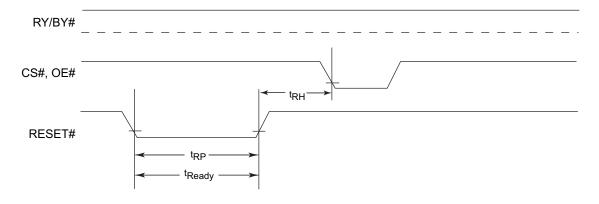

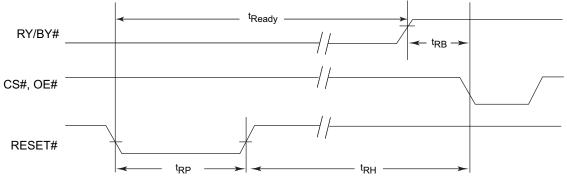

#### AC CHARACTERISTICS – HARDWARE RESET (RESET#)

| Parameter                                                        | Symbol           |     |     | Unit |

|------------------------------------------------------------------|------------------|-----|-----|------|

| 1 4141113101                                                     |                  | Min | Max | J    |

| RESET# Pin Low (During Embedded Algorithms) to Read Mode (1)     | tready           |     | 20  | μs   |

| RESET# Pin Low (NOT During Embedded Algorithms) to Read Mode (1) | tready           |     | 500 | ns   |

| RESET# Pulse Width                                               | t <sub>RP</sub>  | 500 |     | ns   |

| RESET# High Time Before Read (1)                                 | t <sub>RH</sub>  | 50  |     | ns   |

| RESET# Low to Standby Mode (1)                                   | t <sub>RPD</sub> | 20  |     | μs   |

| RY/BY# Recovery Time                                             | trB              | 0   |     | ns   |

NOTE: 1. Not tested.

#### FIGURE 4: RESET TIMINGS NOT DURING EMBEDDED ALGORITHMS

#### FIGURE 5: RESET TIMINGS DURING EMBEDDED ALGORITHMS

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

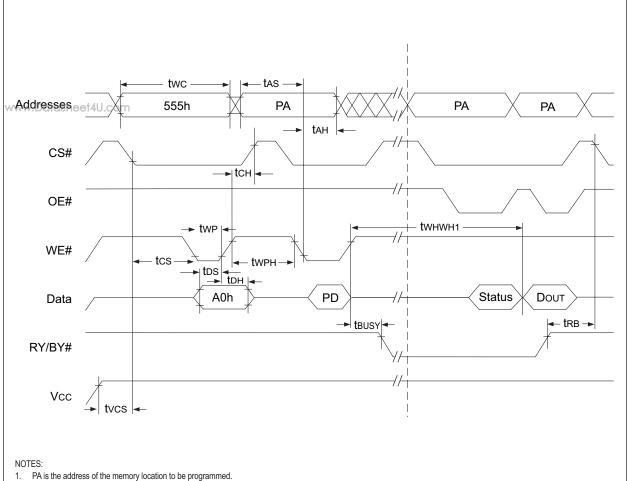

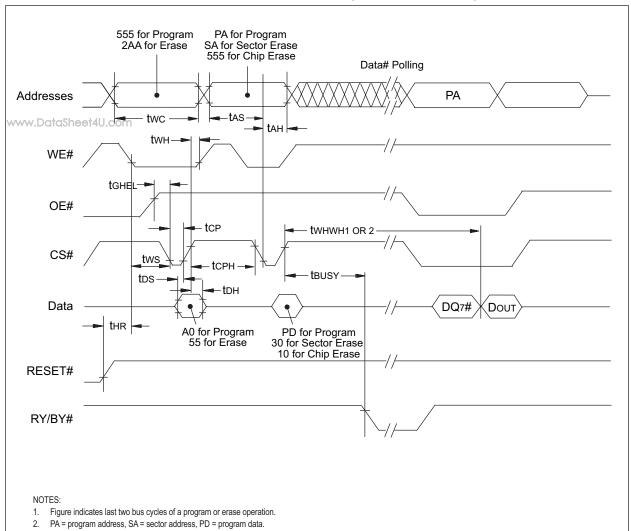

#### FIGURE 6: PROGRAM OPERATIONS

- PD is the data to be programmed at byte address.

- Dout is the output of the data written to the device.

- 4. Figure indicates last two bus cycles of four bus cycle sequence.

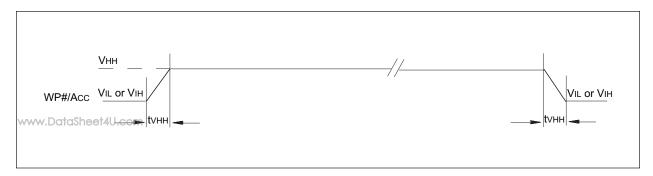

#### FIGURE 7: ACCELERATED PROGRAM TIMING DIAGRAM

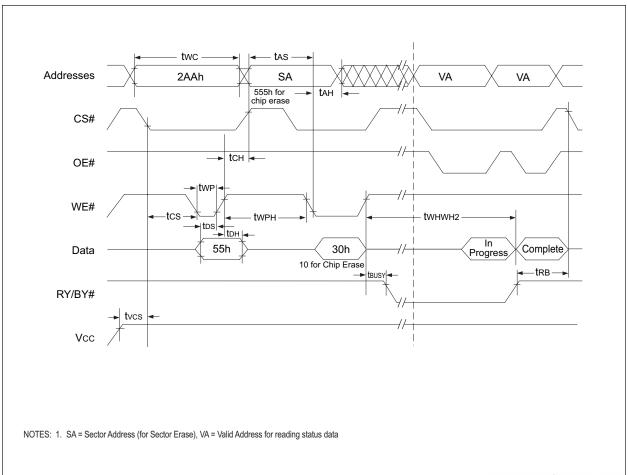

FIGURE 8: CHIP/SECTOR ERASE OPERATION TIMINGS

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

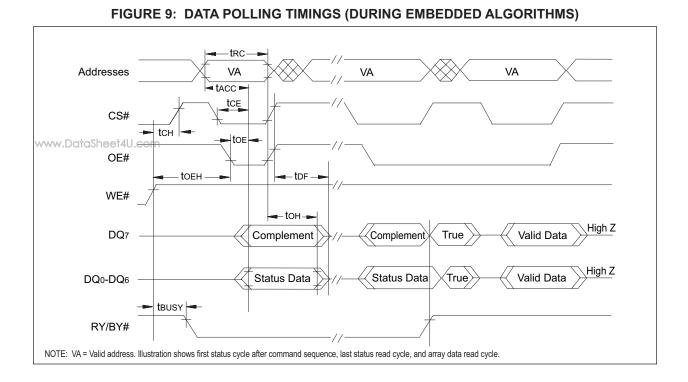

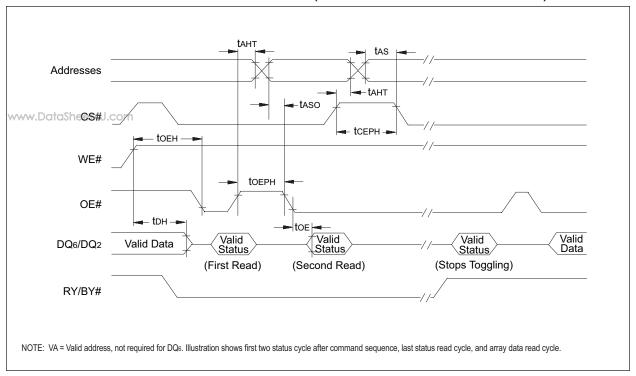

### FIGURE 10: TOGGLE BIT TIMINGS (DURING EMBEDDED ALGORITHMS)

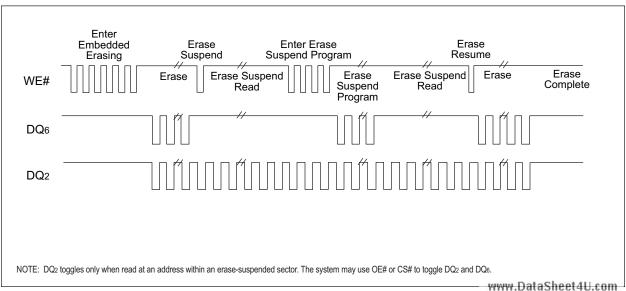

FIGURE 11: DQ2 Vs. DQ6

White Electronic Designs Corp. reserves the right to change products or specifications without notice

#### AC CHARACTERISTICS - ALTERNATE CS# CONTROLLED ERASE AND PROGRAM OPERATIONS

| Parai                 | meter    |                                                       |     | Speed | Options |      |

|-----------------------|----------|-------------------------------------------------------|-----|-------|---------|------|

| JEDEC                 | Std      | Description                                           |     | 100   | 120     | Unit |

| tavav                 | twc      | Write Cycle Time (1)                                  | Min | 100   | 120     | ns   |

| tavwl                 | tas      | Address Setup Time                                    | Min | 0     | 0       | ns   |

| telax                 | tан      | Address Hold Time                                     | Min | 45    | 50      | ns   |

| toveh                 | tos      | Data Setup Time                                       | Min | 45    | 50      | ns   |

| tehdx                 | tон      | Data Hold Time                                        | Min | 0     | 0       | ns   |

| Wytghel <sup>Da</sup> | aShee141 | Read Recovery Time Before Write (OE# High to WE# Low) | Min | 0     | 0       | ns   |

| twlel                 | Tws      | WE# Setup Time                                        | Min | 0     | 0       | ns   |

| tehwh                 | twн      | WE# Hold Time                                         | Min | 0     | 0       | ns   |

| teleh                 | tcp      | CS# Pulse Width                                       | Min | 35    | 35      | ns   |

| tehel                 | tсрн     | CS# Pulse Width High                                  | Min | 30    | 30      | ns   |

| twnwh1                | twnwh1   | Programming Operation                                 | Тур | 60    | 6       | μs   |

| twnwh1                | twnwh1   | Accelerated Programming Operation                     | Тур | 54    | 54      | μs   |

| twhwh2                | twhwh2   | Sector Erase Operation                                | Тур | 0.5   | 05      | sec  |

NOTE: 1. Not tested.

ADVANCED\*

### FIGURE 12: ALTERNATE CS# CONTROLLED WRITE (ERASE/PROGRAM) OPERATION TIMINGS

3. DQ7 is the complement of the data written to the device. Dout is the data written to the device.

ADVANCED\*

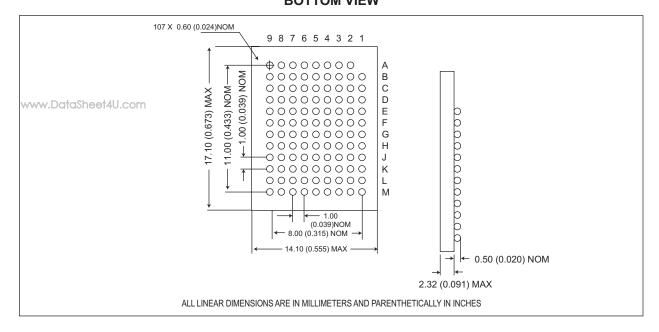

# PACKAGE: 107 PBGA (PLASTIC BALL GRID ARRAY) BOTTOM VIEW

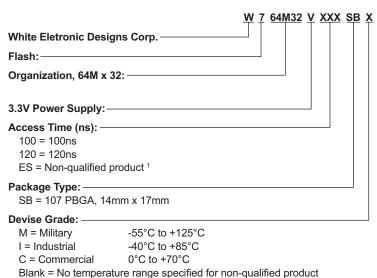

#### **ORDERING INFORMATION**

NOTE 1: W764M32V-ESSB is only available product until completion of qualification.

### **Document Title**

64Mx32 Flash 3.3V

# **Revision History**

| Rev#                | History                                                                                                                             | Release Date  | Status   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------|----------|

| Rev 0               | Initial Release                                                                                                                     | November 2005 | Advanced |

| www.DataSh<br>Rev 1 | changes (All Pages)  1.1 Add AC + DC characteristics and timing diagrams  1.2 Update package dimensions  1.3 Add preliminary pinout | February 2006 | Advanced |

| Rev 2               | Changes (Pg. 1, 3, 16) 2.1 Correct typographical error in pinout on page 3, ball 'B4' is DQ9                                        | March 2006    | Advanced |