## 3-IN-1 10/100M FAST ETHERNET CONTROLLER

# W89C841F/D

# 3-IN-1 100BASE-TX/FX & 10BASE-T Ethernet Controller

The information described in this document is the exclusive intellectual property of Winbond Electronics Corporation and shall not be reproduced without permission from Winbond.

Winbond is providing this document only for reference purposes of W89C841F-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

PC, AT and IBM are registered trademarks of International Business Machines, Inc. DOS and Windows are registered trademarks of Microsoft corporation. All other trademarks mentioned in this document are property of their respective owners.

For additional information or questions, please contact:

Winbond Electronics Corp.

### Table of Contents-

| 1. GENERAL DESCRIPTION                                  | 4                                       |

|---------------------------------------------------------|-----------------------------------------|

| 2. FEATURES                                             | 4                                       |

| 3. PIN CONFIGURATIONS                                   | 6                                       |

| 4. PIN DESCRIPTION                                      | g                                       |

| PCI Interface                                           |                                         |

| Power Management Interface                              | 14                                      |

| BootROM/Flash and EEPROM Interface                      | 15                                      |

| Transceiver Interface                                   | 19                                      |

| LED Interface                                           |                                         |

| Configuration and Test Interface                        |                                         |

| Power Pins                                              | 20                                      |

| 5. BLOCK DIAGRAM                                        | 23                                      |

| 6. SYSTEM DIAGRAM                                       | 24                                      |

| 7. FUNCTIONAL DESCRIPTION                               | 25                                      |

| Operation Mode Configuration                            | 25                                      |

| Direct Memory Access Function                           |                                         |

| Media Access Control (MAC) Function                     |                                         |

| Full Duplex and Half Duplex Function                    |                                         |

| Network Media Speed Function                            |                                         |

| Flow Control in Full Duplex Mode                        |                                         |

| Priority Tagged Frame Supporting QOS                    |                                         |

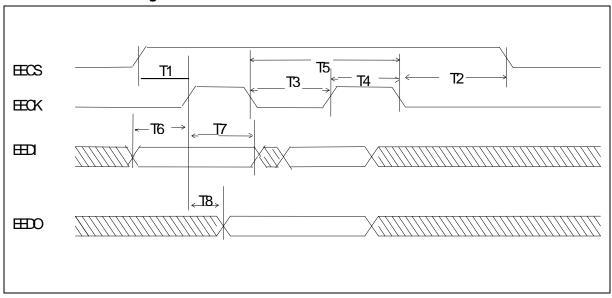

| EEPROM Auto-load and Software Programming Function      |                                         |

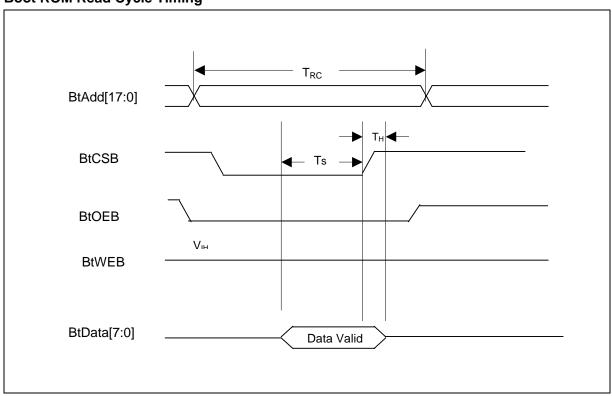

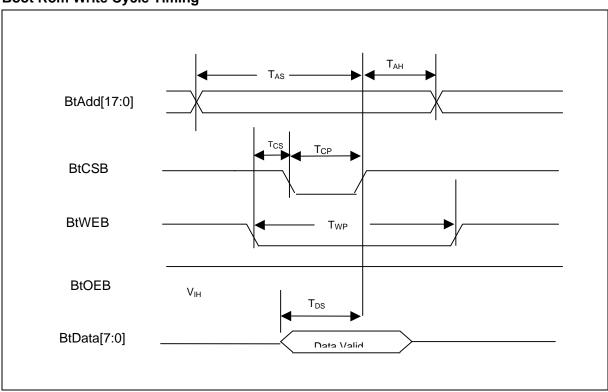

| BootROM Read and Flash Programming Function             |                                         |

| System Resource Configuring                             |                                         |

| Power Management Function                               |                                         |

| 8. CONFIGURATION REGISTERS                              |                                         |

| Configuration Register Mapping                          |                                         |

| 9. FUNCTION REGISTERS                                   |                                         |

| Cxx Function Registers                                  |                                         |

| Dxx Function Registers                                  |                                         |

| MII Management Registers                                |                                         |

| 10. ELECTRICAL CHARACTERISTICS                          | 90                                      |

| Absolute Maximum Ratings                                | • • • • • • • • • • • • • • • • • • • • |

| Power Supply                                            |                                         |

| DC Characteristics                                      |                                         |

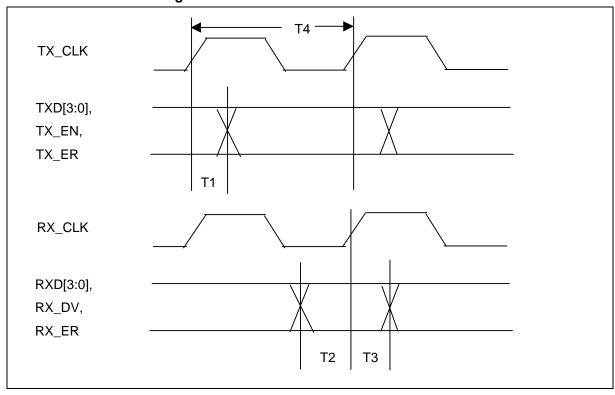

| AC Characteristics                                      | 91                                      |

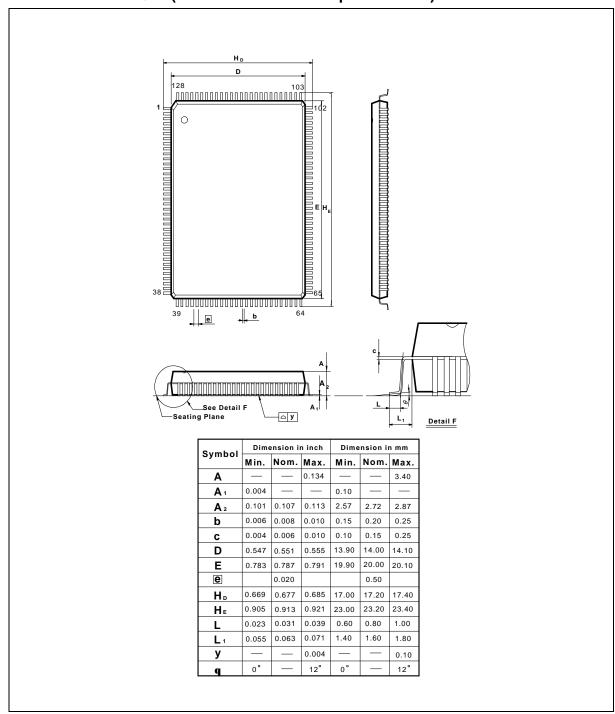

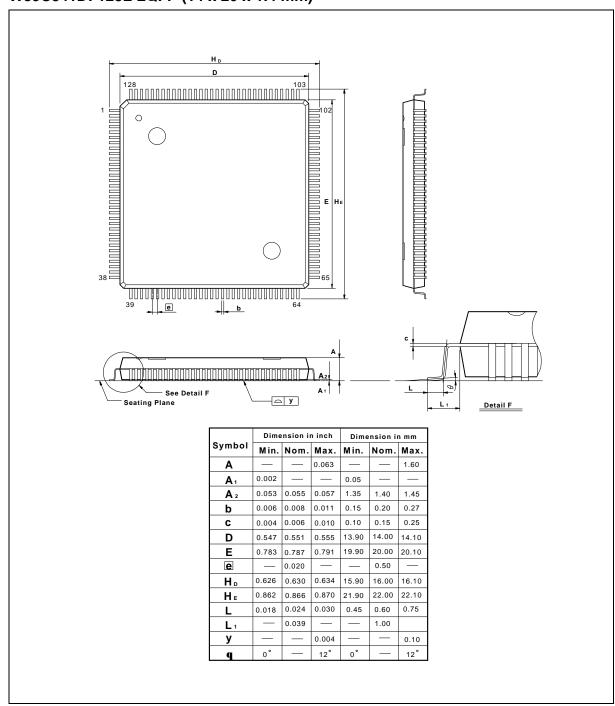

| 11. PACKAGE DIMENSIONS                                  | 100                                     |

| W89C841F: 128L QFP (14 x 20 x 2.75 mm footprint 3.2 mm) |                                         |

| W89C841D: 128L LQFP (14 x 20 x 1.4 mm)                  | 101                                     |

#### 1. GENERAL DESCRIPTION

W89C841F is a highly integrated PCI Fast Ethernet MAC controller with embedded Ethernet transceiver for 100BaseTX, 100BaseFX and 10BaseT. It is compliant with IEEE 802.3, 802.3u specification. Auto cross-over function is supported on TP terminal and the network status of W89C841F is indicated by 3 LED pins. W89C841F supports full/half duplex, asymmetrical flow control operation compliant with IEEE 802.3x and VLAN tagged frame compliant with IEEE 802.1p.

According to different applications, W89C841F can be configured into one of 3 modes to operate by setting the pins CONFIG[1:0] and ModeSel[2:0] after power-on reset. The 3 operational modes of W89C841F are listed as below.

- 1. PCI Ethernet MAC controller with internal Ethernet PHYceiver.

- 2. Pure PCI Ethernet MAC Controller

- 3. Pure 10/100M PHYceiver

W89C841F provides a host bus interface complying with the PCI local bus specification R2.2, Mini PCI Specification R1.0 and CardBus. W89C841F plays as a bus master role to improve network performance and reduce the bus utilization. There are built-in 2K bytes TX FIFO and 2K bytes RX FIFO to store data. The DMA controller handles the data transfer between the host memory and the FIFOs. The data received from network are queued into the RX FIFO then directly moved into the host memory through the PCI bus. On the other hand, the transmitted data are fetched from the host memory and directly queued into the transmit FIFO. No extra on-board memory is needed for data buffering during operation.

For PC99/2001, W89C841F implements power management function that are compliant with Advanced Configuration and Power Interface (ACPI) specification R1.0, PCI Power Management Interface specification R1.1 and Network Device Class Power Management Reference specification V1.0a. W89C841F supports D3<sub>cold</sub> power management state if auxiliary power is detected. 3 types of wakeup events are acceptable like link status change, Magic Packet and 5 sets of wake-up frames.

EEPROM (93C46) is supported by W89C841F to store configuration and Vital Product Data (VPD) information. The length of VPD information is up to 64 bytes. W89C841F can access the CardBus information Structure (CIS) information that is stored at EEPROM (93C56) or BootROM. W89C841F also supports BootROM/Flash interface to read/write BootROM or Flash memory.

#### 2. FEATURES

- Integrated Fast Ethernet MAC controller with 10/100M Ethernet transceiver in one chip

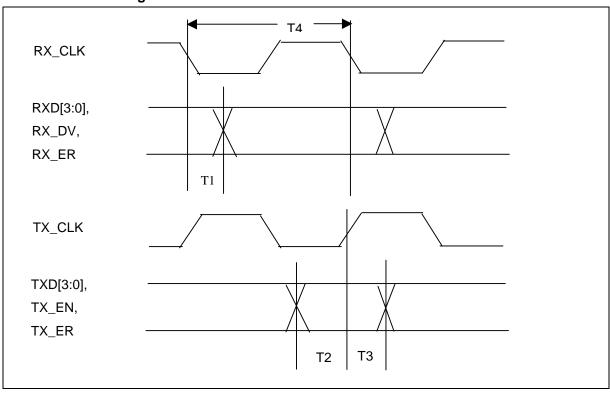

- Supports MII interface for programmable single PHYceiver or single MAC controller

- Complies with IEEE 802.3, 802.3u specification

- Supports 10BAST-T, 100BASE-TX and 100BASE-FX

- Supports auto cross-over operation

- Supports half duplex and full duplex for 10/100M operation

- Supports flow control for full duplex mode compliant with IEEE 802.3x

- Complies with IEEE802.3ac, 802.1Q for VLAN-tagged frame

- Supports LED pins for network activity indication

- Configurable to PCI, MiniPCI or CardBus bus interface

- Supports PCI/MiniPCI bus master mode for DMA operation, fully compliant with PCI Local Bus Specification R2.2 and Mini PCI Specification R1.0

- Supports CardBus Information Structure (CIS)

- Supports 25 to 33 MHz PCI clock speed

- Compliant with APCI R1.0, PCI power management R1.1 and Network device Class Power management Reference specification V1.0a

- Supports power management event asserted from D3<sub>(cold)</sub> device state with auxiliary power existing

- Supports wakeup function for Link status change, Magic Packet and 5 sets of wakeup frames

- Supports Vital Product Data (VPD) data structure up to 64 Bytes

- Supports 2 sets of independent embedded 2K bytes FIFO for transmit and receive

- Flexible multicast address filtering modes

- 64-bit hash-table

- All multicast and promiscuous

- Supports 25 MHz crystal or oscillator as internal clock source

- Provides EEPROM (93C46 or 93C56) to store configuration parameters, VPD, and CIS information

- Supports 8KB to 256 KB BootROM interface for both PROM and Flash memory

- 3.3V powered I/Os with 5V tolerant inputs

- Packaged in 128-pin PQFP for W89C841F/ LQFP for W89C841D

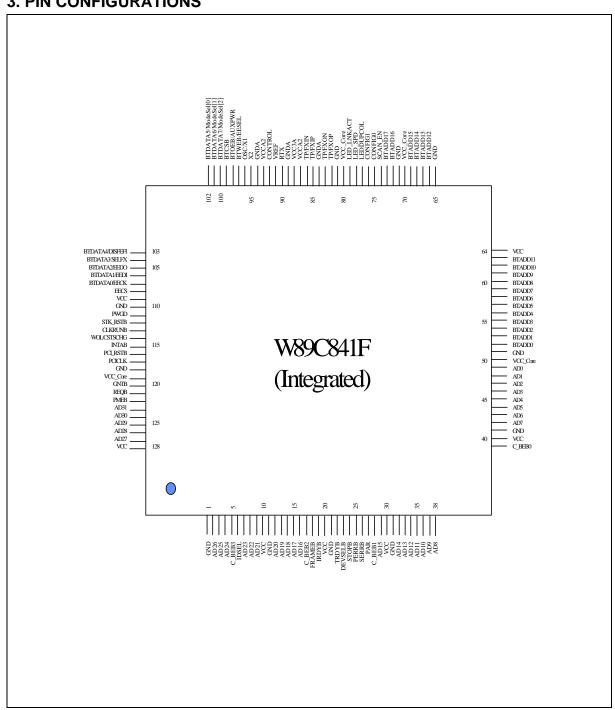

#### 3. PIN CONFIGURATIONS

Figure 1. W89C841F Pin Configuration (Integrated)

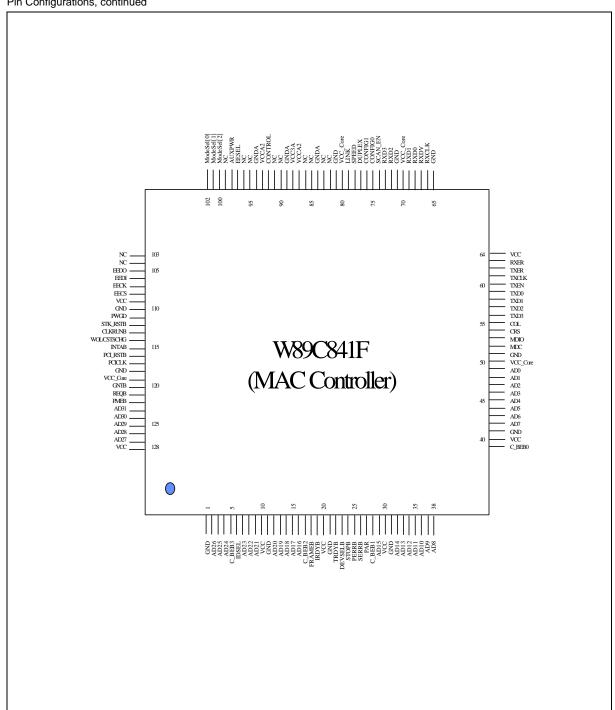

#### Pin Configurations, continued

Figure 1. W89C841F Pin Configuration (MAC Controller)

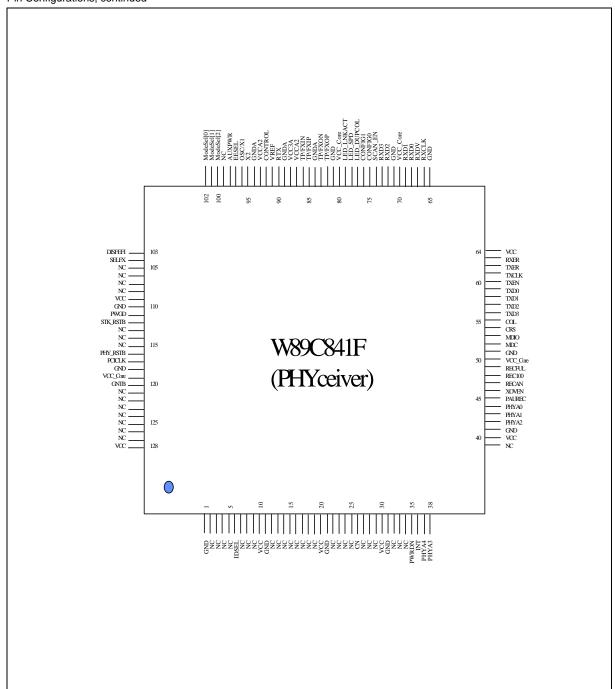

Pin Configurations, continued

Figure 1. W89C841F Pin Configuration (PHYceiver)

### 4. PIN DESCRIPTION

### **PCI** Interface

| CICNAL NAME      | DIN TVD     | DIN NO                                   | DESCRIPTION                                                                                                                                                                           |

|------------------|-------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL NAME      | PIN TYP.    | PIN NO.                                  | DESCRIPTION                                                                                                                                                                           |

| PCICLK           | l           | 117                                      | PCI Clock Input                                                                                                                                                                       |

|                  |             |                                          | A. Normal and MAC mode                                                                                                                                                                |

|                  |             |                                          | W89C841F supports PCI clock rate ranged from 25 MHz to 33 MHz continuously. All PCI signals except PCI_RSTB and INTAB are referenced on the rising edge of this clock.                |

|                  |             |                                          | B. PHYceiver mode                                                                                                                                                                     |

|                  |             |                                          | This pin should be pulled low.                                                                                                                                                        |

| PCI_RSTB/        | I           | 116                                      | PCI Hardware Reset Signal (Normal and MAC mode)                                                                                                                                       |

| PHY_RSTB         |             |                                          | When asserted (active low), all PCI output pins of W89C841F will be in high impedance state, and all open drain signals will be floated.                                              |

|                  |             |                                          | The configurations inside W89C841F will be in its initial state. This signal must be asserted for a period of at least 10 PCI clocks to correctly take effect of a reset on hardware. |

|                  |             |                                          | PHYceiver Reset (PHYceiver Mode)                                                                                                                                                      |

|                  |             |                                          | This pin is used as to reset PHYceiver.                                                                                                                                               |

| AD[31:12]        | IO/TS       | 123 – 127,                               | PCI Multiplexed Address[31:12] and Data Bus[31:12]                                                                                                                                    |

|                  |             | 2 - 4, 7 - 9,<br>12 - 16, 29,<br>32 - 34 | During the first cycle that FRAMEB asserts, they act as an address bus; on the other cycles, they are switched to be a data bus.                                                      |

| AD[11]/<br>PWRDN | IO/TS/      | 35                                       | PCI Multiplexed Address[11] and Data Bus[11] (Normal and MAC mode)                                                                                                                    |

|                  | •           |                                          | Power Down Enable (PHYceiver Mode)                                                                                                                                                    |

|                  |             |                                          | 1: Power Saving.                                                                                                                                                                      |

|                  |             |                                          | 0: Normal.                                                                                                                                                                            |

| AD[10]/<br>INT   | IO/TS/<br>O | 36                                       | PCI Multiplexed Address[10] and Data Bus[10] (Normal and MAC mode)                                                                                                                    |

|                  |             |                                          | PHY Interrupt (PHYceiver Mode)                                                                                                                                                        |

|                  |             |                                          | Output low that is asserted to indicate an active interrupt event has occurred.                                                                                                       |

| SIGNAL NAME      | PIN TYP. | PIN NO.  | DESCRIPTION                                                            |

|------------------|----------|----------|------------------------------------------------------------------------|

| AD[9:5]/         | IO/TS/   | 37 – 38, | PCI Multiplexed Address[9:5] and Data Bus[9:5] (Normal and MAC mode)   |

| PHYA[4:0]        | ı        | 42 – 44  | PHY Address (PHYceiver Mode)                                           |

|                  |          |          | These pins indicate PHYceiver's address used for MII magement function |

| AD[4]/<br>PAUREC | IO/TS/   | 45       | PCI Multiplexed Address[4] and Data Bus[4] (Normal and MAC mode)       |

|                  | -        |          | Pause Capability Recommend (PHYceiver Mode)                            |

|                  |          |          | This pin is recommended value for capability at full duplex operation. |

|                  |          |          | 1: With pause capability                                               |

|                  |          |          | 0: No pause capability                                                 |

| AD[3]/<br>XOVEN  | IO/TS/   | 46       | PCI Multiplexed Address[3] and Data Bus[3] (Normal and MAC mode)       |

| 7101211          | •        |          | Auto Cross Over Enable (PHYceiver Mode)                                |

|                  |          |          | In twist pair mode, this pin controls the function of cross over.      |

|                  |          |          | 1: Enable                                                              |

|                  |          |          | 0: Disable                                                             |

| AD[2]/<br>RECAN  | IO/TS/   | 47       | PCI Multiplexed Address[2] and Data Bus[2] (Normal and MAC mode)       |

|                  | -        |          | Auto Negotiation Enable (PHYceiver Mode)                               |

|                  |          |          | 1: Enable                                                              |

|                  |          |          | 0: Disable                                                             |

| AD[1]/<br>REC100 | IO/TS/   | 48       | PCI Multiplexed Address[1] and Data Bus[1] (Normal and MAC mode)       |

|                  | •        |          | Recommend 100M (PHYceiver Mode)                                        |

|                  |          |          | 1: 100M                                                                |

|                  |          |          | 0: 10M                                                                 |

| AD[0]/<br>RECFUL | IO/TS/   | 49       | PCI Multiplexed Address[1] and Data Bus[1] (Normal and MAC mode)       |

|                  | ,        |          | Recommend Duplex (PHYceiver Mode)                                      |

|                  |          |          | 1: Full Duplex                                                         |

|                  |          |          | 0: Half Duplex                                                         |

| SIGNAL NAME | PIN TYP. | PIN NO.       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_BEB[3:0]  | IO/TS    | 5, 17, 28, 39 | Multiplexed Command and Byte Enables                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |          |               | These signals are driven by current bus master. During address phase, they mean a bus command. On the other phase, they present the byte enable of the transaction.                                                                                                                                                                                                                                                                                                 |

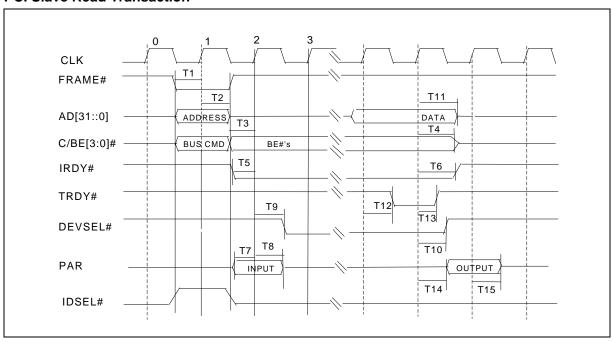

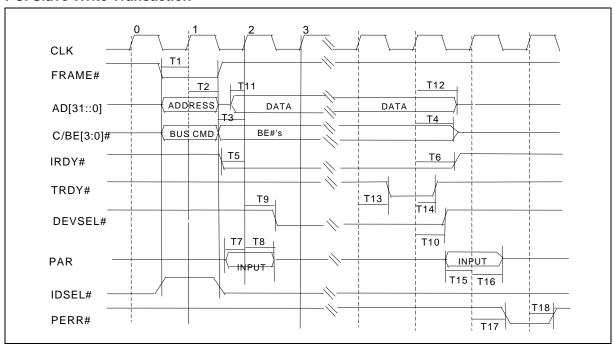

| PAR         | IO/TS    | 27            | Parity Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |          |               | This PAR represents the even parity across AD[31:0] and C_BEB[3:0]. It has the same timing as AD[31:0] but is delayed by one clock.                                                                                                                                                                                                                                                                                                                                 |

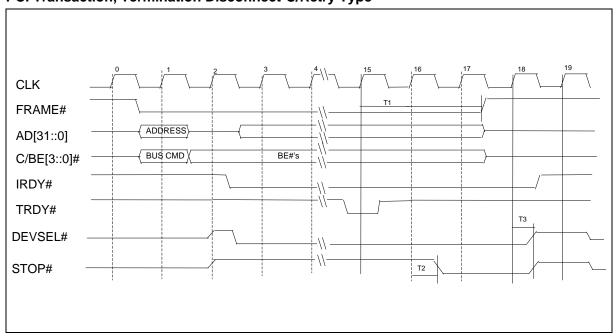

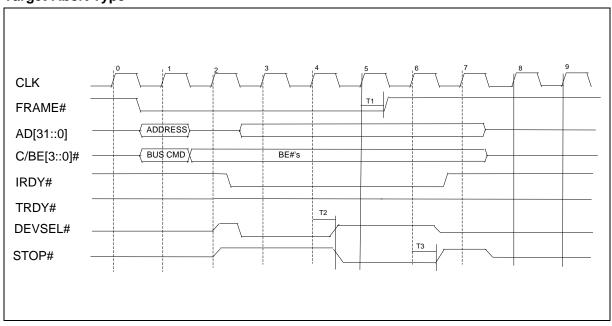

| FRAMEB      | IO/STS   | 18            | PCI Cycle Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |          |               | The current bus master asserts FRAMEB to indicate the beginning and duration of a bus access. This signal keeps asserted while the current transaction is ongoing and keeps deasserted to indicate that the next data phase is the final data phase.                                                                                                                                                                                                                |

| IRDYB       | IO/STS   | 19            | Initiator Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|             |          |               | The IRDYB is asserted by the current initiator to indicate the ability to complete the data transfer at the current data phase. The initiator asserts IRDYB to indicate the valid write data, or to indicate it is ready to accept the read data. More than or exactly one wait state will be inserted if IRDYB is deasserted during the current transaction. Data is transferred at the clock rising edge when both IRDYB and TRDYB are asserted at the same time. |

| TRDYB       | IO/STS   | 22            | Target Ready                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |          |               | Asserted by the current target to indicate ability to complete data transfer at the current data phase. When W89C841F is operating at the bus slave mode, it asserts TRDYB to indicate that the valid read data presents on the bus or to indicate it is ready to accept data. Wait states will be inserted if TRDYB is deasserted. Data is transferred at the rising edge of the PCI clock when IRDYB and TRDYB are both asserted at the same time.                |

| STOPB       | IO/STS   | 24            | PCI Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |          |               | Asserted by the current target to request PCI bus master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                           |

| SIGNAL NAME | PIN TYP. | PIN NO. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IDSEL       | I        | 6       | PCI Initialization Device Select                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |          |         | A. Normal and MAC mode                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |          |         | Asserted by host to signal the configuration access request to W89C841F.                                                                                                                                                                                                                                                                                                                                                                                     |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |          |         | This pin should be pulled to low.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DEVSELB     | IO/STS   | 23      | PCI Device Select                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |          |         | Asserted by the current target to indicate that it has finished decoding its address as the current access target. When W89C841F is the current master, it checks if the target asserted this signal within 5 PCI clocks after having issued command. If not, W89C841F will abort the access operation, releases PCI bus access right and acts no more bus master. When W89C841F is the target, it asserts DEVSELB in a medium speed, i.e., within 2 clocks. |

| REQB        | O/TS     | 121     | PCI Request                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             |          |         | Asserted by W89C841F to request bus ownership. REQB will be tri-stated when RSTB asserted.                                                                                                                                                                                                                                                                                                                                                                   |

| GNTB        | I/TS     | 120     | PCI Grant                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |          |         | A. Normal and MAC mode                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |          |         | Asserted by host to grant that W89C841F have got the bus ownership. When RSTB asserted, W89C841F will ignore GNTB.                                                                                                                                                                                                                                                                                                                                           |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |          |         | This pin should be pulled to high.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PERRB       | IO/STS   | 25      | PCI Parity Error                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |          |         | Asserted by the current data receiptor. When W89C841F acts the bus master, if a data parity error is detected and the parity error response bit (F04/FCS[6]) is also set, it will set both bits of F04/FCS[24] and C14/CISR[13] as 1 to terminate the current transaction after the current data phase is finished. When W89C841F acts the target, if a data parity error is detected and the bit F04/FCS[6] is set, it will assert PERRB only.              |

| SIGNAL NAME | PIN TYP. | PIN NO. | DESCRIPTION                                                                                                                                                                                                                                       |

|-------------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SERRB       | O/OD     | 26      | System Error                                                                                                                                                                                                                                      |

|             |          |         | This pin is asserted with one PCI clock width within two PCI clocks after an address parity error is detected, and keeps in high impedance state when idle. The interrupt function caused by this event is gated by the bits in F04/FCS register. |

|             |          |         | W89C841F will assert SERRB and will set a high to the Detect Parity Error bit F04/FCS[31] and the Signal System Erro bit F04/FCS[30] if an address parity error is detected and SERRB enable bit F04/FCS[8] is previously set to 1.               |

|             |          |         | The Bus Error Status bit C14/CISR[13] will be set to high if both an address parity error is detected and the parity error response bit F04/FCS[6] is set to high.                                                                                |

| INTAB       | O/OD     | 115     | Interrupt A                                                                                                                                                                                                                                       |

|             |          |         | INTAB is asserted when any one of unmasked interrupt bits in C14/CISR is set. It keeps asserted until all of the unmasked interrupt bits is cleared.                                                                                              |

# **Power Management Interface**

| SIGNAL NAME | PIN TYP. | PIN NO. | DESCRIPTION                                                                                                                                                                                                                                                                            |

|-------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STK_RSTB    | I/PU     | 112     | Sticky Reset Signal                                                                                                                                                                                                                                                                    |

|             |          |         | A. Normal and MAC mode                                                                                                                                                                                                                                                                 |

|             |          |         | Sticky_ResetB is a hardware reset signal which is generated from auxiliary power circuit if motherboard supports auxiliary power. So W89C841F can generate PMEB from D3 <sub>(cold)</sub> state to D0 state transition and preserve PME context bits: PME_Status and PME_Enable.       |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                                                                                                      |

|             |          |         | This pin should be floating.                                                                                                                                                                                                                                                           |

| PWGD        | I        | 111     | Power Good                                                                                                                                                                                                                                                                             |

|             |          |         | A. Normal and MAC mode                                                                                                                                                                                                                                                                 |

|             |          |         | When PWGD = 1, W89C841F is put in normal operation mode.                                                                                                                                                                                                                               |

|             |          |         | When PWGD = 0, it isolates any PCI input and has all PCI outputs kept in high impedance state. The PCI bus power can be off by operating system.                                                                                                                                       |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                                                                                                      |

|             |          |         | This pin should be pulled to high.                                                                                                                                                                                                                                                     |

| PMEB        | O/OD     | 122     | Power Management Event                                                                                                                                                                                                                                                                 |

|             |          |         | The PMEB signal indicates that a power management event has occurred, i.e. there is a magic packet received in suspend mode of host.                                                                                                                                                   |

| CLKRUNB     | I/OD     | 113     | Clock Run                                                                                                                                                                                                                                                                              |

|             |          |         | CLKRUNB is used to request starting or speeding up the PCI clock. It also indicates the PCI clock status.                                                                                                                                                                              |

|             |          |         | W89C841F requests the central resource to start, speed up, or maintain the PCICLK by the assertion of CLKRUNB. For the central resource, CLKRUNB is an S/T/S signal. The central resource is responsible for maintaining CLKRUNB asserted and for driving it high to deasserted state. |

Power Management Interface, continued

| SIGNAL NAME | PIN TYP. | PIN NO. | DESCRIPTION                                                                                                                                                                                                                  |

|-------------|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WOL/        | 0        | 114     | Wake on LAN Signal                                                                                                                                                                                                           |

| CSTSCHG     |          |         | The WOL signal indicates that a wake up event (Magic Packet, Link Status change and Wake-up frame) has been received. It is used to inform motherboard to execute wake-up process. The motherboard must support Wake-On-LAN. |

|             |          |         | There are 4 types of output: active high (default), active low, positive pulse, negative pulse.                                                                                                                              |

|             |          |         | CSTSCHG signal:                                                                                                                                                                                                              |

|             |          |         | This signal is used in CardBus application only and is used to inform motherboard to execute wake-up process whenever there is PMEB occurs. It is always an active high signal.                                              |

### **BootROM/Flash and EEPROM Interface**

| SIGNAL NAME   | PIN TYP. | PIN NO. | PIN DESCRIPTION                                |

|---------------|----------|---------|------------------------------------------------|

| BtAdd[17:14]/ | I/O/     | 73,     | BootROM Address (Normal Mode)                  |

| RXD[3:0]_MAC/ | I/       | 72,     | These pins are used as ROM address pins.       |

| RXD[3:0]_PHY  | 0        | 69,     | MII Receive Data (MAC mode)                    |

|               |          | 68      | These pins are used to input MII RXD signals.  |

|               |          |         | MII Receive Data (PHYceiver mode)              |

|               |          |         | These pins are used to output MII RXD signals. |

| BtAdd[13]/    | I/O/     | 67      | BootROM Address (Normal Mode)                  |

| RXDV_MAC/     | I/       |         | This pin is used as ROM address pin.           |

| RXDV_PHY      | 0        |         | MII Receive Data Valid (MAC mode)              |

|               |          |         | This pin is used to input MII RXDV signal.     |

|               |          |         | MII Receive Data Valid (PHYceiver mode)        |

|               |          |         | This pin is used to output MII RXDV signal.    |

| BtAdd[12]/    | I/O/     | 66      | BootROM Address (Normal Mode)                  |

| RXCLK_MAC/    | I/       |         | These pins are used as ROM address pin.        |

| RXCLK_PHY     | 0        |         | MII Receive Clock (MAC mode)                   |

|               |          |         | This pin is used to input MII RXCLK signal.    |

|               |          |         | MII Receive Clock (PHYceiver mode)             |

|               |          |         | This pin is used to output MII RXCLK signal.   |

BootROM/Flash and EEPROM Interface, continued

| SIGNAL NAME   | PIN TYP. | PIN NO. | PIN DESCRIPTION                                |

|---------------|----------|---------|------------------------------------------------|

| BtAdd[11]/    | I/O/     | 63      | BootROM Address (Normal Mode)                  |

| RXER_MAC/     | I/       |         | These pins are used as ROM address pin.        |

| RXER_PHY      | 0        |         | MII Receive Error (MAC mode)                   |

|               |          |         | This pin is used to input MII RXER signal.     |

|               |          |         | MII Receive Error (PHYceiver mode)             |

|               |          |         | This pin is used to output MII RXER signal.    |

| BtAdd[10]/    | I/O/     | 62      | BootROM Address (Normal Mode)                  |

| TXER_MAC/     | O/       |         | These pins are used as ROM address pin.        |

| TXER_PHY      | I        |         | MII Transmit Error (MAC mode)                  |

|               |          |         | This pin is used to output MII TXER signal.    |

|               |          |         | MII Transmit Error (PHYceiver mode)            |

|               |          |         | This pin is used to input MII TXER signal.     |

| BtAdd[9]/     | I/O/     | 61      | BootROM Address (Normal Mode)                  |

| TXCLK_MAC/    | I/       |         | These pins are used as ROM address pin.        |

| TXCLK_PHY     | 0        |         | MII Transmit Clock (MAC mode)                  |

|               |          |         | This pin is used to input MII TXCLK signal.    |

|               |          |         | MII Transmit Error (PHYceiver mode)            |

|               |          |         | This pin is used to output MII TXCLK signal.   |

| BtAdd[8]/     | I/O/     | 60      | BootROM Address (Normal Mode)                  |

| TXEN_MAC/     | O/       |         | These pins are used as ROM address pin.        |

| TXEN_PHY      | I        |         | MII Transmit Enable (MAC mode)                 |

|               |          |         | This pin is used to output MII TXEN signal.    |

|               |          |         | MII Transmit Enable (PHYceiver mode)           |

|               |          |         | This pin is used to input MII TXEN signal.     |

| BtAdd[7:4]/   | I/O/     | 59,     | BootROM Address (Normal Mode)                  |

| TXD[3:0]_MAC/ | O/       | 58,     | These pins are used as ROM address pins.       |

| TXD[3:0]_PHY  | I        | 57,     | MII Transmit Data (MAC mode)                   |

|               |          | 56      | These pins are used to output MII TXD signals. |

|               |          |         | MII Transmit Data (PHYceiver mode)             |

|               |          |         | These pins are used to input MII TXD signals.  |

BootROM/Flash and EEPROM Interface, continued

| SIGNAL NAME  | PIN TYP. | PIN NO.   | PIN DESCRIPTION                                                                         |

|--------------|----------|-----------|-----------------------------------------------------------------------------------------|

| BtAdd[3]/    | I/O/     | 55        | BootROM Address (Normal Mode)                                                           |

| COL_MAC/     | I/       |           | This pin is used as ROM address pin.                                                    |

| COL_PHY      | 0        |           | MII Collision (MAC mode)                                                                |

|              |          |           | This pin is used to input MII COL signal.                                               |

|              |          |           | MII Collision (PHYceiver mode)                                                          |

|              |          |           | This pin is used to output MII COL signal.                                              |

| BtAdd[2]/    | I/O/     | 54        | BootROM Address (Normal Mode)                                                           |

| CRS_MAC/     | I/       |           | This pin is used as ROM address pin.                                                    |

| CRS_PHY      | 0        |           | MII Carrier Sense (MAC mode)                                                            |

|              |          |           | This pin is used to input MII CRS signal.                                               |

|              |          |           | MII Carrier Sense (PHYceiver mode)                                                      |

|              |          |           | This pin is used to output MII CRS signal.                                              |

| BtAdd[1]/    | I/O      | 53        | BootROM Address (Normal Mode)                                                           |

| MDIO_MAC/    |          |           | This pin is used as ROM address pin.                                                    |

| MDIO_PHY     |          |           | MII Management Data (MAC mode)                                                          |

|              |          |           | This pin is used to input/output MII MDIO signal.                                       |

|              |          |           | MII Management Data (PHYceiver mode)                                                    |

|              |          |           | This pin is used to input/output MII MDIO signal.                                       |

| BtAdd[0]/    | I/O/     | 52        | BootROM Address (Normal Mode)                                                           |

| MDC_MAC/     | O/       |           | These pins are used as ROM address pin.                                                 |

| MDC_PHY      | 1        |           | MII Management Clock (MAC mode)                                                         |

|              |          |           | This pin is used to output MII MDC signal.                                              |

|              |          |           | MII Management Clock (PHYceiver mode)                                                   |

|              |          |           | This pin is used to input MII MDC signal.                                               |

| BtData[7:5]/ | I/O      | 100 – 102 | BootROM Data[7:5]                                                                       |

| ModeSel[2:0] |          |           | These pins are used as ROM data pins.                                                   |

|              |          |           | Mode Selection                                                                          |

|              |          |           | When power-on, these pins are used as input pins to latch the setting value of ModeSel. |

|              |          |           | Mode CONFIG ModeSel                                                                     |

|              |          |           | Normal 00 000                                                                           |

|              |          |           | MAC Controller 01 011                                                                   |

|              |          |           | PHYceiver 10 000                                                                        |

|              |          |           | Testing 11 xxx                                                                          |

BootROM/Flash and EEPROM Interface, continued

| SIGNAL NAME | PIN TYP. | PIN NO. | PIN DESCRIPTION                                                                                                    |

|-------------|----------|---------|--------------------------------------------------------------------------------------------------------------------|

| BtData[4]   | I/O      | 103     | BootROM Data[4]                                                                                                    |

|             |          |         | A. Normal mode                                                                                                     |

|             |          |         | This pin is used as ROM data pin.                                                                                  |

|             |          |         | B. PHYceiver mode and MAC mode                                                                                     |

|             |          |         | This pin should be pulled to low.                                                                                  |

| BtData[3]/  | I/O/     | 104     | BootROM Data[3]                                                                                                    |

| SELFX       | I        |         | This pin is used as ROM data pin                                                                                   |

|             |          |         | FX/TX Selection                                                                                                    |

|             |          |         | When power-on, this pin is used as input pin to latch the setting value of SELFX.                                  |

|             |          |         | 1: FX mode                                                                                                         |

|             |          |         | 0: TX mode                                                                                                         |

| BtData[2]/  | I/O/     | 105     | BootROM Data[2]/                                                                                                   |

| EEDO/       | 0        |         | EEPROM Data Output (Normal mode and MAC mode)                                                                      |

| PHY_Duplex  |          |         | This is pin is used for BootROM data pin or EEPROM data output dependent on the bit EESEL of register Dc4/DEEAR.   |

|             |          |         | PHY_DUPLEX (PHYceiver mode)                                                                                        |

|             |          |         | This pin output the PHYceiver duplex status.                                                                       |

|             |          |         | 1: Half Duplex                                                                                                     |

|             |          |         | 0: Full Duplex                                                                                                     |

| BtData[1]/  | I/O      | 106     | BootROM Data[1]/                                                                                                   |

| EEDI        |          |         | EEPROM Data Input                                                                                                  |

|             |          |         | This is pin is used for BootROM data signal or EEPROM data input dependent on the bit EESEL of register Dc4/DEEAR. |

| BtData[0]/  | I/O      | 107     | BootROM Data[0]/                                                                                                   |

| EECK        |          |         | EEPROM Data Clock                                                                                                  |

|             |          |         | This is pin is used for BootROM data signal or EEPROM data clock dependent on the bit EESEL of register Dc4/DEEAR. |

| EECS        | 0        | 108     | EEPROM Chip Select                                                                                                 |

| BtCSB       | 0        | 99      | BootROM Chip Select                                                                                                |

BootROM/Flash and EEPROM Interface, continued

| SIGNAL NAME | PIN TYP. | PIN NO. | PIN DESCRIPTION                                                                                                                                                                                          |

|-------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BtOEB/      | I/O      | 98      | BootROM Read Enable/                                                                                                                                                                                     |

| AuxPWR      |          |         | Auxiliary Power Detection                                                                                                                                                                                |

|             |          |         | A. Normal mode and MAC mode                                                                                                                                                                              |

|             |          |         | After power on latch, auxiliary power is automatically detected by W89C841F. If auxiliary power is detected to be high, wake-up event generation from D3(cold) to D0 (uninitialized) state is supported. |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                        |

|             |          |         | This pin should be pulled to low.                                                                                                                                                                        |

| BtWEB/      | I/O      | 97      | BootROM Write Enable/                                                                                                                                                                                    |

| EESel       |          |         | EEPROM Type Select                                                                                                                                                                                       |

|             |          |         | A. Normal mode and MAC mode                                                                                                                                                                              |

|             |          |         | After power on latch, EEPROM type is detected by W89C841F. If it is high, EEPROM (93C56) is used for CardBus application. Otherwise, EEPROM (93C46) is used in PCI/Mini PCI application.                 |

|             |          |         | B. PHYceiver mode                                                                                                                                                                                        |

|             |          |         | This pin should be pulled to low.                                                                                                                                                                        |

### **Transceiver Interface**

| SIGNAL NAME | PIN TYP. | PIN NO. | PIN DESCRIPTION                                          |

|-------------|----------|---------|----------------------------------------------------------|

| TP/FXOP     | 0        | 82      | Twist Pair / Fiber Transmit Output Positive              |

| TP/FXON     | 0        | 83      | Twist Pair / Fiber Transmit Output Negative              |

| TP/FXIP     | I        | 85      | Twist Pair / Fiber Receive input Positive                |

| TP/FXIN     | I        | 86      | Twist Pair / Fiber Receive input Negative                |

| OSC/X1      | I        | 96      | 25 MHz Crystal/OSC clock input                           |

| X2          | 0        | 95      | Crystal Output                                           |

|             |          |         | Left unconnected when oscillator is chosen for X1 input. |

| VREF        | I        | 91      | RC input for Bias.                                       |

| RTX         | I        | 90      | RC input for Transmitter.                                |

| CONTROL     | 0        | 92      | 2.5V Regulator Control Output                            |

|             |          |         | Drive current below 10 mA.                               |

### **LED Interface**

| SIGNAL NAME | PIN TYP. | PIN NO. | PIN DESCRIPTION                                           |

|-------------|----------|---------|-----------------------------------------------------------|

| LED_        | I/O      | 79      | LED_LNKACT                                                |

| LNKACT      |          |         | 0: Link up without activity.                              |

|             |          |         | 1: Link fail or activity is on (flash 100 mS)             |

| LED_SPD     | I/O      | 78      | LED_SPD                                                   |

|             |          |         | 0: 100M.                                                  |

|             |          |         | 1: 10M.                                                   |

| LED_        | I/O      | 77      | LED_DUPCOL                                                |

| DUPCOL      |          |         | 0: Full duplex or collision in half duplex (flash 100 mS) |

|             |          |         | 1: Half duplex and no collision.                          |

# **Configuration and Test Interface**

| SIGNAL NAME | PIN TYP. | PIN NO. | PIN DESCRIPTION                                                                    |  |

|-------------|----------|---------|------------------------------------------------------------------------------------|--|

| CONFIG[1:0] |          | 76, 75  | Configuration                                                                      |  |

|             |          |         | 00: Normal mode                                                                    |  |

|             |          |         | 01: MAC controller mode (Disable internal PHYceiver and disable Boot ROM function) |  |

|             |          |         | 10: PHYceiver mode (Disable MAC Controller and Boot ROM function)                  |  |

|             |          |         | 11: Reserved for testing                                                           |  |

| Scan_EN     |          | 74      | Scan Enable                                                                        |  |

|             |          |         | Reserved for testing. This pin should be pulled to low.                            |  |

### **Power Pins**

| SIGNAL NAME | PIN TYP. | PIN NO.                                           | PIN DESCRIPTION         |

|-------------|----------|---------------------------------------------------|-------------------------|

| VccA2       |          | 87, 93                                            | 2.5V Analog Power       |

| Vcc3A       |          | 88                                                | 3.3V Analog Power       |

| GNDA        |          | 84, 89, 94                                        | Analog Ground           |

| Vcc         |          | 10, 20, 30, 40, 64,<br>109, 128                   | 3.3V I/O Digital Power  |

| Vcc_Core    |          | 50, 70, 80, 119                                   | 2.5V Core Digital Power |

| GND         |          | 1, 11, 21, 31, 41,<br>51, 65, 71, 81,<br>110, 118 | Digital Ground          |

### **Pins Mapping Table**

W89C841F can be configured into 3 different operational types. In the following table, it lists the pin mapping of different configuration mode.

| NORMAL MODE         | MAC CONTROLLER MODE | PHYCEIVER MODE      |

|---------------------|---------------------|---------------------|

| Config = 00         | Config = 01         | Config = 10         |

| ModeSel [2:0] = 000 | ModeSel [2:0] = 011 | ModeSel [2:0] = 000 |

| LED_LNKACT          | LINK (I)            | LED_LNKACT (O)      |

| LED_SPD             | SPEED (I)           | LED_SPD (O)         |

| LED_DUPCOL          | DUPLEX (I)          | LED_DUPCOL (O)      |

| BTADD17             | RXD3 (I)            | RXD3 (O)            |

| BTADD16             | RXD2 (I)            | RXD2 (O)            |

| BTADD15             | RDX1 (I)            | RDX1 (O)            |

| BTADD14             | RDX0 (I)            | RDX0 (O)            |

| BTADD13             | RXDV (I)            | RXDV (O)            |

| BTADD12             | RXCLK (I)           | RXCLK (O)           |

| BTADD11             | RXER (I)            | RXER (O)            |

| BTADD10             | TXER (O)            | TXER (O)            |

| BTADD9              | TXCLK (I)           | TXCLK (O)           |

| BTADD8              | TXEN (O)            | TXEN (I)            |

| BTADD7              | TXD0 (O)            | TXD0 (I)            |

| BTADD6              | TXD1 (O)            | TXD1 (I)            |

| BTADD5              | TXD2 (O)            | TXD2 (I)            |

| BTADD4              | TXD3 (O)            | TXD3 (I)            |

| BTADD3              | COL (I)             | COL (O)             |

| BTADD2              | CRS (I)             | CRS (O)             |

| BTADD1              | MDIO (I/O)          | MDIO (I/O)          |

| BTADD0              | MDC (O)             | MDC (I)             |

| BTDATA7             | ModeSel[2]          | ModeSel[2]          |

| BTDATA6             | ModeSel[1]          | ModeSel[1]          |

| BTDATA5             | ModeSel[0]          | ModeSel[0]          |

| BTDATA4             | NC                  | NC                  |

Pins Mapping Table, continued

| NORMAL MODE         | MAC CONTROLLER MODE | PHYCEIVER MODE      |

|---------------------|---------------------|---------------------|

| Config = 00         | Config = 01         | Config = 10         |

| ModeSel [2:0] = 000 | ModeSel [2:0] = 011 | ModeSel [2:0] = 000 |

| BTDATA3             | NC                  | SELFX               |

| BTDATA2/            | EEDO                | PHY_DPULEX          |

| EEDO                |                     |                     |

| BTDATA1/            | EEDI                | NC                  |

| EEDI                |                     |                     |

| BTDATA0/            | EECLK               | NC                  |

| EECLK               |                     |                     |

| BTCSB               | NC                  | NC                  |

| ВТОЕВ               | NC                  | NC                  |

| BTWEB               | NC                  | NC                  |

| AD11                | AD11                | PWRDN (I)           |

| AD10                | AD10                | INT (O)             |

| AD9                 | AD9                 | PHYA[4] (I)         |

| AD8                 | AD8                 | PHYA[3] (I)         |

| AD7                 | AD7                 | PHYA[2] (I)         |

| AD6                 | AD6                 | PHYA[1] (I)         |

| AD5                 | AD5                 | PHYA[0] (I)         |

| AD4                 | AD4                 | PAUREC (I)          |

| AD3                 | AD3                 | XOVEN (I)           |

| AD2                 | AD2                 | RECAN (I)           |

| AD1                 | AD1                 | REC100 (I)          |

| AD0                 | AD0                 | RECFUL (I)          |

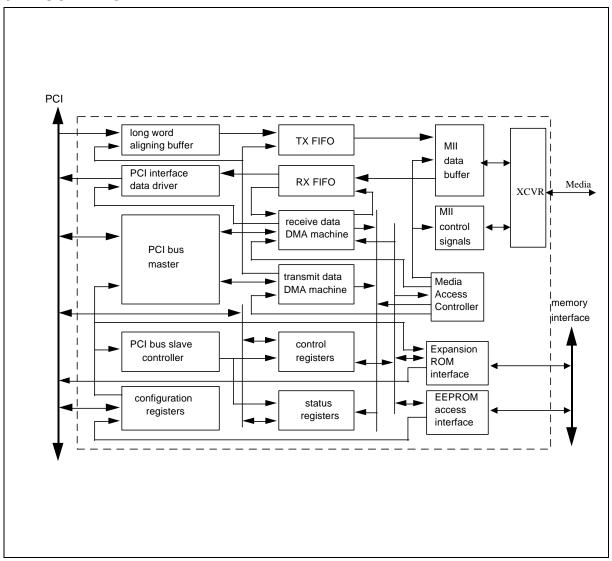

#### 5. BLOCK DIAGRAM

Figure 2. W89C841F Block Diagram

#### **6. SYSTEM DIAGRAM**

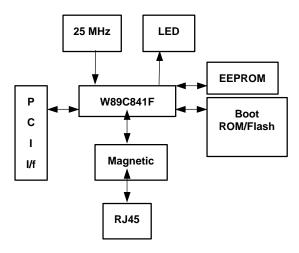

• NIC product: PCI LAN card, Card bus LAN card, MiniPCI LAN card

Figure 3. NIC Application

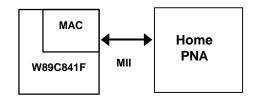

• Home Networking product: HomePNA

Figure 4. HomePNA Application

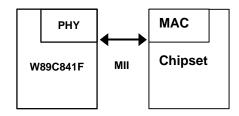

• LAN On Mother board: LOM

Figure 5. LOM Application

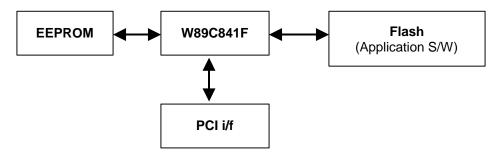

• PCI application: Restore card, Firewall, Education system

Figure 6. Restore Card Application

#### 7. FUNCTIONAL DESCRIPTION

#### **Operation Mode Configuration**

W89C841F can be configured to 3 different operation modes for different applications. In the following table, the assignment of pins CONFIG[1:0] and ModeSel[2:0] is listed.

| PIN ASSIGNMENT | NORMAL | MAC CONTROLLER | PHYCEIVER |

|----------------|--------|----------------|-----------|

| CONFIG[1:0]    | 00     | 01             | 10        |

| Mode_Sel[2:0]  | 000    | 011            | 000       |

In the normal mode, W89C841F is used in the NIC application. In the MAC controller mode, W89C841F that is used as a MAC controller plus HomePHY that is used as a transceiver implement a HomePNA card. In the PHYceiver mode, an application like LAN On Motherboard (LOM) is implemented by W89C841F that is used as a single PHYceiver plus PC chipset.

#### **PHYceiver**

An internal PHYceiver is embedded in W89C841F. It is compatible with IEEE802.3 10-BAST-T, 100BASE-TX and 100BAST-FX. W89C841F can be configured to twist pair interface or fiber interface. Auto-negotiation and auto-crossover function is supported. W89C841F provides 3 LEDs to indicate Link/Activity, Speed and Duplex/Collision status.

#### **Direct Memory Access Function**

On receiving a data packet, the receive DMA function will transfer these data from the internal receive FIFO which has a size of 2k bytes to the host memory with the assistance of the on-chip PCI bus master. During the transaction cycle, the media access controller (MAC) requests the receive DMA state machine to move the data in the receive FIFO onto the PCI bus, and then move it to the host memory.

W89C840F transmit DMA function performs the data transfer from the host memory through on-chip PCI bus master into the internal 2 Kbytes transmit FIFO. The transmit DMA state machine will request the MAC to send out the data in the TX FIFO onto the transmission media.

#### Media Access Control (MAC) Function

The MAC function of W89C841F fully meets the requirements defined by the IEEE802.3u specification. MAC performs many transmission functions, including the inter-frame spacing function, collision detection, collision enforcement, collision backoff and retransmission. MAC performs the receive functions including the address recognition function, the frame check sequence validation, the frame disassembly, framing and collision filtering.

#### **Full Duplex and Half Duplex Function**

In the half duplex mode, the MAC should perform the transmission or reception operation at the different time frame. Simultaneous transmission and reception is not allowed. However, in the time duration from 10 bits time to 16 bits time after the packet is transmitted, the active COL signal is recognized as a SQE test signal but not a collision event. The active signal CRS will be recognized as a loopback carrier sense signal when the MAC is transmitting a packet. The carrier sense lost status is relied on the CRS. Normally, there should not be any carrier sense lost during transmitting if the media and devices are functional. In the full duplex mode, the MAC can perform the transmission and receive operation at the same time. Collision event, SQE lost and carrier sense lost are not defined in the full duplex mode. After auto-negotiation completed, network duplex mode can be decided by internal PHYceiver.

#### **Network Media Speed Function**

W89C841F can work at network speed of 100M or 10Mbps. After auto-negotiation completed, network speed can be decided by internal PHYceiver.

#### Flow Control in Full Duplex Mode

W89C841F supports asymmetrical and symmetrical flow control in full duplex mode compliant with IEEE802.3x. After auto-negotiation completed, W89C841F will decide to operate in which flow control mode (symmetrical, asymmetrical or none).

When the receiving byte counts of RX FIFO is over the high threshold defined at field HTV of register Ddc/DRFCTV[17:9], a pause frame with MAX pause time (FFFFh) is transmitted to prevent the other station keeping on transmitting packets to W89C841F. So W89C841F will not drop packets due to RX FIFO overflow. When the receiving byte count of RX FIFO is below the low threshold defined at field LTV of register Ddc/DRFCTV[8:0], a pause frame with MIN pause time (0000h) is transmitted to let the other station starting to transmit packets to W89C841F.

If W89C841F receives a pause packet with non-zero pause time, the packet transmission ability will be inhibited until the pause time counts down to 0. Pause frame is a flow control packet. It is not a data packet and will be dropped by W89C841F.

#### **Priority Tagged Frame Supporting QOS**

A priority tagged frame defined at IEEE 802.1p contains a VLAN tag which indicates the user priority and Null VLAN ID (VID = 0). W89C841F can transmit and receive priority tagged frames to improve the network quality of service if bit VLANEN of register C1c/CNCR is set.

#### **EEPROM Auto-load and Software Programming Function**

W89C841F reads configuration parameter from EEPROM and stores these data into the configuration registers and function registers after hardware reset. EEPROM 93C46 or 93C56 will be the choice as the storage device for storing these data according to different application.

In PCI/Mini-PCI application, W89C841F stores configuration parameters and Vital Product Data (VPD) in EEPROM 93C46. Configuration parameters and relative register are listed below:

- 1) 6 bytes Ethernet address (Register Dcc[31:0] and Dd0[15:0])

- 2) 1 byte maximum latency (Register F3c[31:24])

- 3) 1 byte minimum grant (Register F3c[23:16])

- 4) 2 bytes subsystem ID (Register F2c[31:16])

- 2 bytes subsystem Vendor ID (Register F2c[15:0])

- 6) 2 bytes Device ID (Register F00[31:16])

- 7) 2 bytes Vendor ID (Register F00[15:0])

- 4 bytes CardBus CIS Pointer (Register F28[31:0])

- 9) 1 bit Power Management Data Enable

- 10) 3 bits Auxiliary Current (Register Fdc[24:22])

- 11) 2 bits Data Scale (Register Fe0[14:13])

- 12) 6 bytes Power Consumption and Dissipation data for D0, D1 and D3 State (Register Fe0[31:24])

- 13) 1 bits Power Management Enable (Register D00[6])

- 14) 1 bit VPD Enable (Register D00[5])

- 15) 2 bits Bus Type (Register D00[1:0])

- 16) 1 bit CLKRUN enable (Register D00[11])

- 17) 1 bit Magic Packet enable (Register D00[10])

- 18) 3 bits Boot ROM Size (Register Dc0[30:28])

- 19) 1 byte Base Class Code (Register F08[31:24])

- 20) 1 byte Subclass code (Register F08[23:16])

- 21) 1 byte Interface Code (Register F08[15:8]

- 22) 1 bytes Revision ID (Register F08[7:0]

- 23) 64 Bytes VPD Data

#### **EEPROM 93C46**

| ADDRESS   | HIGH BYTE (Bit 15 - Bit 8)      | LOW BYTE (Bit 7 - Bit 0)       |

|-----------|---------------------------------|--------------------------------|

| 00h       | Ethernet Address 1 [15:8]       | Ethernet Address 0 [7:0]       |

| 01h       | Ethernet Address 3 [31:24]      | Ethernet Address 2 [23:16]     |

| 02h       | Ethernet Address 5 [47:40]      | Ethernet Address 4 [39:32]     |

| 03h       | MAXLAT                          | MINGNT                         |

| 04h       | Subsystem ID (high byte)        | Subsystem ID (Low byte)        |

| 05h       | Subsystem Vendor ID (high byte) | Subsystem Vendor ID (low byte) |

| 06h       | Device ID (high byte)           | Device ID (low byte)           |

| 07h       | Vendor ID (high byte)           | Vendor ID (low byte)           |