#### **WAS7223Q**

#### USB High speed (480Mbps), DPDT Analog Switch

#### **Descriptions**

The WAS7223Q is a high performance, double pole double throw (DPDT) CMOS analog switch that operates from a single +2.3V to +4.5V power supply.

The WAS7223Q is designed for switching of high-speed USB2.0 signals in handset and consumer applications, such as cell phones, digital cameras, and notebooks with hubs or controllers with limited USB I/Os.

The WAS7223Q has low bit-to-bit skew and high channel-to-channel noise isolation, and is compatible with various standards, such as high-speed USB 2.0 (480Mbps). Each switch is bi-directional and offers little attenuation of the high-speed signals at the outputs. Its bandwidth is quite marginal to pass high-speed USB 2.0 differential signals (480Mbps) with good signal integrity.

The WAS7223Q is featured with special circuitry on the D+/D-, which allows the device to withstand a VBUS short to D+ or D- when the USB devices are either powered off or on.

The SEL/OE pin has overvoltage protection that allows voltages above VCC, up to 7.0V to be present on the pin without damage or disruption of operation of the part, regardless of the operating voltage. The WAS7223Q is also featured with smart circuitry to minimize VCC leakage current even when SEL/OE control voltage is lower than VCC supply voltage. In other word, there is no need of additional device to shift SEL/OE level to be the same as that of VCC in real application.

The WAS7223Q is available in QFN2116-10L package. Standard products are Pb-Free and Halogen-Free.

## **Applications**

- Cell phones

- MID

- Router

- Other electronics equipments

Http//:www.willsemi.com

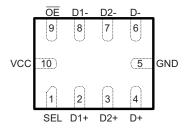

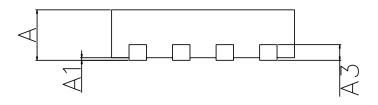

Pin configuration (Top view)

Marking

7223 = Device code

YY = Year WW = Week

#### **Order information**

| Device         | Package     | Shipping       |  |

|----------------|-------------|----------------|--|

| WAS7223Q-10/TR | QFN2116-10L | 3000/Reel&Tape |  |

#### **Features**

Supply voltage : 2.3 ~ 4.5V

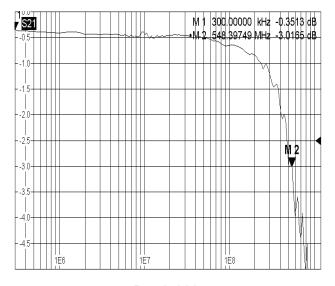

-3dB Bandwidth : 550MHz @ C<sub>L</sub>=5pF

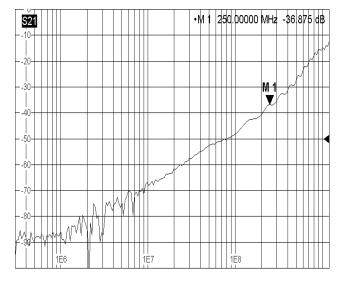

Off isolation : -36dB @ 250MHz

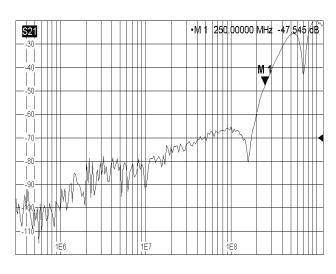

Crosstalk : -47dB @ 250MHz

Low quiescent current : <1uA</li>

### Pin descriptions

| Pin Number | Symbol | Descriptions                                                              |

|------------|--------|---------------------------------------------------------------------------|

| 1          | SEL    | Switch select pin, digital logic low or high.                             |

| 2          | D1+    | Port A data 1 terminal, normally closed                                   |

| 3          | D2+    | Port A data 2 terminal, normally open                                     |

| 4          | D+     | Port A common data terminal, Connect to D1+ or D2+ according to SEL logic |

| 5          | GND    | Ground                                                                    |

| 6          | D-     | Port B common data terminal, Connect to D1- or D2- according to SEL logic |

| 7          | D2-    | Port B data 2 terminal, normally open                                     |

| 8          | D1-    | Port B data 1 terminal, normally closed                                   |

| 9          | ŌĒ     | Enable control, Active low                                                |

| 10         | VCC    | Power supply                                                              |

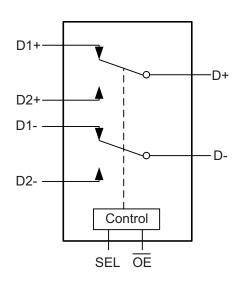

# **Function descriptions**

| SEL | ŌĒ | Function                                |

|-----|----|-----------------------------------------|

| X   | Н  | Bus switch disconnected                 |

| L   | L  | D+ connect to D1+ and D- connect to D1- |

| Н   | L  | D+ connect to D2+ and D- connect to D2- |

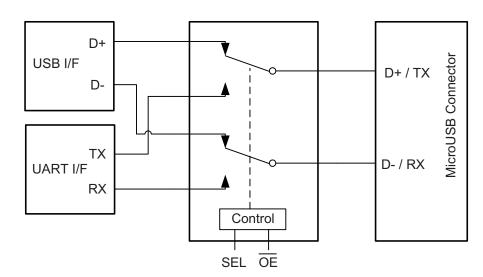

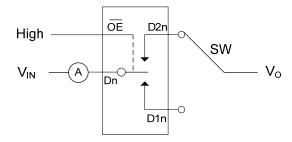

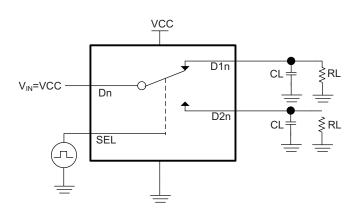

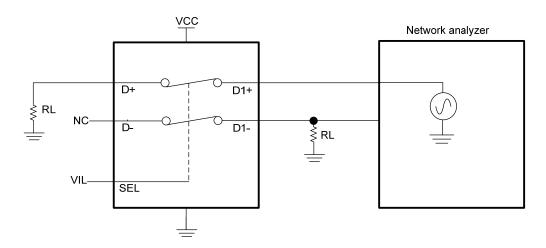

## Logic symbol and typical applications

**Logic Symbol**

**Typical Applications**

**Absolute maximum ratings**

| Parameter                       | Symbol                 | Value      | Unit |

|---------------------------------|------------------------|------------|------|

| Supply voltage range            | VCC                    | -0.5 ~ 6.5 | V    |

| Data input/output voltage range | $V_{DATA}$             | -0.5 ~ 6.5 | V    |

| Select input voltage range      | $V_{SEL}$              | -0.5 ~ 6.5 | V    |

| Continues output current        | I <sub>оит</sub>       | ±50        | mA   |

| Junction temperature range      | TJ                     | 150        | °C   |

| Lead temperature range          | T <sub>L</sub>         | 260        | °C   |

| Storage temperature range       | T <sub>STG</sub>       | -65 ~ 150  | °C   |

| Thermal resistance              | $R_{	heta JA}$         | 250        | °C/W |

| ESD protection (HPM)            | I/O to VCC, I/O to GND | ±7000      | V    |

| ESD protection (HBM)            | I/O to I/O             | ±5000      | V    |

**Recommend operating ratings**

| Parameter                          | Symbol          | Value     | Unit |

|------------------------------------|-----------------|-----------|------|

| Supply voltage range               | VCC             | 2.3 ~ 4.5 | V    |

| Data input/output voltage range    | $V_{DATA}$      | 0.0 ~ VCC | V    |

| Select input voltage range         | $V_{SEL}$       | 0.0 ~ VCC | V    |

| Enable control input voltage range | V <sub>OE</sub> | 0.0 ~ VCC | V    |

| Operating temperature range        | $T_A$           | -40 ~ 85  | °C   |

Will Semiconductor Ltd. 3 Jan, 2012 - Rev. 1.1

### Electronics Characteristics (Ta=25°C, VCC=4.5V, unless otherwise noted)

| Parameter                        | Symbol                              | Conditions                                | Min. | Тур. | Max. | Unit |  |

|----------------------------------|-------------------------------------|-------------------------------------------|------|------|------|------|--|

| Soloet and OE logic high lovel   | V                                   | VCC=3.0∼4.5                               | 1.7  |      |      | V    |  |

| Select and OE logic high level   | V <sub>IH</sub>                     | VCC=2.3~3.0                               | 1.4  |      |      | V    |  |

| Salast and OF lagis law level    | \/                                  | VCC=3.0~4.5                               |      |      | 0.6  | V    |  |

| Select and OE logic low level    | V <sub>IL</sub>                     | VCC=2.3~3.0                               |      |      | 0.4  | V    |  |

|                                  |                                     | I <sub>OUT</sub> =0,                      |      |      |      |      |  |

| Supply guide cent current        |                                     | V <sub>SEL</sub> >1.5V or                 |      |      | 4.0  |      |  |

| Supply quiescent current         | I <sub>CC</sub>                     | V <sub>SEL</sub> <0.7V                    |      |      | 1.0  | uA   |  |

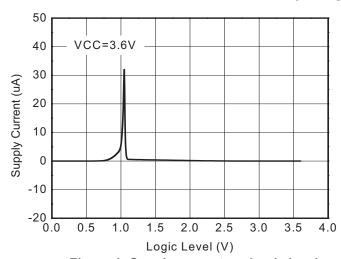

|                                  |                                     | Refer to figure1                          |      |      |      |      |  |

| Select input leakage current     | I <sub>SEL</sub>                    | V <sub>SEL</sub> =VCC                     |      |      | ±1.0 | uA   |  |

| Off state switch leakage current | I <sub>OFF</sub>                    | See figure 2                              |      |      | ±1.0 | uA   |  |

| On state switch leakage current  | I <sub>ON</sub>                     | See figure 3                              |      |      | ±1.0 | uA   |  |

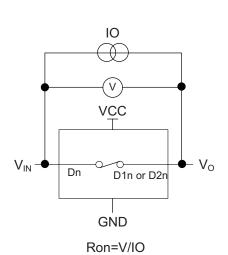

|                                  |                                     | VCC=3.0V,                                 |      |      | 7.5  |      |  |

| On-Resistance                    | D                                   | V <sub>DATA</sub> =0~0.4V,                |      | 5.0  |      | Ω    |  |

| On-Resistance                    | R <sub>ON</sub>                     | I <sub>OUT</sub> =8mA,                    |      | 5.0  |      |      |  |

|                                  |                                     | See figure 4                              |      |      |      |      |  |

|                                  |                                     | VCC=3.0V,                                 |      |      | 0.00 |      |  |

| On Desistance metab              | , D                                 | V <sub>DATA</sub> =0~0.4V,                | 0.15 | 0.45 |      |      |  |

| On-Resistance match              | ΔR <sub>ON</sub>                    | I <sub>OUT</sub> =8mA,                    |      | 0.15 | 0.20 | Ω    |  |

|                                  |                                     | See figure 4                              |      |      |      |      |  |

|                                  |                                     | VCC=3.0V,                                 |      | 1.8  | 2.2  | Ω    |  |

| On Desigtance flatness           | R <sub>FLAT(ON)</sub>               | V <sub>DATA</sub> =0~1.0V,                |      |      |      |      |  |

| On-Resistance flatness           |                                     | I <sub>OUT</sub> =8mA,                    |      |      |      |      |  |

|                                  |                                     | See figure 4                              |      |      |      |      |  |

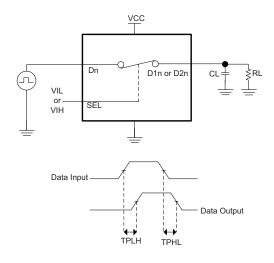

| Drangation delay time            | т /т                                | C <sub>L</sub> =10pF, R <sub>L</sub> =50Ω | 0.3  | 0.3  | 1.2  | no   |  |

| Propagation delay time           | T <sub>PLH</sub> / T <sub>PHL</sub> | See figure 5                              |      | 0.3  |      | ns   |  |

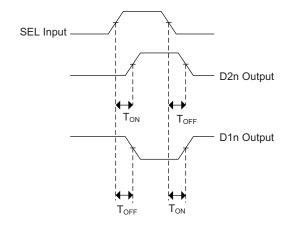

| Calcat input to awitch on time   | т                                   | $C_L$ =10pF, $R_L$ =50 $\Omega$           | 75   |      | 120  | nc   |  |

| Select input to switch on time   | T <sub>ON</sub>                     | See figure 6                              |      | /5   | 120  | ns   |  |

| Select input to switch off time  | T <sub>OFF</sub>                    | $C_L$ =10pF, $R_L$ =50 $\Omega$           |      | 40   | 80   | no   |  |

| Select input to switch on time   |                                     | See figure 6                              |      | 40   |      | ns   |  |

| Break-Before-Make time           | T <sub>BBM</sub>                    | Generated by design                       | 0.5  |      |      | ns   |  |

| -3dB Bandwidth                   | D\A/                                | $R_L=50\Omega$ , $C_L=5pF$                |      | 550  |      | MUZ  |  |

| -3dB Bandwidth                   | BW                                  | $R_L=50\Omega$ , $C_L=0pF$                |      | 800  |      | MHz  |  |

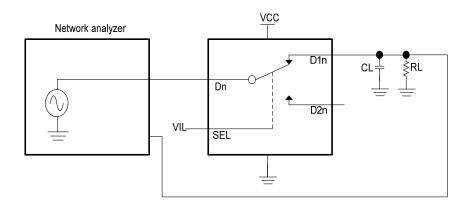

| Off isolation                    | OIRR                                | $R_L$ =50 $\Omega$ , F=250MHz             |      | -36  |      | dB   |  |

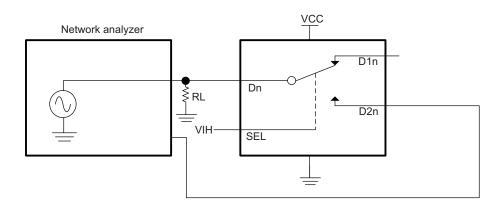

| Crosstalk                        | Xtalk                               | $R_L$ =50 $\Omega$ , F=250MHz             |      | -47  |      | dB   |  |

| Charge injection                 | 0~                                  | C <sub>L</sub> =0.1nF, VCC=3.3V           |      | F    |      | -0   |  |

| (Select input to common I/O)     | Qg                                  | $R_G=0\Omega$ , $V_G=GND$                 |      | 5    |      | pC   |  |

| Select pin input capacitance     | C <sub>IN</sub>                     | VCC=0V                                    |      | 5    |      | pF   |  |

| D1n, D2n,Dn Off capacitance      | C <sub>OFF</sub>                    | VCC=3.3V, <del>OE</del> =3.3V             |      | 5    |      | pF   |  |

| D1n, D2n,Dn On capacitance       | C <sub>ON</sub>                     | VCC=3.3V, OE=0V                           |      | 6.5  |      | pF   |  |

### Typical Characteristics (Ta=25°C, VCC=4.5V, unless otherwise noted)

**Bandwidth**

Crosstalk

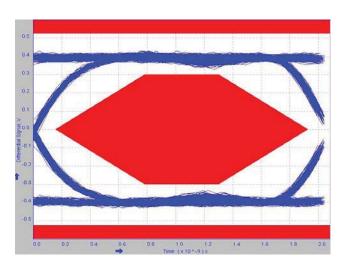

#### Eye Diagram (480Mbps)

Figure 1: Supply current vs. Logic level

#### **Test Circuit**

Conditions: V<sub>IN</sub>=4.5V, VO=GND

Low SEL D2n Vo

Conditions:  $V_{IN}$ =4.5V,  $V_{O}$ =Open

Figure 3: On state switch leakage current

Figure 2: Off state switch leakage current

Figure 4: On-Resistance

Figure 5: Propagation delay time

Figure 6: Select input to switch on/off time

Will Semiconductor Ltd. 6 Jan, 2012 - Rev. 1.1

### Bandwidth (BW)

## Off isolation (OIRR)

Crosstalk (Xtalk)

Will Semiconductor Ltd. 7 Jan, 2012 - Rev. 1.1

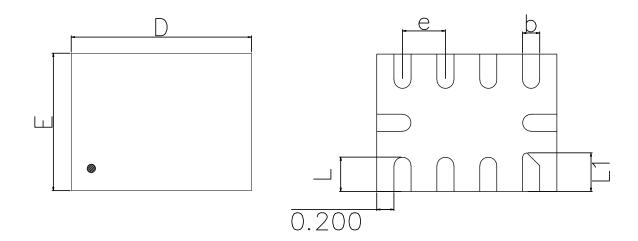

## Package outline dimensions

## QFN2116-10L

| Symbol | Dimension in Millimeters |       |       |  |

|--------|--------------------------|-------|-------|--|

|        | Min.                     | Тур.  | Max.  |  |

| A      | 0.500                    | 0.550 | 0.600 |  |

| A1     | 0.000                    |       | 0.050 |  |

| A3     | 0.150 Ref.               |       |       |  |

| D      | 2.050                    | 2.100 | 2.150 |  |

| Е      | 1.550                    | 1.600 | 1.650 |  |

| b      | 0.150                    | 0.200 | 0.250 |  |

| е      | 0.500 (BSC)              |       |       |  |

| L      | 0.350                    | 0.400 | 0.450 |  |

| L1     | 0.450                    | 0.450 | 0.550 |  |