MARCH, 1981

# WESTERN DIGITAL

WD1993 ARINC 429 RECEIVER/TRANSMITTER MULTI-CHARACTER RECEIVER/TRANSMITTER

### FEATURES

- PRESENT UPON MASTER RESET FOR ARINC 429

PROTOCOL

- PROGRAMMABLE WORD LENGTH FROM 1 CHARAC-TER TO 8 CHARACTERS

- PROGRAMMABLE CHARACTER LENGTH, 5, 6, 7, OR 8 BITS

- RETURN TO ZERO (RZ) OUTPUT

- AUTO SPACE GENERATION

- DOUBLE BUFFERED RECEIVER AND TRANSMITTER

- UNDERRUN ERROR DETECTION FOR TRANSMISSION

- OVERRUN, FRAMING AND PARITY ERROR DETEC-TION ON RECEIVER

- WORD ERROR FLAG FOR COMPREHENSIVE ERROR REPORTING

- FIRST CHARACTER OF WORD FLAG FOR SINGLE IN-TERRUPT APPLICATIONS

- DIAGNOSTIC LOCAL LOOP-BACK TEST MODE

- DC TO 200 KILOBITS PER SECOND OPERATION

- TTL COMPATIBLE INPUTS AND OUTPUTS

- SINGLE +5 VOLT SUPPLY

- 28 PIN CERAMIC OR PLASTIC PACKAGE

- TEMPERATURE RANGES 0°C to 70°C, -40°C to +85°C, or -55°C to +125°C

### INTRODUCTION

The Western Digital WD1993 Avionic Receiver/Transmitter is designed to handle digital data transmission, according to the Avionic Arinc 429 protocol. Also, the word length is programmable from one to eight characters of 5, 6, 7, or 8 bits. Parallel data is converted into a serial data stream during transmission and serial to parallel during reception. The WD1993 is packaged in a 28 pin plastic or ceramic package and is available in three temperature ranges: Commercial, Industrial and Military.

### GENERAL DESCRIPTION

The WD1993 is a bus-orientated MOS/LSI device designed to provide the Avionics Arinc 429 Data Communication Protocol, along with programmable character length capabilities.

Also, the WD1993 contains a local loop-back test mode of operation, which is controlled by the Loop Test Enable (LTE) bit in the command register. In this diagnostic mode, the transmitter output is "looped-back" into the receiver input. The <u>REN</u> and TEN control bits must also be active ("1") and the CTS input must be low. The status and output flags operate normally.

| PIN NO. | SYMBOL | SIGNAL NAME           | FUNCTION                                                                                                                                                                                                                                                                                                                         |

|---------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |        |                       |                                                                                                                                                                                                                                                                                                                                  |

| 1       | VSS    | GROUND                | Ground                                                                                                                                                                                                                                                                                                                           |

| 15      | VCC    | POWER SUPPLY          | +5V DC                                                                                                                                                                                                                                                                                                                           |

| 26      | ĊŚ     | CHIP SELECT           | When active (V $_{\rm IL}$ ), the device is selected. This enables communication between the WD1993 and a micro-                                                                                                                                                                                                                 |

| 27      | C/D    | CONTROL/DATA          | processor.<br>This input is used in conjunction with an active read or<br>write operation to determine register access via the DATA<br>BUS.                                                                                                                                                                                      |

| 28      | RE     | READ ENABLE           | When active (V <sub>IL</sub> ), allows the CPU to read data or status information from the WD1993.                                                                                                                                                                                                                               |

| 25      | WE     | WRITE ENABLE          | When active (V $_{\mbox{IL}}),$ allows the CPU to write into the selected register.                                                                                                                                                                                                                                              |

| 6       | MR     | MASTER RESET          | When active (V <sub>IH</sub> ), presets the WD1993 mode and com-<br>mand registers to the ARINC protocol. Master Reset also<br>resets the data registers and places the WD1993 transmit-<br>ter and receiver into idle states. After MR, the command<br>register is set to 00100101 and the mode register is set to<br>00111100. |

| 4       | TXC    | TRANSMIT CLOCK        | This input is the source clock for transmission. The data rate is a function of this clock frequency.<br>ARINC MODE = $4 \times bit$ rate                                                                                                                                                                                        |

| 12      | RXC    | RECEIVE CLOCK         | This input is the source clock for reception. The data rate characteristics are the same as the transmit clock.                                                                                                                                                                                                                  |

| 3       | CTS    | CLEAR-TO-SEND         | This input is activated (V $_{\rm IL}$ ) to enable the transmitter logic.                                                                                                                                                                                                                                                        |

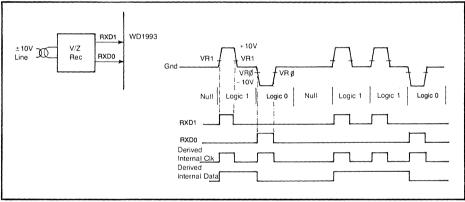

| 16      | RXD1   | RECEIVE DATA ONE      | The RXD1 input is driven by the V/Z line receiver. Each<br>time the V/Z circuit detects a logic one, a TTL level logic<br>one (active for one-half bit time) is provided to this input.                                                                                                                                          |

| 14      | RXD0   | RECEIVE DATA ZERO     | RXD0 is driven by the line V/Z receiver circuit. When the V/Z circuit detects a logic zero, a TTL logic one (active for one-half bit time) is provided to the WD1993.                                                                                                                                                            |

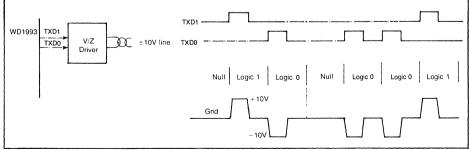

| 11      | TXD1   | TRANSMIT DATA<br>ONE  | This output drives the V/Z circuit when a logic one is to be transmitted and is active for one-half bit time.                                                                                                                                                                                                                    |

| 10      | TXD0   | TRANSMIT DATA<br>ZERO | This output drives the V/Z circuit when a logic zero is to be transmitted and is active for one-half bit time.                                                                                                                                                                                                                   |

| PIN NO.                                      | SYMBOL                                       | SIGNAL NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                            | TXE                                          | TRANSMITTER<br>EMPTY     | This output goes high to indicate the end of a transmit op-<br>eration. TXE is automatically reset after the Transmit Hold-<br>ing Register is loaded.                                                                                                                                                                                                                                              |

| 8                                            | RXRDY                                        | RECEIVER READY           | This output, when high, alerts the CPU that the Receiver<br>Holding Register contains a data character that is ready<br>to be input. This output is automatically reset whenever a<br>character is read from the WD1993. RXRDY is enabled<br>unless inhibited by setting command bit CR3 (RXRDYIN)<br>to a logic "1". It is automatically enabled again after a re-<br>ceive sequence is completed. |

| 9                                            | TXRDY                                        | TRANSMITTER<br>READY     | This output, when high, alerts the CPU that the Transmit<br>Holding Register is ready to accept a data character. The<br>TXRDY output is automatically reset whenever a character<br>is written into the WD1993 and can be used as an interrupt<br>to the system.                                                                                                                                   |

| 13                                           | FCR                                          | FIRST CHARACTER<br>READY | This output goes high after the receiver has completed re-<br>ception of the first character in a multi-character sequence.                                                                                                                                                                                                                                                                         |

| 2                                            | WEF                                          | WORD ERROR<br>FLAG       | This pin is an output, which when active indicates an error<br>in either the transmitter or receiver has been detected. It re-<br>flects an underun, overrun, parity or framing (receive word)<br>error and is intended as an error interrupt. The Status Reg-<br>ister should be read to determine the specific error.                                                                             |

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7 | DATA BUS                 | This is the bi-directional data bus. It is the means of com-<br>munication between the WD1993 and the CPU. Control,<br>Mode, Data and Status Registers are accessed via this bus.                                                                                                                                                                                                                   |

| 5                                            | N.C.                                         |                          | No Internal Connection                                                                                                                                                                                                                                                                                                                                                                              |

SUCHOR 1

### ORGANIZATION

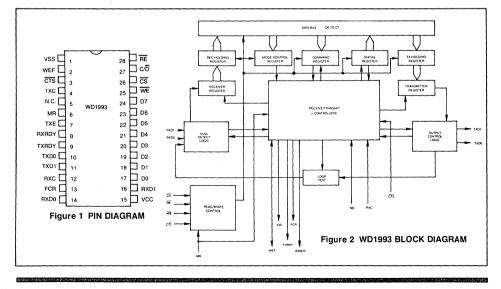

A block diagram of the WD1993 is shown in figure 2.

As mentioned, the WD1993 is an eight bit bus-oriented device. Communication between the WD1993 and the controlling CPU occurs via the 8 bit data bus through the bus transceivers. There are 2 accessible data registers, which buffer transmit and receive data. They are the Transmit Holding Register and the Receive Holding Register. There is a parallel-to-serial shift register (parallel in-serial out), the transmit register and a serial-to-parallel shift register (serial in-parallel out), the receive redister.

Operational control and monitoring of the WD1993 is performed by two control registers (the command instruction register and the mode instruction register) and the status register.

A read/write control circuit allows programming/monitoring or loading/reading of data in the control, status or holding registers by activating the appropriate control lines: Chip Select ( $\overline{CS}$ ), Read Enable ( $\overline{RE}$ ), Write Enable ( $\overline{WE}$ ), and Control or Data Select ( $C/\overline{D}$ ).

Internal control of the WD1993 is by means of two internal microcontrollers; one for transmit and one for receive. The control registers, null detect logic and various counters, provide inputs to the microcontrollers which generate the necessary control signals to send and receive serial data according to the Arinc 429-1 protocol, along with the programmable multicharacter capabilities.

### OPERATION

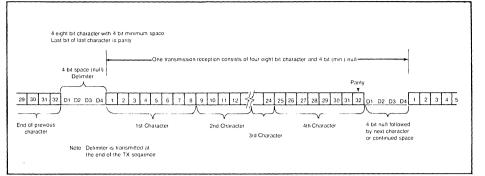

Upon master reset (MR), the device is programmed to transmit and receive four 8-bit contiguous characters with the 32nd bit odd parity. (ARINC protocol.)

A minimum four bit time space is automatically inserted after the character transmission. Two receiver inputs, RXD1/RXD0 and two transmitter outputs, TXD1/TXD0, are provided to interface with voltage—impedance (V/Z) circuits to translate  $\pm$  10 volt ARINC line levels to 5 volt TTL logic levels. The transmit clock (TXC) and receive clock (RXC), in ARINC mode, are four times (4X) the bit rate desired.

The receiver monitors the received data input to detect a four bit time null, which delimits the word. If the communications link is broken during a word reception, the receiver will generate a word error flag to (WEF) to notify the CPU to request retransmission. When a null is detected, the receiver logic is reset and returned to an idle state awaiting the next word. The WD1993 may also be programmed to support a multiple character word consisting of from one to eight characters. Also, the character length is programmable from 5 to 8 bits, and the parity bit if parity is used, may be either inside or outside the word.

The Command Register is used to select features such as parity options, loop test capability, RXRDY flag enabling, transmitter and receiver enabling, and may also cause the WD1993 to return to the Mode instruction.

The Mode Register is used to select features such as bits/ character and characters/word.

The Status Register contains information such as Transmitter Ready, Transmitter Empty, Receiver Ready, error conditions, and First Character Ready.

### OPERATING DESCRIPTION

The WD1993 is primarily designed to operate in an 8 bit micro-processor environment, although other control logic schemes are easily implemented. The DATA BUS and the Interface Control Signals ( $\overline{CS}$ ,  $\overline{RE}$ ,  $\overline{WE}$  and  $C/\overline{D}$ ) should be connected to the microprocessor's data bus and system control bus.

The appropriate TXC and RXC clock frequencies should be selected for the particular application, using a programmable baud rate generator such as a BR1941. A master reset pulse initializes the WD1993 and presets the control registers to the ARINC protocol.

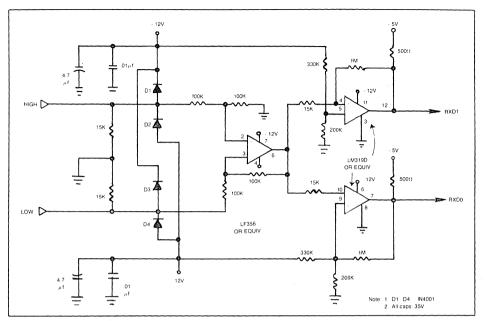

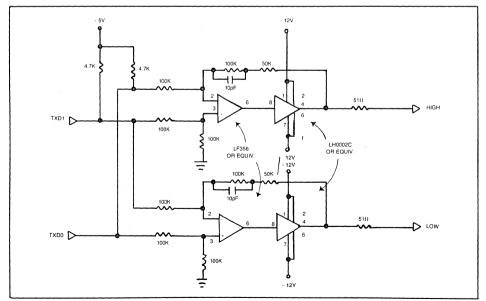

The RXD1/RXD0 inputs are interfaced to the DITS data line via external level translators that provide TTL (5V) logic levels to the WD1993. The TXD1/TXD0 outputs are connected to high voltage ( $\pm$  10V) driver circuits. Figures 16 and 17 show some typical  $\pm$  10V translator and driver circuits.

The TXRDY, RXRDY, FCR and WEF Flags may be connected to the microprocessor system as interrupt inputs. The status register can be periodically read in a polled environment to support WD1993 operations.

The CTS input can be used to synchronize the transmitter to external events.

The WD1993 is designed such that a control register write operation accesses the command instruction register.

The RXRDYIN bit of the command register is used to inhibit the RXRDY output pin for ARINC operations.

### MULTI-CHARACTER OPERATIONS

As discussed above, the WD1993 is equipped with a multicharacter option which provides the user with the means of transmitting and receiving multiple contiguous characters of data within one set of delimiters—4 bit nulls for ARINC 429. Since the WD1993 is an 8 bit bus-oriented device, the controlling processor must read the WD1993 data from its holding register before the subsequent characters are assembled. This situation also exists on the transmit side, i.e., the Transmit Holding Register must be loaded before the previous 8 bits are completely shifted out of the transmit register.

Several "flags" are provided for interrupt purposes so that continuity is maintained and data integrity is preserved. These flags are First Character Ready (FCR), Receiver Ready (RXRDY), Transmitter Ready (TXRDY) and Transmitter Empty (TXE).

The Transmitter operates as follows:

- a) With the mode and command registers programmed as desired, the transmitter is enabled, TEN (CR0) = "1".

- b) The TXE and TXRDY flags are "1" (active).

- c) The external  $\overline{CTS}$  signal = "0".

- d) The CPU loads data into the Transmitter Holding Register, TXE and TXRDY go Low.

- e) The data is loaded into the transmit register and TXRDY goes high. This indicates the first data word is being sent and a character can be loaded into the holding register. If the WD1993 is programmed for more than one character (multi-character) then an underrun error will be generated if the next character is not loaded before the previous word is completely shifted out, unless the current character is the last character in a sequence.

- f) If the last character is transmitted and no more new data is to be sent, the transmitter will indicate its status by raising the TXE flag. (No error is generated as a result of this condition.)

The Receiver operates similarly:

- a) With the control registers suitably programmed, the receiver is enabled, REN (CR2) = "1".

- b) The RXRDY and FCR flags are "0". (Inactive).

- c) The incoming data word activates the receive logic and the data begins to be assembled in the receive register.

- d) When the first character is completely assembled, the data is loaded into the Receive Holding Register, the FCR (First Character Ready) and RXRDY (Receiver Ready) flags become active, "1". The CPU should read the data prior to the reception of the next character or an overrun error will be generated as the receiver will overwrite the old data with the new data character just received.

SHCH-OZ T

The exception to this is in the ARINC mode, where the first character in the ARINC protocol contains a label. The FCR and RXRDY Flags become active to indicate the reception of the first character of data. The CPU reads the first character and decides whether or not it wants to acquire the subsequent characters. If not, then the CPU performs a "control write" to the COM MAND REGISTER, setting the RXRDYIN (CR3) bit to a "1". This bit in ARINC mode, inhibits the RXRDY flag from interrupting the CPU during the reception of the 3 remaining characters. The RXRDYIN bit is then automatically reset upon completion of the receive sequence and RXRDY is enabled again.

### LOOP TEST MODE

As mentioned, the WD1993 is equipped with a diagnostic test mode, local loop-back. This mode is activated by setting the LTE command bit to a "1". The TEN and REN bits should be "1" and  $\overline{\text{CTS}}$  should be "V<sub>IL</sub>". The receiver inputs are ignored and the transmitter outputs are sending nulls. The transmitter is internally "looped-back" to the receiver and the error and status flags operate normally.

For basic testing, failing to reload the Transmit Holding Register in the middle of a data send sequence will cause an underrun error in the transmitter and a word error in the receiver. Failure to read the Receive Holding Register after a FCR or RXRDY flag will cause an overrun error to be generated.

For Loop-Back test operations, the user should be sure that the TXC and RXC clock frequencies are the same. This is normally implemented by placing the same clock signal on both pins (TXC and RXC).

### ARINC BACKGROUND

Aeronautical Radio Inc. (ARINC) publishes the ARINC 429 specification. This document defines the air transport industries standards for the transfer of digital data between avionics systems elements. This specification was adopted by The

Airlines Electronic Engineering Committee April 11, 1978. By the adoption of this specification the foundation is set for a standard protocol governing all intersystems equipment (Line Replaceable Units).

# MARK 33 DIGITAL INFORMATION TRANSFER SYSTEM (DITS)

Basic Philosophy

Transmit from a designated output port over a single twisted and shielded pair of wires to designated receiver.

Bidirectional data flow not permitted on a given pair.

Data Transfer Numeric

> Iso Alphabet #5 Graphic

Data Format

32 bits or less (unused bit positions should be filled with binary zeros or valid data pad bits).

Bit #32 is assigned to parity.

Modulation

| Return t | o Zero (RZ)       |                             |

|----------|-------------------|-----------------------------|

| Transmi  | t Voltage Levels  |                             |

| high     | + 10              | ±0.5V                       |

| null     | 0                 | ±0.5V                       |

| low      | - 10              | ±0.5V                       |

| Receive  | r Voltage Levels: |                             |

|          | (in absence       | (noisy                      |

|          | of noise)         | environment)                |

| high +   | 6.0V to +10V      | +5.0V to +13V               |

| low -    | 6.0V to +10V      | -5.0V to -13V               |

| No dam   | age to receiver u | p to 20 vac rms between A & |

| B; +28,  | A to Gnd; -28,    | B to Gnd.                   |

Data Rate

100 kilo bit per second ± 1%

Low speed 12 to 14.5 kilo bit per second  $\pm$  1%

Word Synchronization

All zero gap of a minimum of 4 bit times

## REGISTER DEFINITIONS

The format and definition of the Command Register is shown below:

| CR7 | CR6       | CR5 | CR4 | CR3            | CR2                         | CR1         | CRO      |

|-----|-----------|-----|-----|----------------|-----------------------------|-------------|----------|

| EPS | IR        | PEN | LTE | RXRDYIN        | REN                         | PIA         | TEN      |

|     |           |     |     |                |                             |             |          |

|     | TEN       |     |     |                | mit ENable                  |             |          |

|     | 1<br>0    |     |     | Enab<br>Disab  |                             |             |          |

|     | PIA       |     |     |                | Inside or A                 |             |          |

|     | 1<br>0    |     |     |                | the data wo<br>(the last da |             | ord      |

|     | REN       |     |     |                | ve ENable                   | _           |          |

|     | 1         |     |     | Enabl<br>Disab |                             |             |          |

| Ī   | RXRDYIN   |     |     |                | DY Inhibit                  |             |          |

|     | 1         |     |     | Inhibi         | t RXRDY ou                  | itput flag  |          |

|     | 0         |     |     |                | al transmitte<br>e RXRDY o  |             |          |

|     | LTE_      |     |     |                | Test ENable                 | -           |          |

|     | 1<br>0    |     |     |                | loop-back n<br>al Operation |             |          |

|     | PEN       |     |     |                | ENable                      |             |          |

|     | 1<br>0    |     |     | Enabl<br>Disab |                             |             |          |

|     | <u>IR</u> |     |     |                | al Reset                    |             |          |

|     | 0         |     |     | forma          | ns WD1993<br>t              | to mode ins | anaction |

|     | EPS       |     |     |                | Parity Selec                | <u>*t</u>   |          |

|     | 1<br>0    |     |     | Even<br>Odd p  |                             |             |          |

|     |           |     |     |                |                             |             |          |

SmCt

Ó N The format and definition of the Mode Register is shown below:

|                       | MR7 | MR6                   | MR5 | MR4              | MR3        | MR2     | MR1                          | MR0      |

|-----------------------|-----|-----------------------|-----|------------------|------------|---------|------------------------------|----------|

|                       | х   | N3                    | N2  | N1               | CLS2       | CLS1    | х                            | x        |

| <u>CLS2</u><br>0<br>0 |     | <u>CLS1</u><br>0<br>1 |     | 5 bits<br>6 bits | Length Sel | ect     |                              |          |

| 1<br>1                |     | 0<br>1                |     | 7 bits<br>8 bits |            |         |                              |          |

| <u>N3</u>             |     | <u>N2</u>             |     | <u>N1</u>        |            | Charact | ers Per Wor                  | d Select |

| 0                     |     | 0                     |     | 0                |            |         | 1 character                  |          |

| 0                     |     | 0                     |     | 1                |            |         | 2 characters                 |          |

| 0                     |     | 1                     |     | 0                |            |         | 3 characters                 |          |

| 0                     |     | 1                     |     | 1                |            |         | 4 characters                 |          |

| 1                     |     | 0                     |     | 0                |            |         | 5 characters                 |          |

| 1                     |     | 0                     |     | 1<br>0           |            |         | 6 characters<br>7 characters |          |

| 1                     |     | 1                     |     | 1                |            |         | 8 characters                 |          |

The WD1993 registers are addressed according to the following table:

| cs  | C/D | RE | WE | Registers Selected              |

|-----|-----|----|----|---------------------------------|

| L   | L   | L  | н  | Read Receive Holding Register   |

| L   | L   | н  | L  | Write Transmit Holding Register |

| L L | н   | L  | н  | Read Status Register            |

| L   | н   | н  | L  | Write Control Registers         |

| н   | Х   | Х  | Х  | Data Bus Tri-Stated             |

$L = V_{IL} \text{ at pins}$   $H = V_{IH} \text{ at pins}$  X = don't care

### The format of the Status Register is shown below:

| SR7 | SR6            | SR5      | SR4 | SR3                                                                                                                                                              | SR2                            | SR1   | SR0                               |  |  |

|-----|----------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|-----------------------------------|--|--|

| UE  | FCR            | WEF      | OE  | PE                                                                                                                                                               | TXE                            | RXRDY | TXRDY                             |  |  |

|     |                |          |     |                                                                                                                                                                  |                                |       | ·                                 |  |  |

|     | TXRD           | <u>(</u> |     | Transmitter I                                                                                                                                                    | Ready                          |       |                                   |  |  |

|     | 1<br>0         |          |     |                                                                                                                                                                  | can be reloa<br>Ismitter is bu |       |                                   |  |  |

|     | RXRD           | <u>r</u> |     | Receiver Re                                                                                                                                                      | ady                            |       |                                   |  |  |

|     | 1<br>0         |          |     | Active (RHR<br>Inactive                                                                                                                                          | should be re                   | ead)  |                                   |  |  |

|     | TXE            |          |     | Transmitter                                                                                                                                                      | Empty                          |       |                                   |  |  |

|     | 1<br>0         |          |     | Transmitter idle<br>Transmitter active                                                                                                                           |                                |       |                                   |  |  |

|     | -              |          |     |                                                                                                                                                                  |                                |       |                                   |  |  |

|     | <u>PE</u><br>1 |          |     | Parity Error<br>Error reported                                                                                                                                   |                                |       |                                   |  |  |

|     | 0              |          |     | No error                                                                                                                                                         |                                |       |                                   |  |  |

|     | <u>OE</u>      |          |     | Overrun Erro                                                                                                                                                     | -                              |       |                                   |  |  |

|     | 1<br>0         |          |     | RHR has be<br>No error                                                                                                                                           | en overwritte                  | n     |                                   |  |  |

|     | WEF            |          |     | Word Error Flag                                                                                                                                                  |                                |       |                                   |  |  |

|     | 1              |          |     | Indicates improper receive sequence (word error)<br>overrun error, parity error or underrun error.                                                               |                                |       |                                   |  |  |

|     | 0              |          |     | No error                                                                                                                                                         |                                |       |                                   |  |  |

|     | FCR            |          |     | First Charac                                                                                                                                                     | ter Ready                      |       |                                   |  |  |

|     | 1              |          | -   | This bit indicates the receiver has just completed a<br>sembly of the 1st character in a multi-character so<br>quence and that the data is contained in the RHR. |                                |       |                                   |  |  |

|     | 0              |          |     | •                                                                                                                                                                | ter not ready                  |       |                                   |  |  |

|     | UE             |          |     | Underrun Er                                                                                                                                                      |                                |       |                                   |  |  |

|     | 1              |          |     |                                                                                                                                                                  |                                |       | aded with a ne<br>ata transmissio |  |  |

|     | Ŭ              |          |     |                                                                                                                                                                  |                                |       |                                   |  |  |

SUCT-OZ 1

## **ABSOLUTE MAXIMUM RATINGS**

Note: Absolute maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under DC Electrical Characteristics.

### DC ELECTRICAL CHARACTERISTICS

$T_A = 0^{\circ}C \text{ to } + 70^{\circ}C; V_{CC} = 5.0V \pm 5\%; GND = 0V$

| SYMBOL          | PARAMETER            | MIN  | TYP | MAX             | UNIT | TEST CONDITIONS             |

|-----------------|----------------------|------|-----|-----------------|------|-----------------------------|

| V <sub>IL</sub> | Input Low Voltage    | -0.3 |     | 0.8             | v    |                             |

| VIH             | Input High Voltage   | 2.0  |     | V <sub>CC</sub> | v    |                             |

| VOL             | Output Low Voltage   |      |     | 0.45            | v    | $I_{OL} = 1.6 \text{mA}$    |

| VOH             | Output High Voltage  | 2.4  |     |                 | v    | $I_{OH} = -100\mu A$        |

| <sup>I</sup> DL | Data Bus Leakage     |      |     | 50              | uA   | Data Bus is in              |

|                 |                      |      |     | 10              | uA   | High Impedence<br>State     |

| ιL              | Input Leakage        |      |     | 10              | uA   | $V_{IN} = V_{CC}$           |

| lcc             | Power Supply Current |      | 45  | 80              | mA   | $V_{CC} = 5.25V$<br>No Load |

### CAPACITANCE

$T_A = 25^{\circ}C; V_{CC} = GND = 0V$

| SYMBOL                              | PARAMETER                            | MIN | TYP | MAX      | UNIT     | TEST CONDITIONS                                             |

|-------------------------------------|--------------------------------------|-----|-----|----------|----------|-------------------------------------------------------------|

| C <sub>IN</sub><br>C <sub>I/O</sub> | Input Capacitance<br>I/O Capacitance |     |     | 10<br>20 | pF<br>pF | f <sub>C</sub> = 1MHz<br>Unmeasured pins<br>returned to GND |

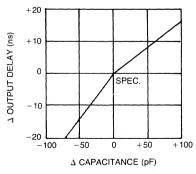

Figure 3 OUTPUT DELAY vs CAPACITANCE

### A.C. TIMING PARAMETERS

| SYMBOL                                                                                       | PARAMETER                                                                                                                                                                                                                                                                                                                                           | MIN                          | МАХ        | UNIT                             | TEST CONDITIONS                                          |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------|----------------------------------|----------------------------------------------------------|

| BUS PA                                                                                       | RAMETERS                                                                                                                                                                                                                                                                                                                                            |                              |            |                                  |                                                          |

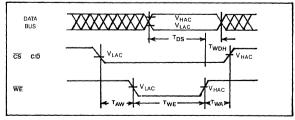

| Read Cy                                                                                      | ycle (Reference Figure 6)                                                                                                                                                                                                                                                                                                                           |                              |            |                                  |                                                          |

| <sup>t</sup> AR<br><sup>t</sup> RA<br><sup>t</sup> RE<br><sup>t</sup> RD<br><sup>t</sup> RDH | Address Stable before $\overline{\text{PE}}$ , ( $\overline{\text{CS}}$ , $\text{C}/\overline{\text{D}}$ )<br>Address Hold Time for $\overline{\text{RE}}$ , ( $\overline{\text{CS}}$ , $\text{C}/\overline{\text{D}}$ )<br>$\overline{\text{RE}}$ Pulse Width<br>Data Delay from $\overline{\text{RE}}$<br>$\overline{\text{RE}}$ to Data Floating | 50<br>5<br>350<br>25         | 200<br>200 | ns<br>ns<br>ns<br>ns<br>ns<br>ns | С L = 50 рF<br>С L = 50 рF<br>С L = 50 рF<br>С L = 15 рF |

| WRITE CYCL                                                                                   | LE (Reference Figure 7)                                                                                                                                                                                                                                                                                                                             |                              |            |                                  |                                                          |

| <sup>t</sup> AW<br><sup>t</sup> WA<br><sup>t</sup> WE<br><sup>t</sup> DS<br><sup>t</sup> WDH | Address Stable before WE<br>Address Hold Time for WE<br>WE Pulse Width<br>Data Set-Up Time for WE<br>Data Hold Time for WE                                                                                                                                                                                                                          | 20<br>20<br>350<br>200<br>40 |            | ns<br>ns<br>ns<br>ns<br>ns       |                                                          |

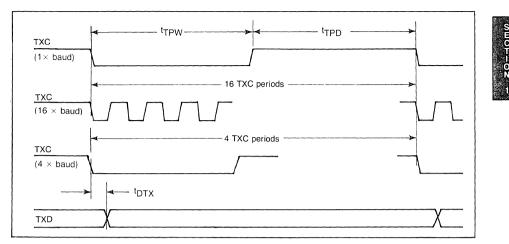

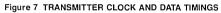

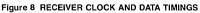

| OTHER TIM        | INGS (Reference Figures 8, 9)         |     |     |                  |                         |

|------------------|---------------------------------------|-----|-----|------------------|-------------------------|

| t <sub>DTX</sub> |                                       |     | 500 |                  | 0 100-5                 |

|                  | TXD Delay from Falling Edge of TXC    |     | 500 | ns               | $C_{L} = 100  pF$       |

|                  | Rx Data Set-up Time to Sampling Pulse | 200 |     | ns               | $C_L = 100  \text{pF}$  |

| t <sub>NRX</sub> | Rx Data Hold Time to Sampling Pulse   | 100 |     | ns               | C <sub>L</sub> = 100 pF |

| t <sub>TX</sub>  | Transmitter Input Clock Frequency     |     |     |                  |                         |

|                  | 1× Baud Rate                          | DC  | 500 | kHz              |                         |

| .                | $4\times$ , 16× Baud Rate             | DC  | 750 | kHz              |                         |

| <sup>t</sup> TPW | Transmitter Input Clock Pulse Width   |     |     |                  |                         |

|                  | 1× Baud Rate                          | 1.0 |     | us               |                         |

|                  | 16× Baud Rate                         | 500 |     | ns               |                         |

| <sup>t</sup> TPD | Transmitter Input Clock Pulse Delay   |     |     |                  |                         |

|                  | 1× Baud Rate                          | 1.0 |     | us               |                         |

|                  | 16× Baud Rate                         | 500 |     | ns               |                         |

| t <sub>RX</sub>  | Receiver Input Clock Frequency        |     |     |                  |                         |

|                  | 1× Baud Rate                          | DC  | 500 | kHz              |                         |

|                  | 4×, 16× Baud Rate                     | DC  | 750 | kHz              |                         |

| <sup>t</sup> RPW | Receiver Input Clock Pulse Width      |     |     |                  |                         |

|                  | 1× Baud Rate                          | 1.0 |     | us               |                         |

|                  | 16× Baud Rate                         | 500 |     | ns               |                         |

| t <sub>RPD</sub> | Receiver Input Clock Pulse Delay      |     | 1   |                  |                         |

|                  | 1× Baud Rate                          | 1.0 | 1   | us               |                         |

|                  | 16× Baud Rate                         | 500 |     | ns               |                         |

|                  |                                       |     |     | ns               |                         |

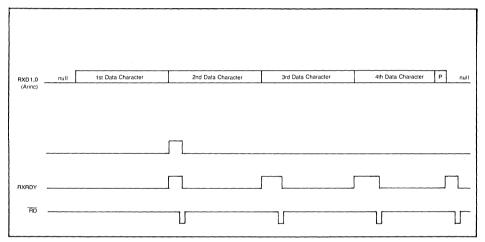

| <sup>t</sup> TX  | TXRDY Delay from center of Data Bit   |     | 1/2 | <sup>t</sup> TXC | (1x or 16x)             |

|                  |                                       |     |     |                  |                         |

SUCH-OZ 1

### A.C. TIMING PARAMETERS

| SYMBOL                             | PARAMETER                                                                                                         | MIN    | MAX      | UNIT                                 | TEST CONDITION                       |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------|----------|--------------------------------------|--------------------------------------|

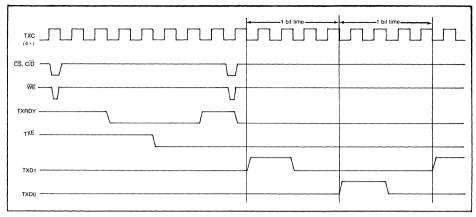

| t <sub>TX</sub><br>t <sub>RX</sub> | TXRDY Delay from Center of Data Bit<br>RXRDY Delay from Center of Data Bit (FCR<br>Delay from Center of Data Bit) | 200 ns | 2<br>1⁄2 | <sup>t</sup> TXC<br>R <sub>RXC</sub> | (4x)                                 |

|                                    | TXE Delay from Center of Data Bit                                                                                 |        | 1⁄2      | t <sub>TXC</sub>                     | C <sub>L</sub> = 50 pF<br>(1 × Rate) |

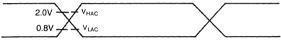

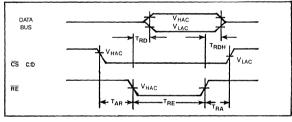

Figure 4 TEST POINTS FOR A.C. TIMING

Figure 5 READ CYCLE TIMING

Note: AC timings measured at  $V_{\mbox{OH}}$  = 2.0V,  $V_{\mbox{OL}}$  = 0.8V and with test load circuit.

Figure 6 WRITE CYCLE TIMING

**₩01--02**

Figure 9 TRANSMITTER TIMINGS (ARINC MODE)

Figure 10 RXRDY AND FCR TIMING

Figure 11 TXRDY AND TXE TIMINGS (4 Character Sequence)

SHCH-OZ

Figure 12 ARINC 429

The V/Z Receiver converts  $\pm 10$  volt levels to TTL logic levels. It is composed of logic one and zero comparators. A logic one (RXD1) TTL output is derived when voltage rising to 1 (VR1) threshold is crossed and terminated at voltage falling to 1 (VF1). A logic zero (RXD0) TTL output is generated between voltage falling to zero (VFO) and voltage rising from zero (VRO). When input thresholds are not exceeded, neither output is active. The V/Z output can drive one TTL input.

The return to zero (RZ) format is shown below

Figure 13 ARINC RECEIVER CIRCUIT

The V/Z Driver convert TTL logic levels into  $\pm$  10 volt levels. The TXD1 and TXD0 outputs of the WD1993 are used to drive the line drivers. Each output can drive one TTL load. When the outputs are not active, the line Driver should return to zero.

SUCT-OZ 1

Figure 15 ARINC 429 LINE LEVEL TRANSLATOR (RECEIVER)

Figure 16 ARINC 429-1 LINE DRIVER

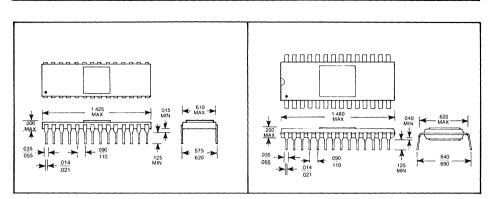

#### WD1993E CERAMIC PACKAGE

WD1993F PLASTIC PACKAGE

SO--10m

This is a preliminary specification with tentative device parameters and may be subject to change after final product characterization is completed.

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation reserves the right to change said circuitry at anytime without notice.

3128 REDHILL AVENUE, BOX 2180 NEWPORT BEACH, CA 92663 (714) 557-3550,TWX 910-595-1139