## **WD3120**

1A output current, fixed 5V Output voltage, Boost Converter with 2.75A Main-Switch

## **Descriptions**

The WD3120 is a high efficiency, peak current control mode DC-DC boost converter. It supports up to 1A output current with an integrated low  $R_{\rm DS(ON)}$  (130m $\Omega$ ) N-channel MOSFET and cycle by cycle current limit protection. The device provides a USB 5V compliant power output from a single Li-ion battery.

The boost converter runs in Pulse-Width Modulation (PWM) mode, at 1MHz fixed switching frequency to reduce output ripple, improve conversion efficiency. It allows for the use of small external components. At light load currents the converter enters Skipping Mode to maintain a high efficiency over a wide load current range. The build-in soft start circuitry minimizes the inrush current at start-up. Fixed 5V output and internal compensation network require only boost inductor, schottky diode, and input and output capacitors for WD3120, save PCB area.

The WD3120 is available in SOT-23-6L package. Standard product is Pb-free and Halogen-free.

#### **Features**

Input voltage range : 2.7~5.5VContinuous output current : 1.0A

Switching frequency : 1MHz (Typ.)

Efficiency : Up to 92%

Low R<sub>DS(ON)</sub> main switch : 0.13 Ω

Main switch current limit : 2.75A (Min.)

Fixed Output Voltage : 5VOutput voltage accuracy :±2%

### **Applications**

- MID

- Mobile power pack

- Mobile phones

- Notebook computers

- Portable games

#### Http//:www.willsemi.com

SOT-23-6L

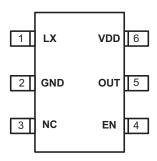

Pin configuration (Top view)

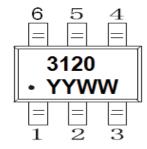

3120 = Device code

YY = Year code

WW = Week code

Marking

## **Order information**

| Device       | Package   | Shipping       |

|--------------|-----------|----------------|

| WD3120E-6/TR | SOT-23-6L | 3000/Reel&Tape |

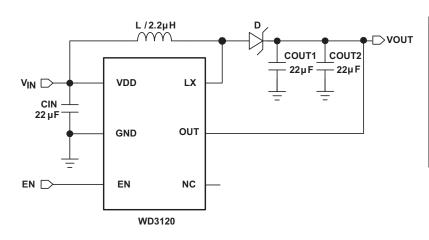

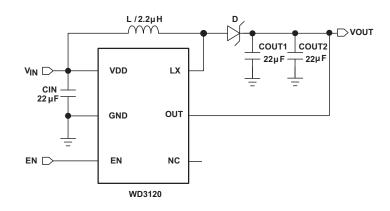

## Typical applications

# Pin descriptions

| Symbol | SOT-23-6L | Descriptions        |

|--------|-----------|---------------------|

| LX     | 1         | Switch pin          |

| GND    | 2         | Ground              |

| NC     | 3         | Not connect         |

| EN     | 4         | Enable, Active High |

| OUT    | 5         | Output pin          |

| VDD    | 6         | Input supply pin    |

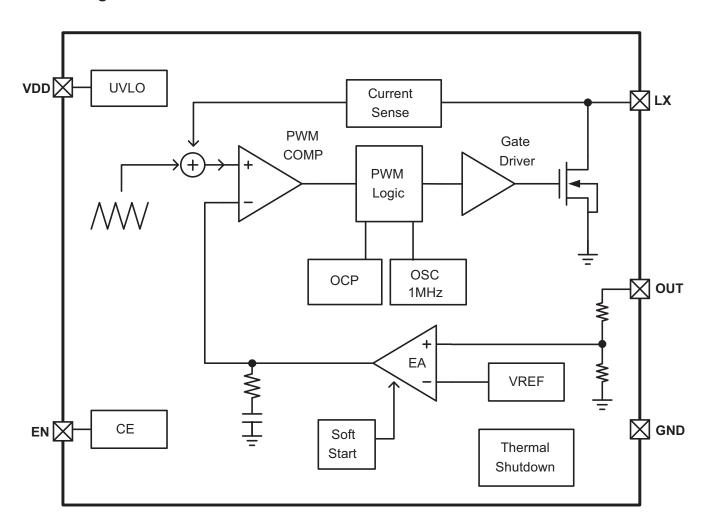

## **Block diagram**

## Absolute maximum ratings

| Parameter                                                   | Symbol           | Value                | Unit |

|-------------------------------------------------------------|------------------|----------------------|------|

| VDD pin voltage range                                       | $V_{DD}$         | -0.3~6.5             | V    |

| Out pin voltage range                                       | V <sub>OUT</sub> | -0.3~6.5             | V    |

| EN pin voltage range                                        | -                | -0.3~V <sub>DD</sub> | V    |

| LX pin voltage range (DC)                                   | -                | -0.3∼V <sub>DD</sub> | V    |

| Power Dissipation – SOT-23-6L (Note 1)                      | В                | 0.5                  | W    |

| Power Dissipation – SOT-23-6L (Note 2)                      | P <sub>D</sub>   | 0.3                  | W    |

| Junction to Ambient Thermal Resistance – SOT-23-6L (Note 1) | В                | 250                  | °C/W |

| Junction to Ambient Thermal Resistance – SOT-23-6L (Note 2) | $R_{\theta JA}$  | 416                  | °C/W |

| Junction temperature                                        | TJ               | 150                  | °C   |

| Lead temperature(Soldering, 10s)                            | T <sub>L</sub>   | 260                  | °C   |

| Operation temperature                                       | Topr             | -40 ~ 85             | °C   |

| Storage temperature                                         | Tstg             | -55 ~ 150            | °C   |

| ESD Potings                                                 | НВМ              | 8000                 | V    |

| ESD Ratings                                                 | MM               | 400                  | V    |

These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

Note 1: Surface mounted on FR-4 Board using 1 square inch pad size, dual side, 1oz copper

Note 2: Surface mounted on FR-4 board using minimum pad size, 1oz copper

# **Electronics Characteristics** (Ta=25°C, V<sub>IN</sub>=3.7V, V<sub>EN</sub>=V<sub>IN</sub>, unless otherwise noted)

| Parameter                     | Symbol                | Test Condition           | Min  | Тур  | Max | Units |

|-------------------------------|-----------------------|--------------------------|------|------|-----|-------|

| Operation Voltage Range       | $V_{DD}$              |                          | 2.7  |      | 5.5 | V     |

| Under Voltage Lockout         | V <sub>UVLO</sub>     | V <sub>IN</sub> Rising   | 1.8  | 2.2  | 2.5 | V     |

| UVLO Hysterisis               | V <sub>UVLO-HYS</sub> |                          |      | 0.1  |     | V     |

| Quiescent Current             | IQ                    | V <sub>OUT</sub> = 5.5V  |      | 0.3  | 1   | mA    |

| Supply Current                | Is                    | V <sub>OUT</sub> = 4.5V  |      | 1    | 2   | mA    |

| Shutdown Current              | I <sub>SD</sub>       | V <sub>EN</sub> < 0.4V   |      |      | 1   | μA    |

| Operation Frequency           | f <sub>OSC</sub>      |                          | 0.8  | 1    | 1.2 | MHz   |

| Maximum Duty Cycle            | D <sub>MAX</sub>      |                          | 85   |      |     | %     |

| Output Voltage                | V <sub>OUT</sub>      | I <sub>LOAD</sub> =100mA | 4.9  | 5    | 5.1 | V     |

| Main Switch MOS on-resistance | R <sub>on_s</sub>     | I <sub>LX</sub> =100mA   |      | 0.13 |     | Ω     |

| Main Switch Current Limit     | I <sub>LIM</sub>      |                          | 2.75 | 4.2  |     | Α     |

| Shutdown Voltage              | V <sub>ENL</sub>      |                          |      |      | 0.4 | V     |

| Enable Voltage                | V <sub>ENH</sub>      |                          | 1.5  |      |     | V     |

| EN Sink Current               | I <sub>EN</sub>       |                          |      | 3    |     | μA    |

| Thermal Shutdown Temperature  | T <sub>SD</sub>       |                          |      | 160  |     | °C    |

| T <sub>SD</sub> Hysteresis    | T <sub>SD-HYS</sub>   |                          |      | 30   |     | °C    |

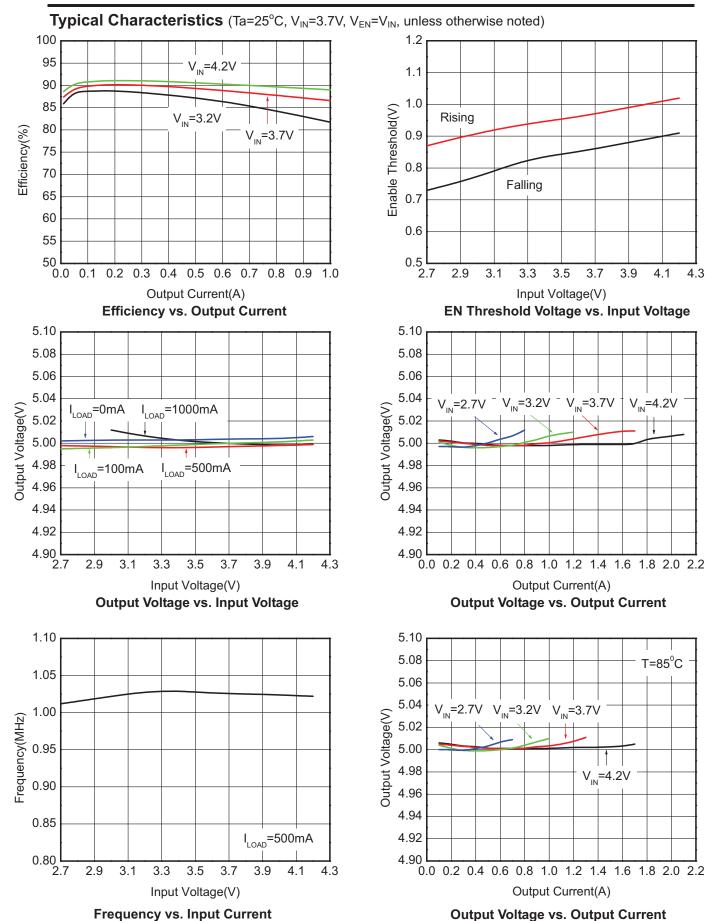

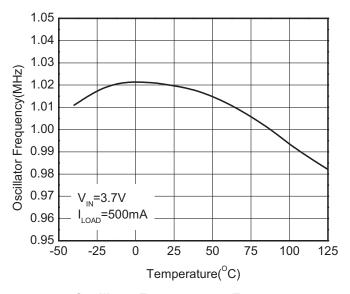

Oscillator Frequency vs. Temperature

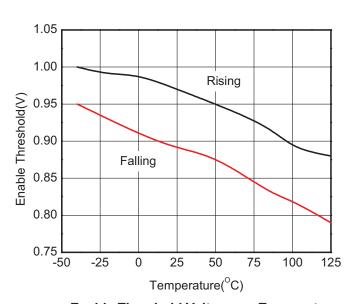

**Enable Threshold Voltage vs. Temperature**

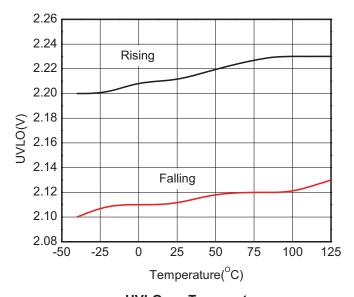

**UVLO vs. Temperature**

**Output Voltage vs. Temperature**

## **Operation Information**

#### **Normal Operation**

The WD3120 is a fixed 5V output, peak current controlled DC-DC boost converter. This means that switch duty cycle is directly controlled by the peak switch current rather than only by output voltage.

The WD3120 regulates the output voltage using a combined pulse-width (PWM) and pulse-skipping (PSM) modulation topology. In PWM mode, the device runs at a 1MHz fixed frequency. Referring to the block diagram, the switch is turned ON at the start of each oscillator cycle. It is turned OFF when switch current reaches a predetermined level. The current trip level is set by using an error amplifier which senses the converter output voltage. The main switch current sensing voltage signal is summed by a slope compensation voltage signal. Slope compensation is necessary to prevent sub-harmonic oscillations that may occur in peak current mode architectures when exceeding 50% duty cycle. At very light loads, the WD3120 will automatically enter pulse skipping mode (PSM). When the converter output voltage is slightly higher than 5V, the device will stop switching and skip some periods to maintain output regulation.

The WD3120 is highly integrated with a low on-resistance N-MOS switch, internal control-loop compensation network and soft-start circuitry. Additional features include Cycle-By-Cycle Current Limit Protection, Under Voltage Protection and Over Temperature Protection.

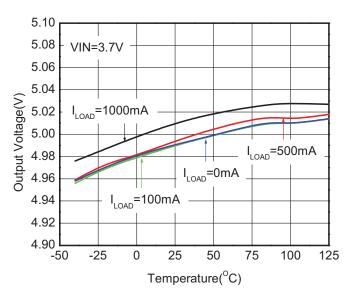

#### Start-Up

The build-in soft-start function of WD3120 is implemented to suppress the inrush current to an acceptable value at the beginning of power on.

### **Cycle by Cycle Current Limit**

The WD3120 uses a cycle-by-cycle current limit circuitry to limit the inductor peak current in the event of an overload condition. The current flow through inductor in charging phase is detected by a current sensing circuit. As the value comes across

the current limiting threshold the N- MOSFET turns off, so that the inductor will be forced to leave charging stage and enter discharging stage. Therefore, the inductor current will not increase over the current limiting threshold.

#### **UVLO Protection**

To avoid malfunction of the WD3120 at low input voltages, an under voltage lockout is included that disables the device, until the input voltage exceeds 2.2V (Typ.).

#### **Shutdown Mode**

Drive EN to GND to place the WD3120 in shutdown mode. In shutdown mode, the reference, control circuit, and the main switch turn off. Input current falls to smaller than  $1\mu A$  during shutdown mode.

#### **Over Temperature Protection (OTP)**

As soon as the junction temperature  $(T_J)$  exceeds  $160^{\circ}$ C (Typ.), the WD310 goes into thermal shutdown. In this mode, the main N-MOSFET is turned off until temperature falls below typically  $130^{\circ}$ C. Then the device starts switching again.

Will Semiconductor Ltd. 8 Feb, 2013 - Rev. 1.3

## **Application Information**

External component selection for the application circuit depends on the load current requirements. Certain tradeoffs between different performance parameters can also be made.

#### **Boost Inductor Selection**

A 2.2uH inductor is recommended to connect from VDD to LX. The minimum and maximum inductor values are constrained by considerations. The minimum inductance is limited by the peak inductor-current value. The ripple current in the inductor is inversely proportional to the inductance value, so the output voltage may fall out of regulation if the peak inductor current exceeds the current-limit value (2.75A minimum). Using a nominal 2.2uH inductor allows full recommended current operation even if the inductance is 20% low (1.76 uH) due to component variation. A maximum 4.7uH (typical) inductor value is recommended to maintain adequate phase margin over the full range of recommended operating conditions.

The saturation current of inductor should be higher enough than the peak switch current. And the inductor should have low core losses at 1MHz and low DCR (copper wire resistance).

## **Input Capacitor Selection**

Connect the input capacitance from VDD to the reference ground plane. Input capacitance reduces the ac voltage ripple on the input rail by providing a low-impedance path for the switching current of the boost converter. The WD3120 does not have a minimum or maximum input capacitance requirement for operation, but a 22uF, X7R or X5R ceramic capacitor is recommended for most applications for reasonable input-voltage ripple performance. There are several scenarios where it is recommended to use additional input capacitance.

### **Output Capacitor Selection**

Connect the boost-converter output capacitance from Output to the reference ground plane. The

Output capacitance controls the ripple voltage on the Output rail and provides a low-impedance path for the switching and transient-load currents of the boost converter. It also sets the location of the output pole in the control loop of the boost converter. There are limitations to the minimum and maximum capacitance on Output. The recommended minimum capacitors on Output are two 22uF, X5R or X7R ceramic capacitor. The low ESR of the ceramic capacitor minimizes ripple voltage and power dissipation from the large, pulsating currents of the boost converter and provides adequate phase margin across all recommended operating conditions.

#### **Diode Selection**

The rectifier diode supplies current path to the inductor when the internal MOSFET is off. Use a schottky with low forward voltage to reduce losses. The diode should be rated for a reverse blocking voltage greater than the output voltage used. The average current rating must be greater than the maximum load current expected, and the peak current rating must be greater than the peak inductor current.

Diode the following requirements:

Low forward voltage

High switching speed : 50ns max.

Reverse voltage : VOUT + VF or more

Rated current : IPK or more

#### **PC Board Layout Considerations**

A good circuit board layout aids in extracting the most performance from the WD3120. Poor circuit layout degrades the output ripple and the electromagnetic interference (EMI) or electromagnetic compatibility (EMC) performance. The evaluation board layout is optimized for the WD3120. Use this layout for best performance. If this layout needs changing, use the following guidelines:

- 1. Use separate analog and power ground planes. Connect the sensitive analog circuitry (such as voltage divider components) to analog ground; connect the power components (such as input and output bypass capacitors) to power ground. Connect the two ground planes together near the load to reduce the effects of voltage dropped on circuit board traces. Locate C<sub>IN</sub> as close to the V<sub>DD</sub> pin as possible, and use separate input bypass capacitors for the analog.

- 2. Route the high current path from  $C_{IN}$ , through L to the LX and PGND pins as short as possible.

- 3. Keep high current traces as short and as wide as possible.

- 4. The output filter of the boost converter is also critical for layout. The Diode and Output capacitors should be placed to minimize the area of current loop through Output –PGND–LX.

- 5. Avoid routing high impedance traces, such as Output, near the high current traces and components or near the Diode node (D).

- If high impedance traces are routed near high current and/or the LX node, place a ground plane shield between the traces.

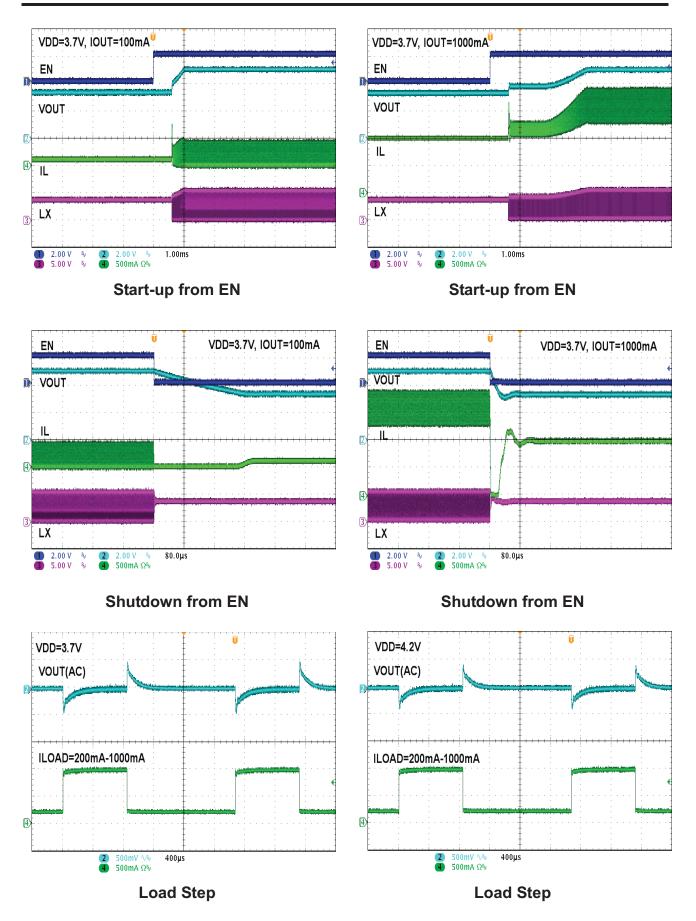

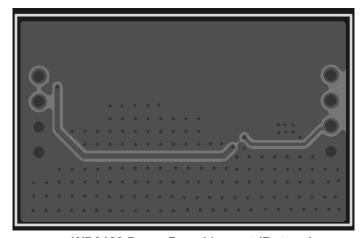

WD3120 Demo Board Layout (Top)

WD3120 Demo Board Layout (Bottom)

**WD3120 Demo Board Schematic**

Will Semiconductor Ltd. 10 Feb, 2013 - Rev. 1.3

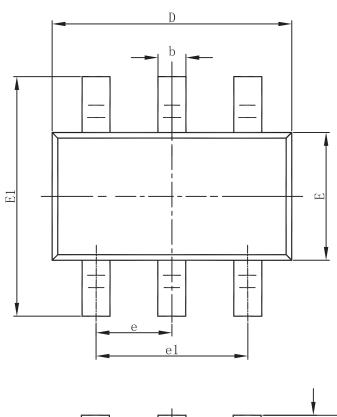

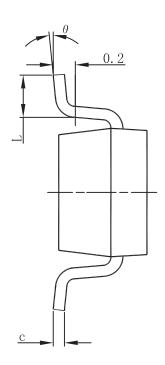

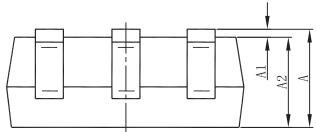

# Package outline dimensions

# SOT-23-6L

| Symbol | Dimensions in millimeter |       |       |  |

|--------|--------------------------|-------|-------|--|

|        | Min.                     | Тур.  | Max.  |  |

| A      | 1.050                    | -     | 1.250 |  |

| A1     | 0.000                    | -     | 0.100 |  |

| A2     | 1.050                    | -     | 1.150 |  |

| b      | 0.300                    | -     | 0.500 |  |

| С      | 0.100                    | -     | 0.200 |  |

| D      | 2.820                    | 2.900 | 3.020 |  |

| Е      | 1.500                    | 1.600 | 1.700 |  |

| E1     | 2.650                    | 2.800 | 2.950 |  |

| е      | 0.950(BSC)               |       |       |  |

| e1     | 1.800                    | -     | 2.000 |  |

| L      | 0.300                    | -     | 0.600 |  |

| θ      | 0°                       | -     | 8°    |  |