# 2Mx16 NOR Flash MODULE SMD 5962-97610\*

MERCURY Systems

WF2M16-XXX5

#### **FEATURES**

- Access Times of 90, 120, 150ns

- Packaging:

- 56 lead, Hermetic Ceramic, 0.520" CSOP (Package 207). Fits standard 56 SSOP footprint.

- 44 pin Ceramic SOJ (Package 102)\*\*

- Sector Architecture

- · 32 equal size sectors of 64KBytes each

- · Any combination of sectors can be erased. Also supports full chip erase.

- Minimum 100,000 Write/Erase Cycles Minimum

- Organized as 2Mx16; User Configurable as 2 x 2Mx8

- Commercial, Industrial, and Military Temperature Ranges

- 5 Volt Read and Write

- Low Power CMOS

- Data# Polling and Toggle Bit feature for detection of program or erase cycle completion.

- Supports reading or programming data to a sector not being erased.

- Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation.

- RESET# pin resets internal state machine to the read mode.

- Ready/Busy (RY#/BY#) output for detection of program or erase cycle completion.

- Multiple Ground Pins for Low Noise Operation

This product is subject to change without notice.

1/00-15

A0-20

WE#

CS1-2#

OE#

Vcc

$V_{\text{SS}}$

RY/BY#

RESET#

Note: For programming information and waveforms refer to Flash Programming 16M5 Application Notes AN0038

PIN DESCRIPTION

Data Inputs/Outputs

Address Inputs

Write Enable

Chip Select

Output Enable

Power Supply

Ready/Busy

Ground

Reset

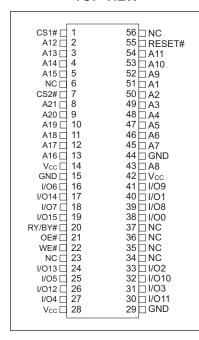

#### FIGURE 1 – PIN CONFIGURATIONS

## WF2M16-XDAX5 56 CSOP

WF2M16-XXX5 44 CSOJ (DL)\*\*

#### **TOP VIEW**

| CS1# 🔲 1    | 56 □ NC     |

|-------------|-------------|

| A12 🗆 2     | 55 ☐ #RESET |

| A13 🔲 3     | 54 🗆 A11    |

| A14 🔲 4     | 53 🗆 A10    |

| A15 🔲 5     | 52 🗀 A9     |

| NC 🗆 6      | 51 🗆 A1     |

| CS2# 🖂 7    | 50 🗆 A2     |

| NC 🗆 8      | 49 🗖 A3     |

| A20 🔲 9     | 48 🔲 A4     |

| A19 🔲 10    | 47 🗆 A5     |

| A18 🔲 11    | 46 🗆 A6     |

| A17 🔲 12    | 45 🗆 A7     |

| A16 🔲 13    | 44 🗆 GND    |

| Vcc 🔲 14    | 43 🗆 A8     |

| GND 🔲 15    | 42 🗆 Vcc    |

| I/O6 🔲 16   | 41 🔲 I/O9   |

| I/O14 🔲 17  | 40 🔲 I/O1   |

| I/O7 🗖 18   | 39 🔲 I/O8   |

| I/O15 🔲 19  | 38 🗖 1/00   |

| RY/BY# 🗆 20 | 37 🗖 A0     |

| OE# 🗆 21    | 36 🗆 NC     |

| WE# 🗆 22    | 35 🗆 NC     |

| NC 🗆 23     | 34 🗆 NC     |

| I/O13 🗆 24  | 33 🔲 I/O2   |

| I/O5 🗆 25   | 32 🔲 I/O10  |

| I/O12 🗆 26  | 31 🔲 I/O3   |

| I/O4 🖂 27   | 30 🗖 I/O11  |

| Vcc ☐ 28    | 29 🗆 GND    |

|             |             |

|             |             |

#### **TOP VIEW**

| CS1# 1                      | 56 NC      |  |  |  |  |  |

|-----------------------------|------------|--|--|--|--|--|

| A12 🗆 2                     | 55 #RESET  |  |  |  |  |  |

| A13 🖂 3                     | 54 A11     |  |  |  |  |  |

| A14 🗖 4                     | 53 🗖 A10   |  |  |  |  |  |

| A15 🗖 5                     | 52 🗖 A9    |  |  |  |  |  |

| NC 🗆 6                      | 51 🗖 A1    |  |  |  |  |  |

| CS2# 🖂 7                    | 50 🗖 A2    |  |  |  |  |  |

| NC 🗆 8                      | 49 🗆 A3    |  |  |  |  |  |

| A20 🗖 9                     | 48 🗆 A4    |  |  |  |  |  |

| A19 🔲 10                    | 47 🗖 A5    |  |  |  |  |  |

| A18 🔲 11                    | 46 🗖 A6    |  |  |  |  |  |

| A17 🔲 12                    | 45 🗆 A7    |  |  |  |  |  |

| A16 🔲 13                    | 44 🗆 GND   |  |  |  |  |  |

| Vcc ☐ 14                    | 43 🗆 A8    |  |  |  |  |  |

| GND 🗆 15                    | 42 □ Vcc   |  |  |  |  |  |

| I/O6 🖂 16                   | 41 🔲 1/09  |  |  |  |  |  |

| I/O14 🔲 17                  | 40 🔲 I/O1  |  |  |  |  |  |

| I/O7 🔲 18                   | 39 🔲 1/08  |  |  |  |  |  |

| I/O15 🔲 19                  | 38 🗀 1/00  |  |  |  |  |  |

| RY/BY# 🔲 20                 | 37 🗖 A0    |  |  |  |  |  |

| OE# 🗆 21                    | 36 🏻 NC    |  |  |  |  |  |

| WE# 🗌 22                    | 35 🏻 NC    |  |  |  |  |  |

| NC 🗆 23                     | 34 🏻 NC    |  |  |  |  |  |

| I/O13 🔲 24                  | 33 🔲 1/02  |  |  |  |  |  |

| I/O5 🔲 25                   | 32 🔲 I/O10 |  |  |  |  |  |

| I/O12 🔲 26                  | 31 🔲 1/03  |  |  |  |  |  |

| 1/04 🔲 27                   | 30 🔲 1/011 |  |  |  |  |  |

| Vcc ☐ 28                    | 29 GND     |  |  |  |  |  |

| ** Package to be developed. |            |  |  |  |  |  |

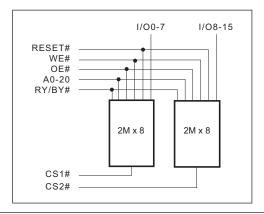

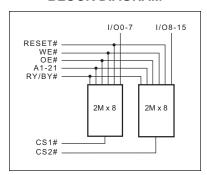

### **BLOCK DIAGRAM**

- 1. RY/BY# is an open drain output and should be pulled up to Vcc with an external resistor.

- 2. Address compatible with Intel 2M8 56 SSOP.

<sup>\*</sup> For reference only. See table page 7.

<sup>\*\*</sup> Package to be developed.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                               | Symbol | Ratings      | Unit   |

|-----------------------------------------|--------|--------------|--------|

| Voltage on Any Pin Relative to Vss      | VT     | -2.0 to +7.0 | V      |

| Storage Temperature                     | Tstg   | -65 to +150  | °C     |

| Data Retention (Mil Temp)               |        | 20           | years  |

| Endurance — write/erase cycles (Mil, Q) |        | 100,000 min. | cycles |

#### NOTES:

- 1. Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, inputs may overshoot V<sub>SS</sub> to -2.0 V for periods of up to 20 ns. See . Maximum DC voltage on output and I/O pins is V<sub>CC</sub> + 0.5 V. During voltage transitions, outputs may overshoot to V<sub>CC</sub> + 2.0 V for periods up to 20 ns. See .

- Minimum DC input voltage on A9, OE#, RESET# pins is -0.5V. During voltage transitions, A9, OE#, RESET# pins may overshoot V<sub>SS</sub> to -2.0 V for periods of up to 20 ns. See Maximum DC input voltage on A9, OE#, and RESET# is 12.5 V which may overshoot to 13.5 V for periods up to 20 ns.

Stresses greater than those listed in this section may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

#### **CAPACITANCE**

$(T_A = +25^{\circ}C)$

| Parameter                 | Symbol           | Conditions                         | Max | Unit |

|---------------------------|------------------|------------------------------------|-----|------|

| OE# capacitance           | Coe              | V <sub>IN</sub> = 0V, f = 1.0 MHz  | 25  | pF   |

| WE# capacitance           | Cwe              | V <sub>IN</sub> = 0V, f = 1.0 MHz  | 25  | pF   |

| CS# capacitance           | Ccs              | V <sub>IN</sub> = 0V, f = 1.0 MHz  | 15  | pF   |

| Data I/O capacitance      | C <sub>I/O</sub> | V <sub>I/O</sub> = 0V, f = 1.0 MHz | 15  | pF   |

| Address input capacitance | CAD              | V <sub>IN</sub> = 0V, f = 1.0 MHz  | 25  | pF   |

This parameter is guaranteed by design but not tested.

#### RECOMMENDED DC OPERATING CONDITIONS

| Parameter                      | Symbol | Min  | Тур | Max       | Unit |

|--------------------------------|--------|------|-----|-----------|------|

| Supply Voltage                 | Vcc    | 4.5  | 5.0 | 5.5       | V    |

| Ground                         | Vss    | 0    | 0   | 0         | V    |

| Input High Voltage             | Vih    | 2.0  | _   | Vcc + 0.5 | V    |

| Input Low Voltage              | VıL    | -0.5 | _   | +0.8      | V    |

| Operating Temperature (Mil, Q) | TA     | -55  | _   | +125°C    | °C   |

| Operating Temperature (Ind)    | TA     | -40  | _   | +85       | °C   |

| Operating Temperature (Com)    | TA     | 0    | _   | +70       | °C   |

#### DC CHARACTERISTICS - CMOS COMPATIBLE

| Parameter                                   | Symbol | Conditions                                                                       | Min      | Max  | Unit |

|---------------------------------------------|--------|----------------------------------------------------------------------------------|----------|------|------|

| Input Leakage Current                       | ILI    | V <sub>CC</sub> = V <sub>CC MAX</sub> , V <sub>IN</sub> = GND to V <sub>CC</sub> |          | 10   | μΑ   |

| Output Leakage Current                      | ILO    | Vcc = Vcc MAX, Vout = GND to Vcc                                                 |          | 10   | μΑ   |

| Vcc Active Current for Read (1)             | Icc1   | CS# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , f = 5MHz                         |          | 80   | mA   |

| Vcc Active Current for Program or Erase (2) | Icc2   | CS# = VIL, OE# = VIH                                                             |          | 120  | mA   |

| Vcc Standby Current                         | Іссз   | Vcc = Vcc MAX, CS# = Vcc ± 0.5V, f = 5MHz, RESET# = Vcc ± 0.5V                   |          | 4.0  | mA   |

| Output Low Voltage                          | Vol    | IoL = 12.0 mA, Vcc = Vcc min                                                     |          | 0.45 | V    |

| Output High Voltage                         | Voн    | I <sub>OH</sub> = -2.5 mA, V <sub>CC</sub> = V <sub>CC</sub> MIN                 | 0.85xVcc |      | V    |

| Low Vcc Lock-Out Voltage                    | VLKO   |                                                                                  | 3.2      | 4.2  | V    |

#### NOTES

- 1. The lcc current is typically less than 4mA/MHz, with OE# at  $V_{IH}$ .

- 2.  $I_{\text{CC}}$  active while Embedded Algorithm (program or erase) is in progress.

## AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS - WE# CONTROLLED

| Parameter                                  | Syn    | nbol | Min | 90<br>Max | Min -1 | 20<br>Max | Min -1 | 50<br>Max | Unit |

|--------------------------------------------|--------|------|-----|-----------|--------|-----------|--------|-----------|------|

| Write Cycle Time                           | tavav  | twc  | 90  |           | 120    |           | 150    |           | ns   |

| Chip Select Setup Time                     | telwl  | tcs  | 0   |           | 0      |           | 0      |           | ns   |

| Write Enable Pulse Width                   | twLwH  | twp  | 45  |           | 50     |           | 50     |           | ns   |

| Address Setup Time                         | tavwl  | tas  | 0   |           | 0      |           | 0      |           | ns   |

| Data Setup Time                            | tovwн  | tos  | 45  |           | 50     |           | 50     |           | ns   |

| Data Hold Time                             | twhox  | tон  | 0   |           | 0      |           | 0      |           | ns   |

| Address Hold Time                          | twlax  | tан  | 45  |           | 50     |           | 50     |           | ns   |

| Write Enable Pulse Width High              | twhwL  | twph | 20  |           | 20     |           | 20     |           | ns   |

| Duration of Byte Programming Operation (1) | twnwh1 |      |     | 300       |        | 300       |        | 300       | μs   |

| Sector Erase (2)                           | twnwh2 |      |     | 15        |        | 15        |        | 15        | sec  |

| Read Recovery Time before Write            | tghwl  |      | 0   |           | 0      |           | 0      |           | μs   |

| Vcc Setup Time                             | tvcs   |      | 50  |           | 50     |           | 50     |           | μs   |

| Chip Programming Time                      |        |      |     | 44        |        | 44        |        | 44        | sec  |

| Chip Erase Time (3)                        |        |      |     | 256       |        | 256       |        | 256       | sec  |

| Output Enable Hold Time (4)                |        | toeh | 10  |           | 10     |           | 10     |           | ns   |

| RESET# Pulse Width                         |        | trp  | 500 |           | 500    |           | 500    |           | ns   |

#### NOTES:

- 1. Typical value for  $t_{WHWH1}$  is  $7\mu s$ .

- Typical value for twhwh2 is 1sec.

- 3. Typical value for Chip Erase Time is 32sec.

- 4. For Toggle and Data Polling.

## **AC CHARACTERISTICS – READ-ONLY OPERATIONS**

| Parameter                                                         | Syn               | nbol               | Min - G | 90<br>Max | -1<br>Min | 20<br>Max | Min -1 | 50<br>Max | Unit |

|-------------------------------------------------------------------|-------------------|--------------------|---------|-----------|-----------|-----------|--------|-----------|------|

| Read Cycle Time                                                   | Tavav             | T <sub>RC</sub>    | 90      |           | 120       |           | 150    |           | ns   |

| Address Access Time                                               | TAVQV             | TACC               |         | 90        |           | 120       |        | 150       | ns   |

| Chip Select Access Time                                           | T <sub>ELQV</sub> | TCE                |         | 90        |           | 120       |        | 150       | ns   |

| Output Enable to Output Valid                                     | T <sub>GLQV</sub> | ToE                |         | 40        |           | 50        |        | 55        | ns   |

| Chip Select High to Output High Z (1)                             | T <sub>EHQZ</sub> | T <sub>DF</sub>    |         | 20        |           | 30        |        | 35        | ns   |

| Output Enable High to Output High Z (1)                           | Tghqz             | TDF                |         | 20        |           | 30        |        | 35        | ns   |

| Output Hold from Addresses, CS# or OE# Change, whichever is First | Taxqx             | Тон                | 0       |           | 0         |           | 0      |           | ns   |

| RESET# Low to Read Mode (1)                                       |                   | T <sub>READY</sub> |         | 20        |           | 20        |        | 20        | μs   |

<sup>1.</sup> Guaranteed by design, not tested.

## AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS,CS# CONTROLLED

| Parameter                                  | Syr    | nbol | q<br>Min | 90<br>Max | Min -1 | 20<br>Max | -1<br>Min | 50<br>Max | Unit |

|--------------------------------------------|--------|------|----------|-----------|--------|-----------|-----------|-----------|------|

| Write Cycle Time                           | tavav  | twc  | 90       |           | 120    |           | 150       |           | ns   |

| Write Enable Setup Time                    | twlel  | tws  | 0        |           | 0      |           | 0         |           | ns   |

| Chip Select Pulse Width                    | teleh  | tcp  | 45       |           | 50     |           | 50        |           | ns   |

| Address Setup Time                         | tavel  | tas  | 0        |           | 0      |           | 0         |           | ns   |

| Data Setup Time                            | toven  | tos  | 45       |           | 50     |           | 50        |           | ns   |

| Data Hold Time                             | tehdx  | tон  | 0        |           | 0      |           | 0         |           | ns   |

| Address Hold Time                          | telax  | tан  | 45       |           | 50     |           | 50        |           | ns   |

| Chip Select Pulse Width High               | tehel  | tсрн | 20       |           | 20     |           | 20        |           | ns   |

| Duration of Byte Programming Operation (1) | twnwh1 |      |          | 300       |        | 300       |           | 300       | μs   |

| Sector Erase Time (2)                      | twnwh2 |      |          | 15        |        | 15        |           | 15        | sec  |

| Read Recovery Time                         | tghel  |      | 0        |           | 0      |           | 0         |           | μs   |

| Chip Programming Time                      |        |      |          | 44        |        | 44        |           | 44        | sec  |

| Chip Erase Time (3)                        |        |      |          | 256       |        | 256       |           | 256       | sec  |

| Output Enable Hold Time (4)                |        | tоен | 10       |           | 10     |           | 10        |           | ns   |

#### NOTES:

- 1. Typical value for twнwн1 is 7µs.

- 2. Typical value for twhwh2 is 1sec.

- 3. Typical value for Chip Erase Time is 32sec.

- 4. For Toggle and Data Polling.

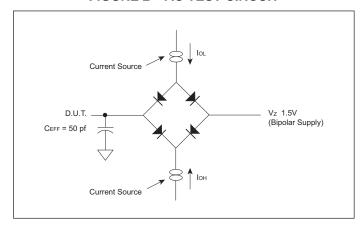

## FIGURE 2 - AC TEST CIRCUIT

## **AC TEST CONDITIONS**

| Parameter                        | Тур                                        | Unit |

|----------------------------------|--------------------------------------------|------|

| Input Pulse Levels               | V <sub>IL</sub> = 0, V <sub>IH</sub> = 3.0 | V    |

| Input Rise and Fall              | 5                                          | ns   |

| Input and Output Reference Level | 1.5                                        | V    |

| Output Timing Reference Level    | 1.5                                        | V    |

## NOTES:

Vz is programmable from -2V to +7V.

IoL & IoH programmable from 0 to 16mA.

Tester Impedance Z0 = 75 ý.

Vz is typically the midpoint of VoH and VoL.

IoL & IoH are adjusted to simulate a typical resistive load circuit.ATE tester includes jig capacitance.

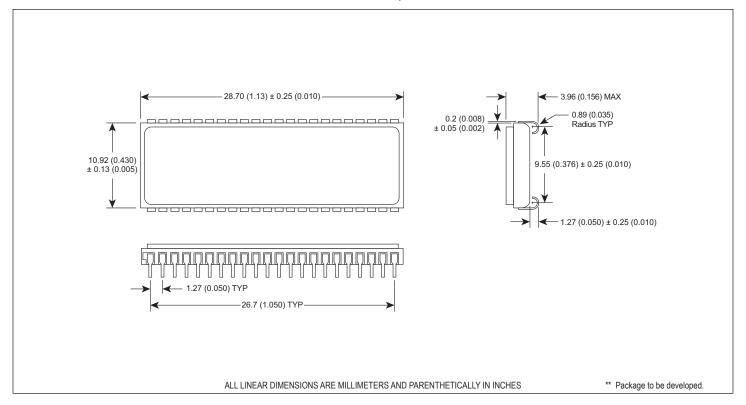

#### PACKAGE 102 - 44 LEAD, CERAMIC SOJ\*\*

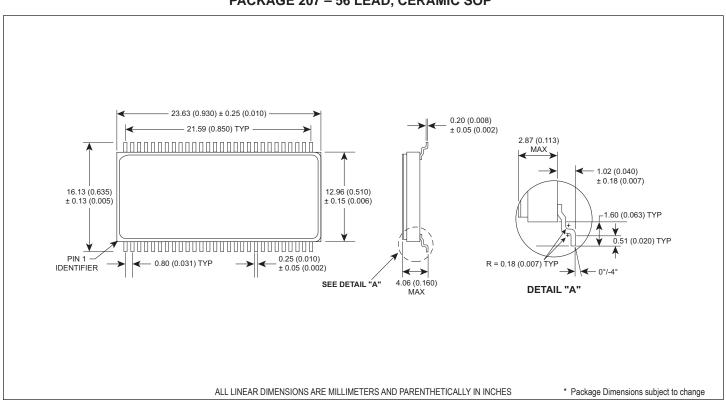

## PACKAGE 207 - 56 LEAD, CERAMIC SOP\*

#### FIGURE 8 – ALTERNATE PIN CONFIGURATION FOR WF2M16W-XDAX5

## 56 CSOP TOP VIEW

#### **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

| I/O0-15 | Data Inputs/Outputs |

|---------|---------------------|

| A0-21   | Address Inputs      |

| WE#     | Write Enable        |

| CS1-2#  | Chip Select         |

| OE#     | Output Enable       |

| Vcc     | Power Supply        |

| Vss     | Ground              |

| RY/BY#  | Ready/Busy          |

| RESET#  | Reset               |

|         |                     |

#### NOTE:

- 1. RY/BY# is an open drain output and should be pulled up toVcc with an external resistor.

- 2. Address compatible with Intel 1M16 56 SSOP.

6

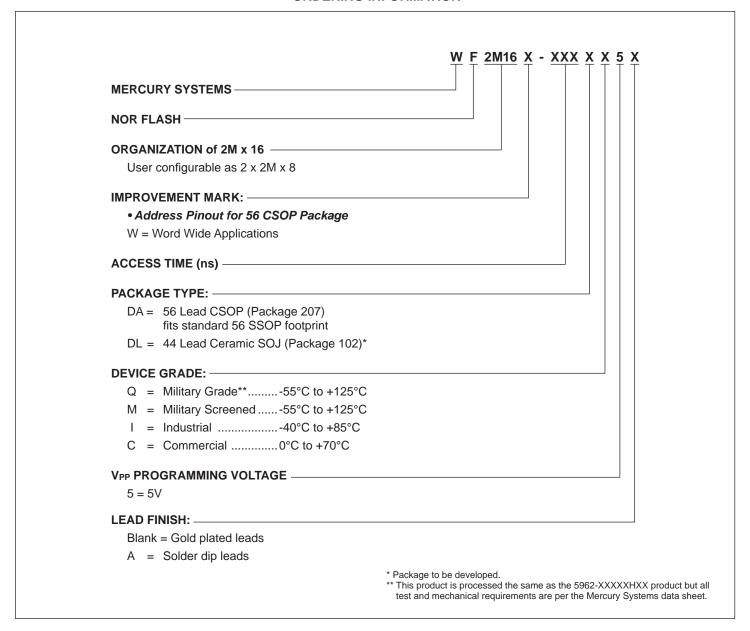

#### **ORDERING INFORMATION**

| DEVICE TYPE       | SECTOR SIZE | SPEED | PACKAGE | SMD NO.          |

|-------------------|-------------|-------|---------|------------------|

| 2M x 16 Flash MCP |             | 150ns |         | 5962-97610 04HXX |

| 2M x 16 Flash MCP |             | 120ns |         | 5962-97610 05HXX |

| 2M x 16 Flash MCP |             | 90ns  |         | 5962-97610 06HXX |

NOTE: This table is for reference only. For 5962-97610 ordering information and specifications refer to latest SMD document.

## **Document Title**

2Mx16 NOR Flash MODULE, SMD 5962-97610

## **Revision History**

| Rev#   | History                                                                                                     | Release Date | Status      |

|--------|-------------------------------------------------------------------------------------------------------------|--------------|-------------|

| Rev 6  | Changes (Pg. 1-13)                                                                                          | June 2011    | Preliminary |

|        | 6.1 Change document layout from White Electronic Designs to Microsemi                                       |              |             |

|        | 6.2 Add document Revision History page                                                                      |              |             |

| Rev 7  | Changes (Pg. 1, 13)                                                                                         | August 2011  | Final       |

|        | 7.1 Add "NOR" to headline                                                                                   |              |             |

| Rev 8  | Changes (Pg. 1, 13)                                                                                         | June 2012    | Final       |

|        | 8.1 Update Features                                                                                         |              |             |

|        | 8.2 Delete 44 Flatpack (FL)** from Figure 1                                                                 |              |             |

|        | 8.3 Update Absolute Maximum Ratings, Recommended DC Operating Conditions and DC Characteristics charts.     |              |             |

|        | 8.4 Delete subhead from AC Characteristics charts                                                           |              |             |

|        | 8.5 Delete Figure 3 and all AC Waveforms diagrams                                                           |              |             |

|        | 8.6 Update Packages 102, 208 and 207.                                                                       |              |             |

|        | 8.7 Update Ordering Information                                                                             |              |             |

|        | 8.8 Add note to SMD chart                                                                                   |              |             |

| Rev 9  | Change (Pg. 7)                                                                                              | May 2014     | Final       |

|        | 9.1 Changed Device Grade "Q" description from "MIL-STD-883 Compliant" to "MIL-PRF-38534 Class H Compliant." | ·            |             |

| Rev 10 | Change (Pg. 7)                                                                                              | August 2014  | Final       |

|        | 10.1 Changed Device Grade "Q" description from "MIL-PRF-38534 Class H<br>Compliant" to "Military Grade."    |              |             |

| Rev 11 | Change (Pg. 5) (ECN 9789)                                                                                   | January 2016 | Final       |

|        | 11.1 Changed lead dimensions on Package 207                                                                 |              |             |

| Rev 12 | Changes (Pg. All) (ECN 10156)                                                                               | August 2016  | Final       |

|        | 12.1 Change document layout from Microsemi to Mercury Systems                                               | -            |             |

|        |                                                                                                             |              |             |