# **PRELIMINARY**

# WMS7201 256-TAP NON-VOLATILE DIGITAL POTENTIOMETER

#### 1. GENERAL DESCRIPTION

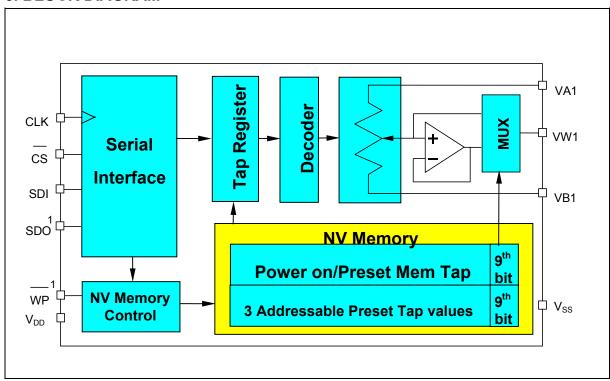

The WMS7201 is a 256-tap, single-channel non-volatile digital potentiometer available in  $10K\Omega$ ,  $50K\Omega$  and  $100K\Omega$  end-to-end resistances. These devices can be used as a three-terminal potentiometer or as a two terminal variable resistor in a wide variety of applications.

The output of the potentiometer is determined by the wiper position, which varies linearly between VA and VB terminal according to the content stored in the volatile Tap Register (TR). The settings of the TR can be provided either directly by the user through the industry standard SPI interface, or by the non-volatile memory (NVMEM0~3) where the previous settings are stored. When changes are made to the TR to establish a new wiper position, the value of the setting can be saved into any non-volatile memory location (NVMEM0~3) by executing a NVMEM save operation. Upon powerup the content of the NVMEM0 is automatically loaded to the Tap Register.

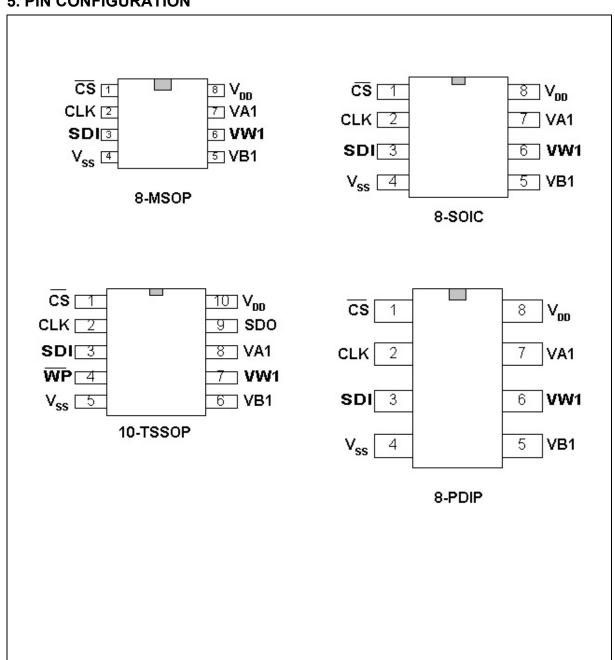

The WMS7201 contains a single potentiometer in 8-pin PDIP, SOIC, MSOP or 10 pin TSSOP packages and can operate over a wide operating voltage range from 2.7V to 5.5V. A selectable output buffer is built-in for those applications where an output buffer is required.

#### 2. FEATURES

- 256 taps for the potentiometer

- End-to-end resistance available in  $10K\Omega$ ,  $50K\Omega$  and  $100K\Omega$

- · Selectable output buffer for each channel

- SPI Serial Interface for data transfer and potentiometer control

- Daisy-chain operation for multiple devices (10-pin TSSOP package only)

- Nonvolatile storage of four wiper positions per channel with power-on recall from NVMEM0

- Low standby current (1μA Max. with output buffer inactive)

- Endurance 100K typical stores per bit

- Register Data Retention 100 years

- Industrial temperature range: -40 ~ 85°C

- Wide operating voltage range: 2.7V ~ 5.5V

- Package option:

- 8-pin MSOP, 8-pin SOIC, 8-pin PDIP, 10-pin TSSOP

# 3. BLOCK DIAGRAM

FIGURE 1 - WMS7201 BLOCK DIAGRAM

Note 1: Available in 10-pin TSSOP packages only.

# **WMS7201**

| 4  | ТΔ | RI | F | ΛF  | CC     | N     | TF | N٦ | rs. |

|----|----|----|---|-----|--------|-------|----|----|-----|

| →. | _  | 1  |   | VI. | $\sim$ | 7 I Y |    |    | J   |

| 1. GENERAL DESCRIPTION                                                    | 2  |

|---------------------------------------------------------------------------|----|

| 2. FEATURES                                                               | 2  |

| 3. BLOCK DIAGRAM                                                          | 3  |

| 4. TABLE OF CONTENTS                                                      | 4  |

| 5. PIN CONFIGURATION                                                      | 5  |

| 6. PIN DESCRIPTION                                                        | 5  |

| 7. FUNCTIONAL DESCRIPTION                                                 | 7  |

| 7.1. Potentiometer and Rheostat Modes                                     | 7  |

| 7.1.1. Rheostat Configuration                                             | 7  |

| 7.1.2. Potentiometer Configuration                                        | 7  |

| 7.2. Programming Modes                                                    | 7  |

| 7.3. Non-Volatile Memory (NVMEM)                                          | 8  |

| 7.3.1 Write Protect of NVMEM                                              | 8  |

| 7.4 Flow Control                                                          | 8  |

| 7.5. Daisy Chain                                                          | 9  |

| 7.6. Serial Data Iterface                                                 | 10 |

| 7.7. Instruction Set                                                      | 12 |

| 7.8. Basic Operation                                                      | 12 |

| 7.8.1 Sending a Command                                                   | 12 |

| 7.8.2 Wake Up/Sleep/Power Commands                                        | 13 |

| 7.8.3 Write to Tap Register (TR)                                          | 13 |

| 7.8.4 Programming Non-Volatile Memory (NVMEM)                             | 14 |

| 7.8.5 Reading Tap Register and NVMEM Location (10-pin TSSOP package only) | 15 |

| 8. TIMING DIAGRAMS                                                        | 16 |

| 9. ABSOLUTE MAXIMUM RATINGS                                               | 18 |

| 10. ELECTRICAL CHARACTERISTICS                                            | 19 |

| 10.1 Test Circuits                                                        | 21 |

| 11. TYPICAL APPLICATION CIRCUIT                                           | 22 |

| 11.1. Layout Considerations                                               | 24 |

| 12. PACKAGE DRAWINGS AND DEMINSIONS                                       | 25 |

| 13. ORDERING INFORMATION                                                  | 28 |

| 1/ VERSION HISTORY                                                        | 20 |

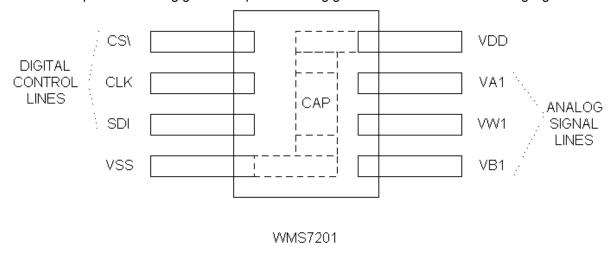

# 5. PIN CONFIGURATION

FIGURE 2 - PACKAGE TYPES

# 6. PIN DESCRIPTION

# **TABLE 1 – PIN DESCRIPTION**

| PIN NAME         | PIN NO | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK              | 2      | ı   | Serial Clock pin. Data Shifts in one bit at a time on positive clock (CLK) edges                                                                                                                                                                                                                                                                                               |

| <del>C</del> S   | 1      | ı   | Chip Select pin. When CS is HIGH, WMS7201 is deselected and the SDO pin is at high impedance, and (unless an internal write cycle is underway) the device will be in the standby state. CS LOW enables WMS7201, placing it in the active power mode. It should be noted that after a power-up, a HIGH to LOW transition on CS is required prior to the start of any operation. |

| SDI              | 3      | 1   | Serial Data Input pin. All opcodes, byte addresses and data to be written to the registers are input on this pin. Data is latched by the rising edge of the serial clock.                                                                                                                                                                                                      |

| SDO <sup>1</sup> | NC     | 0   | Serial Data Output pin with open-drain output. During a read cycle, data is shifted out on this pin. Data is clocked out by the falling edge of the serial clock except for the 1 <sup>st</sup> bit, which is clocked out by the falling edge of CS. Also can be used to daisy-chain several parts. (Only 10-pin TSSOP package)                                                |

| WP 1             | NC     | ı   | Hardware Write Protect pin. When active LOW WP prevents any changes to the present contents except retrieving NVMEM contents. (Only 10-pin TSSOP package)                                                                                                                                                                                                                      |

| V <sub>DD</sub>  | 8      | -   | Power Supply                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>SS</sub>  | 4      | -   | Ground pin, logic ground reference                                                                                                                                                                                                                                                                                                                                             |

| VA1              | 7      | -   | A terminal of potentiometer '1', equivalent to the HI terminal connection on a mechanical potentiometer                                                                                                                                                                                                                                                                        |

| VB1              | 5      | -   | B terminal of potentiometer '1', equivalent to the LO terminal connection on a mechanical potentiometer                                                                                                                                                                                                                                                                        |

| VW1              | 6      | 0   | Wiper terminal of potentiometer '1', equivalent to the wiper terminal of a mechanical potentiometer                                                                                                                                                                                                                                                                            |

#### 7. FUNCTIONAL DESCRIPTION

The WMS7201 series, a family of 256-tap, nonvolatile digitally programmable potentiometers is designed to operate as both a potentiometer or a variable resistor depending upon the output configuration selected.

The chip can store four 9-bit words in nonvolatile memory (NVMEM0 ~ NVMEM3) and the word stored in the NVMEM0 will be used to set the tap register values when the device is powered up.

The WMS7201 is controlled by a serial SPI interface that allows setting tap register value as well as storing data in the nonvolatile memory.

#### 7.1. POTENTIOMETER AND RHEOSTAT MODES

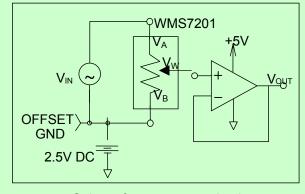

The WMS7201 can operate as either a rheostat or as a potentiometer (voltage divider). When in the potentiometer configuration there are two possible modes. One is without the output buffer and the other mode is with the output buffer. Selecting the mode is done by controlling bit D8 of the data register. D8 = 0 sets the output buffer off and D8 = 1 sets it on.

Note that this bit can only be set by loading the value to the NVMEM with instructions #5 and then loading the TAP register with instruction #6 from NVMEM. This bit cannot be controlled by directly writing the value to the chip when the tap register is set.

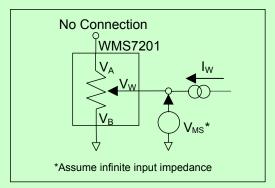

#### 7.1.1. Rheostat Configuration

The WMS7201 acts as a two terminal resistive element in the rheostat configuration where one terminal is either one of the end point pins of the resistor (VA and VB) and the other terminal is the wiper (VW) pin. This configuration controls the resistance between the two terminals and the resistance can be adjusted by sending the corresponding tap register setting commands to the WMS7201 or loading a pre-set tap register value from nonvolatile memory NVMEM0 ~ MVMEM3.

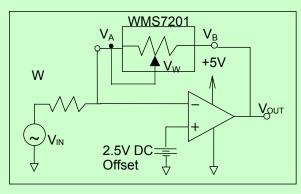

#### 7.1.2. Potentiometer Configuration

In potentiometer configuration an input voltage is connected to one of the end point pins (VA or VB). The voltage on the wiper pin will be proportional to the voltage difference between VA and VB and the wiper setting. The resistance cannot be directly measured in this configuration.

#### 7.2. Programming Modes

Two program modes are available for the WMS7201:

- **Direct program mode**. The tap register setting can be changed either by loading a predetermined value from an external microcontroller or by using the UP/DOWN command. The UP and DOWN commands change the tap register setting incrementally i.e., 1 LSB at a time. The UP and DOWN commands will not wrap around at the ends of the scale.

- NVMEM restore mode. One of the previously stored settings can be loaded into the TR

register from the non-volatile memory. Four 9-bit non-volatile memories, are available for to

store the tap register settings. The first register, NVMEM0, stores the favorite or default tap

register setting that will be loaded into the tap register at system power up or software power

on reset operation.

#### 7.3. NON-VOLATILE MEMORY (NVMEM)

The WMS7201 has four NVMEM positions available for storing the output buffer operating mode and the potentiometer setting. These NVMEM positions can be directly written through the SPI using a write command (#5) with address and data bytes. Another command (#7) is available that stores the current output buffer operating mode and potentiometer settings into the selected NVMEM position. Bit A3 and A2 in the instruction byte decide which NVMEM position is used. (See Table 5)

The potentiometer is loaded with the value stored in the NVMEM position 0 on power up.

#### 7.3.1 Write Protect of NVMEM

Write-Protect ( $\overline{\text{WP}}$ ) disables any changes of current content in the NVMEM regardless of the commands, except that NVMEM setting can be retrieved using commands 4, 6 of Table 5. Therefore, Write-Protect ( $\overline{\text{WP}}$ ) pin provides hardware NVMEM protection feature with  $\overline{\text{WP}}$  tied to Vss.  $\overline{\text{WP}}$ , which is active at logic LOW, should be tied directly to V<sub>DD</sub> if it is not being used. This function is only available on the 10-pin package.

#### 7.4 FLOW CONTROL

Reading and writing to NVMEM requires an internal access cycle to complete before the next command can be sent.

Read Tap Register (#2)

Read NVMEM (#4)

Program NVMEM (#5)

Load Tap Register(#6)

Program NVMEM with Tap Register (#7)

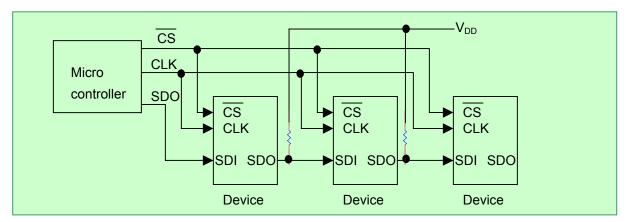

#### 7.5. Daisy Chain

Multiple devices can be controlled by the same bus without the need for extra  $\overline{CS}$  lines from the microcontroller by daisy chaining the devices with the SDO of the first device connected to SDI of the next device as shown in figure 3 when using the 10-pin package.

FIGURE 3 - DAISY CHAIN CONFIGURATION [10-PIN TSSOP PACKAGE ONLY]

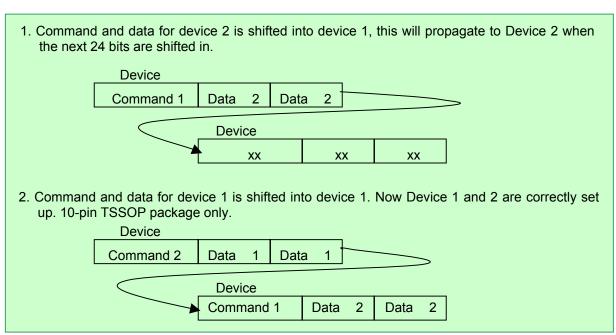

A complete command is 24 bits including the instruction and the two data bytes. When shifting 24 bits in to the first device in the chain, the 24 bits of the previous command will be shifted out. So to set up two devices in a daisy chain, a total of 48 bits must be sent where the first 24 bits will be shifted out to the second device and the 24 bits shifted in last will remain in the first device.

FIGURE 4 - DAISY CHAIN COMMAND EXAMPLE

#### 7.6. SERIAL DATA ITERFACE

The WMS7201 contains a four-wire SPI interface:

- **SDO** (Serial Data Output) Used for reading out the internal register contents and for daisy chaining multiple devices on the 10-pin package.

- SDI (Serial Data Input) Used for clocking in commands and potentiometer settings.

- CS (Chip Select) This pin must be pulled LOW before starting to send a command and pulled HIGH to signal the end of the command; this pin can be used to control multiple devices on the bus.

- **CLK** (Clock) The SDI bits are shifted in on the rising edge of the clock and SDO data is shifted out on the falling edge of the clock.

The key features of this interface include:

- Independently programmable Read & Write to all registers

- Direct parallel refresh of Tap register from corresponding internal NVMEM registers

- Increment and decrement instruction for Tap register

- Nonvolatile storage of the present Tap register values into one of the four NVMEM registers available.

- Configurable output buffer amplifier to allow both the functions of a potentiometer and a variable resistor

- Four 9-bit non-volatile registers store four preset wiper positions and the first one will be recalled to set the wiper position during power up.

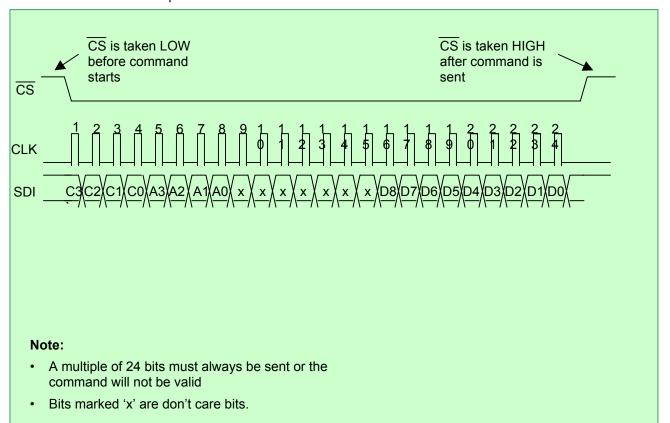

The serial interface uses an SPI compatible uniform 24-bit word format as shown below. This format is used for all members of the WMS720x family. The data is sent MSB first.

TABLE 2 - 24-BIT DATA WORD FORMAT

| MSB |    |    |    |    |    |    |    |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    | LSB |

|-----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|-----|

| C3  | C2 | C1 | C0 | А3 | A2 | A1 | A0 | Х | Х | Х | Х | Х | Х | Х | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

C3-C0 are the command bits that control the operation of the digital potentiometer according to the command instructions shown in the Instruction Set in Table 5 in Section 7.7.

A1 and A0 are the address bits that determine which channel is activated in the WMS720x family as shown in the table below. For the WMS7201 A0 and A1 are always set to 0.

TABLE 3 - A1 AND A0 ADDRESS BIT DECODE TABLE

| [A1 A0] | [0 0] | [0 1] [1 0] [1 1] |

|---------|-------|-------------------|

| Channel | 0     | 1 2 3             |

A3 and A2 are the address bits that decide which NVMEM memory to be accessed, as shown in the table below.

TABLE 4 - A3 AND A2 ADDRESS BIT DECODE TABLE

| [A3 A2] | [0 0] | [0 1] | [1 0] | [1 1] |

|---------|-------|-------|-------|-------|

| NVMEM   | 0     | 1     | 2     | 3     |

D7-D0 are the data values to be loaded into the Tap Register to set the wiper position, while D8 is used to set the output mode. D8 has to be loaded into the NVMEM0~3 first and then the "**Load Tap Register**" command (#6) has be executed to load D8 into the output-selection MUX to set the output mode. D8=0 sets the output to Buffer Off mode while D8=1 sets to Buffer On mode.

FIGURE 5 - SPI COMMAND WAVEFORMS

#### 7.7. INSTRUCTION SET

#### **TABLE 5 - INSTRUCTION SET**

| Inst<br>No. | Instruction Byte           | Data Byte 1                   | Data Byte 2             | Operation                                                                                                      |

|-------------|----------------------------|-------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|

| NO.         | C3 C2 C1 C0 A3 A2 A1<br>A0 | D15 D14 D13 D12 D11 D10 D9 D8 | D7 D6 D5 D4 D3 D2 D1 D0 |                                                                                                                |

| 1           | 0 0 0 0 x x x x            | x x x x x x x x               | x x x x x x x x         | No Operation (NOP). Do nothing                                                                                 |

| 2           | 1 1 0 0 x x A1 A0          | x x x x x x x x               | x x x x x x x x         | Read Tap Register and output selection MUX register                                                            |

| 3           | 0 1 0 0 x x A1 A0          | x x x x x x x x               | D7 D6 D5 D4 D3 D2 D1 D0 | Write to Tap Register with D7-D0                                                                               |

| 4           | 1 0 1 0 A3 A2 A1 A0        | x x x x x x x x               | x x x x x x x x         | Read NVMEM pointed to by A3-A0                                                                                 |

| 5           | 0 0 1 0 A3 A2 A1 A0        | x x x x x x x x D8            | D7 D6 D5 D4 D3 D2 D1 D0 | <b>Program NVMEM</b> pointed to by A3-A0 with D8-D0                                                            |

| 6           | 1 0 1 1 A3 A2 A1 A0        | x x x x x x x x               | x x x x x x x x         | Load Tap Register and output<br>selection MUX register with the<br>contents of NVMEM pointed to by<br>A3-A0    |

| 7           | 0 0 1 1 A3 A2 A1 A0        | x x x x x x x x               | x x x x x x x x         | Program NVMEM pointed to by<br>A3-A0 with the contents of Tap<br>Register and output selection MUX<br>register |

| 8           | 0 1 1 1 x x A1 A0          | x x x x x x x x               | x x x x x x x x         | <b>Up</b> : Increment setting of TR by one tap                                                                 |

| 9           | 1 1 1 1 x x A1 A0          | x x x x x x x x               | x x x x x x x x         | <b>Down</b> : Decrement setting of TR by one tap                                                               |

| 10          | 1 0 0 0 x x x x            | x x x x x x x x               | x x x x x x x x         | Sleep: Discontinue clock supply to the logic and memories                                                      |

| 11          | 0 0 0 1 x x x x            | x x x x x x x x               | x x x x x x x x         | Wake Up: Clock supply to the logic and memories                                                                |

| 12          | 1 1 0 1 A3 A2 A1 A0        | x x x x x x x x               | x x x x x x x x         | Byte-erase NVMEM pointed to by A3-A0                                                                           |

| 13          | 1 0 0 1 x x x x            | x x x x x x x x               | x x x x x x x x         | Power On Reset: Software reset the part to the power up state                                                  |

Note: C3-C0 are the command op-code; A3, A2 are the NVMEM address; A1, A0 are the channel address.

#### 7.8. BASIC OPERATION

This chapter describes the sequences of commands to send to the WMS7201 and how to use the different features.

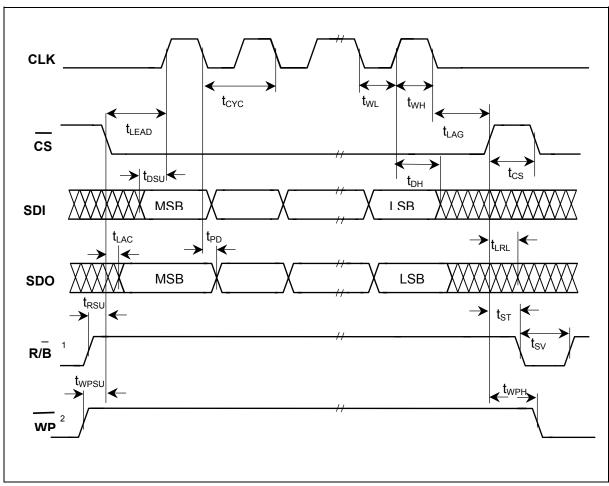

# 7.8.1 Sending a Command

- 1. Take the chip out of SLEEP mode.

- 2. Check that the write protect is set correctly if writing to NVMEM (10-pin TSSOP package only).

- 3. Pull the  $\overline{\text{CS}}$  pin LOW before sending data to the device.

- 4. 24 clock pulses are sent for each command. SDI must be valid on the rising edge of the clock, SDO is valid on the falling edge of the clock or  $\overline{\text{CS}}$ .

- 5. Take  $\overline{\text{CS}}$  HIGH after the command has completed

- 6. If command 2, 4, 5, 6 or 7 is sent, wait T<sub>SV</sub> time before sending the next command.

#### 7.8.2 Wake Up/Sleep/Power Commands

The chip is in SLEEP mode after:

- V<sub>DD</sub> is applied

- A Power on Reset command is sent

- A SLEEP command is sent

Before any operations can be performed the WAKE UP command must be sent.

When a SLEEP command is sent, the chip retains its resistor settings as long as the chip is powered up but cannot accept any other commands than a WAKE UP command.

|              |                | Г               | 1           | 1           | I                              |

|--------------|----------------|-----------------|-------------|-------------|--------------------------------|

| Inst.<br>No. | Command Name:  | Command Byte    | Data Byte 1 | Data Byte 2 | Comment                        |

| 11           | Wake Up        | 0 0 0 1 x x x x | xxxxxxx     | xxxxxxx     | Wake Up entire chip            |

| 10           | Sleep          | 1000xxxx        | xxxxxxx     | xxxxxxx     | Send chip into power save mode |

| 13           | Power on Reset | 1001xxxx        | xxxxxxx     | xxxxxxx     | Reset Chip                     |

| 1            | NOP            | 0000xxxx        | xxxxxxx     | xxxxxxx     | Dummy instruction              |

TABLE 6 - POWER RELATED COMMANDS

The commands above control the entire chip.

#### 7.8.3 Write to Tap Register (TR)

The microcontroller can write a value directly into the tap register or send an increment or decrement command to control the tap register. Alternatively, the contents of an NVMEM location can be written to the tap register. The only way to change the output buffer mode is to write the desired value of bit D8 into an NVMEM location and then load the corresponding NVMEM location into the tap register.

#### TABLE 7 - WRITING TO THE TAP REGISTERS

| Inst.<br>No. | Comman d Name:              | Command Byte      | Data Byte 1 | Data Byte 2             | Comment                                                      |

|--------------|-----------------------------|-------------------|-------------|-------------------------|--------------------------------------------------------------|

| 3            | Write to<br>Tap<br>Register | 0100 x x00        | xxxxxxx     | D7 D6 D5 D4 D3 D2 D1 D0 | Writes a value to the tap register.                          |

| 8            | Up                          | 0111 x x00        | xxxxxxx     | xxxxxxx                 | Increment tap register value by one                          |

| 9            | Down                        | 1111 x x00        | xxxxxxx     | xxxxxxx                 | Decrement tap register value by one                          |

| 6            | Load Tap<br>Register        | 1 0 1 1 A3 A2 0 0 | xxxxxxx     | xxxxxxx                 | Load the selected<br>NVMEM location into<br>the tap register |

#### 7.8.4 Programming Non-Volatile Memory (NVMEM)

The value stored in the NVMEM location is 9 bits, the 8 bits (D7-D0) of the tap register plus 1 bit (D8) of the output buffer mode. The NVMEM position must be erased before writing to it. There are two ways to program a value into NVMEM.

Write a value directly from the microcontroller.

Load the current potentiometer setting into NVMEM.

## **TABLE 8 - PROGRAMMING NVMEM**

| Inst.<br>No | Command<br>Name                          | Command Byte      | Data Byte 1 | Data Byte 2             | Comment                                                                            |

|-------------|------------------------------------------|-------------------|-------------|-------------------------|------------------------------------------------------------------------------------|

| 12          | Erase<br>NVMEM                           | 1 1 0 1 A3 A2 0 0 | xxxxxxx     | x x x x x x x x         | Erases the 9 bit word pointed to by A3, A2, A1 and A0.                             |

| 5           | Program<br>NVMEM                         | 0 0 1 0 A3 A2 0 0 | xxxxxxD8    | D7 D6 D5 D4 D3 D2 D1 D0 | Writes a value to the NVMEM register.                                              |

| 7           | Program<br>NVMEM<br>with Tap<br>Register | 0 0 1 1 A3 A2 0 0 | xxxxxxx     | x x x x x x x x         | Takes the current potentiometer settings and saves in the selected NVMEM location. |

For programming NVMEM, the following sequence must be followed:

- 1. Erase word at NVMEM location

- 2. Program word at NVMEM location

# 7.8.5 Reading Tap Register and NVMEM Location (10-pin TSSOP package only)

The contents of the tap register or any NVMEM location can be read back through the SDO pin. When a command is sent, the data is clocked out on the falling edge of the clock. Since daisy-chain operation requires data from one command to be clocked out when the next command arrives, any read command must be followed by another command to get the correct data on the SDO pin.

#### TABLE 9 - READING THE TAP REGISTER

| Inst.<br>No. | Command Name:              | Command Byte      | Data Byte 1 | Data Byte 2             | Comment                                       |

|--------------|----------------------------|-------------------|-------------|-------------------------|-----------------------------------------------|

| 4            | Read<br>NVMEM              | 1 0 1 0 A3 A2 0 0 | xxxxxxx     | x x x x x x x x         | Read the value of the selected NVMEM location |

| 2            | Read Tap<br>Register       | 1100 x x00        | xxxxxxx     | x x x x x x x x         | Read the value of the selected tap register   |

| 1            | NOP to<br>Read<br>Register | 0000 x xxx        | xxxxxxD8    | D7 D6 D5 D4 D3 D2 D1 D0 | Output data to SDO pin                        |

To read the contents of either the tap register or a NVMEM location, the following sequence must be followed.

- 1. Send the desired read command (#2 or #4)

- 2. Send another command such as NOP and read the SDO pin on the falling edge of the clock. The other command could be any command, but to make sure that the chip does not change anything, send either another Read command or a NOP command (#1).

# 8. TIMING DIAGRAMS

FIGURE 6 - WMS7201 TIMING DIAGRAM

Notes: (1) Internal signal only. (2) Only on 10-pin TSSOP package.

**TABLE 10 - TIMING PARAMETERS**

| PARAMETER                                 | SYMBOL            | MIN. | MAX. | UNIT |

|-------------------------------------------|-------------------|------|------|------|

| SPI Clock Cycle Time                      | t <sub>CYC</sub>  | 100  |      | ns   |

| SPI Clock HIGH Time                       | t <sub>WH</sub>   | 50   |      | ns   |

| SPI Clock LOW Time                        | t <sub>WL</sub>   | 50   |      | ns   |

| Lead Time                                 | t <sub>LEAD</sub> | 100  |      | ns   |

| Lag Time                                  | t <sub>LAG</sub>  | 100  |      | ns   |

| SDI Setup Time                            | t <sub>DSU</sub>  | 20   |      | ns   |

| SDI Hold Time                             | t <sub>DH</sub>   | 20   |      | ns   |

| CS to SDO – SPI Line Acquire 1            | t <sub>LAC</sub>  | 5    |      | ns   |

| CS to SDO – SPI Line Release 1            | t <sub>LRL</sub>  | 5    |      | ns   |

| CLK to SDO Propagation Delay <sup>1</sup> | t <sub>PD</sub>   | 1    |      | ns   |

| Store to NVMEM Save Time                  | t <sub>SV</sub>   |      | 2    | ms   |

| CS Deselect Time                          | t <sub>CS</sub>   | 600  |      | ns   |

| Startup Time                              | t <sub>ST</sub>   | 0.1  |      | ms   |

| WP Setup Time <sup>1</sup>                | t <sub>WPSU</sub> | 10   |      | ns   |

| WP Hold Time <sup>1</sup>                 | t <sub>WPH</sub>  | 10   |      | ns   |

Note: The interface timing characteristics apply to all parts but are guaranteed by design and not subject to production test.

Note 1: 10-pin package only.

# 9. ABSOLUTE MAXIMUM RATINGS

# **TABLE 11 – ABSOLUTE MAXIMUM RATINGS**

| Condition                  | Value                                  |

|----------------------------|----------------------------------------|

| Junction temperature       | 150°C                                  |

| Storage temperature        | -65° to +150°C                         |

| Voltage applied to any pad | $(V_{ss} - 0.3V)$ to $(V_{DD} + 0.3V)$ |

| $V_{DD} - V_{SS}$          | -0.3 to 7.0V                           |

Note: Exposure to conditions beyond those listed under: Absolute Maximum Ratings, may adversely affect the life and reliability of the device.

# 10. ELECTRICAL CHARACTERISTICS

## **TABLE 12 - ELECTRICAL CHARACTERISTICS**

All Parameters apply across specified operating ranges unless noted ( $V_{DD}$ : 2.7V~5.5V; Temp: -40°C~85°C) Typical values:  $V_{DD}$ =5V and T=25°C

| PARAMETER                              | SYMBOL                          | MIN.            | TYP | MAX.        | UNITS      | CONDITIONS                                                  |

|----------------------------------------|---------------------------------|-----------------|-----|-------------|------------|-------------------------------------------------------------|

| Rheostat Mode                          |                                 |                 |     |             |            |                                                             |

| Nominal Resistance                     | R                               | -20             |     | +20         | %          | T=25°C, V <sub>W</sub> open                                 |

| Different Non Linearity                | DNL                             | -1              | 0.3 | +1          | LSB        |                                                             |

| Integral Non Linearity                 | INL                             | -1              | 0.5 | +1          | LSB        |                                                             |

| Rheostat Tempco <sup>1</sup>           | $\Delta R_{AB}/\Delta T$        |                 | 500 |             | ppm/°      |                                                             |

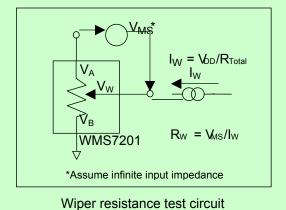

| Wiper Resistance <sup>2</sup>          | R <sub>W</sub>                  |                 | 50  | 100         | Ω          | $V_{DD}$ =5V,<br>I= $V_{DD}/R_{Total}$                      |

|                                        |                                 |                 | 80  | 120         | Ω          | $V_{DD}$ =2.7V,<br>$I=V_{DD}/R_{Total}$                     |

| Potentiometer Mode                     |                                 |                 |     |             |            |                                                             |

| Resolution <sup>1</sup>                | N                               | 8               |     |             | Bits       |                                                             |

| Different Non Linearity <sup>2</sup>   | DNL                             | -1              |     | +1          | LSB        |                                                             |

| Integral Non Linearity <sup>2</sup>    | INL                             | -1              |     | +1          | LSB        |                                                             |

| Potentiometer Tempco <sup>1</sup>      | $\Delta V_w/\Delta T$           |                 | +20 |             | ppm/°<br>C | Code = 80h                                                  |

| Full Scale Error                       | $V_{FSE}$                       | -1              |     | 0           | LSB        | Code = Full Scale                                           |

| Zero Scale Error                       | $V_{ZSE}$                       | 0               |     | 1           | LSB        | Code = Zero Scale                                           |

| Resistor Terminal                      |                                 |                 |     |             |            |                                                             |

| Voltage Range <sup>1</sup>             | $V_A, V_B, V_W$                 | V <sub>SS</sub> |     | $V_{DD}$    | V          |                                                             |

| Terminal Capacitance <sup>1</sup>      | C <sub>A</sub> , C <sub>B</sub> |                 | 30  |             | pF         |                                                             |

| Wiper Capacitance <sup>1</sup>         |                                 |                 | 30  |             | pF         |                                                             |

| Dynamic Characteristics <sup>1</sup>   |                                 |                 |     |             |            |                                                             |

|                                        | BW <sub>10K</sub>               |                 | 1.5 |             | MHz        | V <sub>DD</sub> =5V, V <sub>B</sub> =V <sub>SS</sub>        |

| Bandwidth –3dB                         | BW <sub>50K</sub>               |                 | 300 |             | KHz        | Code = Full Scale Code = 80h                                |

| Baridwidtii –3dB                       | BW <sub>100K</sub>              |                 | 200 |             | KHz        | CL=30pf                                                     |

| Settling Time to 1 LSB                 | T <sub>S</sub>                  |                 | 80  | 100         | uS         | $V_{DD}$ =5.5V= $V_{A}$ ,<br>$V_{B}$ = $V_{SS}$             |

| <b>Analog Output (Buffer enab</b>      | led)                            |                 |     |             |            |                                                             |

| Amp Output Current <sup>2</sup>        | I <sub>OUT</sub>                | 3               |     |             | mA         | V <sub>O</sub> =1/2 scale                                   |

| Amp Output Resistance <sup>2</sup>     | Rout                            |                 | 1   | 10          | Ω          |                                                             |

| Total Harmonic Distortion <sup>1</sup> | THD                             |                 |     | 0.08        | %          | $V_A$ =2.5V, $V_{DD}$ =5V, $f$ =1kHz, $V_{IN}$ =1 $V_{RMS}$ |

| Digital Inputs/Outputs                 |                                 |                 |     |             |            |                                                             |

| Input High Voltage                     | V <sub>IH</sub>                 | $0.7V_{DD}$     |     |             | V          |                                                             |

| Input Low Voltage                      | $V_{IL}$                        |                 |     | $0.3V_{DD}$ | V          |                                                             |

| Output Low Voltage                     | V <sub>OL</sub>                 |                 |     | 0.4         | V          | I <sub>OL</sub> =2mA                                        |

| Input Leakage Current                  | I <sub>LI</sub>                 | -1              |     | +1          | uA         | CS =V <sub>DD</sub> ,Vin=Vss                                |

# **WMS7201**

|                                 |                              |     |     |     |       | ~ V <sub>DD</sub>                                                  |

|---------------------------------|------------------------------|-----|-----|-----|-------|--------------------------------------------------------------------|

| Output Leakage Current          | I <sub>Lo</sub>              | -1  |     | +1  | uA    | $\overline{\text{CS}} = V_{\text{DD}}, \text{Vin} = V_{\text{SS}}$ |

|                                 |                              |     |     |     |       | ~ V <sub>DD</sub>                                                  |

| Input Capacitance <sup>1</sup>  | C <sub>IN</sub>              |     | 25  |     | pF    | $V_{DD}$ =5V, fc = 1Mhz                                            |

|                                 |                              |     |     |     |       | Code = 80h                                                         |

| Output Capacitance <sup>1</sup> | C <sub>OUT</sub>             |     | 25  |     | pF    | $V_{DD}$ =5V, fc = 1Mhz                                            |

|                                 |                              |     |     |     |       | Code = 80h                                                         |

| Power Requirements              |                              |     |     |     |       |                                                                    |

| Operating Voltage <sup>1</sup>  | $V_{DD}$                     | 2.7 |     | 5.5 | V     |                                                                    |

| Operating Current               | I <sub>DDR</sub>             |     | 1   | 1.8 | mA    | All ops except                                                     |

| Operating Current               |                              |     | I   | 1.0 | IIIA  | NVMEM program                                                      |

|                                 | I <sub>DDW</sub>             |     | 1   | 2   | mA    | During Non-                                                        |

| Operating Current               |                              |     |     |     |       | volatile memory                                                    |

|                                 |                              |     |     |     |       | program                                                            |

| Standby Current                 | I <sub>SA</sub>              | 0.5 |     | 1   | mA    | Buffer is active, ,                                                |

|                                 |                              |     |     |     |       | no load                                                            |

|                                 | I <sub>SB</sub> <sup>2</sup> |     | 0.1 | 1   | uA    | Buffer is inactive,                                                |

|                                 |                              |     |     |     |       | Power Down, No                                                     |

|                                 |                              |     |     |     |       | load                                                               |

| Power Supply Rejection Ratio    | PSRR                         |     |     | 1   | LSB/V | V <sub>DD</sub> =5V±10%,                                           |

|                                 | 1 51(1)                      |     |     |     |       | Code=80h                                                           |

Note: 1. Not subject to production test; 2. Only on Final Test; 3.  $V_{DD}$  = +2.7V to 5.5V,  $V_{SS}$  = 0V, T = 25°C, unless otherwise noted.

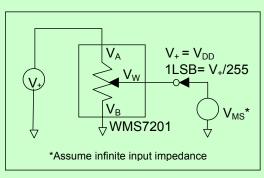

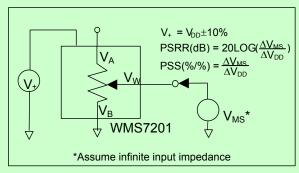

#### **10.1 TEST CIRCUITS**

Potentiometer divider nonlinearity error test circuit (INL, DNL)

Power supply sensitivity test circuit (PSS, PSRR)

Resistor position nonlinearity error test circuit (Rheostat Operation: R-INL, R-DNL)

Capacitance test circuit

Gain vs. frequency test circuit

FIGURE 7 - TEST CIRCUITS

# 11. TYPICAL APPLICATION CIRCUIT

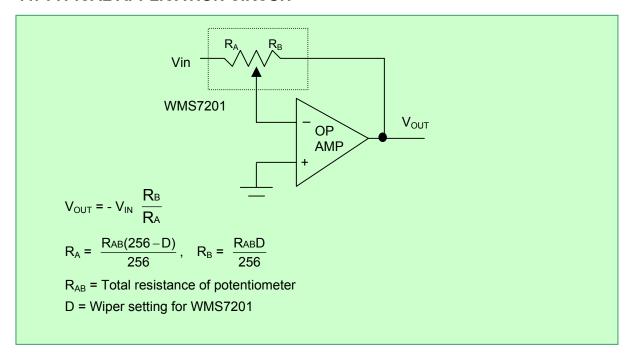

FIGURE 8 - PROGRAMMABLE INVERTING GAIN AMPLIFIER USING THE WMS7201

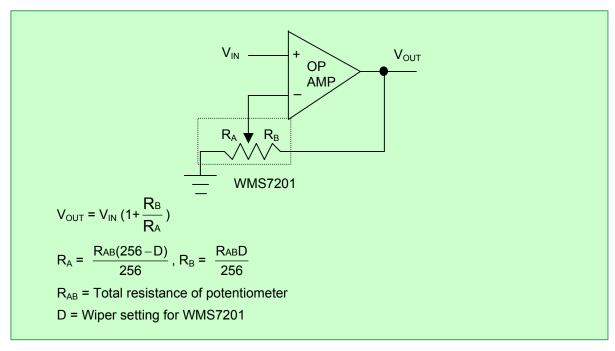

FIGURE 9 - PROGRAMMABLE NON-INVERTING GAIN AMPLIFIER USING THE WMS7201

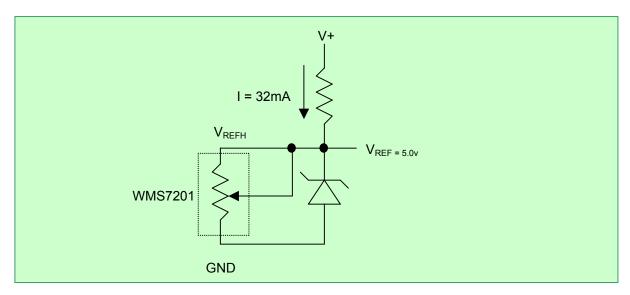

FIGURE 10 – WMS7201 TRIMMING VOLTAGE REFERENCE

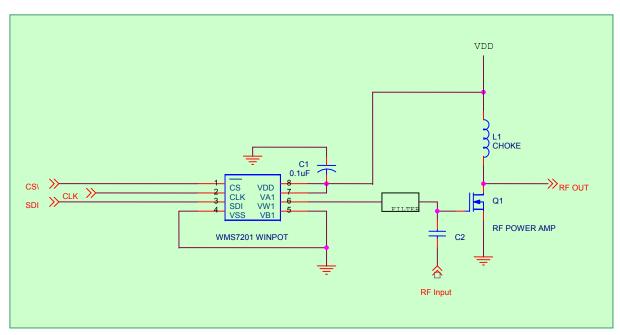

FIGURE 11 - WMS7201 RF AMP CONTROL

#### 11.1. LAYOUT CONSIDERATIONS

A  $0.1\mu F$  bypass capacitor as close as possible to the  $V_{DD}$  pin is recommended for best performance. Often this can be done by placing the surface mount capacitor on the bottom side of the PC board, directly between the  $V_{DD}$  and  $V_{SS}$  pins. Care should be taken to separate the analog and digital traces. Sensitive traces should not run under the device or close to the bypass capacitors.

A dedicated plane for analog ground helps in reducing ground noise for sensitive analog signals.

FIGURE 12 - WMS7201 LAYOUT

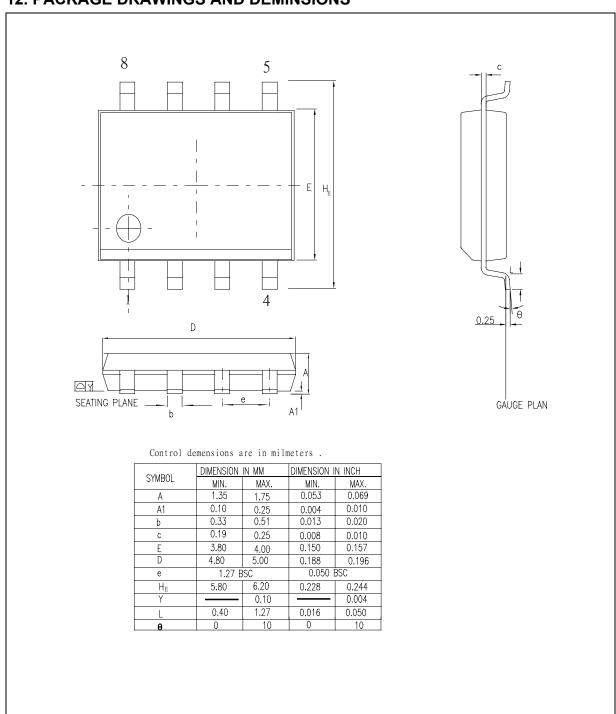

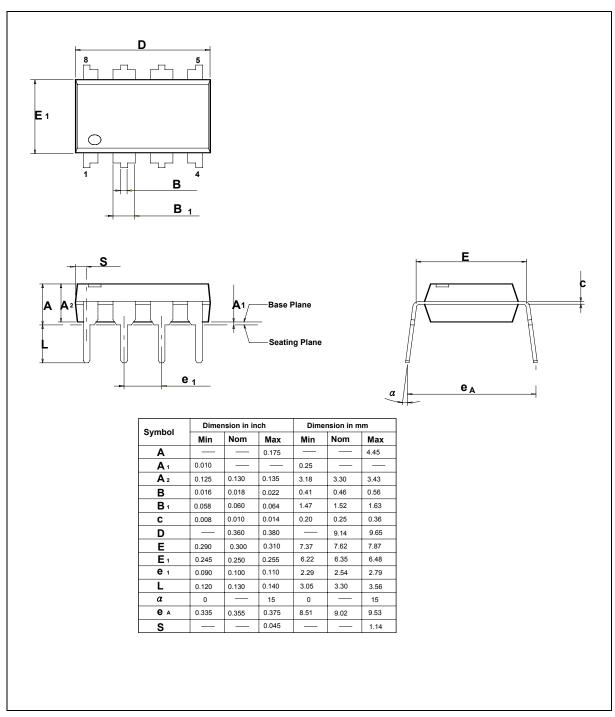

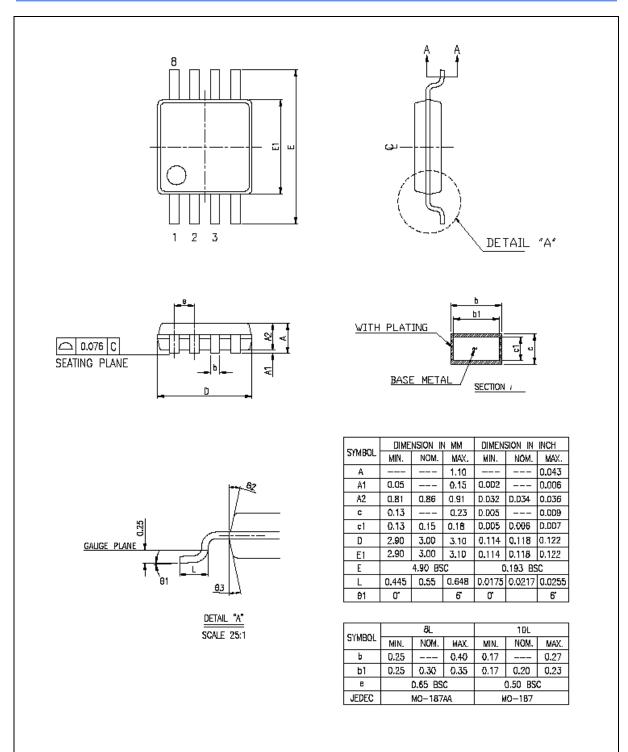

# 12. PACKAGE DRAWINGS AND DEMINSIONS

FIGURE 13 - 8L SOIC - 150MIL

FIGURE 14 - 8L PDIP

FIGURE 15 - 8L MSOP

## 13. ORDERING INFORMATION

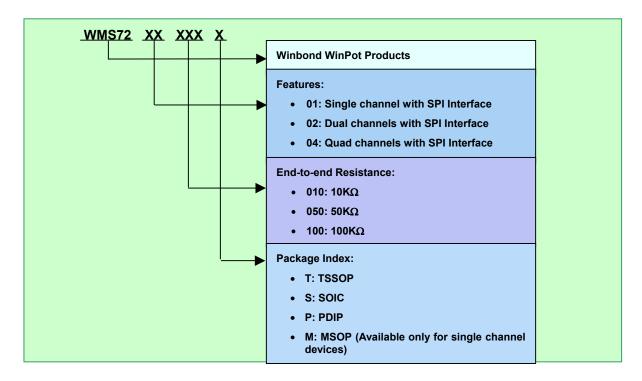

Winbond's WinPot Part Number Description:

For the latest product information, access Winbond's worldwide website at <a href="http://www.winbond-usa.com">http://www.winbond-usa.com</a>

#### 14. VERSION HISTORY

| VERSION | DATE      | PAGE | DESCRIPTION   |

|---------|-----------|------|---------------|

| 1.0     | Jan. 2003 | All  | Initial issue |

The contents of this document are provided only as a guide for the applications of Winbond products. Winbond makes no representation or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to discontinue or make changes to specifications and product descriptions at any time without notice. No license, whether express or implied, to any intellectual property or other right of Winbond or others is granted by this publication. Except as set forth in Winbond's Standard Terms and Conditions of Sale, Winbond assumes no liability whatsoever and disclaims any express or implied warranty of merchantability, fitness for a particular purpose or infringement of any Intellectual property.

Winbond products are not designed, intended, authorized or warranted for use as components in systems or equipments intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental injury could occur.

#### Headquarters

No. 4, Creation Rd. III Science-Based Industrial Park, Hsinchu, Taiwan TEL: 886-3-5770066 FAX: 886-3-5665577 http://www.winbond.com.tw/

#### **Taipei Office**

9F, No. 480, Pueiguang Rd. Neihu District Taipei, 114 Taiwan TEL: 886-2-81777168 FAX: 886-2-87153579

#### Winbond Electronics Corporation America

2727 North First Street, San Jose, CA 95134, U.S.A. TEL: 1-408-9436666 FAX: 1-408-5441797 http://www.winbond-usa.com/

#### **Winbond Electronics Corporation Japan**

7F Daini-ueno BLDG. 3-7-18 Shinyokohama Kohokuku, Yokohama, 222-0033 TEL: 81-45-4781881 FAX: 81-45-4781800

#### Winbond Electronics (Shanghai) Ltd.

27F, 299 Yan An W. Rd. Shanghai, 200336 China TEL: 86-21-62365999 FAX: 86-21-62356998

#### Winbond Electronics (H.K.) Ltd.

Unit 9-15, 22F, Millennium City, No. 378 Kwun Tong Rd., Kowloon, Hong Kong TEL: 852-27513100 FAX: 852-27552064

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners. This product incorporates SuperFlash® technology licensed From SST.