DOCUMENT: I20010 REV LETTER: A PAGE NO: 1 OF 5 DATE: 2016-03-24 PART NUMBER:

# Over-Voltage Protection IC

#### CYG Wayon Circuit protection Co., Ltd.

No. 1001, Shiwan Qi Road, Pudong Area, Shanghai

Tel: 86-21-50310888 50968308

E-mail: market@way-on.com Http://www.way-on.com

### **WP3881**

## **Description**

WP3881 can disconnect the systems from its output pin(OUT) in case wrong input operating conditions are detected.

The system is positive overvoltage protected up to 28V. The overvoltage thresholds (OVLO) is 13.75 V.

WP3881 internal Thermal-Shutdown Protection.

The device is packaged in advanced full-Green compliant Wafer Level Chip Scale Packaging (WLCSP12).

#### **Features**

- □ 4.8A Continuous Current Capability

- $\square$  Typical R<sub>ON</sub>: 35 m $\Omega$  N-Channel MOSFET

- $\hfill \square$   $\hfill V_{IN}$  Operating Range: 2.1V to 28V

- □ Overvoltage Lockout: OVLO=13.75V(TYP.)

- □ Overvoltage-Protection Response Time: 100ns(TYP.)

- □ OVLO Threshold Range: +4V to +20V

- ☐ Startup Debounce Time: 21ms(TYP.)

- □ Internal Thermal-Shutdown Protection

- □ Surge immunity to ± 100V

- □ ESD Protected: Human Body Model: JESD22-A114(All pins)±2KV

- ☐ CSP12 Package (ball pitch=0.4mm)

### **Applications**

- □ Smartphones, Tablet PC

- ☐ HDD, Storage and Solid State Memory Devices

- □ Portable Media Devices, Laptop & MID

- □ SLR Digital Cameras

- □ GPS and Navigation Equipment

- □ Industrial Handheld and Enterprise Equipment

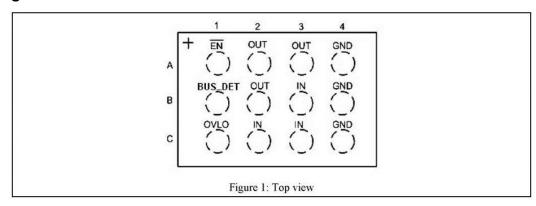

## **Pin Configuration**

| SYMBOL                       | PARAMETERS                                    | MIN  | MAX                  | UNIT |

|------------------------------|-----------------------------------------------|------|----------------------|------|

| V <sub>IN</sub>              | VIN to GND                                    | -0.3 | 29                   | V    |

| Vouт                         | VOUT to GND                                   | -0.3 | V <sub>IN</sub> +0.3 | V    |

| Vovlo                        | OVLO to GND                                   | -0.3 | 14                   | V    |

| $V_{\overline{\mathrm{EN}}}$ | EN to GND                                     | -0.3 | 7                    | V    |

| I <sub>SW1</sub>             | Maximum Continuous Current of switch IN-OUT   |      | 4.8                  | Α    |

| I <sub>SW2</sub>             | Maximum Peak Current of switch IN-OUT(10ms)   |      | 8                    | Α    |

| $P_{D}$                      | Power Dissipation at $T_A$ = +70 $^{\circ}$ C |      | 1090                 | mW   |

| T <sub>STG</sub>             | Storage Junction Temperature                  | -65  | +150                 | °С   |

| T <sub>A</sub>               | Operating Temperature Range                   | -40  | +85                  | °С   |

| T∟                           | Lead Soldering Temperature (reflow).          |      | +260                 | °С   |

| TJ                           | Junction Temperature                          |      | +150                 | °C   |

| Surge                        | VIN to GND, IEC 61000-4-5, Surge Protection   | -100 | 100                  | V    |

### **Pin Function**

| Pin      | Name     | Pin Function                                                                                                                                                                                                                               |  |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1       | EN       | Microphone Mode Enable. Active low.                                                                                                                                                                                                        |  |

| A2,A3,B2 | OUT      | Output Voltage. Output of internal switch. Connect OUT pins together for proper operation.                                                                                                                                                 |  |

| A4,B4,C4 | GND      | Ground. Connect GND pins together for proper operation.                                                                                                                                                                                    |  |

| B1       | VBUS_DET | Regulation output of VBUS                                                                                                                                                                                                                  |  |

| B3,C2,C3 | IN       | Voltage Input. Connect IN pins together for proper operation.                                                                                                                                                                              |  |

| C1       | OVLO     | External OVLO Adjustment. Connect OVLO to GND when using the internal threshold. Connect a resistor-divider to OVLO to set a different OVLO threshold; this external resistor-divider is completely independent of the internal threshold. |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| SYMBOL               | PARAMETERS                                        | CONDITIONS                                                           | MIN   | TYP   | MAX  | UNIT |

|----------------------|---------------------------------------------------|----------------------------------------------------------------------|-------|-------|------|------|

| Basic Operatio       | n                                                 |                                                                      |       |       |      |      |

| V <sub>IN</sub>      | Input Voltage                                     |                                                                      | 2.1   |       | 28   | V    |

| I <sub>IN</sub>      | V <sub>IN</sub> Quiescent Current                 | V <sub>IN</sub> =5V, OUT floating                                    |       |       | 220  | μA   |

| Ron                  | On-Resistance of<br>Switch IN-OUT                 | V <sub>IN</sub> =5.0V, I <sub>OUT</sub> =1A                          |       | 35    | 42   | mΩ   |

| V <sub>OVL</sub> O   | Overvoltage protect of V <sub>IN</sub>            | $V_{\text{IN}}$ rise up                                              | 13.50 | 13.75 | 14.0 | V    |

|                      | Overvoltage protect hysteresis of V <sub>IN</sub> |                                                                      |       | 0.15  |      | V    |

|                      | Adjustable OVLO Threshold Range                   |                                                                      | 4     |       | 20   | V    |

| V <sub>OVLO_TH</sub> | OVLO Set Threshold                                |                                                                      | 1.18  | 1.2   | 1.22 | V    |

| Vovlo_select         | External OVLO Select<br>Threshold                 |                                                                      | 0.2   |       | 0.3  | V    |

| V <sub>DET</sub>     | regulation output of VBUS_DET                     | $V_{IN}$ =12V, $\overline{EN}$ =low                                  | 6     |       | 9.5  | V    |

| V <sub>IH</sub>      | EN Input Logic High<br>Voltage                    |                                                                      | 1.4   |       |      | V    |

| V <sub>IL</sub>      | EN Input Logic Low<br>Voltage                     |                                                                      |       |       | 0.3  | V    |

|                      | Thermal Shutdown                                  |                                                                      |       | 150   |      | °C   |

|                      | Thermal-shutdown<br>Hysteresis                    |                                                                      |       | 20    |      | °C   |

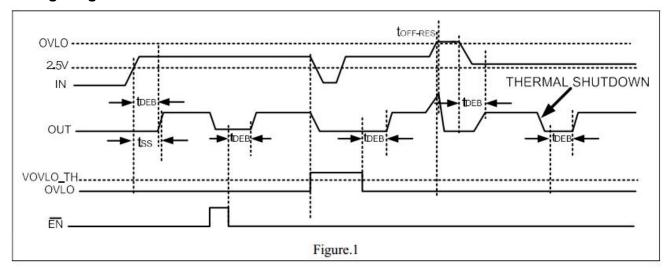

| Dynamic Chara        | acteristics: see figure                           |                                                                      |       |       |      |      |

| t <sub>DEB</sub>     | Debounce time                                     | Time from 2.1V< $V_{IN}$ < $V_{OVLO}$ to $V_{OUT}$ = 10% of $V_{IN}$ |       | 21    |      | ms   |

| t <sub>SS</sub>      | Soft-start time                                   | Time from 2.1V< $V_{IN}$ < $V_{OVLO}$ to $V_{OUT}$ = 90% of $V_{IN}$ |       | 22    |      | ms   |

| toff_res             | Switch turn-off response time                     | V <sub>IN</sub> > V <sub>OVLO</sub> to V <sub>OUT</sub> stop rising  |       | 100   |      | ns   |

# **Electrical Characteristics**

Unless otherwise noted, typical values are at  $V_{\text{IN}}\text{=}5V$  and  $T_{\text{A}}\text{=}25~^{\circ}\text{C}.$

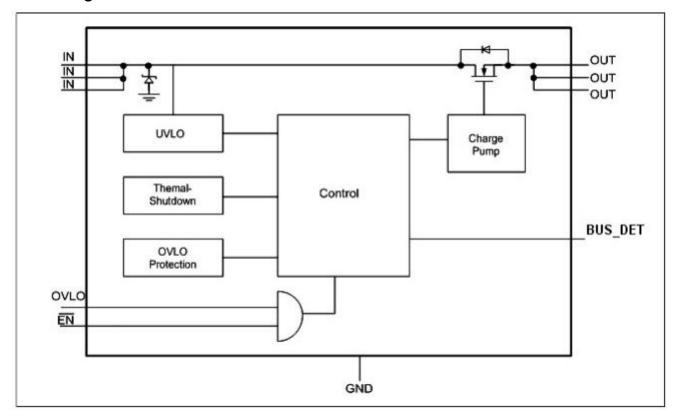

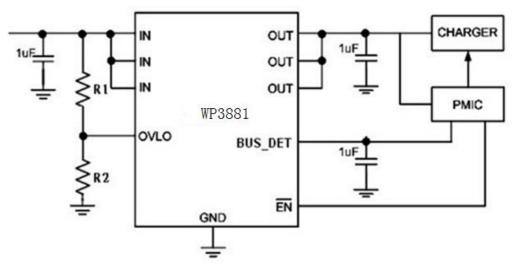

### **Block Diagram**

### **Functional Description**

The OVP switch with overvoltage protection feature a low 35 m $\Omega$  (TYP.) on-resistance(R<sub>ON</sub>) internal FET and protect low-voltage systems against voltage faults up to  $28V_{DC}$ . If  $\overline{\rm EN}$  is in the logic low state, when the input voltage(V<sub>IN</sub>) exceeds 13.75V, the internal FET is quickly turned off to prevent damage to the protected downstream components. If  $\overline{\rm EN}$  is in the logic high state, the WP3881 will feature the Microphone mode which disables the protect low-voltage system.

When input (OVLO) is set lower than 0.2V. The overvoltage protection threshold is 13.75V.

The overvoltage protection threshold can also be adjusted by external resistors when input (OVLO) is set higher than 0.3V.

$$V_{IN\_OVLO} = V_{OVLO\_TH} * (1+R1/R2)$$

$V_{OVLO\_TH} = 1.2V(TYP.)$

The internal FET turns off when the junction temperature exceeds +150°C (TYP.). The device exits thermal shutdown after the junction temperature cools by 20°C (TYP.).

#### Input Capacitor

To limit the voltage drop on the input supply caused by transient inrush current when the switch turns on into a discharged load capacitor or short-circuit, a capacitor 1µF or larger must be placed between the VIN and GND pins.

### **Output Capacitor**

A 1µF or larger capacitor should be placed between the OUT and GND pins.

# **Timing Diagram**

# **Application Circuits**

Note: R1 and R2 are only required for adjustable OVLO; Otherwise OVLO is connected to GND.

\*: This circuit only supplies for reference.

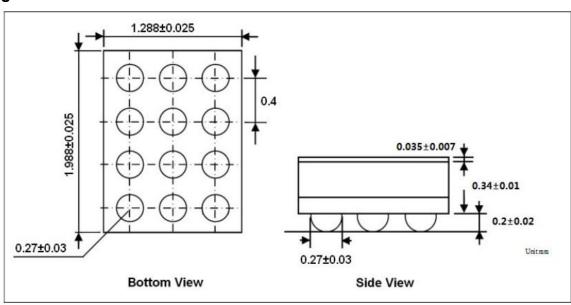

# **Package**